### NATIONAL RADIO ASTRONOMY OBSERVATORY Green Bank, West Virginia

# 300-FOOT CONTROL COMPUTER MEMO NO. 17

1

ß

## DA/CP IMPLEMENTATION OF THE 10-ms SIDEREAL CLOCK COUNTER

$\mathcal{L}_{k'}^{\ell}$

R. Fisher

August 28, 1985

#### DA/CP Implementation of the 10-ms Sidereal Clock Counter

## 27 August 1985 R. Fisher

Part of the sidereal time keeping scheme in the 300-ft control computer system is a 10-ms pulse counter which keeps track of elapsed time since the system's master clock was last read. Servicing this rapid stream of interrupts would impose a considerable timing burden on the main processor, so the DA/CP's own software has been modified to include this counter function and to pass the counter value to the cpu upon request.

External interrupts to the MASSCOMP computer must go through the DA/CP. These can be generated by the I/O modules in the DA/CP or can come from or go through the DA/CP clock module. All of these interrupts enter the DA/CP on the STD bus with one interrupt line for each I/O slot. Slot 0 (the one next to the clock module) has the highest interrupt priority, and higher numbered slots have successively lower priorities. For this application we will have an externally generated 100 Hz pulse train applied to the "S" input of clk0 of the clock module which in turn will generate an interrupt every 10 ms on the slot 0 STD interrupt line. This slot has no I/O module plugged into it which would normally use this interrupt line. For test purposes, the clock module can be programmed to generate a 100 Hz pulse train on the slot0 interrupt line to simulate the external generator.

Each I/O module has a block of DA/CP program code associated with it to control the flow of data and control between the module and the memory in the host computer. Also, associated with every DA/CP slot, including empty ones, are small blocks of code which allow the host cpu to effectively talk directly to and receive data and interrupts directly from each slot in a mode called the buswindow. Before this modification of the DA/CP code the host cpu could receive the 10-ms interrupts directly from slot 0 and keep track of them by incrementing a counter in its own memory. The modified DA/CP code intercepts the 10-ms pulses and increments a DA/CP register counter, and when the host cpu asks for data from slot 0 in the buswindow mode the new code causes the DA/CP to send the counter value as if it had come from an I/O module in this slot. When the counter is read it is reset to zero to keep it from overflowing.

As of this writing some consideration is being given to the possibility of accessing the 10-ms counter from the code (handlers) for other I/O modules in the DA/CP, and the counter word size may be increased to 24 or 32 bits, so the details of the DA/CP code accompanying this note may have been changed by the time you read this, but the general idea should be the same.

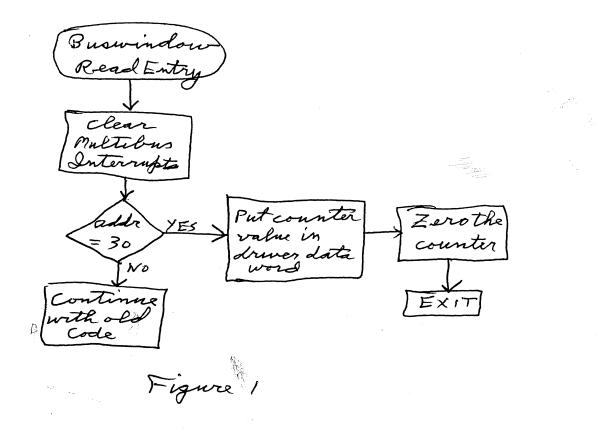

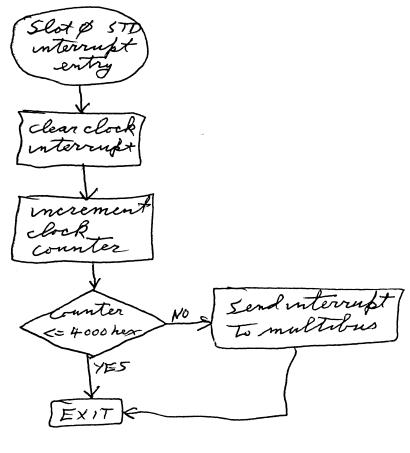

Figures 1 and 2 show the logic flow associated with the counter incrementing in response to clock interrupts and the access of the counter value by the host cpu. The first program listing labelled "buswnclk.asd" shows the modified buswindow handler code. The changes are marked in the left margin. One of the three new constants (slot0\_rd\_mask=0x2e001e) defines the I/O address which the host cpu must read to get the counter Aug 27 18:15 1985 buswnclk.doc Page 2

value. In this case the address is (1E hex = 30 decimal). The counter is kept in a DA/CP register "clock counter". The piece of code under ORIGIN(7) tests the cpu read request for the assigned address and, if a match is found, branches to the new code which puts the counter value in the driver's data word and resets the counter.

ORIGIN(960) is the entry point for the slot 0 interrupt. The register SD is the STD data register to which a command word is written to clear the clock interrupt, SA is the address register for this command word, and QR is a general purpose register used as a dummy here. The operation BLEQUW means "branch if less than or equal to zero" and refers to the preceding CoMPare. The NOP is for timing delay.

The second program listing shows how the DA/CP clock may be used from a C program. The procedure "start\_clock" contains the MASSCOMP supplied DA/CP routine references to set up the internal clock or route the external pulses to the STD bus and to open the path for buswindow access to the counter. The routine "sidereal\_time" contains the read statement "mrwnrd" for the counter value which ends up in "dacp\_counter". The references "mrwnion" and "mrclkintgat" in "reset clock" enable AST's from the driver and interrupts to the DA/CP from the STD bus, respectively. If the counter has not been read for some time, and it is in danger of overflowing, the DA/CP and its driver generate an AST whose service routine has been defined to be "inc\_ten\_ms\_count" by the open-window call at the end of "start\_clock". (See the description of the "mrwnopn" routine in the DA/CP applications programming manual.)

Figure 2

#### Aug 27 20:15 1985 buswnclk.asd Page 1

1.1 (MASSCOMP) 10/23/84 ; @(#)buswindow.asd BEGIN MODULE \*\*\*\* Bus Window Mode IPC Handler \*\*\*\* ;Revision History ;24-Sep-82 Created Final Tweaks ;30-Oct-82 ;04-Nov-82 Disable Clock Interrupts on Start Up ;10-Dec-82 Change Clock address to FF00 in memory space ;04-Jan 83 Add Register with constant 4 ;11-Feb-83 Add Free Pool ;16-Feb-83 Fix Start Code so Fifo Enables correctly ;25-Mar-83 Modify syntax for new assembler declare "idle" global ;28-Mar-83 remove "PSECT" from "bwcode" P change bus window interrupt enable/disable to ;04-apr-83 get mask from "bwadr" ;13-Apr-83 add handler table output operations D. Cane broke out all waits into callable routine ;08-sep-83 ;23-aug-85 R. Fisher added patches to implement clk0 intr counter ; this is the default load image for the ipc that i will call its ;operating system. it contains bus window mode for each std interrupt, ;the idle loop, the subroutine return code and the fifin interrupt ; handler. it also has the code for handler entry points ; these are global constants for use by any ipc device handler intr clr=0xf800 fi ov set==0x201init cr=0x241 ; reset fov, enable fi interrupts, disable slot intrpts clk wr csr==0xleff00 intr no stat0==0x600080 intr no statl==0x600088 intr no stat2==0x600090 intr no stat3==0x600098 intr no stat4==0x6000a0 intr no stat5==0x6000a8 intr no stat6==0x6000b0 intr no stat7==0x6000b8 intr no stat ex0==0x60003c intr no stat ex1==0x600034 intr stat0==0x600082intr\_stat1==0x60008a intr stat2==0x600092 intr\_stat3==0x60009a intr stat4==0x6000a2intr stat5==0x6000aa

intr\_stat6==0x6000b2 intr\_stat7==0x6000ba intr\_stat\_ex0==0x60003e intr\_stat\_ex0==0x600036

Constants associated with 10-ms clock counter in slot 0 slot0 rd mask=0x2e001e ;slot0 read address (30 decimal) intro\_clr=0x008000 ;clk0 interrupt clear clk wr csr4==0xleff04 ;clk0-3 command address CONFIGURATION CONFIGURATION NUMBER, dacp start, entry pt, bwcmd BEGIN MODULE PARAMETER DECLARE bwcmd, DS, GLOBAL, 0x000000 ; bus window command cmdpatch DECLARE bwadr, DS, GLOBAL, 0x000000 ;bus window address DECLARE bwdat, DS, GLOBAL, 0x000000 ;bus window data END PARAMETER DECLARE entry pt, DS, GLOBAL ;INTO entry point ENTRY bw rd wr, bw rd wr, 0, 0, 0, 0, 0 ENTRY bw ints, bw interrupts, 0, 0, 0, 0, 0 STD -1,  $\overline{0}$ , 0, 0,  $\overline{0}$ DECLARE taqvec, DS, LOCAL ;temp. loc. for jump thru fifin tag ;will be loaded with constant 4 DECLARE lit\_4, REG, GLOBAL DECLARE clock counter, REG, STATIC ; counter to be used with 10ms sidereal ; pulses (300' cntl comp) HANDLER 0, 0, 0; this is the code for the "service" interrupts that ARE( part the ipc ;hardwARE(; idle loop, subroutines, fifo in interrupt, etc..... ORIGIN(0) ; idle loop interrupt location idle:: INT JMP idle ; idle loop must leave DS free ORIGIN(1) ;subroutine interrupt location RESUME ;pop stack to subroutine ORIGIN(2) ;mbus 0 interrupt location JMP entry\_pt ; jump to handler entry point ORIGIN(3) ;fifo in interrupt handler MOV FI, tagvec ;get tag for jump to service JMP taqvec ; go to tag defined code ;ex 0 interrupt location ;handle external interrupt 0 ORIGIN(5) JMP exoloc ;ex 1 interrupt location ORIGIN(6) JMP exlloc ;handle external interrupt 1 ; bus window read, write and reset code ;mbus 1 interrupt location ORIGIN(7) bwcode: MOV bwdat,SD ; loading data does no harm MOV bwadr, SA ;do the command JMP bwcmd ; command determines length bw rd wr:

; clear the multibus interrupt MOV #4, CR MOV SA, QR CMP QR, #slot0 rd mask ; is this a word read req from slot0? ;go to special slot0 patch to get BEQLG get counter 10 ms counter . · ; · . jsr wait3 MOV SD, bwdat ; fast read & get data INT CLR SA ;clear STD BUS reset ; bus window mode interrupt enable/disable code bw interrupts: MOV #4,CR ;clear multibus interrupt MOV bwadr, CR ;enable/disable STD interrupt jmp idle bw intr send: ;send multibus interrupt MOV OR, FO INT MOV OR, OR ;nop ;start up code dacp start: JMP ipc start1 ;load next address into pc ipc start1: MOV #intr clr,SD ;disable ex0 interrupt MOV #clk\_wr\_csr,SA,QR ;on the clock module MOV #init cr,CR ;1 enb. fifin int. & clear ovflow ; disable all interrupts jsr wait4 ;5 prepARE( to clear exl ;set to clear exl ADD #4,QRMOV #intr clr,SD MOV QR, SA MOV #4, lit\_4 ;clear exl ;3 load constant register jsr wait5 MOV QR, SD INT ; and terminate the write ;clk0 counter fetch get counter: MOV clock counter, bwdat ;get the current counter value CLR clock counter ;reset the counter INT CLR SA ; clear STD bus reset and get next intr ; ipc interrupt handing code ex0loc: MOV #intr\_no\_stat ex0,QR,CR ;disable ipc interrupt JMP by intr send ;go to common interrupt service exlloc: ;disable ipc interrupt MOV #intr no stat ex1,QR,CR ;go to common interrupt service JMP bw intr send ;slot a interrupt location ORIGIN(512)

Aug 27 20:15 1985 buswnclk.asd Page 3

## Aug 27 20:15 1985 buswnclk.asd Page 4

;disable ipc interrupt ;go to common interrupt service ;slot b interrupt location ;disable ipc interrupt ;go to common interrupt service MOV #intr no stat0, QR, CR JMP bw\_intr\_send ORIGIN(576) MOV #intr no statl, QR, CR JMP bw\_intr\_send ;go to common interrupt service ;slot c interrupt location ;disable ipc interrupt ;go to common interrupt service ;slot d interrupt location ;disable ipc interrupt ;go to common interrupt service ;slot e interrupt location ;disable ipc interrupt ;go to common interrupt service ;slot f interrupt location ;disable ipc interrupt ;go to common interrupt service ;slot g interrupt location ;disable ipc interrupt ORIGIN(640) MOV #intr no stat2,QR,CR JMP bw intr send ORIGIN(704) MOV #intr\_no\_stat3,QR,CR JMP bw intr send ORIGIN(768) MOV #intr no stat4, QR, CR JMP bw\_intr\_send ORIGIN(832) MOV #intr no stat5, QR, CR JMP bw\_intr\_send ORIGIN(896) ;disable ipc interrupt ;go to common interrupt service MOV #intr no stat6,QR,CR JMP bw intr send ORIGIN(960) ;slot h interrupt location MOV #intr0 clr,SD ;clear clk0 interrupt MOV #clk\_wr\_csr4,SA INC clock\_counter INC clock\_counter ;add one to elapsed time counter CMP clock\_counter,#0x004000 ;is counter getting full? NOP ; if not reenable intr ; complete intr clr xfer ; load interrupt I.D. BLEQUW toidle MOV QR, SD MOV #intr no stat7,QR JMP bw intr send ;go to common interrupt service toidle: MOV QR, SD ;complete intr clr xfer JMP idle psect wait5:: mov qr,qr wait4:: mov qr,qr wait3:: mov qr,qr wait2:: mov qr,qr waitl:: rts psect quit5:: mov qr,qr quit4:: mov qr,qr quit3:: mov qr,qr quit2:: mov qr,qr quitl:: int clr sd END MODULE ;The following constants are defined for use by all IPC ucode. enable\_intr==0xc0 ;enable selected interrupt in CR disable\_intr==0x80 ;disable selected interrupt in CR io\_rd\_B==0x2d0000 ;read STDL onto low and mid byte of inbus io\_rd\_W==0x2e0000 ;read word to inbus

mem rd B==0x0d0000; read STDL onto low and mid byte of inbus mem rd W==0x0e0000 ;read word to inbus io wr H==0x380000 ;write mid byte onto STDL & STDH io wr L = 0x350000;write low byte onto STDL & STDH io wr W==0x3e0000 ;write word to STDL & STDH And a second sec mem wr H==0x180000 ;write mid byte onto STDL & STDH mem\_wr\_L==0x150000 ;write low byte onto STDL & STDH mem wr W==0xle0000 ;write word to STDL & STDH fast std==0x400000;fast write mode bit rd\_byte==0x800000 ;multibus byte read rd\_word==0x900000 ;multibus word read rd\_long==0xb00000 ;multibus longword read wr\_byte==0xc00000 ;multibus byte write wr word==0xd00000 ;multibus word write wr long==0xf00000 ;multibus longword write loop back==0x200000;loop back ipc intr==0x600000 ;multibus interrupt

#### Aug 26 16:06 1985 clockdemo.c Page 1

```

/*

**

This is a demonstration of the use of the 10 ms sidereal time

**

counter in the DA/CP. The DA/CP buswindow code has been modified to

**

intercept interrupts from the clock module and increment a counter

**

in the DA/CP on each interrupt. This counter may be read from a

**

program in the host computer. The DA/CP counter is only 15 bits wide

so when it is read it is reset to zero, and the host program must

**

**

keep its own elapsed time counter to which each reading is added.

**

If the DA/CP counter is not read after about 2min 40sec the DA/CP

**

will interrupt the host with an AST to a service routine which is

**

expected to read the DA/CP counter and update its own counter.

**

The program is in file /users/staff/rick/Asdfiles/clockdemo.c.

**

Until the DA/CP code is permanently modified you will have to load

**

the patched code by running the shell script

**

/users/staff/rick/Asdfiles/ld

**

This will load only the clock and buswindow code so the other DA/CP

**

modules will be inoperative. To compile this code use

**

cc clockdemo.c -lmr -lm

**

**

R.Fisher 26 Aug. 1985

*/

#include <fcntl.h>

#include "/usr/include/mr.h"

main()

int ext int = 0;

/* assume internal clock time generator */

int lst;

start_clock(ext_int); /* set up internal clock rate or route external

10 ms clock pulses to STD interrupt line */

reset clock();

/* zero elapsed time counter (ten ms counter)

and enable clock interrupts */

while(1)

lst = sidereal_time(); /* gets current elapsed time in 10 ms unite */

display(lst);

/* demonstration routine to show elapsed time */

sleep(10);

}

}

/*

Return the current elapsed sidereal time

**

*/

sidereal time()

short dacp counter;

```

Aug

Aug 26 16:06 1985 clockdemo.c Page 2

```

/* read the dacp counter and reset it */

mrwnrd(clockpn, 30, 2, & dacp counter);

return(ten ms counter = ten ms counter+dacp counter);

}

/*

This routine displays elapsed time in hh:mm:ss.ss format

**

*/

display(lst)

int 1st;

int h,m,s,fl,f2;

fl = (lst/10) % 10;

f2 = 1st \% 10;

s = lst/100;

m = (s/60) % 60;

h = (s/3600)  % 24;

s = s % 60;

printf("Sidereal time = %d:%d:%d.%d%d\n",h,m,s,f1,f2);

/*

**

Updates the 10ms elapsed time counter if the dacp counter is getting

**

full. This can happen if the time has not been read for over 2m40s.

**

When the dacp counter gets half full it interrupts the host computer

**

with and AST to this routine.

*/

inc ten ms count()

short dacp counter;

/* read the dacp counter and reset it */

mrwnrd(clockpn, 30, 2, & dacp counter);

ten ms counter = ten ms counter+dacp counter;

/* re-enable AST interrupt from dacp */

mrwnion(clockpn);

}

**

Set elapsed time counter to zero and start clock

*/

reset clock()

short dacp counter;

ten ms counter = 0;

mrwnrd(clockpn,30,2,&dacp_counter); /* zero dacp_counter */

/* enable dacp interrupt to cpu */

mrwnion(clockpn);

/* enable clock interrupt */

mrclkintgat(clockpn, 1);

}

```

Aug 26 16:06 1985 clockdemo.c Page 3

/\*

\*\* This routine opens the clock path and sets up the internal clock parameters

\*\* or routes the external pulses.

\*/

start\_clock(ext\_int)

int ext int; /\* 0 = internal clock \*/ /\* allow read only to clock \*/ int read write = 1; int nearest = 0;/\* pick closest clock frequency to one specified \*/ /\* use square clock waveform \*/ int square = 4;/\* waveform begins low \*/ int low = 0; /\* divisor for external pulse rate \*/ int ndiv = 1; /\* arm the external clock \*/ int armsw = 1; /\* number of clocks to be armed \*/ int nclks  $=^{\beta}$ l; /\* array containing clock path nos. \*/ int pnarray[1]; /\* number of STD address ranges \*/ int naddrs = 1; int adrsarray[3]; /\* AST priority of service routine \*/ int intpri = 127; double trigfreg = 100.\*366.25/365.25; /\* internal clock sidereal rate in Hz \*/ /\* internal clock rate actually set \*/ double freturn; double wreturn; /\* internal pulse width actually set \*/ adrsarray[0] = 0; /\* dacp clock is treated as an I/O address \*/ /\* address start \*/ adrsarray[1] = 30; /\* address end \*/ adrsarray[2] = 30;mropen(&clockpn,"/dev/dacp0/clk0",read\_write);/\* open clock path \*/ /\* disable clock interrupts \*/ mrclkintgat(clockpn,0); if(!ext int) { /\* set up internal clock parameters \*/ mrclkl(clockpn,nearest,trigfreq,&freturn,square,0.0,&wreturn,low); /\* start the clock generator \*/ pnarray[0] = clockpn; mrclkarm(nclks,pnarray); printf("Clock freq. requested = %f Hz\n", trigfreg); printf(" actually set = %f Hz\n", freturn); ł else /\* send external 10ms pulses directly to STD bus \*/ mrclkbyps(clockpn,ndiv,armsw); } /\* open protected window to slot0 \*/

```

mrwnopn(clockpn,naddrs,adrsarray,inc_ten_ms_count,intpri);

printf("Clock started\n");

```