# NATIONAL RADIO ASTRONOMY OBSERVATORY Green Bank, West Virginia

Electronics Division Internal Report No. 80

AUTOCORRELATION RECEIVER MODEL II: DIGITAL SYSTEM

Arthur M. Shalloway

September 1968

NUMBER OF COPIES: 35

# PREFACE

This report is for maintenance personnel on the digital system of the NRAO Autocorrelation Receiver Model II. The system is of such complexity that a "build-up" type of approach is taken here. A description is given of a simplified block diagram, followed by a description of a more detailed block diagram; and then a thorough description is provided using the actual logic diagrams.

A complete coverage of every detail is not possible. However, an engineer or technician with a good knowledge of digital logic should be able to fill in the fine details by the use of the logic and timing diagrams.

Wherever it was considered helpful for quick reference, information has been restated in tabular form. Once this report has been read, most questions which arise while servicing can be answered by use of one of the tables.

To get a familiarity with the operation of the entire system, it is suggested that the NRAO Electronics Division Internal Report No. 75 be read. In addition to the data and drawings contained in this report, the following items too bulky to be incorporated in this report - are available:

- 1. Wiring list of large card file.

- 2. Wiring list of small card file.

- 3. Cable wiring list.

- 4. Load and location chart.

- 5. Spare module and location tabulation.

- 6. Instruction manuals for core memory, power supplies, level converter and relay driver cards, and sensitive relays.

These items can be found in the Autocorrelation Receiver Service Center Cabinet which should always accompany the two receiver racks. Item 4 above is especially helpful in locating the origin and destination of any signal. All of the above are needed for any logic changes that would be contemplated.

**(i)**

Thanks are due to many people for help in completion of this project. In particular, I express appreciation to the following:

Sander Weinreb for developing the digital autocorrelator theory;

Gart Westerhout of the University of Maryland for initiating the drive for a large autocorrelator;

Robert Mauzy for his excellent analog design, especially the clippers, samplers, and clock emitter followers which feed the digital system;

Raymond Hunter, who did every job imaginable, from wiring to design of Omni Comb units, through the entire project;

Wilbur Andrews and Jack Cochran for various mechanical and electrical designs and construction; and

Henry Light for all the drafting and logic checks.

I thank all of these people for going along with me and not doing it the WRONG WAY nor the RIGHT WAY, but the SHALL-O-WAY.

FIG. 16

# AUTOCORRELATION RECEIVER MODEL II DIGITAL SYSTEM

# TABLE OF CONTENTS

# Page

| Prefa       | ce                                                                                                                                                                  | i                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| I.<br>II.   | IntroductionOperation                                                                                                                                               | 1<br>1                                             |

| ]           | Dump Period         Switching Rates         Switching Rates         Noise Tube Duty Cycle         Blanking Time         Display         Testing                     | 5<br>5<br>7<br>7                                   |

| III.        | Block Diagram Description                                                                                                                                           | 9                                                  |

| IV.         | Descriptive Terminology                                                                                                                                             | 14                                                 |

|             | <ul> <li>A. Location Terminology</li> <li>B. Identification Terminology</li> <li>C. Timing Chart Terminology</li> </ul>                                             | 17<br>20                                           |

| <b>V.</b> 3 | Logic Description                                                                                                                                                   | 20                                                 |

|             | A. Location Code<br>B. Synchronous System<br>C. 20 MHz Clock<br>D. Sampling Rate Generator<br>E. Sampler<br>F. Correlator<br>G. Counter<br>H. Shift Register Memory | 21<br>22<br>24<br>25<br>27<br>27<br>30<br>33<br>33 |

|             | <ol> <li>Switching Signals</li> <li>Counter &amp; SRM Control</li> <li>Address Registers &amp; Controls</li> <li>Miscellaneous Controls</li> </ol>                  | 34<br>35                                           |

| ]           | L. Display                                                                                                                                                          | 43                                                 |

|             | dix I - List of Control Signals                                                                                                                                     |                                                    |

|             | dix II - Control Logic Numbering Guide                                                                                                                              |                                                    |

|             | dix III - Components List                                                                                                                                           |                                                    |

| Index-      |                                                                                                                                                                     | 54                                                 |

# LIST OF FIGURES

|     |                                                                     | Page |

|-----|---------------------------------------------------------------------|------|

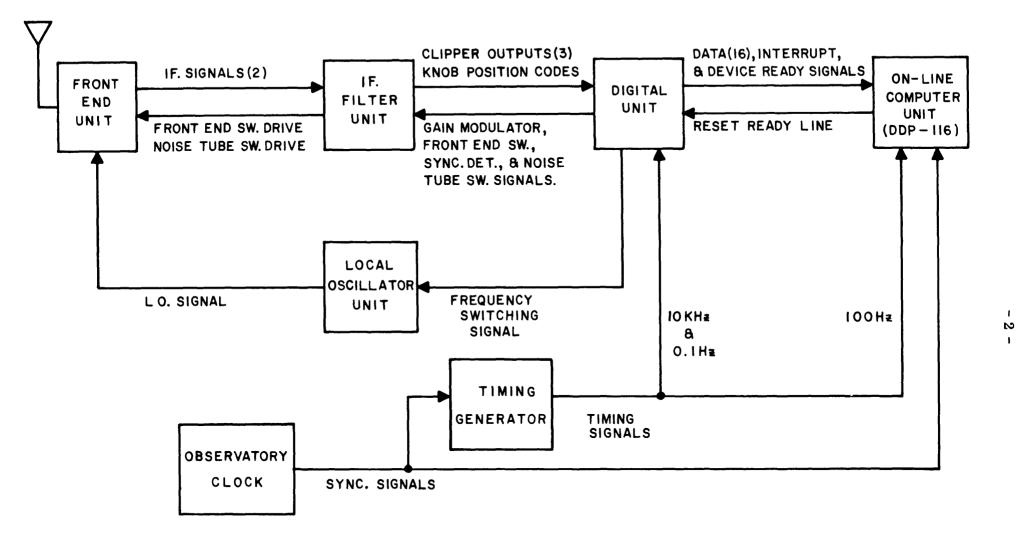

| 1.  | System Block Diagram                                                | 2    |

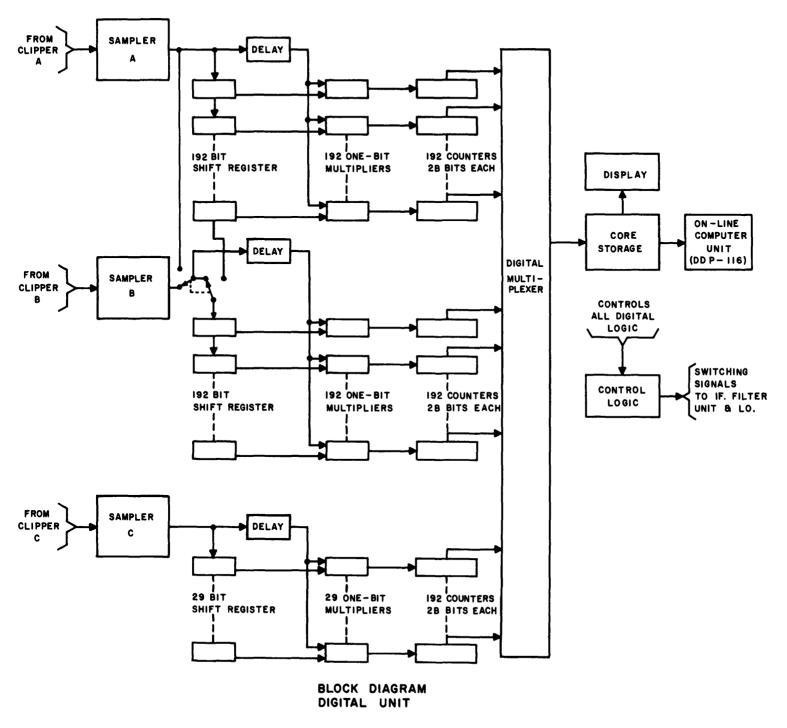

| 2.  | Block Diagram Digital Unit                                          | 3    |

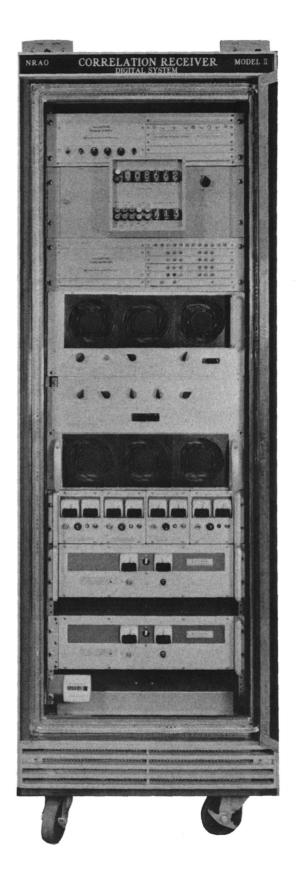

| 3.  | Digital Rack - Door Open & Closed                                   | 6    |

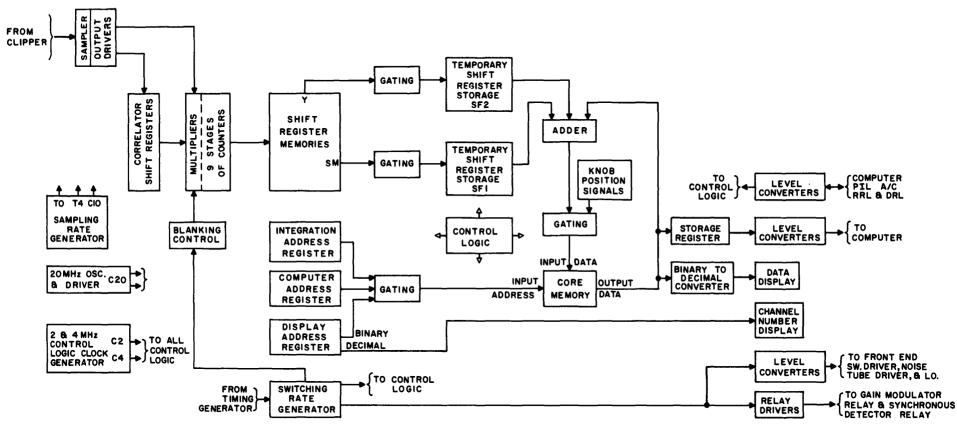

| 4.  | Detailed Block Diagram                                              | 10   |

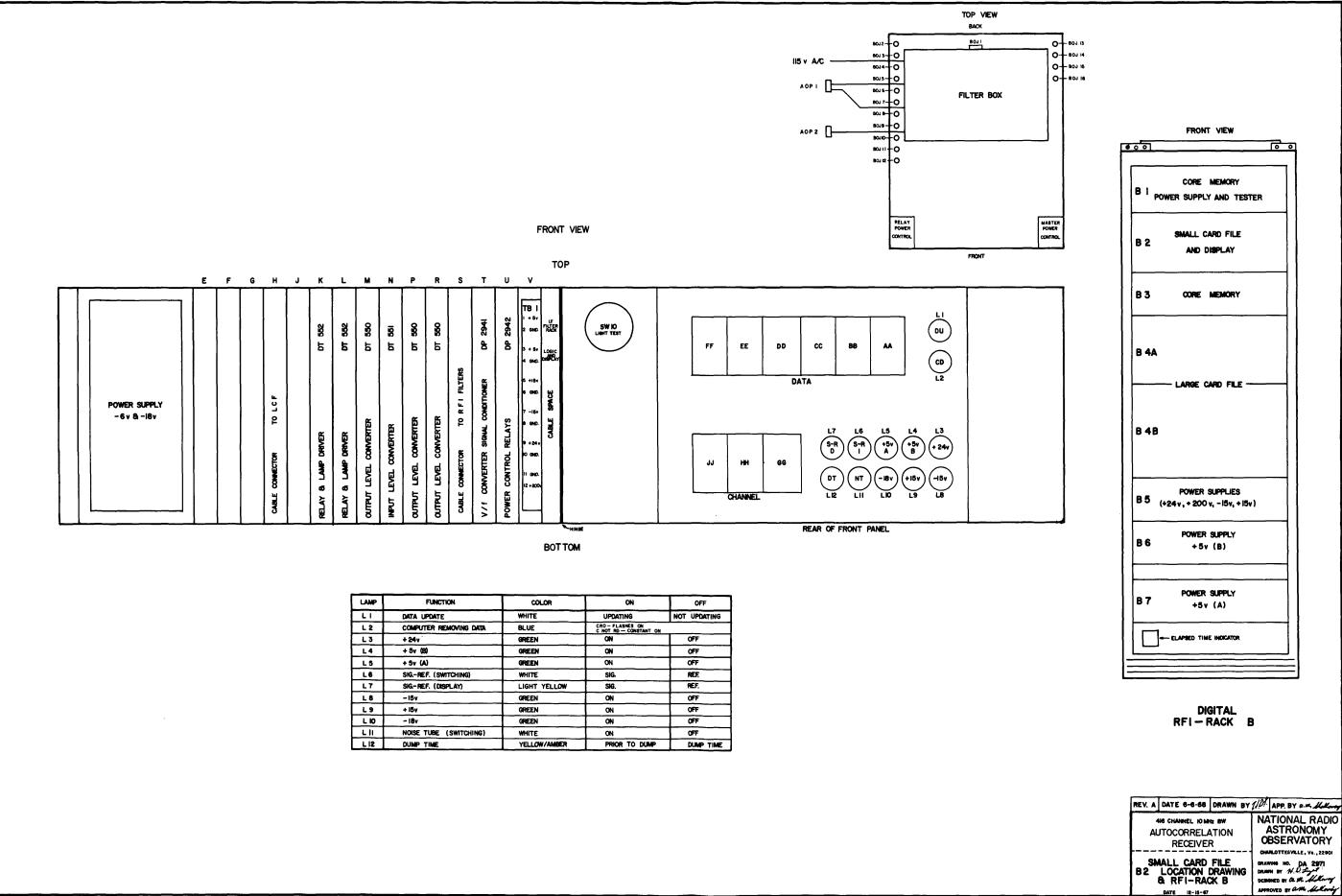

| 5.  | Location Drawing, SCF & Rack - NRAO #DA-2971                        | 15   |

| 6.  | Location Drawing, LCF - NRAO #DA-2970                               | 16   |

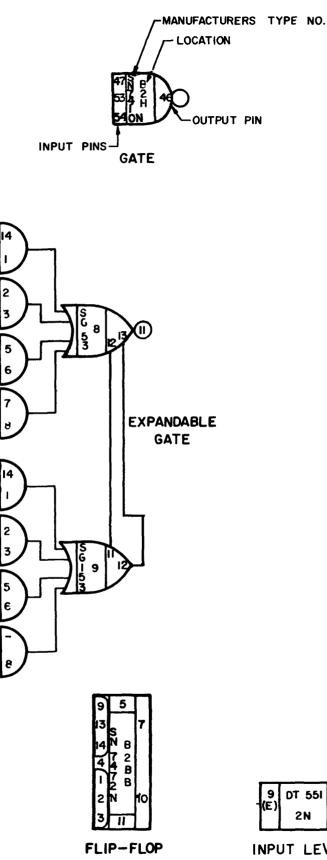

| 7.  | Logic Symbols                                                       | 18   |

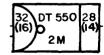

| 8.  | 20 MHz Clock - Emitter Followers                                    | 23   |

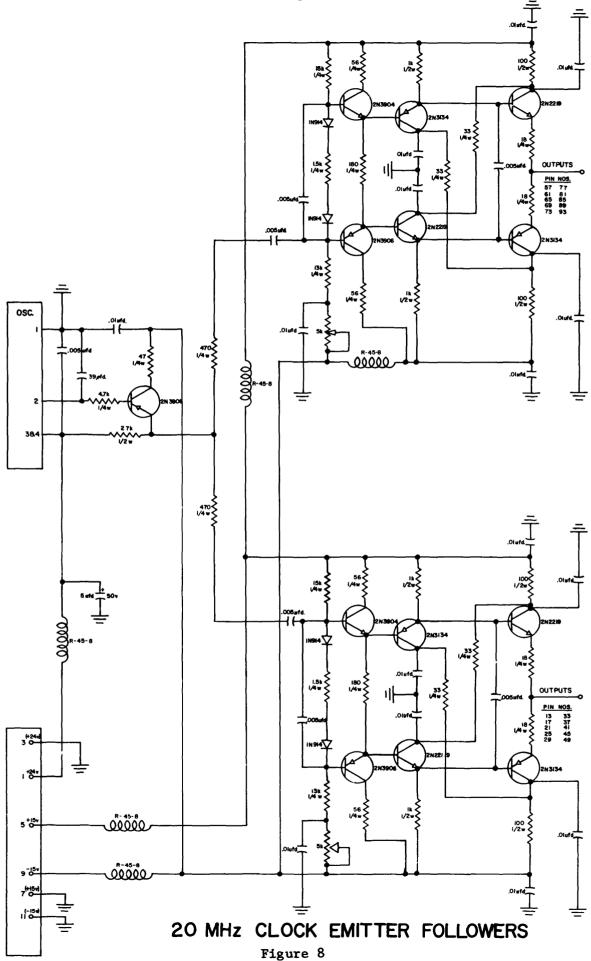

| 9.  | Data Flow - Shift Register Memory to Core Memory                    | 31   |

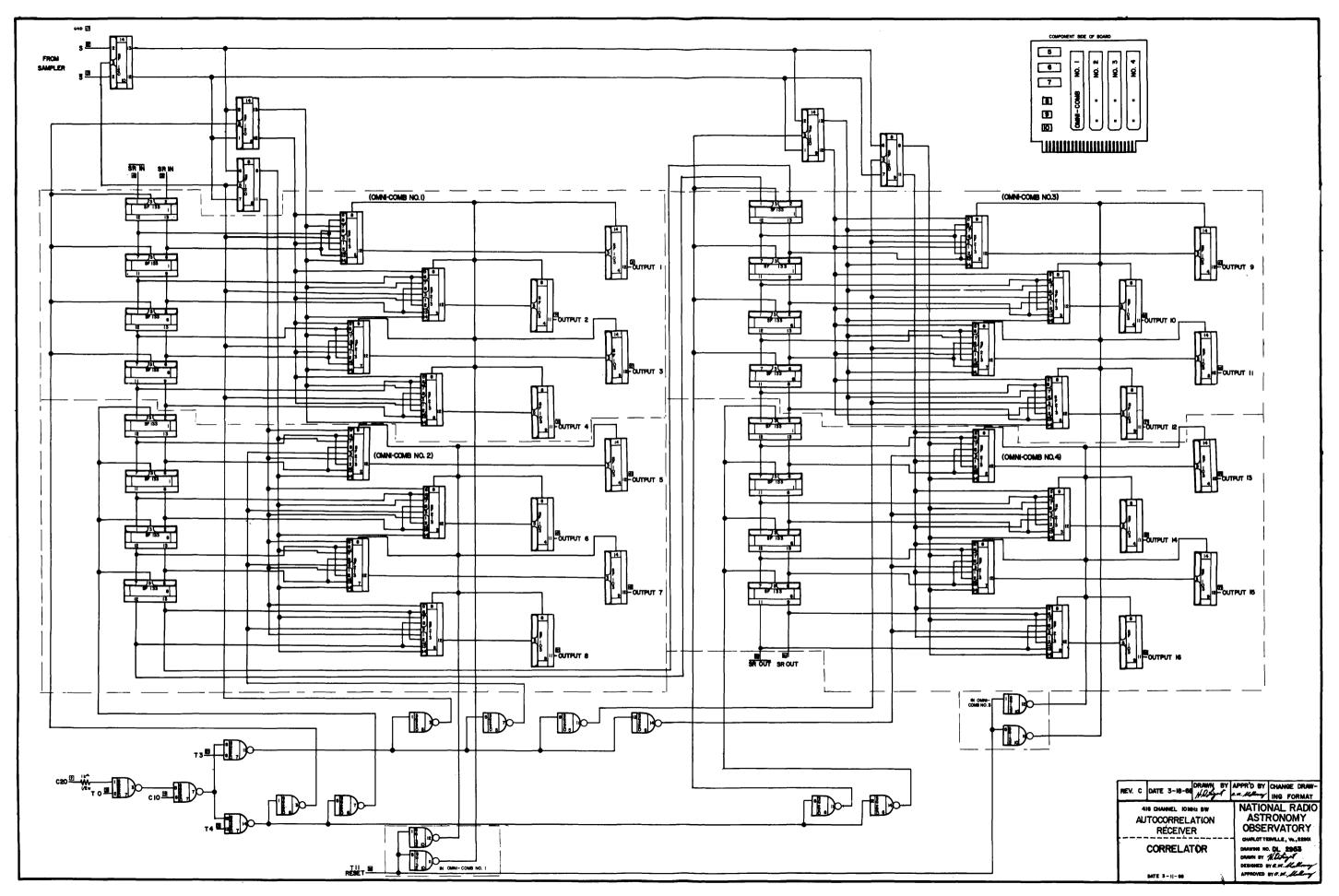

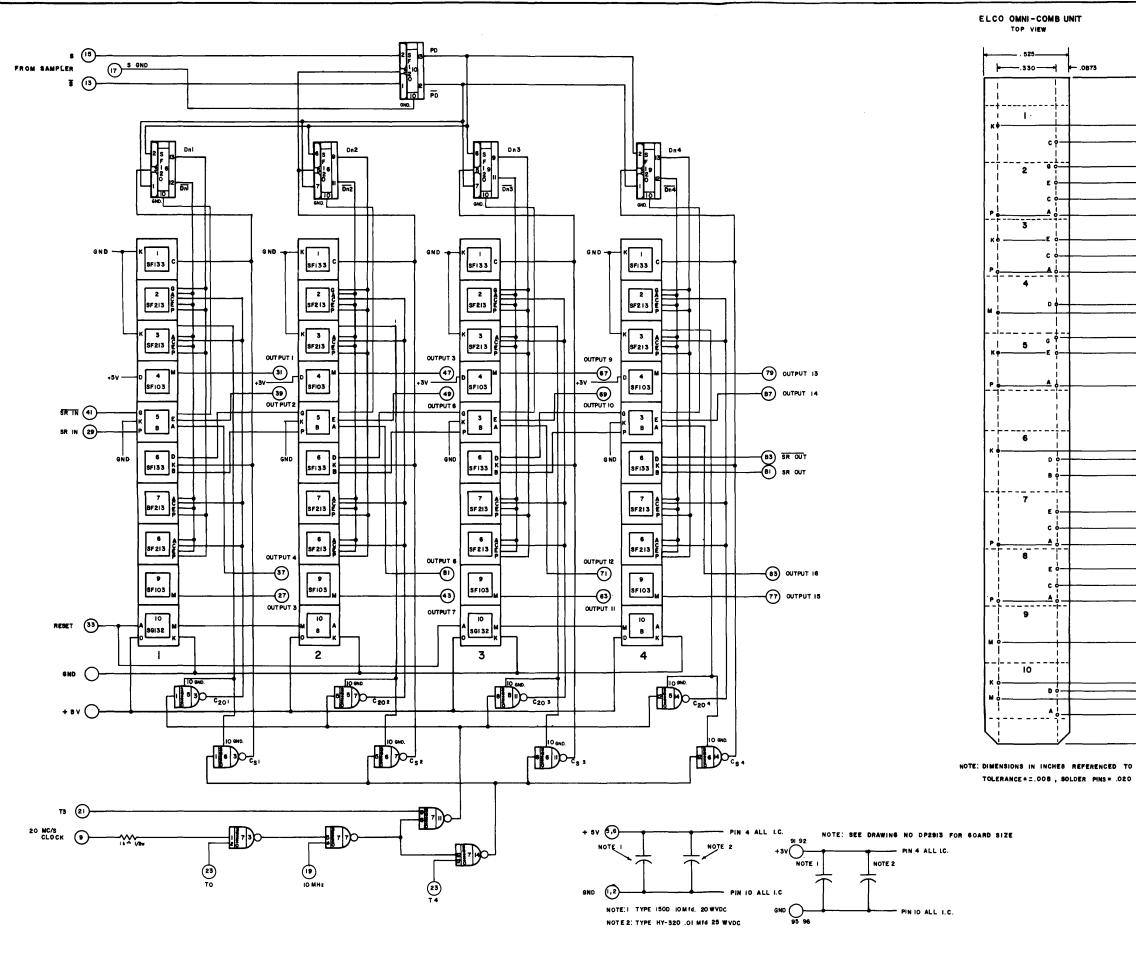

| 10. | Correlator Board Logic - NRAO #DL-2953                              | 59   |

| 11. | Correlator Board Layout - NRAO #DP-2915                             | 60   |

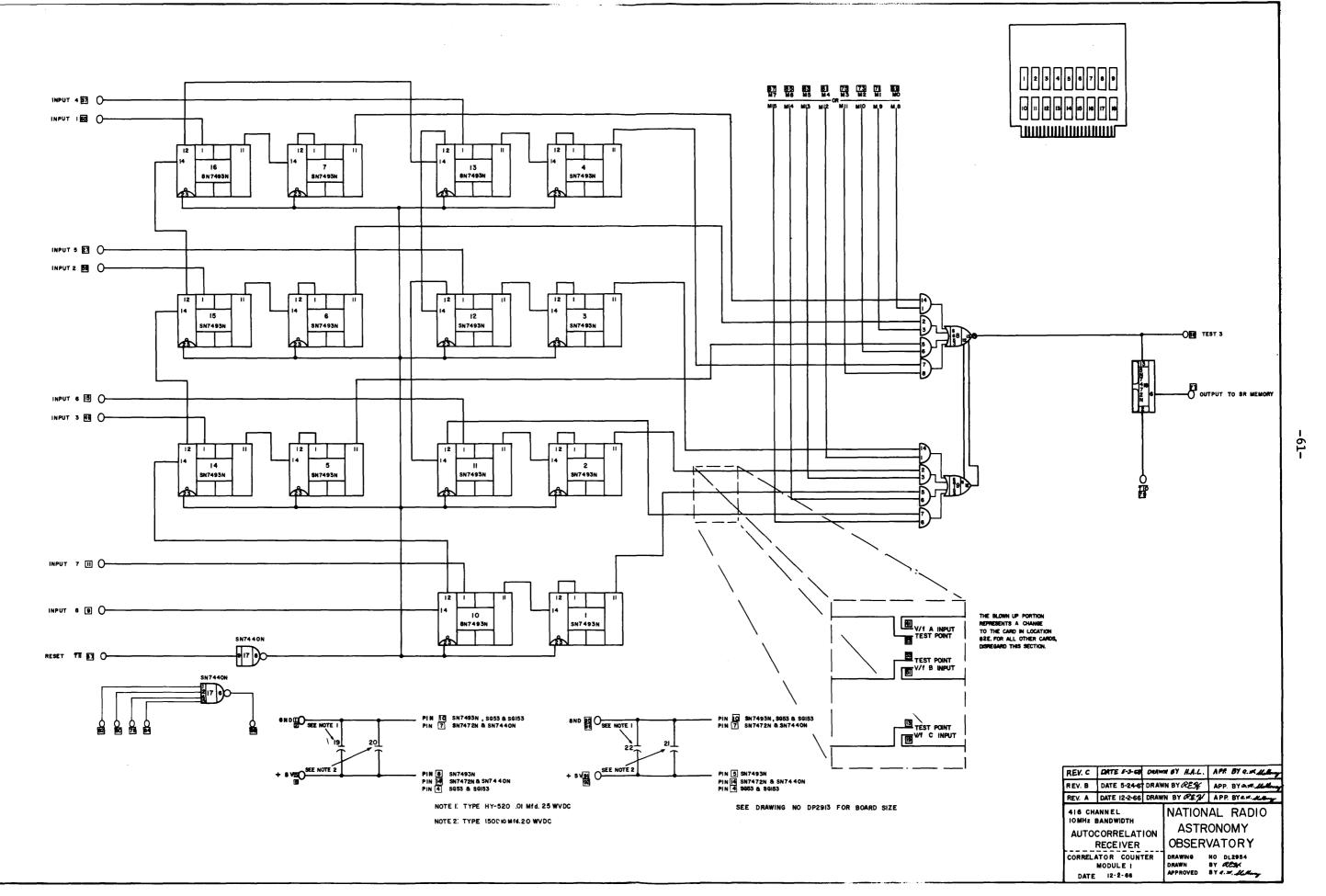

| 12. | Counter Board Logic & Layout - NRAO #DL-2954                        | 61   |

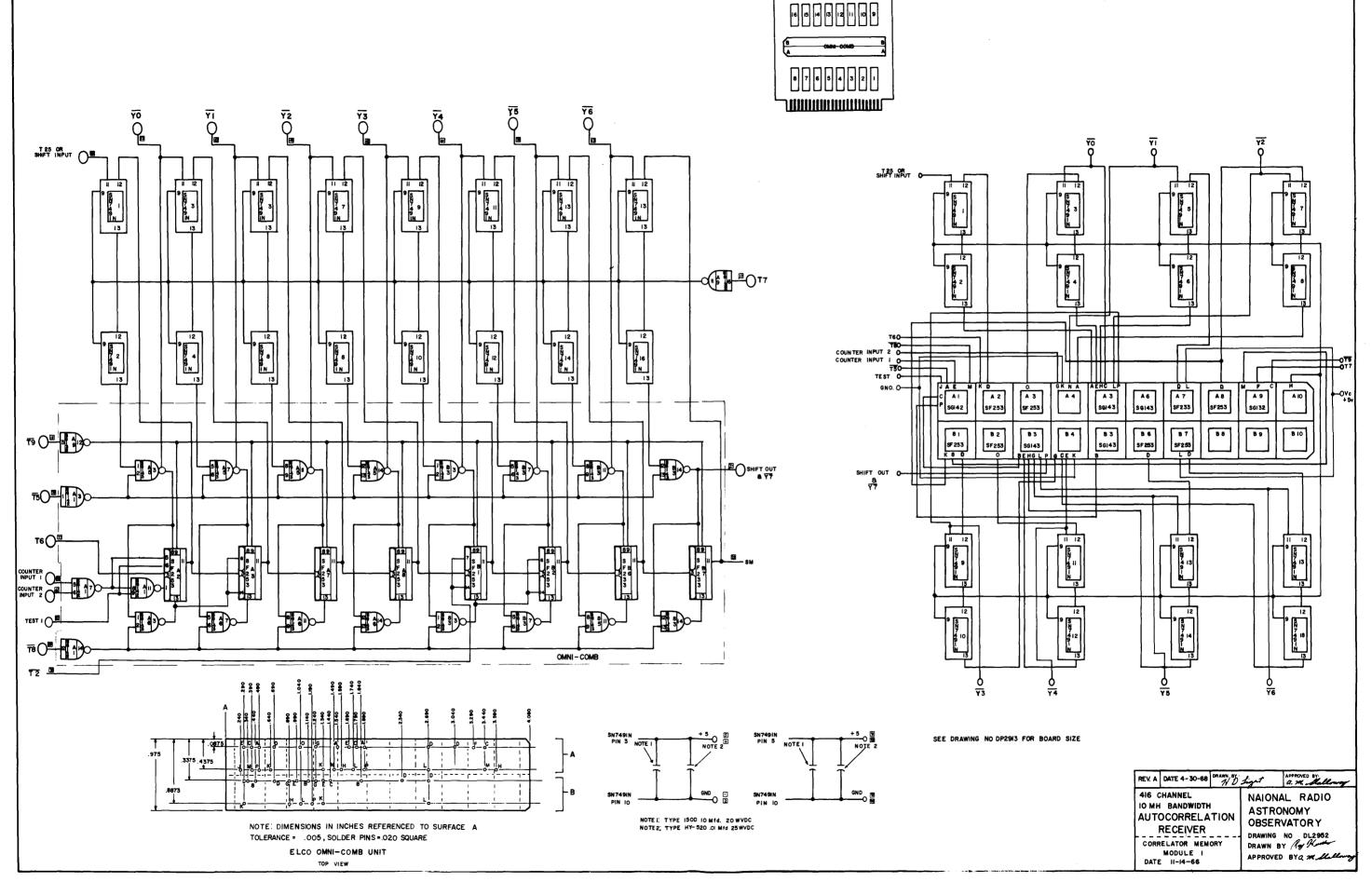

| 13. | Shift Register Memory Logic & Layout - NRAO #DL-2952                | 62   |

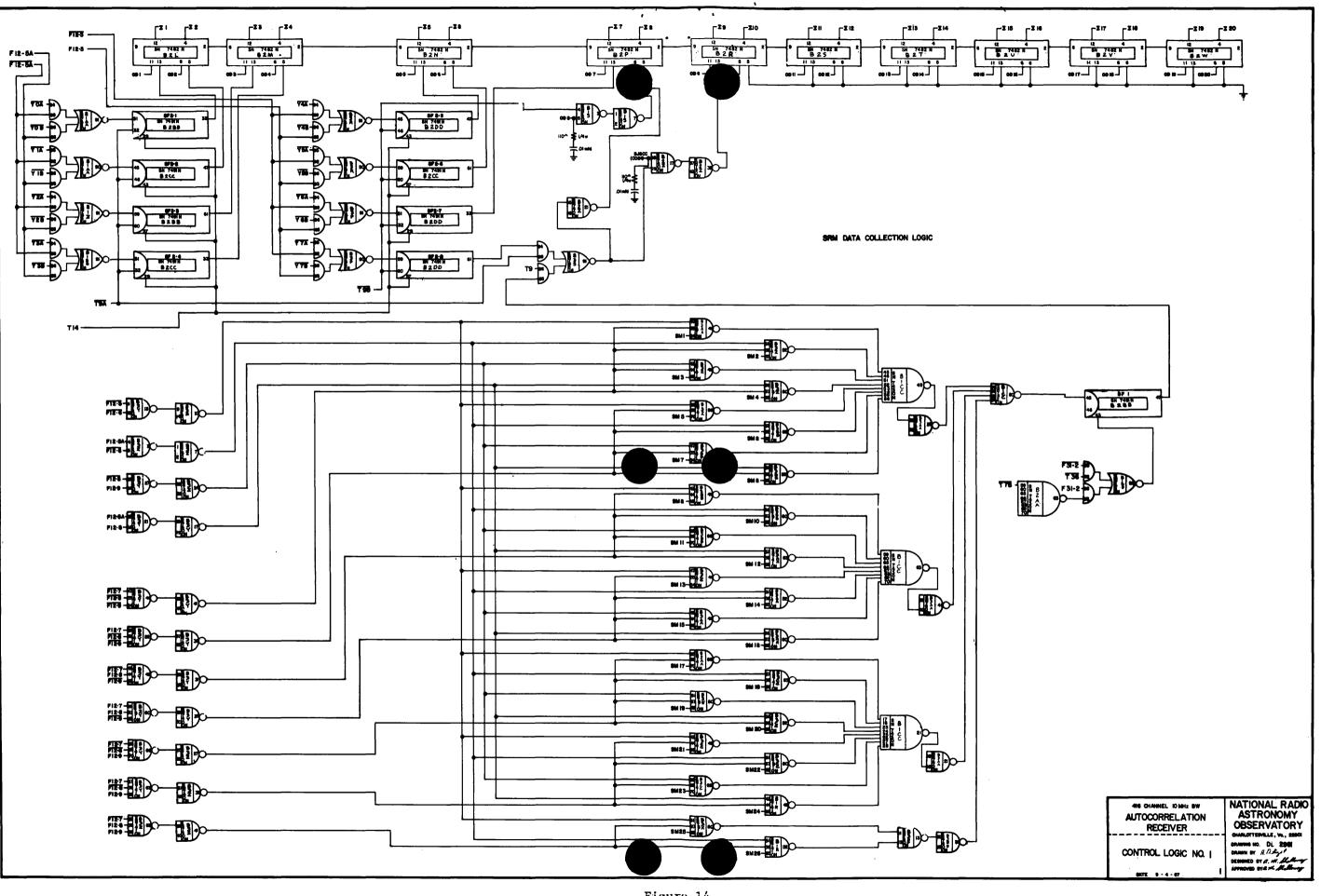

| 14. | Control Logic No. 1 - NRAO #DL-2961                                 | 63   |

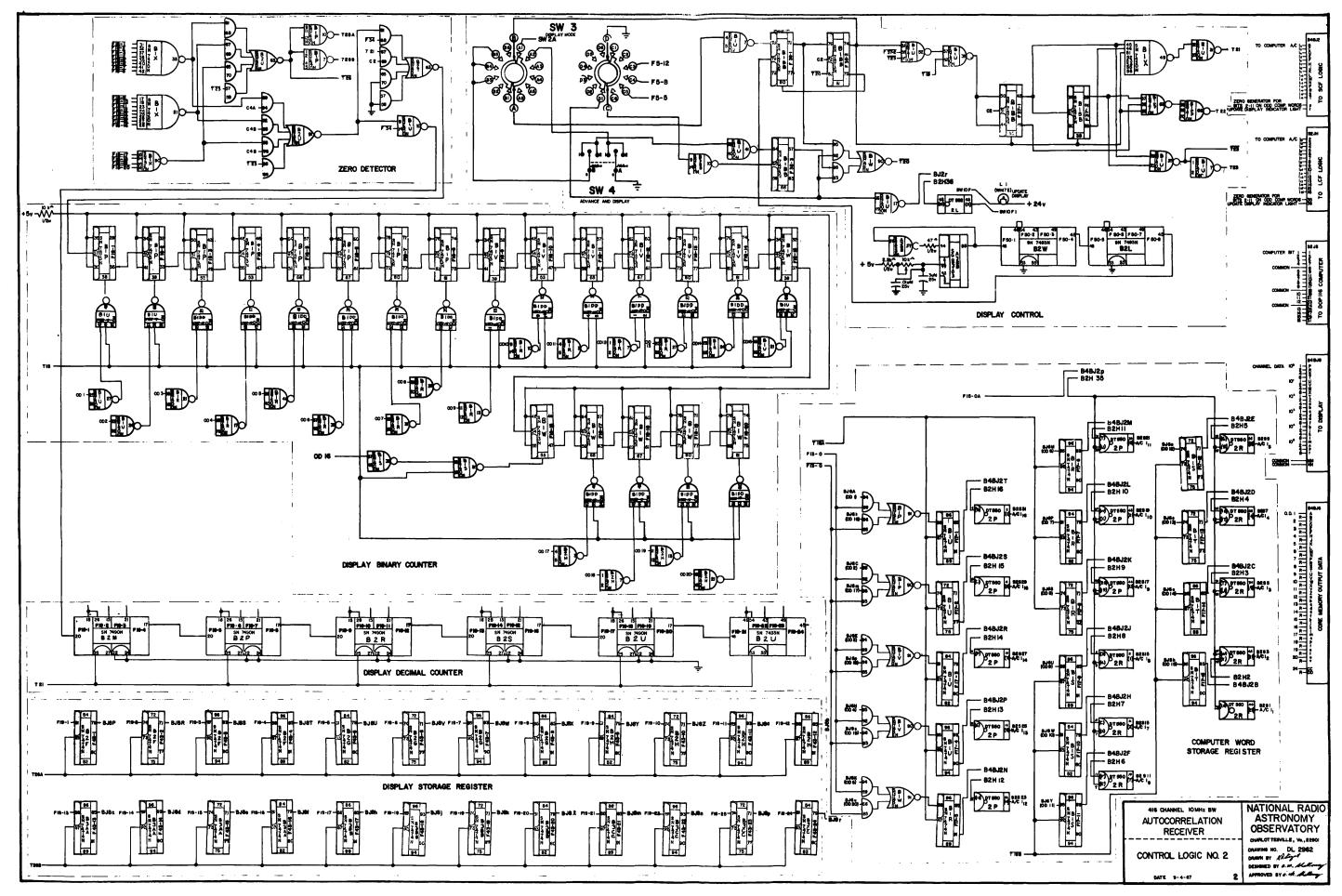

| 15. | Control Logic No. 2 - NRAO #DL-2962                                 | 64   |

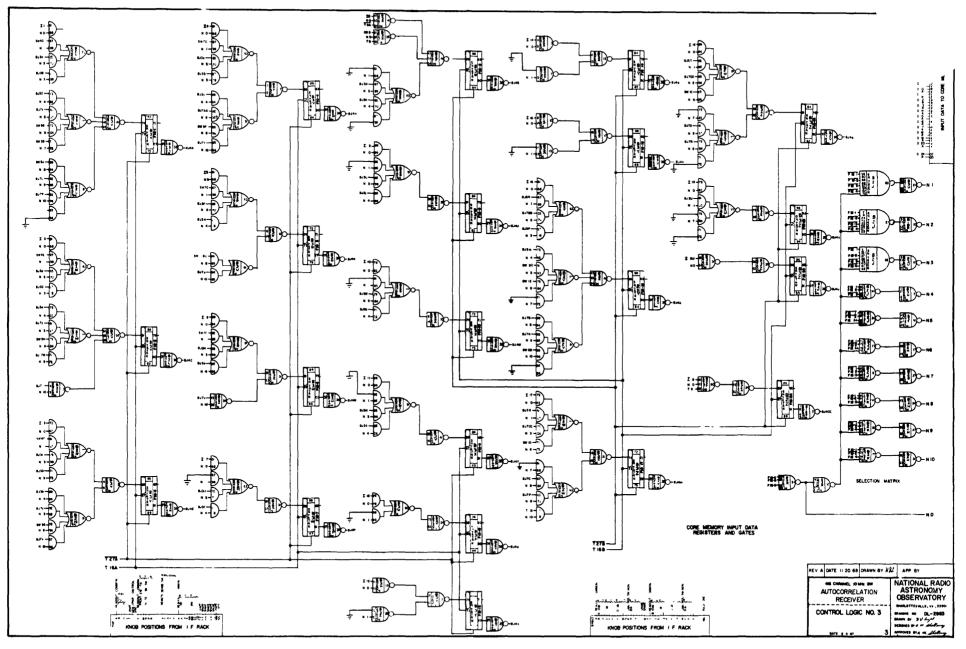

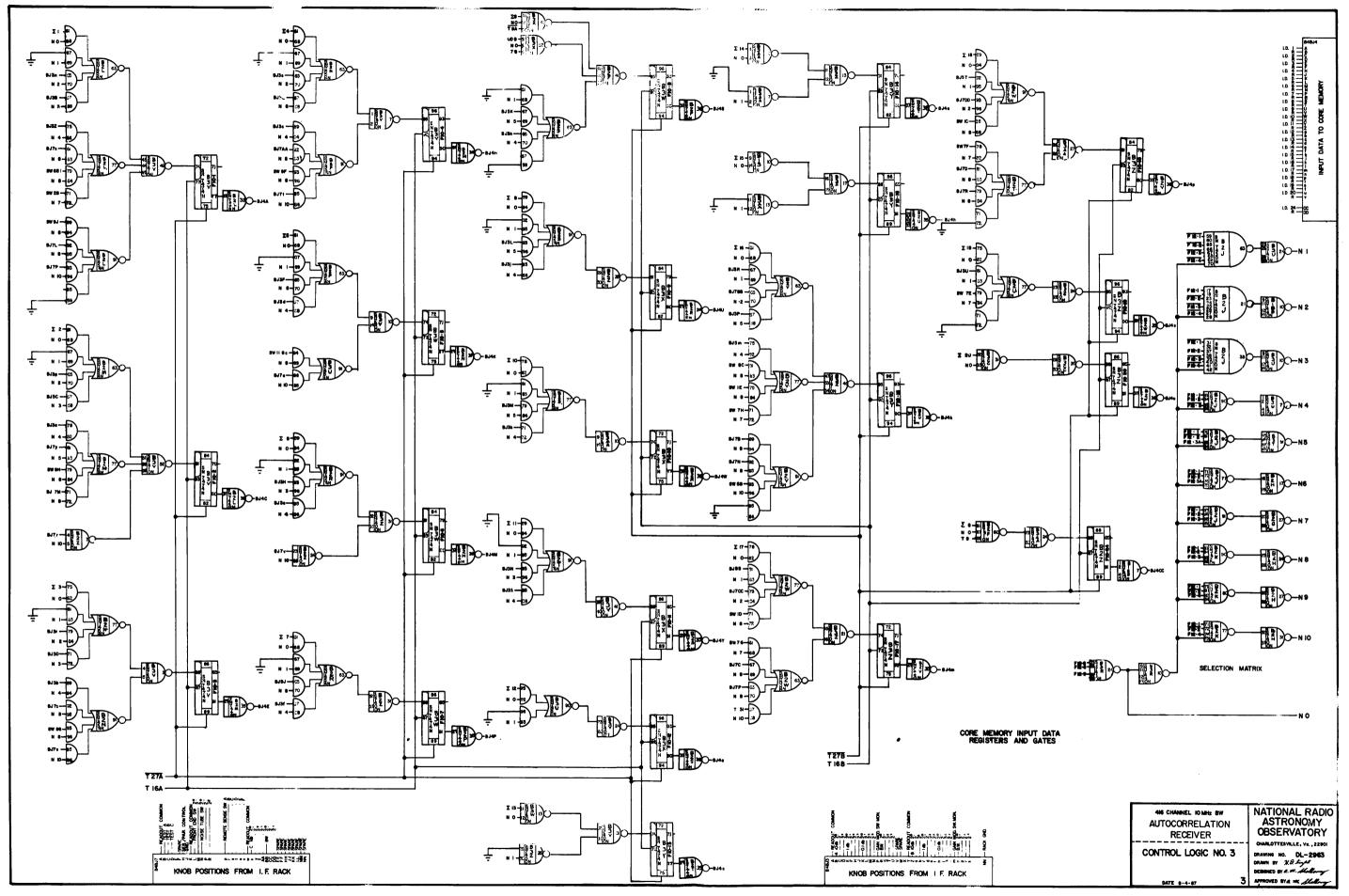

| 16. | Control Logic No. 3 - NRAO #DL-2963                                 | 65   |

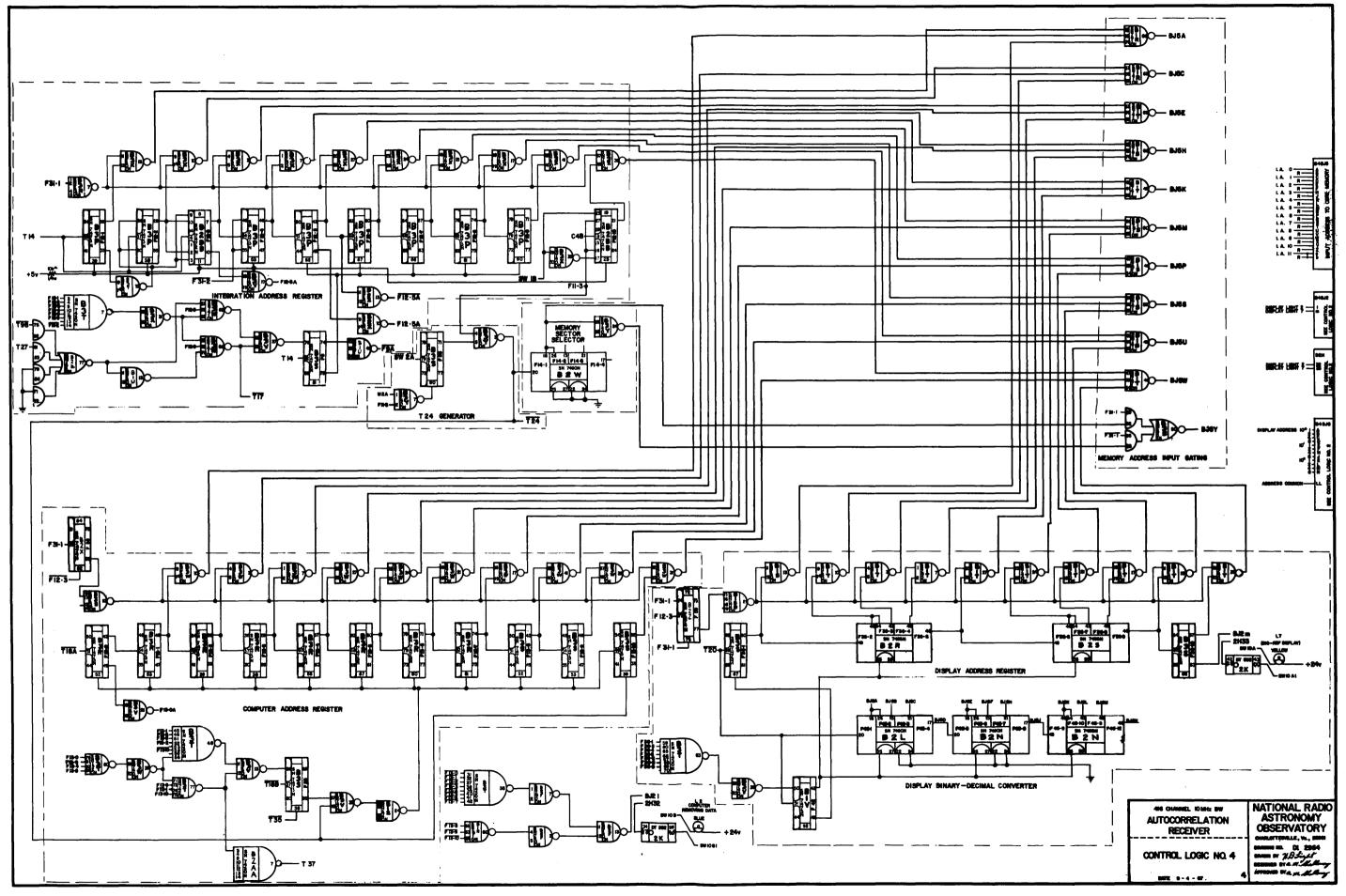

| 17. | Control Logic No. 4 - NRAO #DL-2964                                 | 66   |

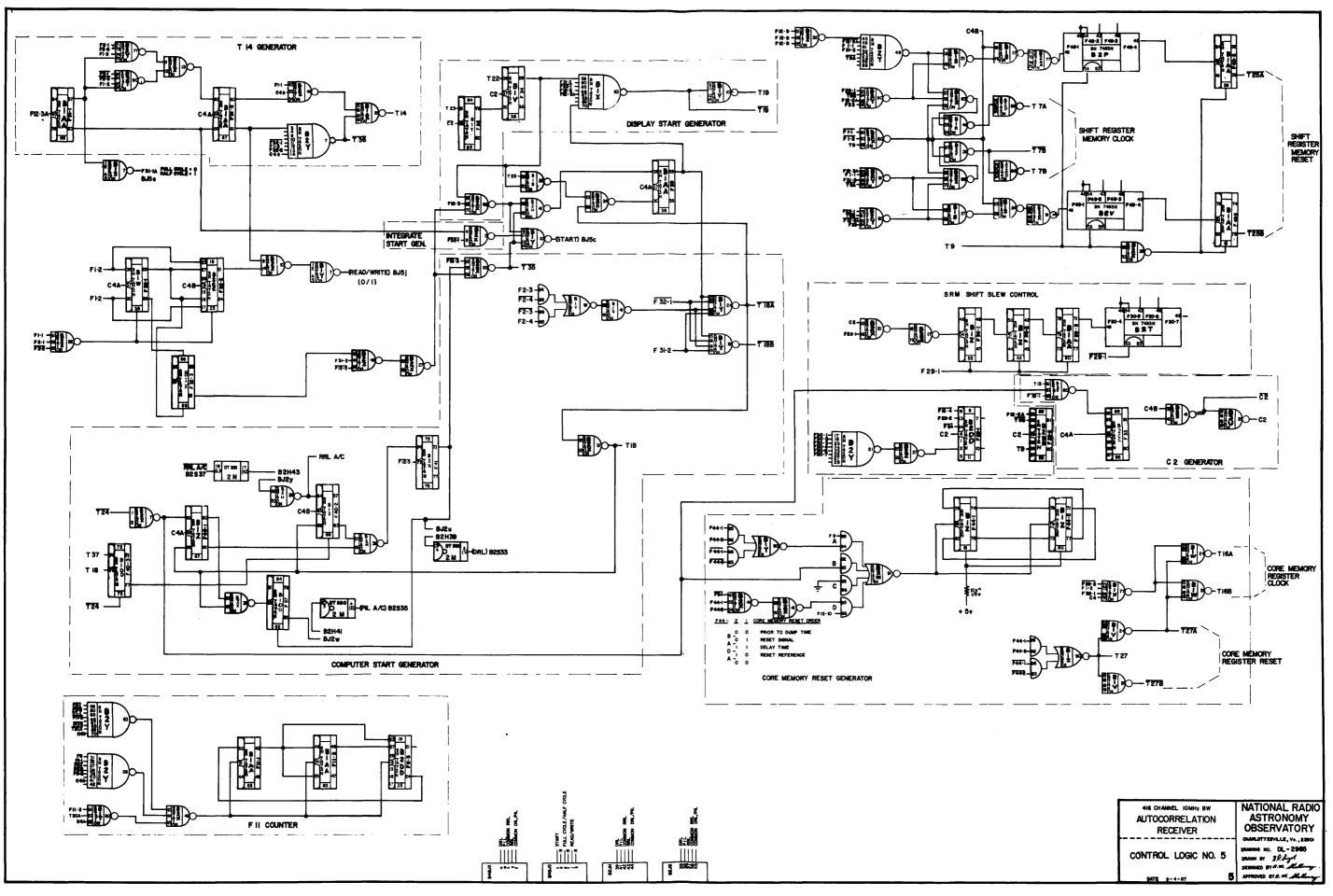

| 18. | Control Logic No. 5 - NRAO #DL-2965                                 | 67   |

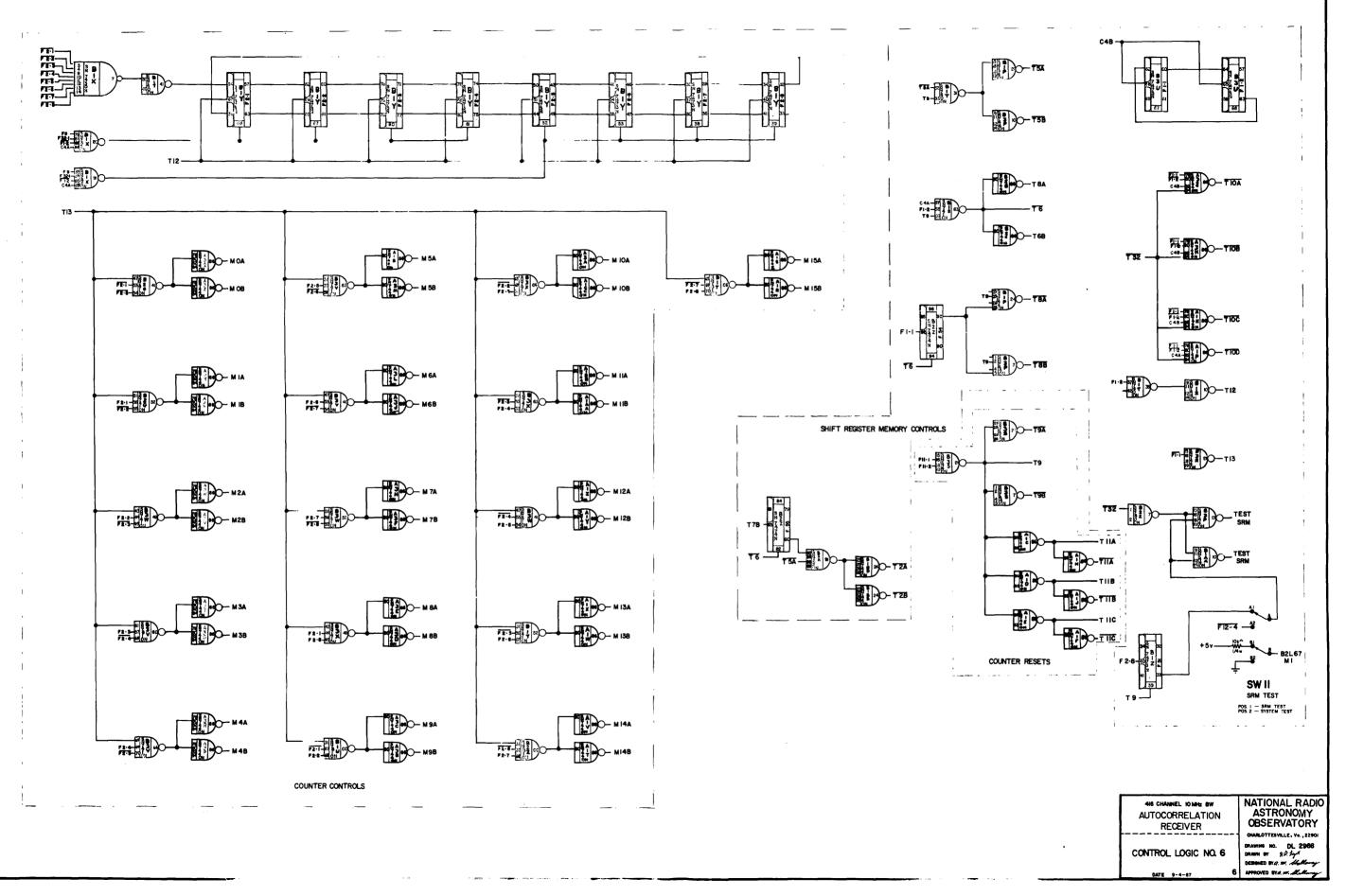

| 19. | Control Logic No. 6 - NRAO #DL-2966                                 | 68   |

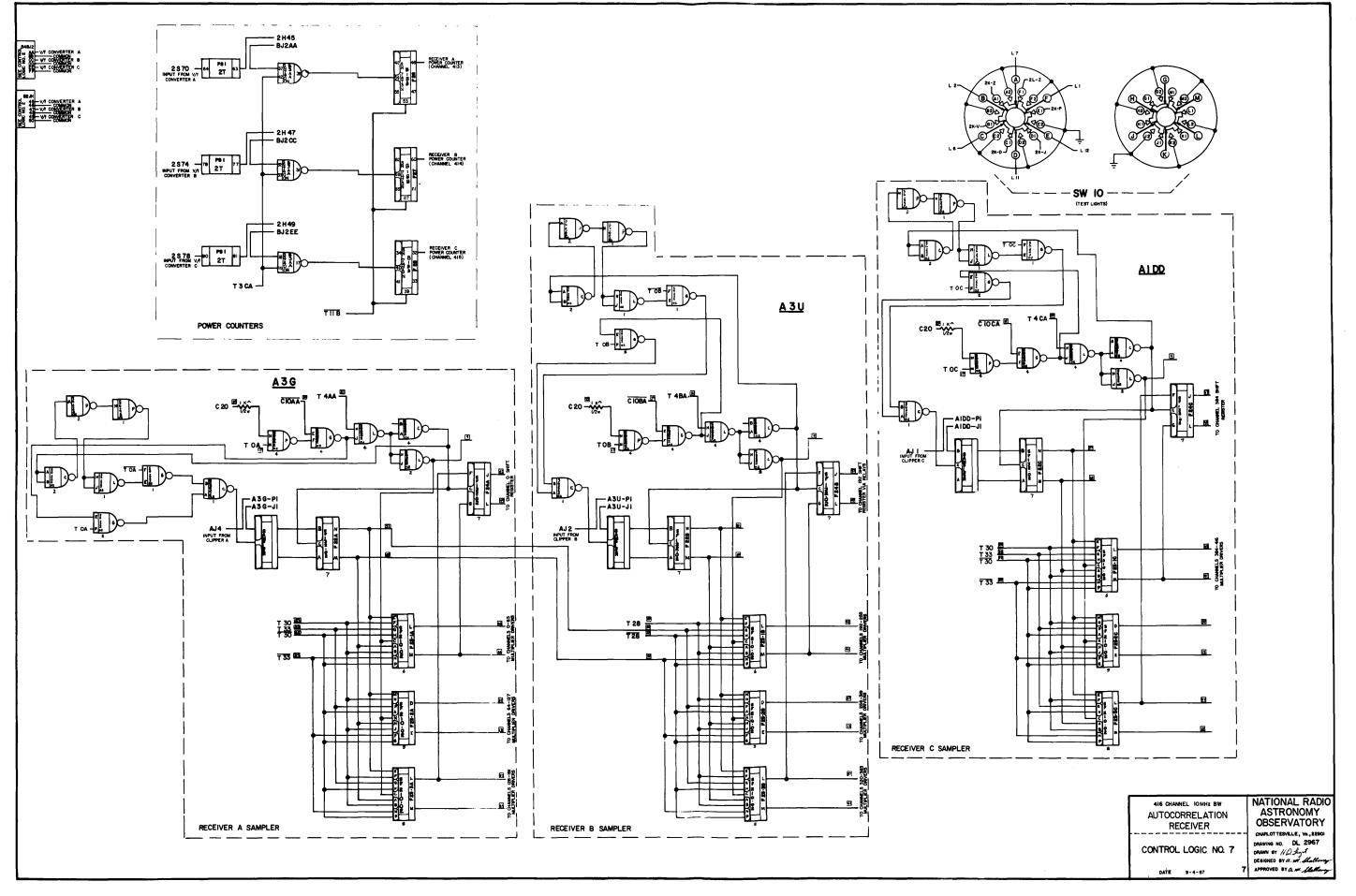

| 20. | Control Logic No. 7 - NRAO #DL-2967                                 | 69   |

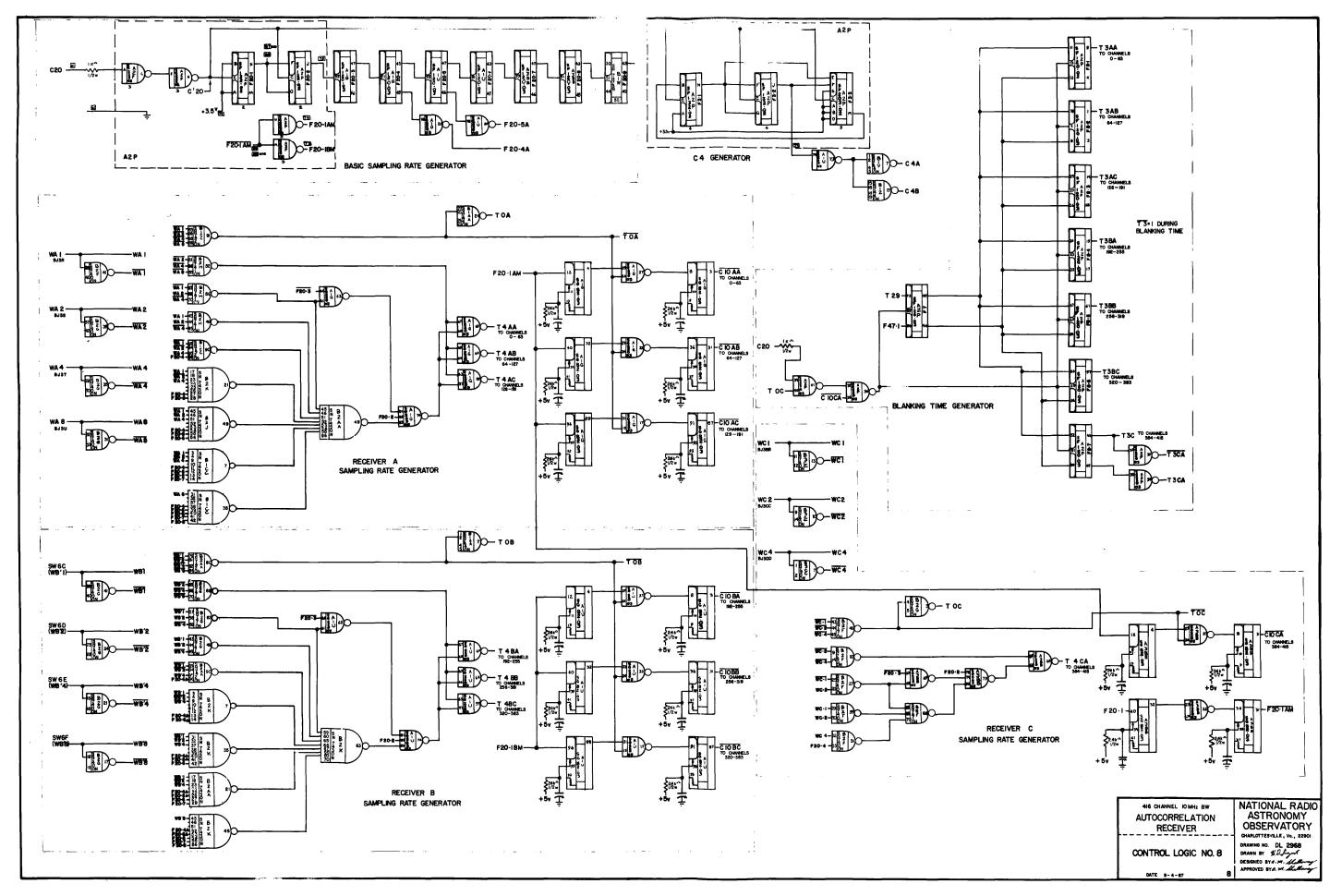

| 21. | Control Logic No. 8 - NRAO #DL-2968                                 | 70   |

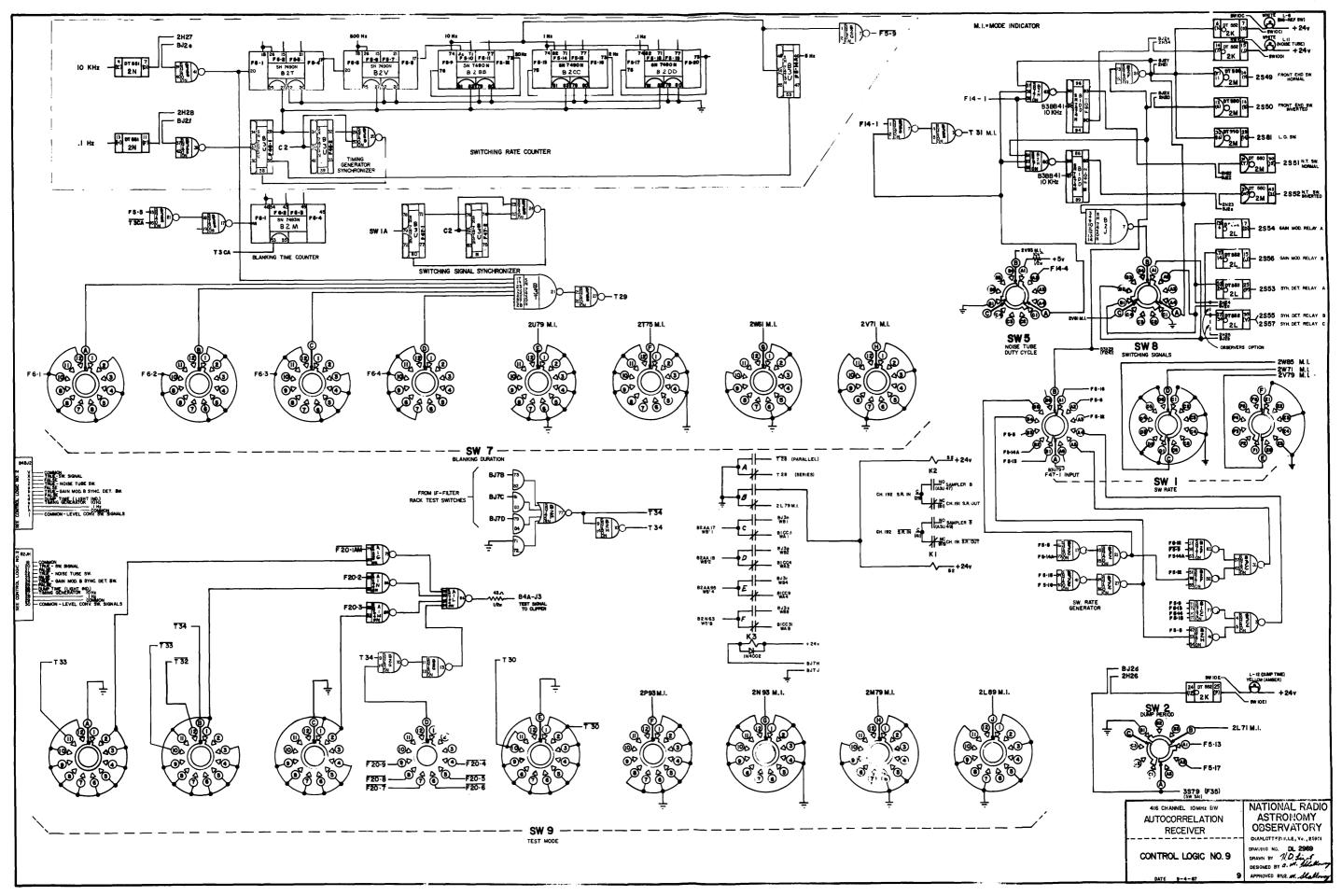

| 22. | Control Logic No. 9 - NRAO #DL-2969                                 | 71   |

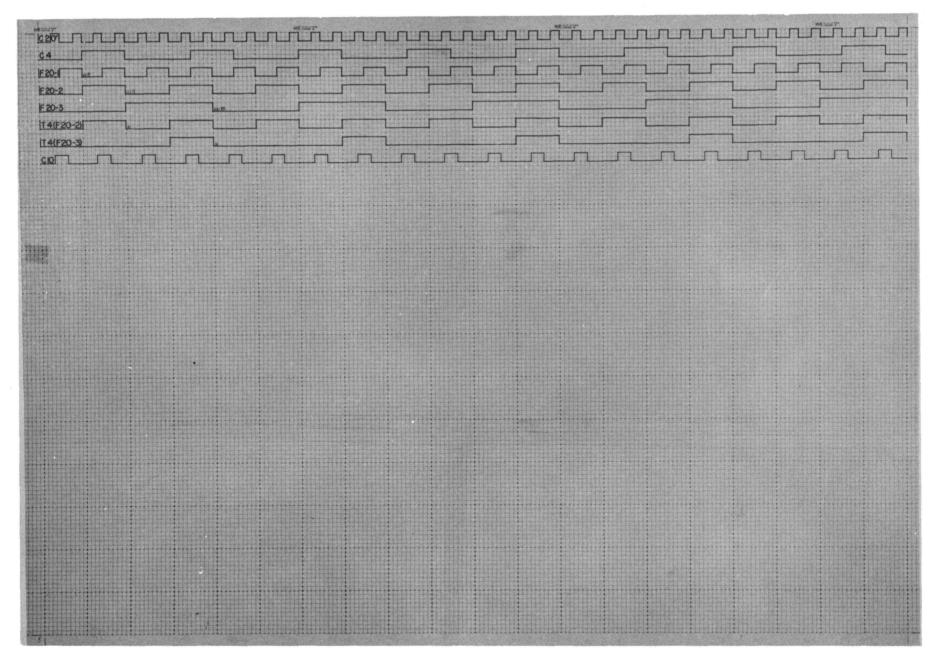

| 23. | Timing Diagram No. 1 - Sample Rate Generator                        | 72   |

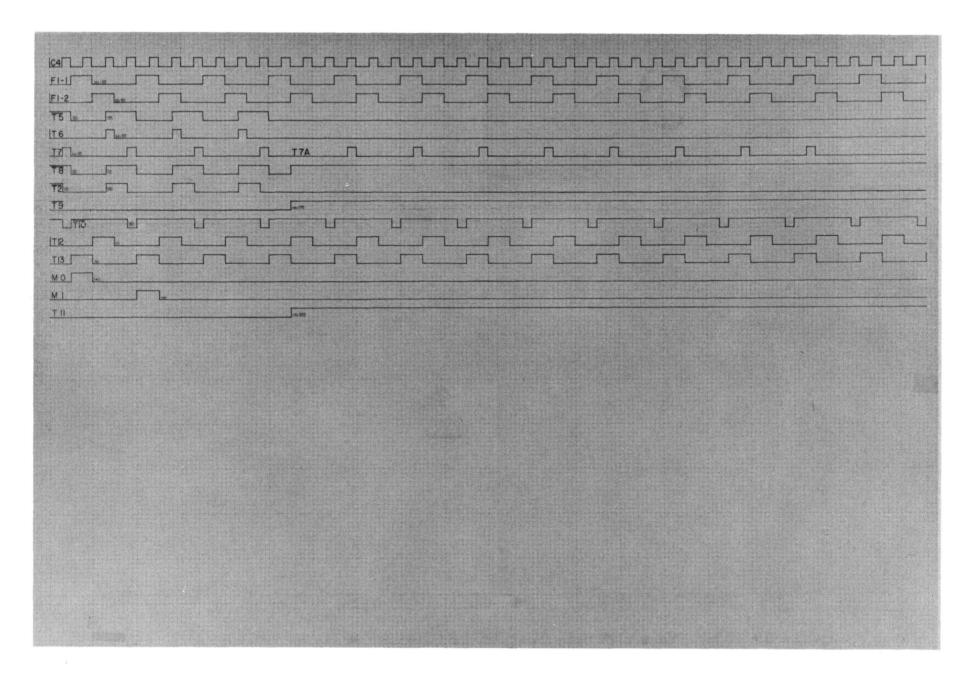

| 24. | Timing Diagram No. 2 - Shift Register Memory                        | 73   |

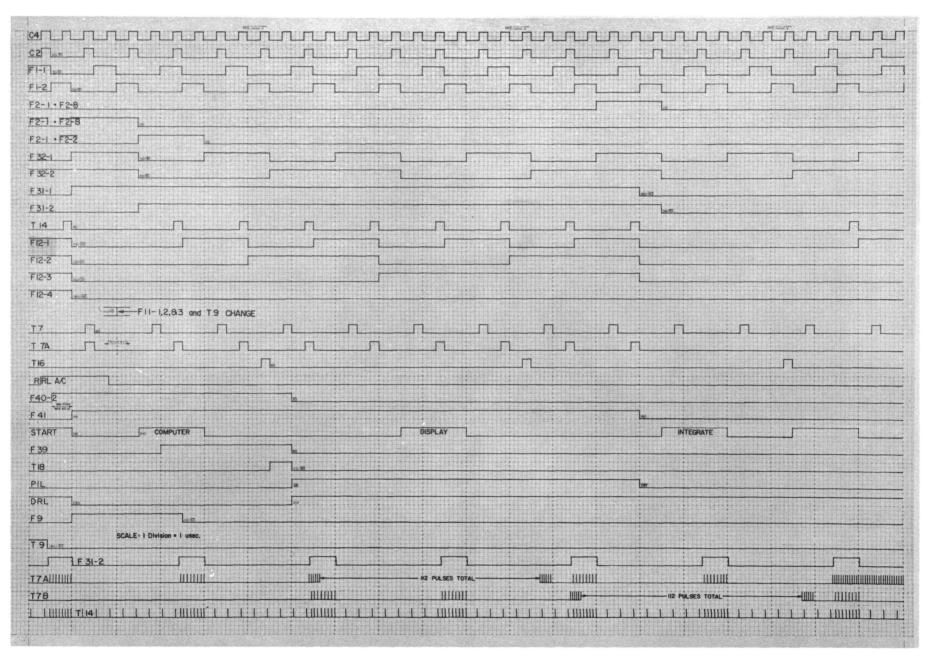

| 25. | Timing Diagram No. 3 - Switching Signal & Blanking Time Generators- | 74   |

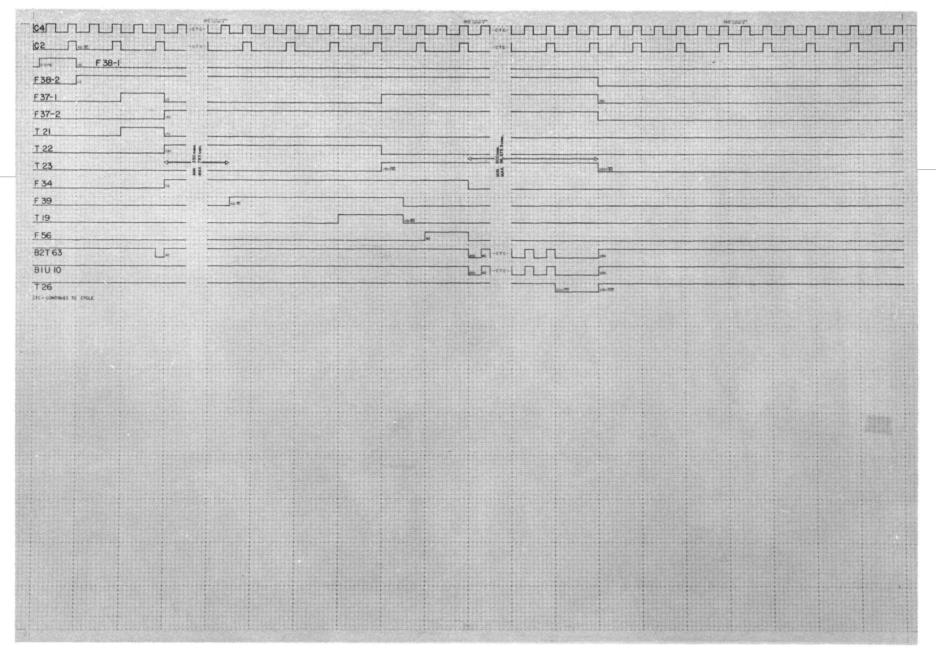

| 26. | Timing Diagram No. 4 - Miscellaneous                                | 75   |

| 27. | Timing Diagram No. 5 - Display                                      | 76   |

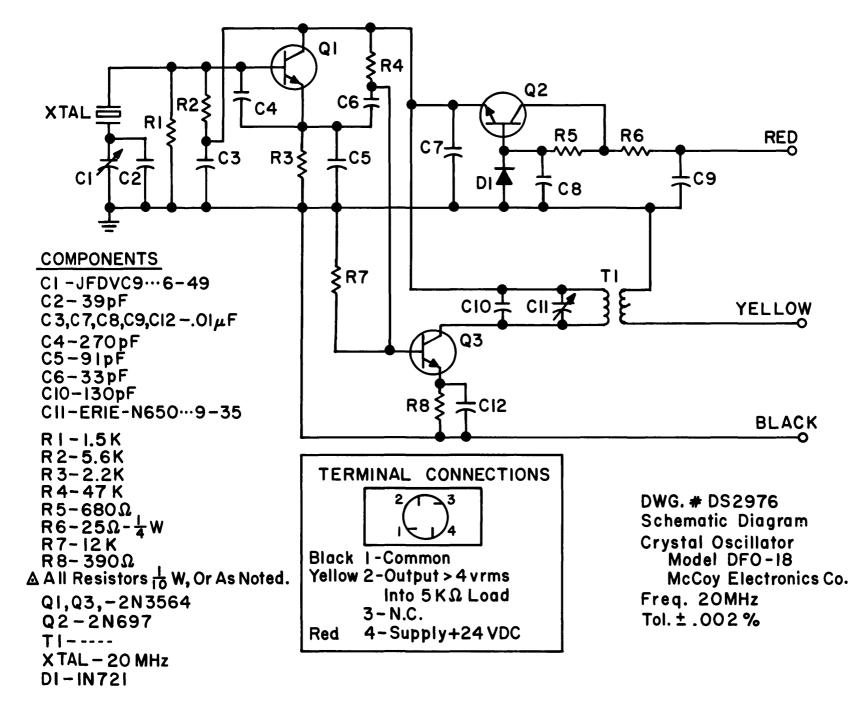

| 28. | 20 MHz Clock Crystal Oscillator+                                    | 77   |

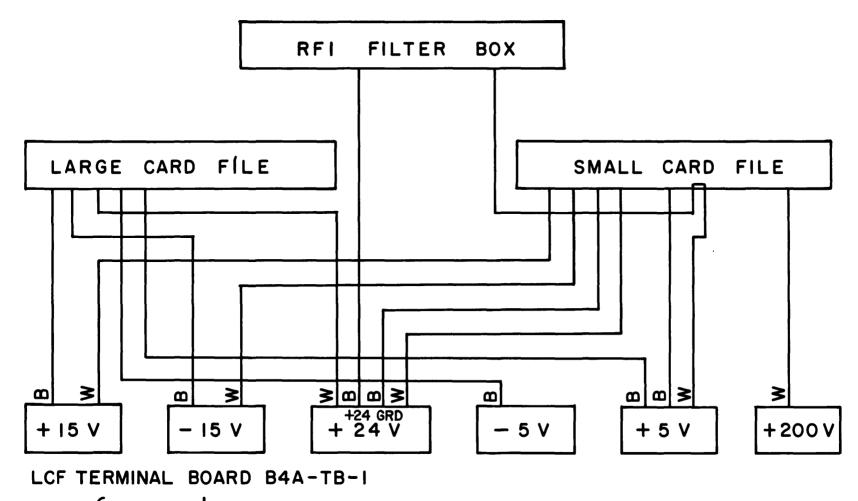

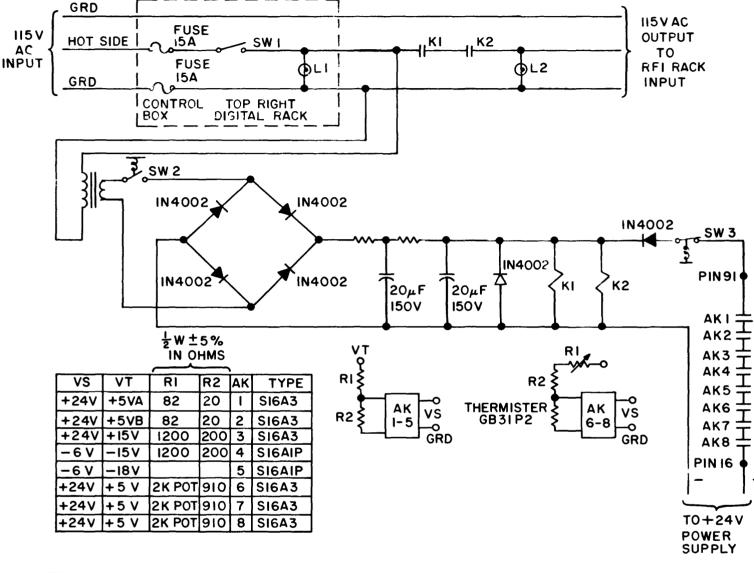

| 29. | Power Supply Cabling Diagram                                        | 78   |

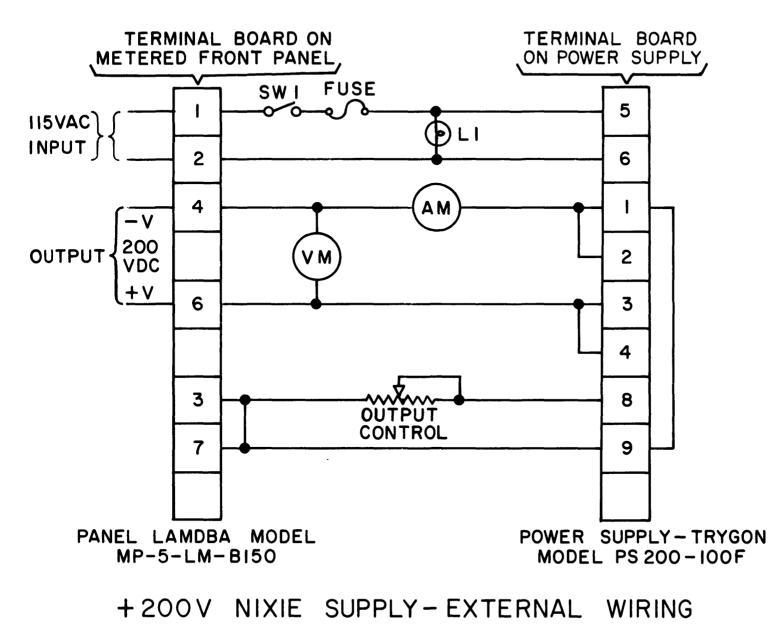

| 30. | +200V Nixie Supply - External Wiring                                | 79   |

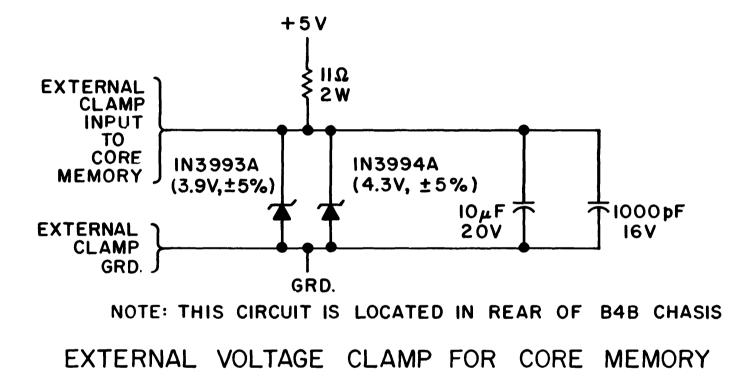

| 31. | External Voltage Clamp for Core Memory                              | 80   |

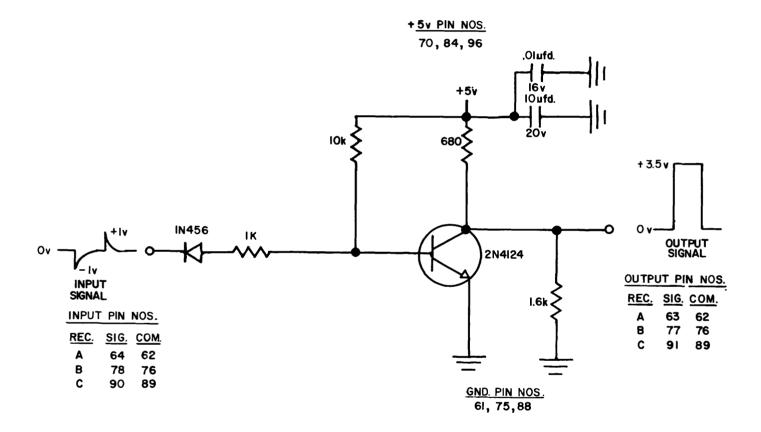

| 32. | V/F Converter Interface Circuit                                     | 81   |

| 33. | Power Control Schematic                                             | 82   |

# LIST OF TABLES

# Page

| TABLE | Ι  | Parameter V | alues for  | Various | Values | of | Bandwidth | <br>12 |

|-------|----|-------------|------------|---------|--------|----|-----------|--------|

| TABLE | II | Signal Iden | tification | n Codes |        |    |           | <br>19 |

# LIST OF TABULATIONS

| 1.  | Wiring Lists and Location Charts               | i  |

|-----|------------------------------------------------|----|

| 2.  | Switching Rates                                | 5  |

| 3.  | Signals Controlled by Switching Rate Generator | 11 |

| 4.  | Use of Core Memory Data                        | 13 |

| 5.  | Location Terminology List                      | 14 |

| 6.  | Abbreviations                                  | 17 |

| 7.  | Drawing Quadrant Nomenclature                  | 21 |

| 8.  | Multiplier Truth Table                         | 26 |

| 9.  | Shift Register Memory Cycle                    | 29 |

| 10. | SRM - Core Memory Cycle                        | 30 |

| 11. | F2 Counter Sequence                            | 34 |

| 12. | Cycle Times Counters - SRM's - Core Memory     | 37 |

| 13. | F11 Counter Sequence                           | 40 |

| 14. | Switching Signals                              | 43 |

# AUTOCORRELATION RECEIVER MODEL II DIGITAL SYSTEM

A. M. Shalloway

# I. Introduction

The NRAO Autocorrelation Receiver Model II is a specialized receiving system for observation of spectral lines. It is the equivalent of a multichannel spectrum analyzer. A block diagram of a complete system using the correlation receiver is shown in Figure 1.

The process consists of filtering out a selected bandpass centered at a desired spectral-line frequency and heterodyning it down to the videofrequency range with one side of the bandpass being at zero frequency. This signal is clipped to provide a rectangular waveshape of fixed amplitude. The only correspondence between the clipped and unclipped signal is that they both cross zero at the same time. The clipped signal is sampled at a frequency equal to twice the bandwidth and the sampled data is used to generate two autocorrelation functions with 192 points or one with 384 points.

The integrated autocorrelation function is processed by an on-line computer. The computer performs a Fourier transform to generate a power spectrum. The computer data is available as an on-line graph on a storage oscilloscope, as a printed-tabular output, and as an output on magnetic tape which can be further processed by an off-line computer.

# II. Operational Description

Reference should be made to the block diagram of Figure 2. The clipper output, which has been previously described as a rectangular waveshape containing the frequency information of the original received signal, is sampled at a rate equal to twice the filter bandwidth. The sampler provides a compatible digital output which is synchronized to the digital system clock.

# SYSTEM BLOCK DIAGRAM

Figure 1

μ

The sampled data is continuously stored in a 192 bit shift register which is updated at every clock (sample) pulse. Each shift register stage feeds a one bit multiplier. The other input to the multiplier is the "present" (latest) data out of the sampler. This provides a correlation comparison between the present sample and the previous 191 samples, each spaced  $\tau$  seconds behind the adjacent sample; where  $\tau$  is the sampling period.

If the two samples sent to a multiplier correlate, the multiplier provides a 1 to the associated counter; if not a 0 is provided. After the appropriate integration time the counters represent 192 points on the autocorrelation curve of the integrated signal. The first channel always correlates, as it multiples the present sample times itself. This provides a record of the number of sample pulses used during one integration period. In terms of the NRAO Autocorrelation Receiver Model I, this is what was referred to as 2V.

The digital unit keeps the signal and reference data in separate memory locations of its core memory until dump time (every second or every 10 seconds), at which time the signal and reference data for all channels are sent to the on-line computer. Also sent to the computer are the signal and reference total power measurements for the three receivers. All knob positions are then sent to the computer. The knob positions sent to the computer are determined in the last half switching cycle prior to dump time.

There are 28 bits in each autocorrelation counter. The eight least significant bits are discarded prior to transmittal of the data to the computer. These eight bits are equal to or less than the RMS variations, and thus nothing is lost. There are 20 bits in the total power counters and they are all transmitted to the computer. A detailed description of data transferred to the computer is given in Appendix I.

The digital rack is an RFI shielded rack to prevent transmission of the many signals generated by the digital logic. Therefore, except to change

-4-

knob positions or to service the instrument, the front and rear doors should always be closed securely.

Figure 3 is a photograph of the digital rack. Power can be controlled from either box on top. The push buttons are normally used. If a long downtime is expected (more than a day) the toggle switch is also moved to the off position. A switch on the small card file with the display tests the display lamps. All other controls are on the digital autocorrelator chassis panel (large card file). A brief explanation of these follows:

## Dump Period

The Dump Period is the integration time (1 or 10 seconds) in the correlator before dumping data into the computer.

# Switching Rates

Switching rates between 1 Hz and 10 Hz can be selected. The signal/ reference duty cycle can also be changed. The allowed combinations of switch rate and duty cycle are:

| 1  | Ηz | ~ | 50%/50% |

|----|----|---|---------|

| 5  | Ηz | - | 50%/50% |

| 10 | Ηz | - | 50%/50% |

| 1  | Ηz | - | 90%/10% |

| 5  | Ηz | ~ | 75%/25% |

As an example, "1 Hz - 90%/10%" means that 0.9 second is spent on signal and 0.1 second is spent on reference. This mode will improve sensitivity by approximately a factor of 2 if the reference data is integrated in the computer 100 times longer than the signal data. The usual setting is "1 Hz - 50%/50%".

#### Noise Tube Duty Cycle

In normal operation the noise calibration signal is automatically turned on for every other dump period (50%/50%) or for every tenth dump period (10%/90%).

When the noise calibration signal is on, it is not on continuously - it is so modulated that it is on during the signal period and off during the comparison period. The usual setting is 50%/50%.

# Blanking Time

Blanking time is a "dead" time at the beginning of each signal or reference period. A small amount of blanking time is needed to clear various registers in the correlator. A longer blanking time can be switch selected to allow front-end or LO switching transients to die out of both analog and digital portions of the system. The allowed blanking time is 4 to 26 ms in steps of 2 ms.

# Display

A description of the displays and associated knobs follows:

<u>Channel Data</u>: Indicates data obtained for a particular channel during the previous dump period.

<u>Channel Number</u>: Indicates number of channel whose data is being displayed.

LAMP-DU: Data/Update - Whenever this lamp is on the channel data information is updated every dump time.

LAMP-CD: Computer Data - This lamp goes on as soon as the data is available for the computer at the beginning of each dump period. As soon as the computer has removed the data, the light goes out. A continuously burning light indicates that the computer is not taking data. If the cable between the Digital Unit and the Computer Unit is disconnected, the light will act as though the computer is removing data.

LAMP - +24 V: +24 volt power supply on-off indicator. +24 volts used on clock crystal oscillator circuit, lamps, and relays.

<u>LAMP - +5 VB</u>: +5 volt power supply on-off indicator +5 volt B is used on the lower half of the correlator chassis.

<u>LAMP - +5 VA</u>: +5 volt power supply on-off indicator. +5 volt A is used on the upper half of the correlator chassis.

LAMP S-R/I: Signal-Reference Integration. Light on indicates signal is being integrated. Off indicates reference being integrated. This assumes first half of each switching cycle is signal.

LAMP S-R/D: Signal-Reference Display. Light on indicates the channel being displayed is signal data. Light off implies reference. This assumes first half of each switching cycle is signal.

<u>LAMP - -15 V</u>: -15 volt power supply on-off indicator. -15 volts is used on clock amplifiers and sampler circuits.

<u>LAMP - +15 V</u>: +15 volt power supply on-off indicator. +15 volts is used on clock amplifiers and sampler circuits.

LAMP - -18 V: -18 volt and -6 volt power supplies on-off indicator. -18 and -6 volts are used on the input and output level converters.

LAMP - NT: Noise Tube. Light on indicates noise tube on.

<u>LAMP - DT</u>: Dump Time. Light goes off at beginning of dump period. Light goes on when dump period is half over.

<u>KNOB - Light Test</u>: Clockwise rotation turns all lamps except power supply indicators on.

<u>KNOB - Display and Advance Rate</u>: When the Display and Advance (Sw. 4) knob is in the Display and Advance position, this knob controls the rate of advancing from one channel to the next. The rate varies from approximately 0.8 Hz to 3.5 Hz.

# KNOB - Display Mode (Sw. 3):

Display Update - Channel number remains constant. Data display is updated at every dump time.

-8-

- Display & Advance Channel is advanced at rate determined by Display & Advance Rate knob. As each new channel number appears the data display changes to show the data in that channel.

- Advance 10 Ch/s, 50 Ch/s, and 250 Ch/s Advances the channel display at the rate indicated. The Channel Data Display is inoperative.

TOGGLE SWITCH - Display and Advance (Sw. 4): Up is a locked

position. Down is a spring return position. If the toggle is up or down, the Display Mode Knob (Sw. 3) is activated for all positions except Display Update. Display Update does not require the use of this toggle switch.

# Testing

Square waves can be sent into the clippers by positioning the desired test toggle switch on the IF filter rack and choosing the desired frequency on the Test Signal Switch (Sw. 9) on the digital rack.

The crystal oscillator clock frequency can be checked by disconnecting the test signal cable between the digital rack and the IF-filter rack - top of the rack. Put the test signal switch on 10 MHz and feed the test output from the digital rack to a stable counter. Multiply the reading by 2. An error of  $\Delta f$  in this oscillator causes an expansion of the frequency scale so that a point at one end of the spectrum is shifted by  $\Delta f \cdot B/20$  where B is the spectrum bandwidth in MHz.

# III. Block Diagram Description

# (Refer to Figure 4)

The CONTROL LOGIC consists of many small logic groups throughout the system. Each block in the diagram is associated with several of these logic groups to control the block's timing, gating, etc.

-9-

DIAGRAM

Figure 4.

The 20 MHz CLOCK is a crystal controlled oscillator from which all clocking pulses are derived. The oscillator has a stability of 20 PPM per 10 seconds and per 24 hours over a temperature range of +20° to +50°C, and can be set to within a few cycles of 20 MHz. In addition to using the 20 MHz directly, a divider provides a 4 MHz and 2 MHz clocks for clocking the lower speed sections.

The SAMPLING RATE GENERATOR is a dividing and timing system which, combined with the 20 MHz CLOCK, generates the correct sampling, shifting and multiplying rate.

The SAMPLER, described in the IF and Filter Section, receives the clipped noise signal at its input. A clock pulse is provided the SAMPLER to indicate when a sampling should be made. The SAMPLER output consists of a flip-flop which can only change state at the clock pulse time. It stores a one or a zero, until the next clock pulse, depending on whether the clipped noise signal is above or below zero at the sample time. The SAMPLER output is transferred to drivers with sufficient power to drive the first stage of the SHIFT-REGISTER and the 192 MULTIPLIERS.

The SAMPLER, SHIFT REGISTER and MULTIPLIERS operate at the clock rates indicated in Table I for the various bandwidths.

Two signals are received from the telescope Timing Generator: 10 KHz and 0.1 Hz. These are used to drive the SWITCHING RATE GENERATOR which controls the following:

- 1. Blanking Time

- 2. Dump Time

- 3. Front End Switching Rate

- 4. Noise Tube Switching Rate

- 5. Gain Modulator Switching Rate

- 6. Synchronous Detector Switching Rate

The BLANKING CONTROL holds up operation of the multipliers during the blanking time. During this time the data in the COUNTERS is transferred to the core memory and the old SHIFT REGISTER data is replaced by new data.

-11-

# TABLE I

# PARAMETER VALUES FOR VARIOUS VALUES OF BANDWIDTHS

|            |    |    |    | <b></b> | 1  |                       |                 | PULSE F                     | ATE         |

|------------|----|----|----|---------|----|-----------------------|-----------------|-----------------------------|-------------|

| BANDWIDTH  | W8 | W4 | W2 | W1      | то | C10                   | T4 <sup>*</sup> | Sampler & Shift<br>Register | Multipliers |

| 10 MHz     | 0  | 0  | 0  | 0       | 1  | 1                     | 1               | 20MHz                       | 20MHz       |

| 5MHz       | 0  | 0  | 0  | 1       | 0  | <u>Pulse</u><br>10MHz | 1<br>Pulse      | 10MHz                       | 10MHz       |

| 2.5MHz     | 0  | 0  | 1  | 0       | 0  | 10MHz                 | 5MHz            | 5MHz                        | 10MHz       |

| 1.25MHz    | 0  | 0  | 1  | 1       | 0  | 10MHz                 | 2.5MHz          | 2.5MHz                      | 10MHz       |

| 625KHz     | 0  | 1  | 0  | 0       | 0  | 10MHz                 | 1.25MHz         | 1.25MHz                     | 10MHz       |

| 312.5KHz   | 0  | 1  | 0  | 1       | 0  | 10MHz                 | 625KHz          | 625KHz                      | 10MHz       |

| 156.25KHz  | 0  | 1  | 1  | 0       | 0  | 10MHz                 | 312.5KHz        | 312.5KHz                    | 10MHz       |

| 78.125KHz  | 0  | 1  | 1  | 1       | 0  | 10MHz                 | 156.25KHz       | 156.25KHz                   | 10MHz       |

| 39.0625KHz | 1  | 0  | 0  | 0       | 0  | 10MHz                 | 78.125KHz       | 78.125KHz                   | 10MHz       |

| ļ          |    |    |    |         |    |                       |                 |                             |             |

$^{\star}$  T4 positive pulse width is 100ns and brackets C10 at gates where used.

See Figure 23.

The SHIFT REGISTER MEMORIES are an extension of the counters. They contain the 9th through the 16th least significant bits of the total 28 bits which are counted. The 9th bit exists both in the last stage of the COUNTERS and the first stage of the SHIFT REGISTER MEMORIES. Stages 16 through 28 are contained in the CORE MEMORY. A detailed explanation of the operation appears in Section IV. This arrangement greatly reduces the total number of components, both in the form of flip-flop counters required and gating required between the COUNTERS and the CORE MEMORY.

The ADDER is used in the process of extending the counters in to the CORE MEMORY, and, as mentioned above, covered in Section IV.

The CORE MEMORY is accessed for three purposes:

- 1. Integration and storage of the autocorrelation function, i.e. the counter numbers.

- 2. Removal of the data for transfer to the ON LINE COMPUTER.

3. Removal of the data for visual display.

These three processes are interleaved; each being allowed a specific time in which it may operate. This is accomplished by the use of three ADDRESS REGISTERS: INTEGRATION, COMPUTER and DISPLAY. The DISPLAY ADDRESS REGISTER is duplicated in decimal form to display the channel of the data being displayed.

A STORAGE REGISTER is used to hold one computer word until removed by the computer.

A BINARY-TO-DECIMAL CONVERTER provides the necessary output for the DATA DISPLAY.

The output signals of the autocorrelator, to the COMPUTER and switch drivers, pass through LEVEL CONVERTERS for adapting the positive logic level swings of the correlator integrated circuits to the negative swings required by the CCC S-PAC germanium circuits used in the external devices.

-13-

During the detailed description of Section IV, an occasional look at the block diagram of Figure 4 will help locate ones thinking in the overall picture.

## IV. Descriptive Terminology

# A. Location Terminology (Refer to Figures 5 and 6)

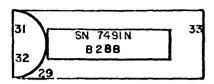

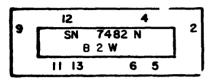

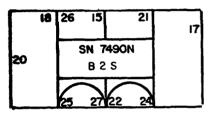

Wherever possible, all components can be located by an alphanumeric coding system. To reduce reading errors, the codes generally alternate between alphabetical and numerical indications e.g. B2K12. The codes travel from larger to smaller module as read from left to right. In the above example, B indicates the digital rack, 2 indicates the second chassis from the top of the rack (in this case the small card file), K indicates the tenth printed circuti connector position from the left as viewed from the wiring side of the file, and 12 indicates connector pin number 12.

An understanding of the location codes is necessary, particularly when servicing the equipment by use of the logic diagrams. The following notes will be helpful in deciphering the codes:

- Rack A = IF-Filter Rack

Rack B = Digital Rack

Rack C = DDP-116 Computer Input-Output Rack

- Plugs on the end of a cable are always referred to with the letter P. Jacks on a panel surface are referred to with the letter J.

- 3. Chassis B4 folds out. The two parts upper and lower are referred to as sub-chassis A and B, these letters entering into the location code. There are three files in each of these sub-chassis which are numbered 1, 2, and 3 from back to front. These numbers also enter into the location code, e.g. B4B2G15 would refer to the digital rack (B), the large card file (4), the lower sub-chassis (B), the middle file (2), the seventh connector from the

| LAMP | FUNCTION               | COLOR        | ON                                       | OFF          |

|------|------------------------|--------------|------------------------------------------|--------------|

| LI   | DATA UPDATE            | WHITE        | UPDATING                                 | NOT UPDATING |

| L2   | COMPUTER REMOVING DATA | BLUE         | CRO-FLASHES ON<br>C NOT RD - CONSTANT ON |              |

| L3   | + 24v                  | GREEN        | ON                                       | OFF          |

| L4   | + 5v (B)               | GREEN        | ON                                       | OFF          |

| L 5  | + 5v (A)               | GREEN        | ON                                       | OFF          |

| L6   | SIGREF. (SWITCHING)    | WHITE        | SIG.                                     | REF          |

| L7   | SIG-REF. (DISPLAY)     | LIGHT YELLOW | SIG.                                     | REF.         |

| L8   | -15v                   | GREEN        | ON                                       | OFF          |

| L9   | + 15v                  | GREEN        | ON                                       | OFF          |

| LIO  | - 18v                  | GREEN        | ON                                       | OFF          |

| LII  | NOISE TUBE (SWITCHING) | WHITE        | ON                                       | OFF          |

| LIZ  | DUMP TIME              | YELLOW/AMBER | PRIOR TO DUMP                            | DUMP TIME    |

-15-

| Т | 0 | Ρ |

|---|---|---|

|---|---|---|

# BOTTOM

|                      |         |         |                |              |         |                      |                         | :                | SUB       | CHA       | 9918     | B 4, | A                  |              |                         |                 |                   |                        |                         |                 |                   |                   |                   |                           |           |                              |           | 、                 | IEW FROM | WIRING SIDF |                 |         |             |         |          | SUB                  | CHA                          | SSIS                   | B4      | в         |           |          |          |                      |             |          |              |             |         |          |

|----------------------|---------|---------|----------------|--------------|---------|----------------------|-------------------------|------------------|-----------|-----------|----------|------|--------------------|--------------|-------------------------|-----------------|-------------------|------------------------|-------------------------|-----------------|-------------------|-------------------|-------------------|---------------------------|-----------|------------------------------|-----------|-------------------|----------|-------------|-----------------|---------|-------------|---------|----------|----------------------|------------------------------|------------------------|---------|-----------|-----------|----------|----------|----------------------|-------------|----------|--------------|-------------|---------|----------|

| A                    | в       | с       | D              | E            | E       | F                    | G                       | н                | J         | ĸ         | L        |      | м                  | N            | Ρ                       | R               | s                 | т                      | U                       | v               | w                 | x                 | Y                 | z                         | AA        | BB                           | CC        | _                 | BACK     |             | A               | B       | c           | D       | E        | F                    | G                            | H                      | J       | к         | L         | M        | N        | Ρ                    | R           | s        | т            | U           | v       | ٧        |

| $\mathbf{F}$         |         | DP      | 2 954<br>U NTE |              | -       |                      | 2932                    | -                | Ė         | -         | Ŧ        | 4    |                    | 544          | -                       | _               |                   |                        | 2932                    | -               | ļ.                | Ť.                | DP2               | 9544<br>TER               | Ŧ         | F                            | -         | 2931              |          |             | F               |         |             |         |          | _                    | -DL2<br>S                    |                        |         | $\square$ | $\square$ |          | -        | DP2936               |             |          | 2938         |             | + DP 2  |          |

| -<br>CHANNEL 0-7     | 8 - 15  | 24-31   | - 47           | 63-          | 60-00   | 72 – 79              | SAMPLING RATE GEN. A DP | CHANNEL 88 - 95  | 104-111   | 120 - 127 |          |      | 00                 | - 175        | 184 - 191               | 200 - 207       | 216 - 223         | 232 -239               | SAMPLING RATE GEN. A DP | CHANNEL 248-255 | 264-271           | 280 - 287         | 296-303           | 61E - 21E                 | 328-335   | 344-351                      | 360 - 367 | SAMPLER BOARD DP  |          |             | CHANNEL 0 15    | 32 47   | 64 79       | 96      | 128 143  | 160 175              | SECT<br>SECT<br>202 261      | 224 239 <sup>2</sup> 3 | 256 271 | 288 303   | 320 335   | 352 367  | 384 399  | CONTROL LOGIC TYPE 3 | 2           | Ð        | ŝ            | ŝ           | 'n      |          |

| 1<br>27              | 2<br>26 | 3<br>23 |                |              | 5<br>23 | 6<br>22              | 7<br>21                 | 8<br>20          | 9<br>19   | 10        |          |      | 12<br>16           | 13<br>13     | }4<br> 4                | 13<br>13        | 16<br>12          | 17<br>11               | 18<br>10                | 19<br>9         | 20<br>8           | 21<br>7           | 22<br>6           | 23<br>3                   | 24<br>4   | 23<br>3                      | 26<br>2   | 27                | -FOR REI | ERENCE      | 27              | 2<br>26 | 3<br>25     | 4<br>24 | 3<br>23  | 6<br>22              | 7<br>21                      | 8<br>20                | 9<br>19 | 10<br>18  | 11<br>17  | 12<br>16 | 13<br>15 | 14<br>14             | 15<br>13    | 16<br>12 | 17<br>11     | 18<br>10    | 19<br>9 | 2        |

|                      |         |         | T              |              |         | DP2                  | 9158                    |                  |           |           |          |      |                    | _            | <del>9</del>            |                 |                   |                        |                         | [               |                   | 2 9158            | <u> </u>          |                           |           |                              |           | L.,               | ]        |             |                 |         | DP2         | 9644    | DP 2954  | •D                   | P 293                        | 8                      | + DP2   | 937       |           |          | [        |                      | - DP 2      | 935      |              |             |         | <u> </u> |

| CHANNEL 0 - 15       | 16 - 31 | 32 - 47 | 48             |              | 61 - 49 | COR<br>56<br> <br>08 |                         | 10R<br>121 - 211 | 128 - 143 | 144 - 159 |          |      | 176 - 191          | :07 - 201    | SAMPLING RATE GEN. C DP | CHANNEL 208     | 224 - 239         | 240 - 255              | 256 - 271               | 272 - 287       | CORI<br>208-982   | RELA<br>616 - 406 | F OR<br>920 - 335 | 336 - 351                 | 352 - 367 | 368 383                      | 384 – 399 | 400-415           |          |             | CHANNEL 376-383 | 384 391 | 305 399 000 | TER     | 408 4 15 | CONTROL LOGIC TYPE 5 | Ω.                           | 20                     | 4       | 4         | 8         | 8        | N        | 5                    | 2           | 8        | 2            | 8           | N       | •        |

| <b>^</b>             | 8       | c       | 0              |              | E       | F                    | G                       | н                | J         | ĸ         | <u> </u> |      | м                  | N            | P                       | R               | s                 | T                      | <u> </u>                | v               |                   | ×                 | Y                 | z                         | AA        | 88                           | 00        | 00                | 1        |             | L               | 8       | <u>د</u>    | D       | E        | F                    | G                            | н                      | J       | ĸ         | د<br>     | M        | N        | P                    | R           | s        | T            | U           |         | _        |

| a<br>CHANNEL 16-23 A | 32 - 39 |         | 11             | R  <br>:   2 | 80-87   | 96-103               | SAMPLER BOARD DP 293    | CHANNEL 112-119  | 128-135   | 144 - 151 |          |      | 14 400<br>1400 183 | ER 661 - 261 | 20 MHz OSCILLATOR       | CHANNEL 208-215 | 224-231 890<br>20 | 954A<br>TER<br>142-042 | SAMPLER BOARD DP 2931   | 256 - 263       | CHANNEL 272 - 279 |                   |                   | 2 9544<br>NTER<br>128-028 | 336-343   | SAMPLING RATE GEN. B DP 2939 | 352-359   | CHANNEL 368-375 5 | FRONT    |             | CHANNEL 16 31   | 48 63   | 80 95       | 112 127 | 144 159  | 126 191              | 208 223 80 5<br>208 223 80 5 | RM                     | 272 287 | 304 319   | 336 351   | 368 383  | 400 415  | CONTROL LOGIC TYPE 3 | P 293<br>10 | 5<br>10  | <del>7</del> | P 2336<br>P | 10      |          |

| W     X     Y     Z     AA     BB     CC     DD       36     pr 2337     DP     2936     pr 2337                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In     Im     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | In     4*     In     <                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                |

| 20     21     22     23     24     26     26     27       0     21     22     23     24     26     26     27       0     203     0     203     0     203     0     203       0     0     9     203     0     203     0     203       0     0     9     203     0     203     0       0     0     9     203     0     0     203       0     0     9     203     0     0     0       0     0     9     203     0     0     203       0     0     9     203     0     0     0       0     0     9     203     0     0     0       0     0     9     203     0     0     0       0     0     9     203     0     0     0       0     0     9     203     0     0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20     21     22     23     24     25     26     27       0     27     5     4     3     2     1       0     2050     0*2050     0*2050     0*2050     0*2057     D     2933       0     40     4*     40     4*     -     -     -       0     40     4*     40     4*     -     -     -       1     1     1     1     1     1     1     1       1     1     1     1     1     1     1     1       1     1     1     1     1     1     1     1       1     1     1     1     1     1     1     1       1     1     1     1     1     1     1     1       1     1     1     1     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                |

| 0P2339         0P2337         0P2338         0P2337         D         P         293         4            2         2         3         4            2         2         3         4            2         2         3         4             2         2         3         4             2         3         4            2         2         3         4          2         2         3         4            2         2         3         4          2         3         4          2         3         4          2         2         3         4          2         3         4          2         3         4          2         3         4          2         3         4          2         3         4          2         3         4         3         3         3         4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DP 2010         DP 2017         CP 2018         CP 2017         DP 2013         A         A           N         40         4         40         4         -         -         -         -         293         4         -         -         -         2         2           W         X         Y         Z         AA         BB         CC         DD         2         3         4         -         -         -         -         2         2           W         X         Y         Z         AA         BB         CC         DD         -         -         -         -         -         -         -         2         2         -         -         -         -         -         -         -         2         2         -         -         -         -         -         -         2         2         -         -         -         -         -         -         2         2         3         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |                                                                                                                                                                                                                                                                                                |

| 0P2339         0P2337         0P2338         0P2337         D         P         293         4            2         2         3         4            2         2         3         4            2         2         3         4             2         2         3         4             2         3         4            2         2         3         4          2         2         3         4            2         2         3         4          2         3         4          2         3         4          2         2         3         4          2         3         4          2         3         4          2         3         4          2         3         4          2         3         4          2         3         4         3         3         3         4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DP 2010         DP 2017         CP 2018         CP 2017         DP 2013         A         A           N         40         4         40         4         -         -         -         -         293         4         -         -         -         2         2           W         X         Y         Z         AA         BB         CC         DD         2         3         4         -         -         -         -         2         2           W         X         Y         Z         AA         BB         CC         DD         -         -         -         -         -         -         -         2         2         -         -         -         -         -         -         -         2         2         -         -         -         -         -         -         2         2         -         -         -         -         -         -         2         2         3         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |                                                                                                                                                                                                                                                                                                |

| pr2350         pr2351         pr2351 <th pr2351<="" td=""><td>0     00     4     100     92807     DP     293     4       N     100     47     100     47     -     -     -     -     2       W     X     Y     Z     AA     BB     CC     DD       W     X     Y     Z     AA     BB     CC     DD       W     x0     40     40     40     40     40     40</td></th> | <td>0     00     4     100     92807     DP     293     4       N     100     47     100     47     -     -     -     -     2       W     X     Y     Z     AA     BB     CC     DD       W     X     Y     Z     AA     BB     CC     DD       W     x0     40     40     40     40     40     40</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0     00     4     100     92807     DP     293     4       N     100     47     100     47     -     -     -     -     2       W     X     Y     Z     AA     BB     CC     DD       W     X     Y     Z     AA     BB     CC     DD       W     x0     40     40     40     40     40     40 |

| N         ID         IP         ID         ID<                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N         0         4         10         4         -         -         -         -         -         2           W         X         Y         Z         AA         BB         CC         DD           W         X         Y         Z         AA         BB         CC         DD           W         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w         w <td< td=""></td<>      |                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DP2938                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                |

| 416 CHANNEL 10MH2 BW                                     | NATIONAL RADIO                                                 |

|----------------------------------------------------------|----------------------------------------------------------------|

| AUTOCORRELATION                                          | ASTRONOMY                                                      |

| RECEIVER                                                 | OBSERVATORY                                                    |

| LARGE CARD FILE<br>B 4 LOCATION DRAWING<br>DATE 12-12-07 | DRAWING NO. DA 2970<br>DRAWIN BY<br>DESIGNED BY<br>APPROVED BY |

left (as viewed from the front of the chassis) (G), and the fifteenth pin on the connector (15).

4. In some drawings the rack indication B is left off. Also, in some cases, the chassis designation 2 or 4 is left off in which B2 or B4 is assumed. However, this is done in such a manner that an ambiguity as to what is meant, should not exist.

<u>B. Identification Terminology</u> (Refer to Figure 7 and Figures 10 through 22) Figure 7 illustrates and identifies all of the logic symbols,

All flip-flops in the logic diagrams are given an F number. If the flip-flop is a part of a counter, register, or closely associated with other flip-flops in logic operation, they are given dash numbers, e.g. Fl8-10, which would be referred to as the 10th bit of the Fl8 counter. These F numbers refer to the output of the flip-flops and are barred for the complement (lower) output, e.g.  $\overline{F18-10}$ .

Gates and other logic elements do not have a designation other than location. Reference is made to gates by listing their location with the output pin. When an output line from any logic element is not continuous on the drawing to its input point, it is given an identification code. The code consists of a letter followed by a number and the general classifications are shown in Table II.

Some abbreviations which are used are as follows:

A/C - Autocorrelation (receiver) Ch - Channel DRL - device ready line - to computer Gain mod - gain modulator I.C.- Integrated circuit L.O.- local oscillator LSF - least significant bit

-17-

8-BIT SHIFT REGISTER

2-BIT BINARY FULL ADDER

COUNTER

MULTIVIBRATOR

INPUT LEVEL CONVERTER

OUTPUT LEVEL CONVERTER

OUTPUT DRIVER

LOGIC SYMBOLS

# TABLE II

#### CODE GENERAL CLASSIFICATION EXAMPLE С Clocks C4 4MHz clock IA Core Memory Address Selection IAO 1st bit of input address Core Memory Input Data ID ID1 lst bit of input word Μ Counter Control Matrix M5 6th output of matrix Ν Core Memory Input Data NO 1st input word Selection Matrix OD Core Memory Output Data OD1 1st bit of output word SF Control Section Shift SF1 lst control shift Registers register SM Sampled Output of Shift SF5 Sampled output of 5th **Register Memories** shift register memory All other signals not Т Т3 Blanking signal covered by other codes W Bandwidth code from IF-WA1 Least significant bit filter rack of code from receiver A Y Parallel Output of Shift YOA Least significant bit Register Memories from shift register memory section A Σ Adder Output Σ1 Least significant bit output of adder

#### SIGNAL IDENTIFICATION CODES

When a signal code is followd by an A or B (e.g. C4A or C4B) it generally means they are the same signal logically, but from different sources, such as two separate drivers.

| MSB -   | most significant bit                                           |

|---------|----------------------------------------------------------------|

| M.I     | mode indicator - knob position signals sent<br>to the computer |

| N.T     | noise tube                                                     |

| 0.C     | omni-comb                                                      |

| PIL -   | priority interupt line - to computer                           |

| ref -   | reference                                                      |

| RRL –   | reset ready line - from computer                               |

| sig -   | signal                                                         |

| SR -    | shift register                                                 |

| SRM -   | shift register memory                                          |

| SW -    | switch                                                         |

| syn det | - synchronous detector                                         |

| V/f C - | <ul> <li>voltage-to-frequency connector</li> </ul>             |

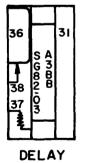

# C. Timing Chart Terminology (Refer to Figures 23 through 27)

The timing charts are self-explanatory and are used in the detailed logic description. They are drawn as though there were no delays in any of the logic elements through which the various signals must pass. However, to indicate the possible delay, the small numbers mixed in with each plot indicate the maximum delay possible assuming the worst case from the integrated circuit manufacturer's specifications. A barred number indicates the complements signal maximum delay. If only a true or a complement delay is given, the other one is the same or no signal exists for the other one.

The two states available in the logic are zero volts (nominally 0 to 0.5 V) and a plus volt (nominally 3 to 4 V). Within the A/C OV is a logical zero and the plus voltage is a logical 1. In further discussion, only the terms 0 and 1 will be used.

# V. Logic Description

# A. Location Code

In this section a detailed description will be given of the logic,

-20-

following in general, the same order of items as in Section III. Figures 14 through 22 are the nine control drawings and are entitled CONTROL LOGIC NO. 1 through 9. When reference is made to a particular piece of logic, a code will be noted in parenthesis to indicate the drawing location of the logic. The first item in the code will be a number between 1 and 9 to indicate the control logic drawing. The second item will be one or more of four letters; A, B, C, or D. They each refer to one quarter of the drawing, thus:

| A | В |

|---|---|

| С | D |

If only a number is contained in the parenthesis, it indicates reference to all four quadrants.

#### B. Synchronous System

The entire logic system is operated synchronously. Every flip-flop is operated in synchronism with either the 20 MHz clock, the 4 MHz clock, the display oscillator or the timing generator signal. Although these four clocks are not in synchronism with each other, whenever a signal is passed from a logic element controlled by one clock to a logic element controlled by another, it passes through an asynchronous to synchronous element.

Delay multivibrator circuits have been kept to a minimum and are used only for shaping and delaying the C10 clock signals. Along with the synchronous design, counters have been designed such that they cannot remain in an unused or undesirable logic state. This eliminates the need for a reset switch on the control panel. About 20 seconds after applying power, the system should be synchronized and operating properly.

#### C. 20 MHz Clock

The clocking system (Figure 8) must generate all of the signals listed in Table I plus a 4 MHz and 2 MHz pulse for the control logic. All clock pulses originate on the 20 MHz crystal control oscillator board. The oscillator drives two emitter follower amplifiers, the total load being divided between the two amplifiers. The 20 MHz is distributed as a sine wave over unmatched but constant impedance transmission lines which are the same length within about  $\pm 6$ ".

On each board the 20 MHz sine wave is then converted into a pulse waveshape by a 1 K ohm resistor feeding a gate. The width of the pulse is controlled by a DC level set on each emitter follower on the clock board. They are normally set to produce a positive pulse width of approximately 21 or 22 nanoseconds into the clock input of the flip-flop.

#### D. Sampling Rate Generator

Except in logic drawings 8A and 8B the 20 MHz sine wave traverses four gates (7) to produce the required clock signal for sampling, shifting, and multiplying. When 20 MHz is required out of the four gates, TO, ClO, and T4 are all 1. For 10 MHz; TO is 0, ClO is a 10 MHz pulse, and T4 is a 1. For lower frequencies, TO and ClO are the same as for 10 MHz and T4 is a control signal of such shape as to gate through every other ClO, or every fourth ClO, or every eighth ClO, etc.

Counter F20 (8A) generates outputs at 10 MHz, 5 MHz, etc. - to 39.0625 KHz. When operating at 10 MHz bandwidth, the W (8A, 8C, 8D) signals are all 0. This produces: TO = 1, C1O = 1, and T4 = 1, and all correlating

(sampling, shifting, and multiplying) circuits (7C, 7D, and Figure 10) are clocked at 20 MHz.

At lower than 10 MHz bandwidth, C20 continues to be distributed as a 20 MHz sine wave; however TO, C1O, and T4 control the correlating cirucits as shown in Table I.

A study of the table, control logic drawing 8A, B, C, and D, and timing diagram (Figure 23) illustrate how all of the high speed timing pulses are generated.

The two delay multivibrators (8D) with F20-1 input and  $\overline{F20-1}$  AM (M for modulated) output, are to provide as symmetrical a signal as possible for the "test signal to clipper" (9C), and also to provide some delay for the proper phasing of the C10 signals with respect to the T4 signals.

The remainder of the delay multivibrators (8A, B, C, and D) are for shaping C10 to an approximate 30ns positive pulse and aligning all C10's in phase.

The C4 generator (8B) is an instantaneous divide by 5 counter. The output is taken from F3-2 to provide a pulse of 100ns positive and 150ns at ground. If the counter takes up an unused state when power is turned on, it will cycle around to its normal operation without the need of a reset. No phase relation need exist between C4 and C20 or C10.

C2 is generated (5B) by F33 driving C4. F33 controls the B2X41 gate, allowing every other C4 pulse through. This provides a C2 of 100ns positive duration and 400ns ground duration. The input to pin 92 of F33 is to synchronize C2 and C4 properly.

#### E. Sampler

In the following explanation of the SAMPLERS, CORRELATORS, COUNTERS, and SHIFT REGISTER MEMORIES, it will be assumed the incoming control signals are available as required and their generation by the control unit will be explained later.