# NATIONAL RADIO ASTRONOMY OBSERVATORY CHARLOTTESVILLE, VIRGINIA

# ELECTRONICS DIVISION INTERNAL REPORT NO. 169

# TOTAL POWER INTEGRATOR FOR VLBI MARK II TERMINAL

B. RAYHRER AND B. WIREMAN

August 1976

NUMBER OF COPIES: 150

### LIST OF FIGURES

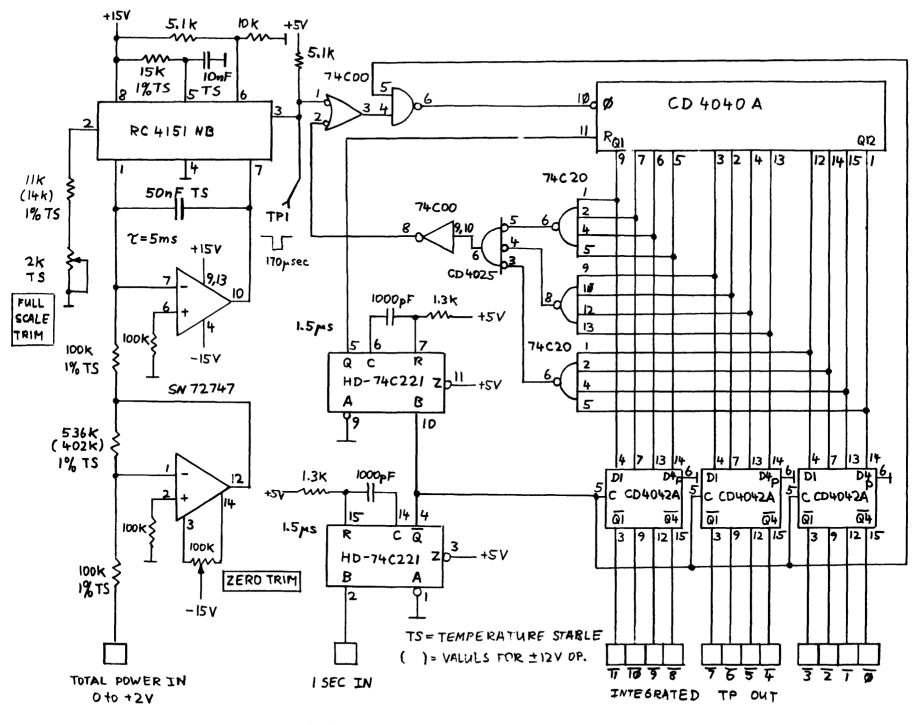

| Figure l | Circuit | diagram: | Total | power | integrator |

|----------|---------|----------|-------|-------|------------|

|          |         |          |       |       |            |

- Figure 2 S/N as function of  $\tau$  and BW

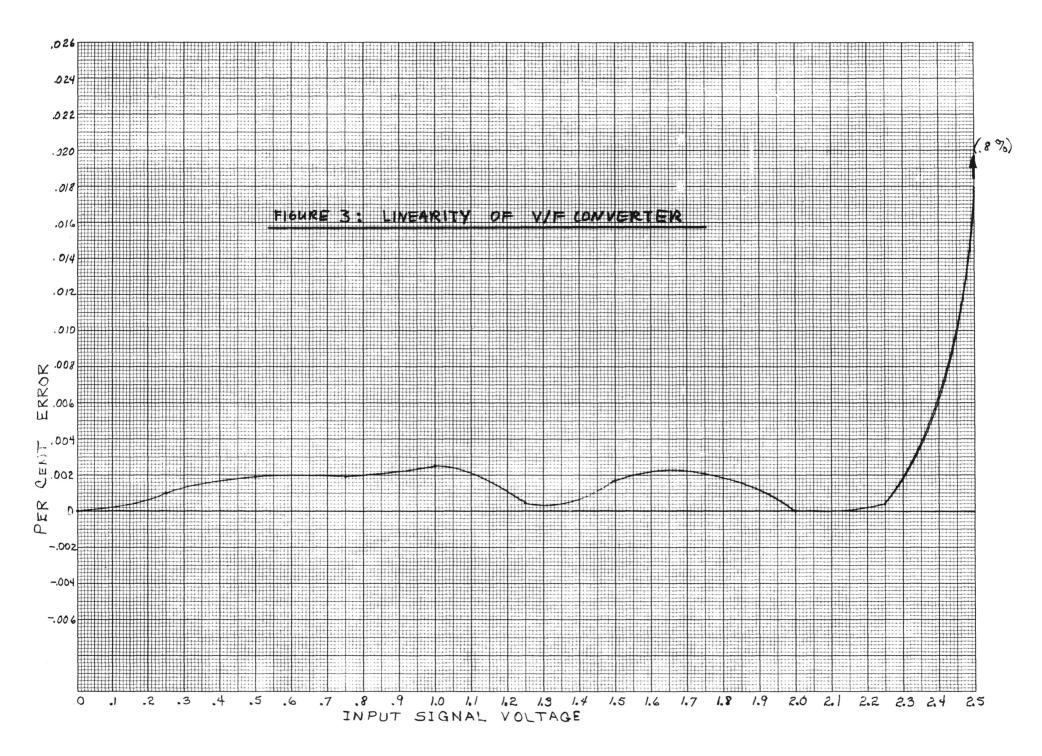

- Figure 3 Linearity of V/F converter

#### INTRODUCTION

A total power integrator was developed for Mark II terminals using a voltage to frequency converter and a binary converter as integrator. The integrator takes independent samples and has a time constant of 1 second. Linearity is excellent. Temperature drift is low enough for Mark II use and if needed can be improved by selecting operational amplifiers with lower drift and resistors with better stability. The integrator does not overflow or underflow when input voltages are excessive.

### SPECIFICATIONS

| Input amplitude: 0         | to +2V                                   |

|----------------------------|------------------------------------------|

| Input impedance: 10        | OK ohms                                  |

| Saturation of input amplif | ier: <u>+</u> 2.5V                       |

| Output: 12 binary bit      | S                                        |

| Low true TTL               | level                                    |

| Sink 0.4 mA                |                                          |

| 0 volts In $\rightarrow$   | 0 count Out                              |

| +2 volts In $\rightarrow$  | 4095 count Out                           |

| Integration time:          | l second                                 |

| External timing signal:    | lsecond positive pulse                   |

| Linearity:                 | <0.003% of measured value                |

| Temperature drift:         | 0.01% per °C estimated                   |

| Supply voltage:            | +15 VDC 7 mA -15 VDC 43 mA +5 VDC 210 mA |

|                            | All voltages <u>+</u> 0.5V               |

| Supply voltage rejection:  | +15V: 0.06% per volt                     |

|                            | -15V: 0.01% per volt                     |

#### CIRCUIT DESCRIPTION

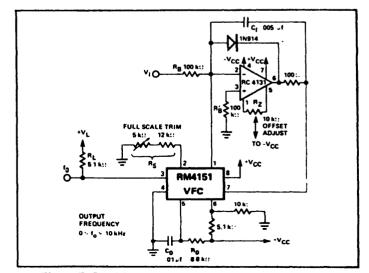

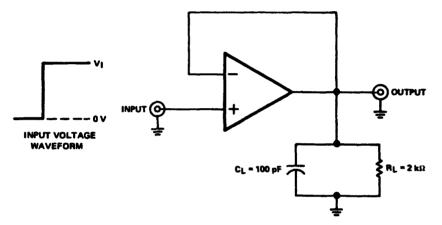

Total power input is first amplified and inverted by a 747 operational amplifier having a gain of -5.4. The output voltage ranging from 0 to -13.2Vis converted into a current of 0 to -0.125 mA. This current is then compared to the pulsed current output pin 1 of RM4151 averaged by capacitor 50 nF. The output of the comparator is applied to a VCO (pin 7 of RM4151). The output of the VCO is counted by a 4040 12 bit binary counter. Every second the count is latched into three 4 bit 4042 latches and then the counter is reset for the next integration. An overflow circuit of three 74C20 gates detects a count of 4095 and inhibits further counts. The counter therefore does not overflow.

#### CALIBRATION

- Apply +2V at input, connect counter at TP1. Adjust full scale trim for 4095 Hz.

- 2) Apply +10 mV at input, adjust zero trim for 20 Hz

- 3) Go back to 1).

### CONCLUSIONS

The linearity of the converter is excellent as shown in Figure 3. The measured variations are probably a result of the accuracy of the measurement set up of 0.002% and temperature drift of the circuit during measurement. We believe the linearity is better than shown in Figure 3. No measurement of temperature drift was attempted. It is primarily caused by temperature drift of the resistors and the 10 nF capacitor and secondarily by voltage offset drift of the 747 operational amplifier. Both can be improved by selecting more stable components.

FIGURE 1: CIRCUIT TOTAL POWER INTEGRATOR

| BW      | τ     | (Βτ) <sup>-1</sup> 2 | 3 (BT) -12 |

|---------|-------|----------------------|------------|

| 2 1/17- | 10    | 8                    | 8          |

| 2 MHz   | 10 ms | 0.7                  | 2.1        |

| 2 MHz   | 5 ms  | 1                    | 3          |

| 2 MHz   | l ms  | 1.8                  | 5.4        |

| 15 kHz  | 10 ms | 8                    | 24         |

| 15 kHz  | 5 ms  | 11.5                 | 34.6       |

| 15 kHz  | l ms  | 15                   | 45         |

|     | BW  | $(B\tau)^{-\frac{1}{2}}$<br>$\tau=5 ms$ | (Βτ) <sup>-1</sup> 2<br>τ=1 sec |

|-----|-----|-----------------------------------------|---------------------------------|

| 2   | MHz | <b>%</b><br>1.0                         | %<br>0.07                       |

|     | MHz | 1.4                                     | 0.10                            |

| 500 | kHz | 2.0                                     | 0.14                            |

| 250 | kHz | 2.8                                     | 0.20                            |

| 125 | kHz | 4.0                                     | 0.28                            |

| 62  | kHz | 5.6                                     | 0.40                            |

| 31  | kHz | 8.0                                     | 0.56                            |

| 15  | kHz | 11.3                                    | 0.80                            |

### Figure 2. S/N as function of $\tau$ and BW

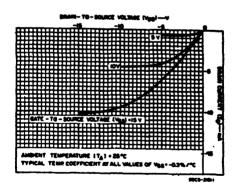

## CD4040A Types

# COS/MOS 12-Stage Ripple-Carry Binary Counter/Divider

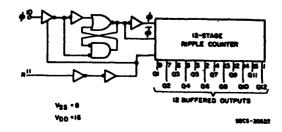

The RCA-CD4040A consists of an inputpulse-shaping circuit and 12 ripple-carry binary counter stages. Resetting the counter to the all-O's state is accomplished by a high-level on the reset line. A masterslave flip-flop configuration is utilized for each counter stage, The state of the counter is advanced one step in binary order on the negative-going transition of the input pulse. All inputs and outputs are fully buffered in

The CD4040A-series types are supplied in 16-lead hermetic dual-in-line ceramic packages (D,F, and Y suffixes), 16-lead dual-inline plastic package (E suffix), 16-lead ceramic flat package (K suffix), and in chip form (H suffix).

#### Features:

- Medium-speed operation . . . 5 MHz (typ.) input pulse rate at VDD - VSS = 10 V

- Low output impedance . . . 750  $\Omega$  (typ.) at VDD VSS = 10 V and VDS = 0.5 V

- Common reset

Fully static operation

- All 12 buffered outputs available

- Low-power TTL competible

- Quiescent current specified to 15 V

- Maximum input leakage current of 1 µA at 15 V (full package-temperature range)

- 1-V noise margin (full package-temperature range)

Applications:

- Frequency-dividing circuits

- Time-delay circuits Control counters

**RECOMMENDED OPERATING CONDITONS at T<sub>A</sub> = 25°C, Except as Noted:** For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges :

|                                                                               | <b></b> |      | LIN           | AITS      |       | 1   |  |

|-------------------------------------------------------------------------------|---------|------|---------------|-----------|-------|-----|--|

| CHARACTERISTIC                                                                | VDD     | •    | ,K,H<br>kages | E<br>Paci | UNITS |     |  |

|                                                                               | (V)     | Min. | Max.          | Min.      | Max.  | 1   |  |

| Supply Voltage Range (For T <sub>A</sub> = Full<br>Package-Temperature Range) |         | 3    | 12            | 3         | 12    | v   |  |

| Input Pulse Width, tw                                                         | 5       | 400  | -             | 500       | _     |     |  |

| input i dise motili, tw                                                       | 10      | 110  | -             | 125       | -     | ns  |  |

| Input-Pulse Frequency, fd                                                     | 5       | dc   | 1             | dc        | 0.9   | MHz |  |

| input and reducines, in                                                       | 10      | dc   | 3.5           | dc        | 3.25  |     |  |

| Input-Pulse Rise or Fall Time, t <sub>ro</sub> , t <sub>fo</sub>              | 5       | 15   | -             | 15        | -     |     |  |

|                                                                               | 10      | 15   | -             | 15        | [     | μs  |  |

|                                                                               | 5       | 1000 | -             | 1250      | -     |     |  |

| Reset Pulse Width, tw                                                         | 10      | 500  | -             | 600       | -     | ns  |  |

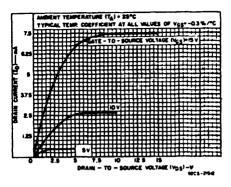

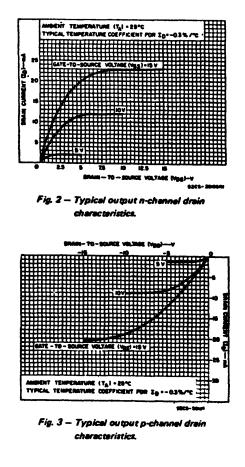

Fig.3 — Typical output p-channel drain characteristics.

Fig.4 - Functional diagram.

Fig.1 - Logic diagram of CD4040A input pulse shaper and 1 of 12 stages.

449

## CD4040A Types

| MAXIMUM RATINGS, Absolute-Maximum Values:                                                         |

|---------------------------------------------------------------------------------------------------|

| STORAGE-TEMPERATURE RANGE (T <sub>stg</sub> )                                                     |

| OPERATING TEMPERATURE RANGE (TA):                                                                 |

| PACKAGE TYPES D, F, K, H                                                                          |

| PACKAGE TYPES E, Y                                                                                |

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                                                    |

| (Voltages referenced to V <sub>SS</sub> Terminal)                                                 |

| POWER DISSIPATION PER PACKAGE (PD):                                                               |

| FOR T <sub>A</sub> = -40 to +60 <sup>0</sup> C (PACKAGE TYPES E, Y)                               |

| FOR TA= +60 to +85°C (PACKAGE TYPES E, Y) Derate Linearly at 12 mW/°C to 200 mW                   |

| FOR T <sub>A</sub> = -55 to +100 <sup>0</sup> C (PACKAGE TYPES D, F, K)                           |

| FOR T <sub>A</sub> = +100 to +125°C (PACKAGE TYPES D, F, K) Derate Linearly at 12 mW/°C to 200 mW |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                                          |

| FOR T <sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE (ALL PACKAGE TYPES) 100 mW                    |

| INPUT VOLTAGE RANGE, ALL INPUTS                                                                   |

| LEAD TEMPERATURE (DURING SOLDERING):                                                              |

| At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79 mm) from case for 10 s max +265°C               |

### STATIC ELECTRICAL CHARACTERISTICS

| [                              | _           |          | · · · · · | Limits at Indicated Temperatures (°C)         |                                         |        |           |           |        |       |       |             |

|--------------------------------|-------------|----------|-----------|-----------------------------------------------|-----------------------------------------|--------|-----------|-----------|--------|-------|-------|-------------|

| Characteristic                 | C           | onditi   | Dine      |                                               | -                                       | Packag |           |           | E,Y PM |       |       | Units       |

|                                | Vo          | Vini     | VDD       | -65                                           | +2                                      | _      | +125      | -40       | +2     |       | +85   |             |

|                                | (V)         | (V)      | (V)       | -00                                           |                                         | Limit  | T125      |           | Typ.   | Limit | 100   |             |

| Quiescent Device               | -           | -        | 5         | 15                                            | 0.5                                     | 15     | 900       | 50        | 1      | 50    | 700   |             |

| Current,                       | -           | -        | 10        | 25                                            | 1                                       | 25     | 1500      | 100       | 2      | 100   | 1400  | μA          |

| IL Max.                        | -           | -        | 15        | 50                                            | 2.5                                     | 50     | 2000      | 500       | 5      | 500   | 5000  |             |

| Output Voltage:                |             |          |           |                                               |                                         |        |           |           |        |       |       |             |

| Low-Level,                     | -           | 5        | 5         |                                               |                                         |        | yp.; 0.0  |           |        | -     |       |             |

| VOL                            | -           | 10       | 10        |                                               | 0 Typ.; 0.05 Max.                       |        |           |           |        |       | v     |             |

| High-Level                     | <b>–</b>    | 0        | 5         | 4.95 Min.; 5 Typ.<br>9.95 Min.; 10 Typ.       |                                         |        |           |           |        |       |       |             |

| VOH                            | -           | 0        | 10        |                                               |                                         | 9.9    | 5 Min.; 1 | O Typ.    | ·      |       |       |             |

| Noise Immunity:<br>Inputs Low, |             |          |           |                                               |                                         |        |           |           |        |       |       |             |

| VNL                            | <b>4</b> .2 |          | 5         |                                               | 1.5 Min.; 2.25 Typ.                     |        |           |           |        |       |       |             |

| Inputs High,                   | 0.8         | -        | 10<br>5   |                                               | 3 Min.; 4.5 Typ.<br>1.5 Min.; 2.25 Typ. |        |           |           |        |       |       | v           |

| VNH                            |             | 1-       | 10        |                                               |                                         | _      | lin.; 4.5 |           |        |       |       |             |

| Noise Margin:                  | <u> </u>    | <u> </u> |           |                                               |                                         | 51     |           | · • • p.  |        |       |       |             |

| Inputs Low,                    | 4.5         | -        | 5         |                                               |                                         |        | 1 Min     | •         |        |       |       |             |

| VNML                           | 9           | -        | 10        |                                               |                                         |        | 1 Min     | •         |        |       |       |             |

| Inputs High,                   | 0.5         | -        | 5         |                                               |                                         |        | 1 Min     |           |        | ····· |       | v           |

| VNMH                           | 1           | -        | 10        |                                               |                                         |        | 1 Min     |           |        |       |       |             |

| Output Drive                   |             |          |           |                                               |                                         |        |           |           | _      |       |       | <u>├</u> ── |

| Current:                       |             |          |           |                                               |                                         |        |           |           |        |       |       |             |

| N-Channel                      |             |          |           |                                               |                                         |        |           |           |        |       |       |             |

| (Sink).                        | 0.5<br>0.5  |          | 5         | 0.22                                          | 0.36                                    |        | 0.102     | 0.21      | 0.36   | 0.08  | 0.056 | l           |

| IDN Min.                       | 0.5         |          | 10        | 0.44                                          | 0.75                                    | 0.4    | 0.250     | 0.42      | 0.75   | 0.2   | 0.14  | mA          |

| P-Channel<br>(Source):         | 4.5         | l        | 5         |                                               |                                         |        |           |           |        |       |       |             |

| (Source):                      | 4.5         |          | 10        | -0.15                                         |                                         |        |           |           |        |       |       |             |

| L                              | <b></b>     | <u> </u> |           | -0.03 -0.5 -0.25 -0.175 -0.29 -0.5 -0.15 -0.1 |                                         |        |           |           |        |       |       |             |

| Input Leakage<br>Current,      | A           | ny inj   | put       | [                                             |                                         |        |           |           |        |       |       | l           |

| IL, IH                         | <u> </u>    | - 1      | 15        |                                               |                                         | ±10    | )-5 Typ   | ., ±1 Mai | ۲.     |       |       | M           |

|                                | L           | L        | L.,       | L                                             | ±10 <sup>-5</sup> Typ., ±1 Max.         |        |           |           |        |       |       |             |

Fig.5 — Minimum output n-channel drain characteristics.

Fig.6 — Minimum output p-channel drain characteristics.

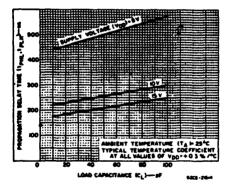

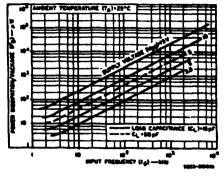

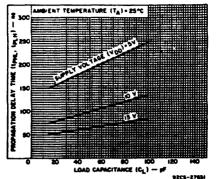

Fig.7 — Typical propagation delay time vs. load capacitance (per stage).

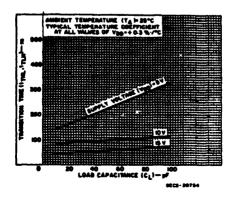

Fig.8 — Typical transition time vs. load capacitance.

## CD4040A Types

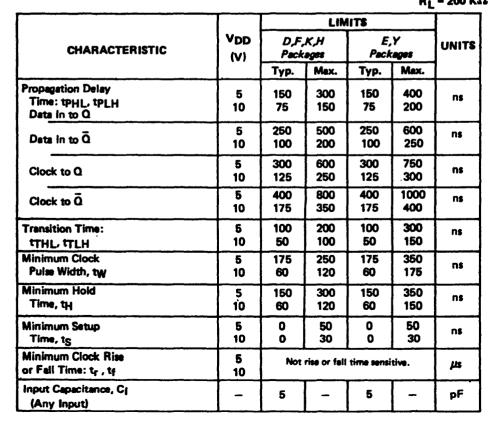

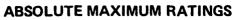

DYNAMIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C, input t<sub>7</sub>, t<sub>7</sub> = 20 ns, C<sub>L</sub> = 15 pF, R<sub>L</sub> = 200 k $\Omega$

|                                                       |                 |     | LIMITS |                     |      |      |                 |      |      |

|-------------------------------------------------------|-----------------|-----|--------|---------------------|------|------|-----------------|------|------|

| Characteristic                                        | Test Conditions |     |        | D,F,K,H<br>Packages |      |      | E,Y<br>Packages |      |      |

|                                                       |                 | (V) | Min.   | Typ.                | Max. | Min. | Тур.            | Mex. |      |

| Input-Pulse Operation                                 |                 |     |        |                     |      |      |                 |      |      |

| Propagation Delay<br>Time.                            |                 | 5   | -      | 450                 | 900  | -    | 450             | 950  |      |

| ፡ ነ™#,<br>፟፟፟፟፟፟፟፟፟፟፟፟<br>፟፟፟፟፟፟፟፟፟፟፟፟፟<br>፟፟፟፟፟፟፟፟፟፟ |                 | 10  | -      | 225                 | 450  | -    | 225             | 475  | ns   |

| Transition Time,                                      |                 | 5   | 1      | 150                 | 300  |      | 150             | 350  | ns   |

| THL TLH                                               |                 | 10  | 1      | 75                  | 150  | -    | 75              | 175  | ris. |

| Maximum Input-Pulse                                   |                 | 5   | 1      | 1.75                | -    | 0.9  | 1.75            | 1    | MHz  |

| Frequency, f <sub>ø</sub>                             |                 | 10  | 3,5    | 5                   | -    | 3.25 | 5               | -    | MITZ |

| Minimum Input-Puls*                                   | f=100 kHZ       | 5   | -      | 200                 | 400  | -    | 200             | 500  |      |

| Width, tw                                             |                 | 10  | -      | 75                  | 110  | 1    | 75              | 125  | ns   |

| Input-Pulse Rise &                                    |                 | 5   | -      | -                   | 15   | -    | -               | 15   |      |

| Fall Time, t <sub>rø</sub> , t <sub>fø</sub> A        |                 | 10  | 1      | 1                   | 7.5  | 1    | 1               | 7.5  | μs   |

| Average Input<br>Cepacitance, C                       | Any Input       |     | -      | 5                   | -    | -    | 5               | -    | pF   |

| Reset Operation                                       | Reset Operation |     |        |                     |      |      |                 |      |      |

| Propagation Delay                                     |                 | 5   | -      | 500                 | 1000 | -    | 500             | 1250 | ns   |

| Time, tPHL*                                           |                 | 10  | -      | 250                 | 500  | -    | 250             | 600  |      |

| Minimum Reset                                         |                 | 5   | -      | 500                 | 1000 | -    | 500             | 1250 | ns   |

| Pulse Width, tw                                       |                 | 10  | -      | 250                 | 500  | -    | 250             | 600  |      |

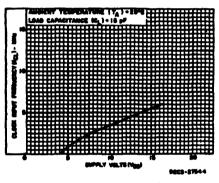

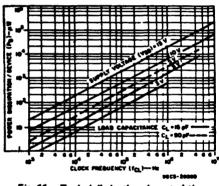

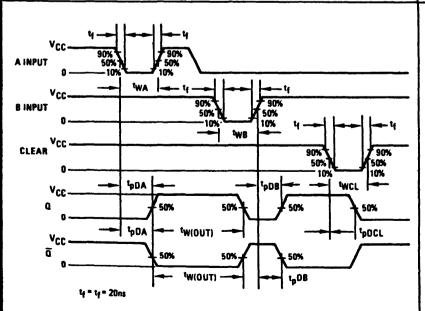

Fig. 9 - Typical dissipation characteristics.

Fig.10 - Typical input-pulse frequency vs. supply voltage.

- Measured from the 50% level of the negative clock edge to the 50% level of either the positive or negative edge of the Q1 output (pin 9); or measured from the negative edge of Q1 through Q11 outputs to the positive or negative edge of the next higher output.

- Maximum input rise or fall time for functional operation.

- Measured from the positive edge of the reset pulse to the negative edge of any output (Q1 to Q12).

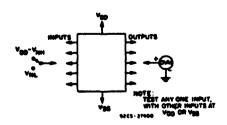

Fig. 11 - Noise-immunity test circuit.

Fig. 12 - Quiescent-device-current test circuit.

Fig. 13 - Input-leekage-current test circuit.

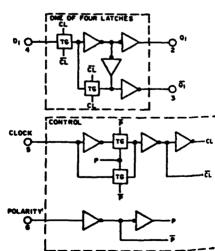

## **CD4042A Types**

# COS/MOS Quad Clocked "D" Latch

The RCA-CD4042A types contain four latch circuits, each strobed by a common clock. Complementary buffered outputs are available from each circuit. The impedance of the *n*- and *p*-channel output devices is balanced and all outputs are electrically identical.

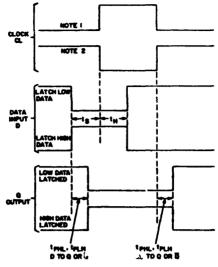

Information present at the data input is transferred to outputs Q and  $\overline{Q}$  during the CLOCK level which is programmed by the POLARITY input. For POLARITY = 0 the transfer occurs during the 0 CLOCK level and for POLARITY = 1 the transfer occurs during the 1 CLOCK level. The outputs follow the data input providing the CLOCK and POLARITY levels defined above are present. When a CLOCK transition occurs (positive for POLARITY = 0 and negative for POLARITY = 1) the information present at the input during the CLOCK transition is retained at the outputs until an opposite CLOCK transition occurs.

The CD4042A types are supplied in 16-lead hermetic dual-in-line ceramic packages (D, F, and Y suffixes), 16-lead dual-in-line plastic packages (E suffix), 16-lead ceramic flat packages (K suffix), and in chip form (H suffix).

MAXIMUM RATINGS, Absolute-Maximum Values:

| STORAGE-TEMPERATURE RANGE (T <sub>sta</sub> )                                                          |

|--------------------------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE RANGE (TA):                                                                      |

| PACKAGE TYPES D, F, K, H                                                                               |

| PACKAGE TYPES E,Y                                                                                      |

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                                                         |

| (Voltages referenced to V <sub>SS</sub> Terminel):                                                     |

| POWER DISSIPATION PER PACKAGE (PD):                                                                    |

| FOR TA = -40 to +60°C (PACKAGE TYPES E,Y)                                                              |

| FOR T <sub>A</sub> = +60 to +85°C (PACKAGE TYPES E, Y) Dense Linearly at 12 mW/ $^{\circ}$ C to 200 mW |

| FOR $T_A = -55$ to +100°C (PACKAGE TYPES D. F. K)                                                      |

| FOR T <sub>A</sub> = +100 to +125°C (PACKAGE TYPES D, P, K) Derate Linearly at 12 mW/°C to 200 mW      |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                                               |

| FOR T <sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE (ALL PACKAGE TYPES)                                |

| INPUT VOLTAGE RANGE, ALL INPUTS                                                                        |

| LEAD TEMPERATURE (DURING SOLDERING):                                                                   |

| At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79 mm) from case for 10 s mex                           |

### DYNAMIC ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C, Input $t_r$ , $t_f$ = 20 ns, C<sub>L</sub> = 15 pF, R<sub>1</sub> = 200 K $\Omega$

| 4 0<br>7 0<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>1 |            |  |  |  |

|-----------------------------------------------------------------------|------------|--|--|--|

| V000-                                                                 | 98C3-88+9+ |  |  |  |

| CD4042A<br>FUNCTIONAL DIAGRAM                                         |            |  |  |  |

### Features:

- Clock polarity control

- Q and Q outputs

- Common clock

- Low power TTL competible

- Quiescent current specified to 15 V

- Maximum input leakage of 1 µA at 15 V (full package-temperature range)

- I-V noise margin (full package-temperatun range)

### Applications:

- Buffer storage

- Holding register

- General digital logic

12CS - 20190

| CLOCK  | POLARITY | ٩     |

|--------|----------|-------|

| 0      | 0        | D     |

|        | 0        | LATCH |

| 1      | 1        | D     |

| $\sim$ | 1        | LATCH |

Fig. 1 – Logic block diagram & truth table.

## CD4042A Types

**RECOMMENDED OPERATING CONDITIONS at T<sub>A</sub> = 25°C, Except as Noted.** For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                                   | V <sub>DD</sub><br>(V) | D,F,K,H<br>Packages              |      | E,Y<br>Packages |      | UNITS |

|----------------------------------------------------------------------------------|------------------------|----------------------------------|------|-----------------|------|-------|

|                                                                                  |                        | Min.                             | Max. | Min.            | Max. | 1     |

| Supply-Voltage Range<br>(For T <sub>A</sub> = Full Package<br>Temperature Range) | -                      | 3                                | 12   | 3               | 12   | v     |

| Clock Pulse<br>Width, tw                                                         | 5<br>10                | 350<br>175                       | -    | 250<br>120      | =    | ns    |

| Setup Time, ts                                                                   | 5<br>10                | 50<br>30                         | -    | 50<br>30        | -    | ns    |

| Hold Time, t <sub>H</sub>                                                        | 5<br>10                | 350<br>150                       | -    | 300<br>120      | =    | ns    |

| Clock Rise or Fall<br>Time: t <sub>r</sub> , t <sub>f</sub>                      | 5<br>10                | Not rise or fall time sensitive. |      |                 |      | μs    |

### STATIC ELECTRICAL CHARACTERISTICS

| [                                                |     |           |     |        | 1 Junio             |                                                                                                                | iceted '           | Tamp   |                    | - CCL |       | <u> </u>   |  |

|--------------------------------------------------|-----|-----------|-----|--------|---------------------|----------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|-------|-------|------------|--|

|                                                  | Co  | nditic    |     | ~      | K,F,H               |                                                                                                                |                    |        |                    |       |       |            |  |

| Characteristic                                   | Vo  | Vin       | VDD |        | +2                  | the second s |                    |        | E,Y Package<br>+25 |       | •     | Units      |  |

|                                                  | (V) | (V)       | (V) | ~55    | Typ.                | Limit                                                                                                          | +125               | 40     | Typ. Limit         |       | +85   |            |  |

| Quiescent Device                                 | 1   | -         | 5   | 1      | 0.005               | 1                                                                                                              | 60                 | 10     | 0.01               | 10    | 140   |            |  |

| Current, I Max.                                  | 1   | -         | 10  | 2      | 0.005               | 2                                                                                                              | 120                | 20     | 0.02               | 20    | 280   | <b>μ</b> Α |  |

|                                                  | 1   | -         | 15  | 25     | 0.25                | 25                                                                                                             | 1000               | 250    | 2.5                | 250   | 2500  |            |  |

| Output Voltage:<br>Low-Level,                    | -   | 0,5       | 5   |        |                     | 0                                                                                                              | Тур.; О.           | 05 M   | IX.                |       |       |            |  |

| VOL                                              | -   | 0,10      | 10  |        |                     | 0                                                                                                              | Тур.; О            | .05 M  | BX.                |       |       |            |  |

| High Level,                                      | ۱   | 0,5       | 5   |        |                     | 4.                                                                                                             | 95 Min.            | ;5 Ty  | р.                 |       |       |            |  |

| VOH                                              | -   | 0,10      | 10  |        |                     | 9.                                                                                                             | 95 Min.            | ; 10 T | yp.                |       |       |            |  |

| Noise Immunity:<br>Inputs Low,                   | 4.2 | -         | 5   |        |                     | 1.                                                                                                             | 5 Min.;            | 2.25   | Гур.               |       |       |            |  |

| VNL                                              | 9   | -         | 10  |        | 3 Min.; 4.5 Typ.    |                                                                                                                |                    |        |                    |       |       |            |  |

| Inputs High,                                     | 0.8 | -         | 5   |        | 1.5 Min.; 2.25 Typ. |                                                                                                                |                    |        |                    |       |       |            |  |

| VNH                                              | 1   | -         | 10  |        |                     | 3                                                                                                              | Min.; 4.           | 5 Тур  | ).                 |       |       |            |  |

| Noise Margin:<br>Inputs Low,                     | 4.5 | -         | 5   | 1 Min. |                     |                                                                                                                |                    |        |                    |       |       |            |  |

| VNML                                             | 9   | -         | 10  |        | 1 Min.              |                                                                                                                |                    |        |                    |       |       |            |  |

| Inputs High,                                     | 0.5 | -         | 5   |        |                     |                                                                                                                | 1 M                | in.    |                    |       |       | ]          |  |

| VNMH                                             | 1   | - 1       | 10  |        |                     |                                                                                                                | 1 M                | lin.   |                    |       |       | 1          |  |

| Output Drive<br>Current:<br>n-Channel<br>(Sink), | 0.5 | -         | 5   | 0.5    | 1                   | 0.4                                                                                                            | 0.27               | 0.24   | 1                  | 0.2   | 0.18  |            |  |

| I <sub>D</sub> N Min.                            | 0.5 | -         | 10  | 1.25   | 2                   | 1                                                                                                              | 0.7                | 0.6    | 2                  | 0.5   | 0.45  | mA         |  |

| p-Channel                                        | 4,5 | -         | 5   | -0.45  | -1                  | -0.35                                                                                                          | -0.25              | ·0.2   | •1                 | 0.175 | -0.15 |            |  |

| (Source),<br>IDP Min.                            | 9.5 | -         | 10  | -1.15  | -2                  | •0.9                                                                                                           | ·0.6               | -0.34  | •2                 | -0.45 | -0.4  |            |  |

| Input Leakage<br>Current,<br>IIL, IIH Max.       |     | ny<br>put | 15  |        |                     | ±                                                                                                              | 10- <sup>5</sup> T | yp.; 1 | Max.               |       |       | μΑ         |  |

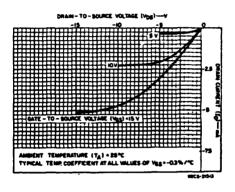

Fig. 5 - Minimum p-channel drain characteristics.

## CD4042A Types

I. FOR POSITIVE CLOCK EDGE, HIPUT DATA IS LATCHED WHEN POLANITY IS LOW.

2. FOR NEGATIVE CLOCK EDGE, INPUT DATA IS LATCHED WHEN POLARITY IS NON. \$2C\$-27630

Fig. 6 - Dynamic test parameters.

Fig. 11 - Typical dissipation characteristics.

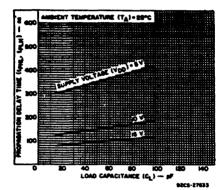

Fig. 7 — Typical propagation delay time vs. load capacitance- data to Q.

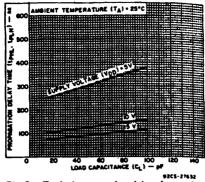

Fig. 9 — Typical propagation delay time vs. load capacitance - clock to Q.

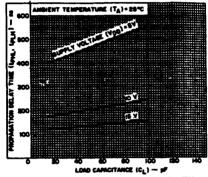

Fig. 8 - Typical propagation delay time vs. load capacitance — date to Q.

a2CB-2763 Fig. 10 - Typical propagation delay time vs. load capacitance – clock to  $\overline{Q}$ .

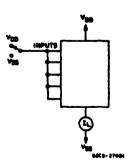

Fig. 12 - Quiescent device current test circuit.

Fig. 13- Noise immunity test circuit.

Fig. 14 - Input leskage current test circuit.

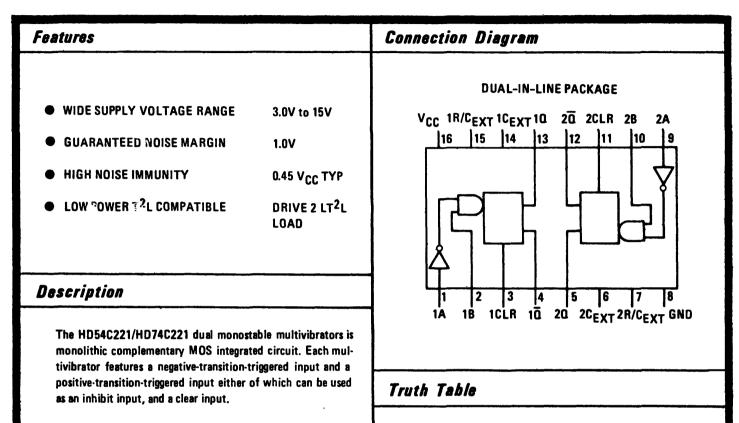

## HD-54C221/HD-74C221 Dual Monostable Multivibrator

Once fired, the output pulses are independent of further transitions of the A and B inputs and are a function of the external timing components  $C_{EXT}$  and  $R_{EXT}$ . The pulse width

is stable over a wide range of temperature and V<sub>CC</sub>. Pulse stability will be limited by the accuracy of external timing components. The R<sub>EXT</sub> ranges from 10k to 100k. Throughout these ranges the pulse width is approximately defined by the relationship tw(OUT)  $\approx$  C<sub>EXT</sub> R<sub>EXT</sub>.

| ſ | 1     | оит | PUTS |          |   |

|---|-------|-----|------|----------|---|

| I | CLEAR | Α   | B    | ۵        | ā |

|   | L     | х   | x    | L        | н |

|   | x     | н   | x    | L        | Н |

|   | x     | x   | L    | L        | н |

|   | н     | Ļ   | ł    | <b>Л</b> | J |

|   | н     | †   | Н    | Л        | ប |

= Transition from Low to High

Transition from High to Low

Cone High Level Pulse

- One Low Level Pulse

-----

See CMOS Packaging Section 5 for complete package information. This device is available in Ceramic Dual In-Line and Flat Packs.

See package outline Code 1W and Code 9L.

X = irrelevant

H = High Level

Package

| Voltage at any Pin          |           | -0.3V to V <sub>CC</sub> +0.3V            | Package Dissipation                   | 500mW       |

|-----------------------------|-----------|-------------------------------------------|---------------------------------------|-------------|

| Oparating Temperature Ranga | HD-54C221 | -55°C to +125°C                           | Operating VCC Range                   | 4.5V to 15V |

|                             | HD-74C221 | -40°C to +85°C                            | Absolute Maximum VCC                  | 16V         |

| Storaga Tamparatura Range   |           | -65 <sup>0</sup> C to +150 <sup>0</sup> C | Lead Tamperatura (Soldering, 10 Sec.) | 300°C       |

ELECTRICAL CHARACTERISTICS Min/Max limits apply across temperature range, unless otherwise noted.

|     | PARAMETER                            | SYMBOL               | MIN.                     | TYP.   | MAX.       | UNITS  | CONDITIONS                                                                                                    |

|-----|--------------------------------------|----------------------|--------------------------|--------|------------|--------|---------------------------------------------------------------------------------------------------------------|

|     | CMOS TO CMOS                         |                      |                          |        |            |        |                                                                                                               |

|     | Logical "1" Input Voltaga            | VIN(1)               | 3.5<br>8.0               |        |            | v<br>v | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V                                                               |

|     | Logical "O" Input Voltaga            | VIN(0)               |                          |        | 1.5<br>2.0 | v<br>v | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V                                                               |

|     | Logical "1" Output Voltage           | VOut(1)              | 4.5<br>9.0               |        |            | v<br>v | V <sub>CC</sub> = 5.0V, 1 <sub>0</sub> = -10 A<br>V <sub>CC</sub> = 10V, 1 <sub>0</sub> = -10 A               |

|     | Logical "O" Output Voltage           | V <sub>Out</sub> (0) |                          |        | 0.5<br>1.0 | v<br>v | V <sub>CC</sub> = 5.0V, I <sub>O</sub> = +10 A<br>V <sub>CC</sub> = 10V, I <sub>O</sub> = +10 A               |

|     | Logical "1" Input Current            | <sup>1</sup> IN (1)  |                          | 0.005  | 1.0        | A      | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 15V                                                                  |

|     | Logical "O" Input Current            | <sup>1</sup> IN (0)  | -1.0                     | -0.005 |            | A      | V <sub>CC</sub> = 15V, V <sub>IN</sub> = 0V                                                                   |

| .c. |                                      |                      |                          | 0.05   | 300        | A      | V <sub>CC</sub> = 15V, R <sub>Ext.</sub> =<br>Q1, Q2 = Logic 0 (Note 3)                                       |

|     | Supply Current                       | ICC                  |                          | 15     |            | mA     | V <sub>CC</sub> = 15V, Q1 = Logic 1<br>Q2 = Logic 0                                                           |

|     |                                      |                      |                          | 2      |            |        | V <sub>CC</sub> = 5.0V, Q1 = Logic 1<br>Q2 = Logic 0                                                          |

|     | CMOS/LPTTL INTERFACE                 |                      |                          |        |            |        |                                                                                                               |

|     | Logical "1" Input Voltage            | VIN (1)              | V <sub>CC</sub> -<br>1.5 |        |            | V      | 54C, V <sub>CC</sub> = 4.5V<br>74C, V <sub>CC</sub> = 4.75V                                                   |

|     | Logical "O" Input Voltage            | VIN (0)              |                          |        | 0.8<br>0.8 | v<br>v | 54C, V <sub>CC</sub> = 4.5V<br>74C, V <sub>CC</sub> = 4.75V                                                   |

|     | Logical "1" Output Voltage           | V <sub>Out(1)</sub>  | 2.4<br>2.4               |        |            | v<br>v | 54C, V <sub>CC</sub> = 4.5V, I <sub>O</sub> = -360 A<br>74C, V <sub>CC</sub> = 4.75V, I <sub>O</sub> = -360 A |

|     | Logical "O" Output Voltaga           | V <sub>Out</sub> (0) |                          |        | 0.4<br>0.4 | v<br>v | 54C, V <sub>CC</sub> = 4.5V, I <sub>O</sub> = 360 A<br>74C, V <sub>CC</sub> = 4.75V, I <sub>O</sub> = 360 A   |

|     | OUTPUT DRIVE                         |                      |                          |        |            |        |                                                                                                               |

|     | Output Source Current<br>(P-Channel) | ISource              | -1.75                    | 3.3    |            | mA     | VCC = 5.0V, V <sub>Out</sub> = 0V<br>T <sub>A</sub> = 25°C                                                    |

|     | Output Source Current<br>(P-Channel) | ISource              | -8.0                     | -15    |            | mА     | V <sub>CC</sub> = 10V, V <sub>Out</sub> = 0V<br>T <sub>A</sub> = 25 <sup>o</sup> C                            |

|     | Output Sink Current<br>(N-Channel)   | ISink                | 1.75                     | 3.6    |            | mA     | VCC = 5.0V, VOut = VCC<br>TA = 25°C                                                                           |

|     | Output Sink Currant                  | <sup> </sup> Sink    | 8.0                      | 16     |            | mA     | V <sub>CC</sub> = 10V, V <sub>Out</sub> = V <sub>CC</sub><br>T <sub>A</sub> = 25 <sup>o</sup> C               |

<u>ග</u> උ

### **ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}C$ ,  $C_L = 50pF$ , Unless Otherwise Specified.

|      | PARAMETER                                                    | SYMBOL              | MIN.                                                      | TYP.       | MAX.                                       | UNITS                                        | CONDITIONS                                                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------------------|---------------------|-----------------------------------------------------------|------------|--------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Propagation Delay From Trigger<br>Input (A,B) to Output Q, Q | <sup>t</sup> PD A,B |                                                           | 250<br>120 | 500<br>250                                 | ns<br>ns                                     | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V                                                                                                                                                                                                                                             |

|      | Propagation Delay from Clear<br>Input (CL) to Output Q, Q    | <sup>t</sup> DP CL  |                                                           | 250<br>120 | 500<br>250                                 | ns<br>Rs                                     | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V                                                                                                                                                                                                                                             |

|      | Minimum Trigger Input (A,B)<br>Pulse Width                   | <sup>t</sup> w(A,B) | 150<br>70                                                 | 65<br>30   |                                            | ns<br>ns                                     | VCC = 5.0V<br>VCC = 10V                                                                                                                                                                                                                                                                     |

|      | Minimum Clear Input (CL) Pulse<br>Width                      | <sup>t</sup> w(CL)  | 150<br>70                                                 | 65<br>30   |                                            | ns<br>ns                                     | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V                                                                                                                                                                                                                                             |

| A.C. | ቢ or Ц Output Pulse Width                                    | <sup>t</sup> w(Qut) | 250<br>250<br>250<br>9.3<br>9<br>8.5<br>900<br>900<br>900 |            | 12.3<br>11<br>10.5<br>1200<br>1100<br>1100 | ns<br>ns<br>ns<br>S<br>S<br>S<br>S<br>S<br>S | V <sub>CC</sub> = 5.0V, R = 10K<br>V <sub>CC</sub> = 10V, C = 0pF<br>V <sub>CC</sub> = 15V<br>V <sub>CC</sub> = 5.0V, R = 10K<br>V <sub>CC</sub> = 10V, C = 1000pF<br>V <sub>CC</sub> = 15V<br>V <sub>CC</sub> = 5.0V, R = 10K<br>V <sub>CC</sub> = 10V, C = 0.1 F<br>V <sub>CC</sub> = 15V |

|      | Output Duty Cycle                                            |                     |                                                           |            | 90<br>95                                   | *<br>*                                       | R = 10K, C = 1000pF<br>R = 10K, C = 0.1 F                                                                                                                                                                                                                                                   |

|      | Input Capacitance                                            | CiN                 |                                                           | 25<br>5    |                                            | pF<br>pF                                     | R/C <sub>Ext</sub> Input<br>Any Other Input                                                                                                                                                                                                                                                 |

NOTES: 1. "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

- 2. Capacitance is guaranteed by periodic testing.

- 3. In standby (Q = Logic 0) the power dissipated equals the leakage current plus VCC/RExt.

# Switching Time Waveforms

### Typical Characteristics

NOTE: Power shown is measured with both one shots switching together and REXT = 100K.

### **GENERAL DESCRIPTION**

The RC4151 and RM4151 provide a simple low-cost method of A/D conversion. They have all the inherent advantages of the voltage-to-frequency conversion technique. The output of RC4151/RM4151 is a series of pulses of constant duration. The frequency of the pulses is proportional to the applied input voltage. These converters are designed for use in a wide range of data conversion and remote sensing applications.

### **DESIGN FEATURES**

- Single Supply Operation (+8V to +22V)

- Pulse Output Compatible With All Logic Forms

- Programmable Scale Factor (K)

- Linearity ±0.05% typical precision mode

- Temperature stability ±100% ppm/°C typical

- High Noise Rejection

- Inherent Monotonicity

- Easily Transmittable Output

- Simple Full Scale Trim

- Single-Ended Input, Referenced to Ground

- Also Provides Frequency-to-Voltage Conversion

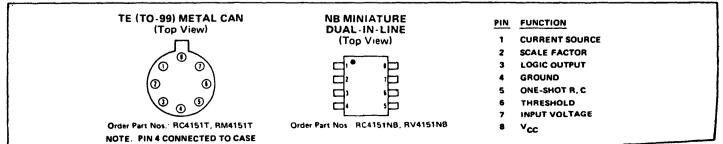

### **CONNECTION INFORMATION**

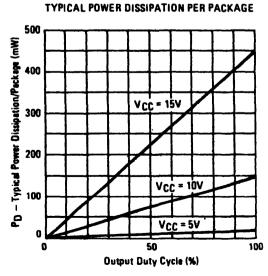

## SCHEMATIC DIAGRAM

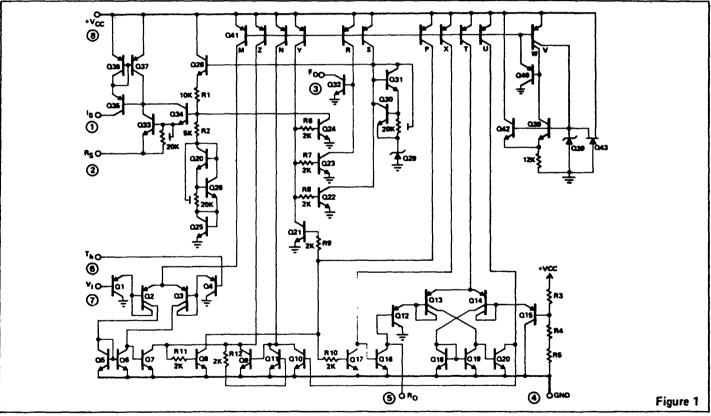

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltages       +8.0 to +22V         Output Sink Current       20mA         Internal Power Dissipation       500mW         Input Voltage       -0.2V to +V <sub>CC</sub> Output Short Circuit to Ground       Continuous | Storage Temperature Range           RM4151         -65°C to +150°C           RV4151         -55°C to +125°C           RC4151         -55°C to +125°C           RC4151         -55°C to +125°C           Operating Temperature Range |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                | RM4151       -55°C to +125°C         RV4151       -40°C to +85°C         RC4151       0°C to +70°C                                                                                                                                  |

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = +15V$ , $T_A = +25^{\circ}C$ , unless otherwise specified)

| PARAMETER                                      | CONDITIONS                                                   | MIN  | ТҮР        | MAX      | UNITS  |

|------------------------------------------------|--------------------------------------------------------------|------|------------|----------|--------|

| Supply Current                                 | 8V < V <sub>CC</sub> < 15V                                   | 2.0  | 3.5        | 6.0      | mA     |

|                                                | 15V < V <sub>CC</sub> < 22V                                  | 2.0  | 4.5        | 7.5      | mA     |

| Conversion Accuracy<br>Scale Factor            | Circuit Figure 3, VI = 10V<br>RS = 14.0k                     | 0.90 | 1.00       | 1.10     | kHz/V  |

| Drift with Temperature                         | Circuit Figure 3, VI = 10V                                   | -    | ±100       |          | ppM/ºC |

| Drift with VCC                                 | Circuit Figure 3, $V_I = 1.0V$<br>8V < V <sub>CC</sub> < 18V | -    | 0.2        | 1.0      | %/V    |

| Input Comparator<br>Offset Voltage             |                                                              | _    | 5          | 10       | mV     |

| Offset Current                                 |                                                              |      | ±50        | ±100     | nA     |

| Input Bias Current                             |                                                              | -    | -100       | -300     | nA     |

| Common Mode Range (Note 1)                     |                                                              | 0    | 0 to VCC-2 | Vcc -3.0 | V      |

| One-Shot<br>Threshold Voltage, Pin 5           |                                                              | 0.63 | .667       | 0.70     | × Vcc  |

| Input Bias Current, Pin 5                      |                                                              |      | -100       | -500     | nA     |

| Reset VSAT                                     | Pin 5, 1 = 2.2mA                                             | -    | 0.15       | 0.50     | V      |

| Current Source<br>Output Current (Rs = 14.0kΩ) | Pin 1, Figure 2, V = 0                                       | -    | 138.7      | _        | μΑ     |

| Change with Voltage                            | Pin 1, V = 0V to V = 10V                                     |      | 1.0        | 2.5      | μΑ     |

| Off Leakage                                    | Pin 1, V = 0V                                                |      | 1          | 50.0     | nA     |

| Reference Voltage                              | Pin 2, Figure 2                                              | 1.70 | 1.9        | 2.08     | v      |

| Logic Output<br>VSAT                           | Pin 3, I = 3.0mA                                             |      | 0.15       | 0.50     | v      |

| VSAT                                           | Pin 3, I = 2.0mA                                             |      | 0.10       | 0.30     | v      |

| Off Leakage                                    |                                                              |      | .1         | 1.0      | μΑ     |

Note 1: Input Common Mode Range includes ground.

### **PRINCIPLE OF OPERATION**

### Single Supply Mode Voltage-to-Frequency Conversion

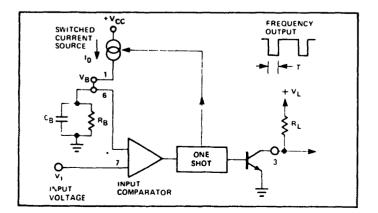

In this application the RC4151/RM4151 functions as a standalone voltage to frequency converter operating on a single positive power supply. Refer to Figure 2, the simplified block diagram. The RC/RM4151 contains a voltage comparator, a one-shot, and a precision switched current source. The voltage comparator compares a positive input voltage applied at pin 7 to the voltage at pin 6. If the input voltage is higher, the comparator will fire the one-shot. The output of the one-shot is connected to both the logic output and the precision switched current source. During the one-shot period. T. the logic output will go low and the current source will turn on with current I. At the end of the one-shot period the logic output will go high and the current source will shut off. At this time the current source has injected an amount of charge  $Q = I_0 T$  into the network RB-CB. If this charge has not increased the voltage VB such that  $V_B > V_I$ , the comparator again fires the one-shot and the current source injects another lump of charge, Q, into the R<sub>B</sub>-C<sub>B</sub> network. This process continues until  $V_B > V_I$ . When this condition is achieved the current source remains off and the voltage  $V_B$  decays until  $V_B$  is again equal to  $V_1$ . This completes one cycle. The VFC will now run in a steady state mode. The current source dumps lumps of charge into the capacitor  $C_B$  at a rate fast enough to keep  $V_B \ge V_I$ . Since the discharge rate of capacitor  $C_B$  is proportional to  $V_B/R_B$ , the frequency at which the system runs will be proportional to the input voltage.

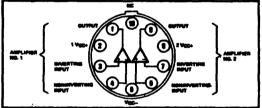

The 4151 VFC is easy to use and apply if you understand the operation of it through the block diagram, Figure 2. Many users, though, have expressed the desire to understand the workings of the internal circuitry. Figure 1 shows the schematic of the 4151. The circuit can be divided into five sections: the internal biasing network, input comparator, one-shot, voltage reference, and the output current source.

The internal biasing network is composed of Q39-Q43. The Nchannel FET Q43 supplies the initial current for zener diode Q39. The NPN transistor Q38 senses the zener voltage to derive the current reference for the multiple collector current source Q41. This special PNP transistor provides active pull-up for all of the other sections of the 4151.

Figure 2. Simplified Block Diagram, Single Supply Mode

The input comparator section is composed of Q1-Q7. Lateral PNP transistors Q1-Q4 form the special ground-sensing input which is necessary for VFC operation at low input voltages. NPN transistors Q5 and Q6 convert the differential signal to drive the second gain stage Q7. If the voltage on input pin 7 is less than that on threshold pin 6, the comparator will be off and the collector of Q7 will be in the high state. As soon as the voltage on pin 7 exceeds the voltage on pin 6, the collector of Q7 will go low and trigger the one-shot.

The one-shot is made from a voltage comparator and an R-S latch. Transistors Q12-Q15 and Q18-Q20 form the comparator, while Q8-Q11 and Q16-Q17 make up the R-S latch. One latch output, open-collector reset transistor Q16, is connected to a comparator input and to the terminal, pin 5. Timing resistor RO is tied externally from pin 5 to +VCC and timing capacitor CO is tied from pin 5 to ground. The other comparator input is tied to a voltage divider R3-R5 which sets the comparator threshold voltage at 0.667 VCC. One-shot operation is initiated when the collector of Q7 goes low and sets the latch. This causes Q16 to turn off, releasing the voltage at pin 5 to charge exponentially towards  $+V_{CC}$  through RO. As soon as this voltage reaches 0.667 VCC, comparator output Q20 will go high causing Q10 to reset the latch. When the latch is reset, Q16 will discharge CO to ground. The one-shot has now completed its function of creating a pulse of period T = 1.1RO CO at the latch output, Q21. This pulse is buffered through Q23 to drive the open-collector logic circuit transistor Q32. During the one-shot period the logic output will be in the low state. The one-shot output is also used to switch the reference voltage by Q22 and Q24. The low T.C. reference voltage is derived from the combination of a 5.5V zener diode with resistor and diode level shift networks. A stable 1.89 volts is developed at pin 2, the emitter of Q33.

Connecting the external current-setting resistor  $R_S = 14.0\Omega$ from pin 2 to ground gives  $135\mu$ A from the collectors of Q33 and Q34. This current is reflected in the precision current mirror Q35-Q37 and produces the output current IQ at pin 1. When the R-S latch is reset, Q22 and Q24 will hold the reference voltage off, pin 2 will be at 0V, and the current will be off. During the one-shot period T, the latch will be set, the voltage of pin 2 will go to 1.89V, and the output current will be switched on.

### TYPICAL APPLICATIONS

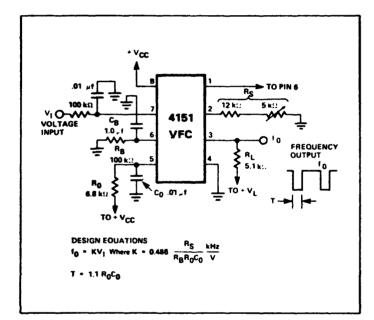

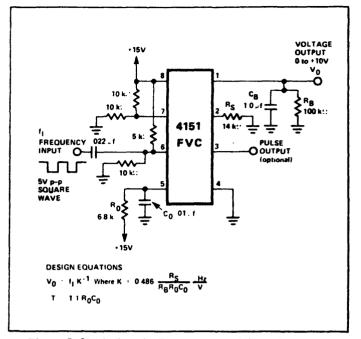

### Single Supply Voltage-to-Frequency Converter

Figure 3 shows the simplest type of VFC that can be made with the 4151. Input voltage range is from 0 to +10V, and output frequency is from 0 to 10kHz. Full scale frequency can be tuned by adjusting RS, the output current set resistor. This circuit has the advantage of being simple and low in cost, but it suffers from inaccuracy due to a number of error sources. Linearity error is typically 1%. A frequency offset will also be introduced by the input comparator offset voltage. Also, response time for this circuit is limited by the passive integration network RB CB. For the component values shown in Figure 3, response time for a step change input from 0 to +10V will be 135msec. For applications which require fast response time and high accuracy, use the circuits of Figure 4 and 5.

Figure 3. Single Supply Voltage-to-Frequency Converter

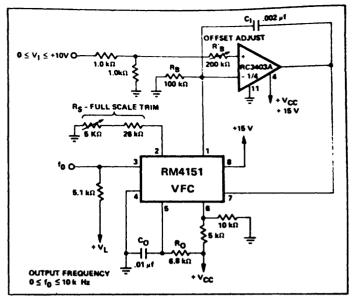

### Precision VFC with Single Supply Voltage

For applications which requrie a VFC which will operate from a single positive supply with positive input voltage, the circuit of Figure 4 will give greatly improved linearity, frequency offset, and response time. Here, an active integrator using one section of the RC3403A quad ground-sensing op-amp has replaced the Rg-Cg network in Figure 3. Linearity error for this circuit is due only to the 4151 current source output conductance. Frequency offset is due only to the op-amp input offset and can be nulled to zero by adjusting Rg. This technique uses the op-amp bias current to develop the null voltage, so an opamp with stable bias current, like the RC3403A, is required.

Figure 4. Precision Voltage-to-Frequency Converter Single Supply

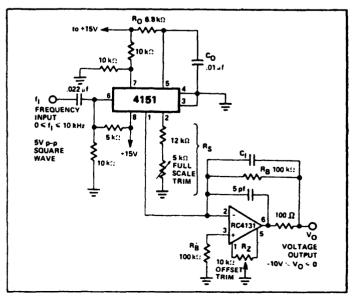

### Precision Voltage-to-Frequency Converter

In this application (Figure 5) the 4151 VFC is used with an operational amplifier integrator to provide typical linearity of 0.05% over the range of 0 to -10V. Offset is adjustable to zero. Unlike many VFC designs which lose linearity below 10mV, this circuit retains linearity over the full range of input voltage, all the way to 0V.

Trim the full scale adjust pot at VI = -10V for an output frequency of 10kHz. The offset adjust pot should be set for 10Hz with an input voltage of -10mV.

Figure 5. Precision Voltage-to-Frequency Converter

The 4131 operational amplifier integrator improves linearity of this circuit over that of Figure 3 by holding the output of the source, Pin 1, at a constant OV. Therefore linearity error due to the current source output conductance is eliminated. The diode connected around the op-amp prevents the voltage at 4151 pin 7 from going below 0. Use a low-leakage diode here, since any leakage will degrade the accuracy. This circuit can be operated from a single positive supply if an RC3403A ground-sensing op-amp is used for the integrator. In this case, the diode can be left out. Note that even though the circuit itself will operate from a single supply, the input voltage is necessarily negative. For operation above 10kHz, bypass 4151 pin 6 with  $0.01\mu f$ .

### Comparison of Voltage-to-Frequency Applications Circuits

Table 1 compares the VFC applications circuits for typical linearity, frequency offset, response time for a step input from 0 to 10 volts, sign of input voltage, and whether the circuit will operate from a single positive supply or split supplies.

Table 1

|                  | Figure 3 | Figure 4 | Figure 5 |  |  |  |  |  |  |  |

|------------------|----------|----------|----------|--|--|--|--|--|--|--|

| Linearity        | 1%       | 0.2%     | 0.05%    |  |  |  |  |  |  |  |

| Frequency Offset | +10Hz    | 0        | 0        |  |  |  |  |  |  |  |

| Response Time    | 135msec  | 10µsec   | 10µsec   |  |  |  |  |  |  |  |

| Input Voltage    | +        | +        | -        |  |  |  |  |  |  |  |

| Single Supply    | yes      | yes      | yes      |  |  |  |  |  |  |  |

| Split Supply     | -        | -        | yes      |  |  |  |  |  |  |  |

### Frequency-to-Voltage Conversion

The 4151 can be used as a frequency-to-voltage converter. Figure 6 shows the single-supply FVC configuration. With no signal applied, the resistor bias networks tied to pins 6 and 7 hold the input comparator in the off state. A negative going pulse applied to pin 6 (or positive pulse to pin 7) will cause the comparator to fire the one-shot. For proper operation, pulse width must be less than the period of the one-shot, T =1.1 RO CO. For a 5V p-p square-wave input the differentiator network formed by the input coupling capacitor and the resistor bias network will provide pulses which correctly trigger the one-shot. An external voltage comparator such as the 311 or 339 can be used to "square-up" sinusoidal input signals before they are applied to the 4151. Also, the component values for the input signal differentiator and bias network can be altered to accommodate square waves with different amplitudes and frequencies. The passive integrator network RB CB filters the current pulses from the pin 1 output. For less output ripple, increase the value of CB.

Figure 6. Single Supply Frequency-to-Voltage Converter

For increased accuracy and linearity, use an operational amplifier integrator as shown in Figure 7, the precision FVC configuration. Trim the offset to give -10mV out with 10Hzin and trim the full scale adjust for -10V out with 10kHz in. Input signal conditioning for this circuit is necessary just as for the single supply mode, and scale factor can be programmed by the choice of component values. A tradeoff exists between output ripple and response time, through the choice of integration capacitor C<sub>1</sub>. If C<sub>1</sub> =  $0.1\mu$ f the ripple will be about 100mV. Response time constant  $\tau_R = R_B C_1$ . For  $R_B =$  $100k\Omega$  and C<sub>1</sub> =  $0.1\mu$ f,  $\tau_B = 10msec$ .

Figure 7. Precision Frequency-to-Voltage Converter

### PRECAUTIONS

- 1. The voltage applied to comparator input pins 6 and 7 should not be allowed to go below ground by more than 0.3 volt.

- 2. Pins 3 and 5 are open-collector outputs. Shorts between these pins and +VCC can cause overheating and eventual destruction.

- 3. Reference voltage terminal pin 2 is connected to the emitter of an NPN transistor and is held at approximately 1.9 volts. This terminal should be protected from accidental shorts to ground or supply voltages. Permanent damage may occur if current in pin 2 exceeds 5mA.

- 4. Avoid stray coupling between 4151 pins 5 and 7, which could cause false triggering. For the circuit of Figure 3, bypass pin 7 to ground with at least  $0.01\mu$ f. If false triggering is experienced with the precision mode circuits, bypass pin 6 to ground with at least  $0.01\mu f$ . This is necessary for operation above 10kHz.

### **PROGRAMMING THE 4151**

The 4151 can be programmed to operate with a full scale freguency anywhere from 1.0Hz to 100kHz. In the case of the VFC configuration, nearly any full scale input voltage from 1.0V and up can be tolerated if proper scaling is employed. Here is how to determine component values for any desired full scale frequency.

1. Set  $R_S = 14k\Omega$  or use a 12k resistor and 5k pot as shown in the figures. (The only exception to this is Figure 5.)

2. Set T = 1.1 R<sub>O</sub>C<sub>O</sub> = 0.75  $\begin{bmatrix} 1 \\ f_0 \end{bmatrix}$  where fo is the desired full

scale frequency. For optimum performance make  $6.8k\Omega$ < R<sub>O</sub> < 680k $\Omega$  and 0.001 $\mu$ f < C<sub>O</sub> < 1.0 $\mu$ f.

3. a) For the circuit of Figure 3 make CB =  $10^{-2} \left[ \frac{1}{f_0} \right]$  Farads.

Smaller values of CB will give faster response time, but will also increase frequency offset and nonlinearity.

b) For the active integrator circuits make

$$C_1 = 5 \times 10^{-5} \left[\frac{1}{fo}\right]$$

Farads.

The op-amp integrator must have a slew rate of at least 135 X 10<sup>-6</sup>  $\left[\frac{1}{C_{I}}\right]$  volts per second where the value of C<sub>1</sub> is again give in Farads.

- 4. a) For the circuits of Figure 3 and 4 keep the values of RB and Rg as shown and use an input attenuator to give the desired full scale input voltage.

- b) For the precision mode circuit of Figure 5, set Rg = VIO where VIO is the full scale input voltage. 100µA Alternately the op-amp inverting input (summing node)

can be used as a current input with full scale input current I<sub>IO</sub> =  $-100\mu$ A.

5. For the FVCs, pick the value of CB or CI to give the optimum tradeoff between response time and output ripple for the particular application.

#### DESIGN EXAMPLE

Design a precision VFC (from Figure 5) with fo # 1. 100kHz and VIO = -10V.

1. Set

$$R_S = 14.0k\Omega$$

.

2. T = 0.75  $\left[\frac{1}{10^{-5}}\right] = 7.5\mu sec$

Let

$$R_O = 6.8k\Omega$$

and  $C_O = 0.001\mu f$ .

3.  $C_I = 5 \times 10^{-5} \left[ \frac{1}{10^{-5}} \right] = 500 \text{pf}.$

Op-amp slew rate must be at least

SR =

$$135 \times 10^{-6} \left[ \frac{1}{500 \text{ pf}} \right] = 0.27 \mu \text{sec}$$

4. R<sub>B</sub> =  $\frac{10 \text{ V}}{100 \mu \text{ A}} = 100 \text{ k} \Omega$ .

11. Design a precision VFC with fo = 1Hz and  $V_{10} = -10V$ .

1. Let

$$R_{S} = 14.0k\Omega$$

.

2.  $T = 0.75 \left[\frac{1}{1}\right] = 0.75$  sec.

Let  $R_{O} = 680k\Omega$  and  $C_{O} = 1.0\mu f$ .

3.  $C_{I} = 5 \times 10^{-5} \left[\frac{1}{1}\right] F = 50\mu f$ .

4.  $R_{B} = 100k\Omega$ .

111. Design a single supply FVC to operate with a supply voltage of 9V and full scale input frequency to = 83.3Hz. The output voltage must reach at least 0.63 of its final value in 200msec. Determine the output ripple.

1. Set

$$R_S = 14.0k\Omega$$

.

2.  $T = 0.75 \begin{bmatrix} 1 \\ 83.3 \end{bmatrix} = 9msec$

Let

$$R_0 = 82k\Omega$$

and  $C_0 = 0.1\mu f$ .

3. Since this FVC must operate from 8.0V, we shall make the full scale output voltage at pin 6 equal to 5.0V.

4.

$$R_B = \frac{5V}{100\mu A} = 50k\Omega$$

.

5. Output response time constant is  $r_{\rm R} \leq 200$  msec

Therefore

$$C_B \le \frac{7R}{R_B} = \frac{200 \times 10^{-3}}{50 \times 10^3} = 4\mu f.$$

Worst case ripple voltage is:

$$V_{\rm R} = \frac{9{\rm mS}\times135\mu{\rm A}}{4\mu{\rm f}} = 304{\rm mV}.$$

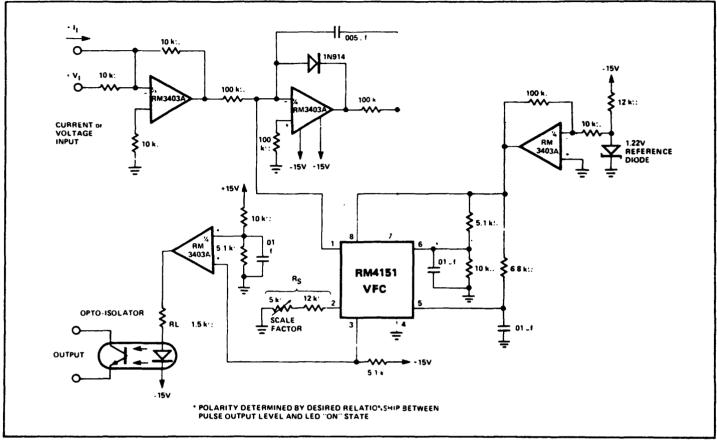

IV. Design an opto-isolated VFC with high linearity which accepts a full scale input voltage of +10V. See Figure 8 for the final design. This circuit uses the precision mode

VFC configuration for maximum linearity. The RC3403A quad op-amp provides the functions of inverter, integrator, regulator, and LED driver.

Figure 8. Opto-Isolated VFC

### TYPES SN52747, SN72747 DUAL GENERAL-PURPOSE OPERATIONAL AMPLIFIERS

BULLETIN NO. DL-6 7311446, FEBRUARY 1971-REVISED SEPTEMBER 1973

- No frequency Compensation Required

- Low Power Consumption

- Short-Circuit Protection

- Offset-Voltage Null Capability

#### description

The SN52747 and SN72747 are dual general-purpose operational amplifiers featuring offset-voltage null capability. Each half is electrically similar to SN52741/SN72741.

The high common-mode input voltage range and the absence of latch-up make the amplifiers ideal for voltage-follower applications. The devices are shortcircuit protected and the internal frequency compensation ensures stability without external components. A low-value potentiometer may be connected between the offset null inputs to null out the offset voltage as shown in Figure 3.

The SN52747 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the SN72747 is characterized for operation from 0°C to 70°C.

#### schematic (each amplifier)

- Wide Common-Mode and Differential Voltage Ranges

- No Latch-up

- Designed to be Interchangeable with Fairchild µA747 and µA747C

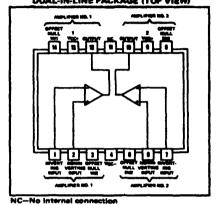

FA FLAT PACKAGE OR J, JA, OR N DUAL-IN-LINE PACKAGE (TOP VIEW)

TEXAS INSTRUMENTS

### TYPES SN52747. SN72747 DUAL GENERAL-PURPOSE OPERATIONAL AMPLIFIERS

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                                           |        |                  | SN52747      | SN72747      | UNIT |

|-----------------------------------------------------------|--------|------------------|--------------|--------------|------|

| Supply voltage V <sub>CC+</sub> (see Note 1)              |        |                  | 22           | 18           | V    |

| Supply voltage V <sub>CC-</sub> (see Note 1)              |        |                  | -22          | -18          | V    |

| Differential input voltage (see Note 2)                   |        |                  | ±30          | ± <b>3</b> 0 | V    |

| Input voltage any input, (see Notes 1 and 3)              |        |                  | ±15          | ±15          | V    |

| Voltage between any offset null terminal (N1/N2) and VCC- |        |                  | ±0.5         | ±0.5         | V    |

| Duration of output short-circuit (see Note 4)             |        |                  | unlimited    | unlimited    |      |

| Continuous total dissipation at (or below) 25°C           |        | Each amplifier   | 500          | 500          | mw   |

| free-air temperature (see Note 5)                         |        | Total package    | See Figure 2 |              |      |

| Operating free-air temperature range                      |        |                  | -55 to 125   | 0 to 70      | °ċ   |

| Storage temperature range                                 |        |                  | 65 to 150    | -65 to 150   | °C   |

| Lead temperature 1/16 inch from case for 60 seconds       | FA, J, | JA, or L package | 300          | 300          | °c   |

| Lead temperature 1/16 inch from case for 10 seconds       | N paci | age              | 260          | 260          | °C   |

NOTES: 1. All voltage values, unless otherwise noted, are with respect to the zero reference level (ground) of the supply voltages where the zero reference level is the midpoint between VCC+ and VCC-.

Differential voltages are at the noninverting input terminal with respect to the inverting input terminal.

The magnitude of the input voltage must never exceed the magnitude of tha supply voltage or 15 volts, whichever is less.

The output may be shorted to ground or either power supply. For the SN52747 only, the unlimited duration of the short-circuit applies et (or below) 125°C case temperature or 75°C free-air temperature.

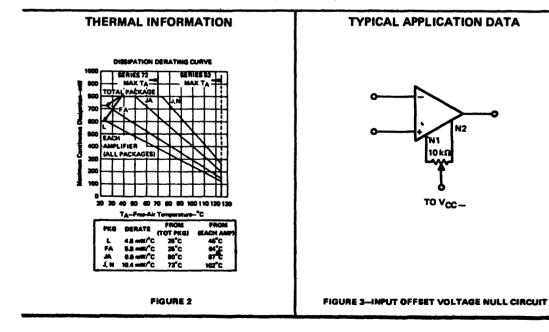

For operation above 25°C free-air temperature and for total package ratings, refer to Dissipation Dersting Curve, Figure 2.

|            |                                       | -                                   | DITIONS*              |        | SN52747 | ,    |        | N72747  |     | UNIT         |

|------------|---------------------------------------|-------------------------------------|-----------------------|--------|---------|------|--------|---------|-----|--------------|

|            | PARAMETER                             | TEST CO                             | NDITIONS <sup>†</sup> | MIN    | TYP     | MAX  | MIN    | ТҮР     | MAX |              |

|            | Input offert voltage                  | Rs < 10 kΩ                          | 25°C                  |        | 1       | 5    |        | 1       | 6   | mV           |

| VIO        |                                       | IS S IUKI                           | Full range            | T      |         | 6    |        |         | 7.5 | mv           |

| ∆VIO(adj)  | Offset voltage adjust range           |                                     | 25°C                  |        | ±15     |      |        | ±15     |     | m۷           |

|            | Input offset current                  |                                     | 25°C                  |        | 20      | 200  |        | 20      | 200 | nA           |

| 10         | mpat on art canent                    |                                     | Full range            |        |         | 500  |        |         | 300 | <u> </u>     |

|            | Input bias current                    |                                     | 25°C                  |        | 80      | 500  |        | 80      | 500 | nA           |

| 18         | Input bias current                    |                                     | Full range            |        |         | 1500 |        |         | 800 |              |