## EVLA Memo No. 39

Application Note Using the Serial Peripheral Interface (SPI) For EVLA

SPI is a form of synchronous serial transmission. The basic aspect of SPI is that each SPI device has a serial input, a serial output, and serial clock. One SPI device will be considered to be the master and all additional SPI devices will be considered slaves. The master is simply the device that provides the serial clock and controls the data transfer.

The simplest form of SPI communications is one master and one slave. In this form, only the three lines mentioned above need to be connected in the proper fashion. If more then one slave exists, then an additional line usually called the slave select line (SS) is used to select a particular slave. The SS line acts as chip select lines, as well as a slave output enable line.

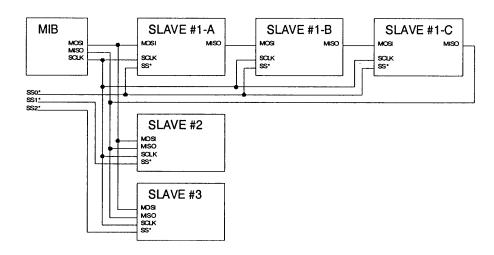

For the EVLA, it is planned that the MIB processor will always act as the master SPI device. All SPI devices on the User Device shall be slaves. Also, it is expected that the MIB will have to support multiple SPI devices, so the SPI slave components must have the SS line function. Figure 1 shows the basic connection need to connect the MIB SPI Master to multiple SPI slaves. The line designated Master-Output-Slave-Input (MOSI) simply states that the Master-Output connects to all Slave-Inputs. The same is true for the Master-Input-Slave-Output (MISO) in that the Master-Input must connect to all the Slave-Outputs. The SPI Clock (SCLK) is connected together for all the SPI devices. As stated before, the MIB is the source for the SPI Clock. The active low Slave Select (SS\*) lines must be generated one per slave device. It can be generated directly from the MIB or via digital logic controlled by the MIB. The first slave shows the method to daisy chain multiple slaves together, where the SS\* line on its low to high transition acts as a data valid signal for each device. This methodology has the problem in that when one needs to update one slave in the chain, the MIB must remember the other slave values. Especially after a power failure, it may in fact be impossible to load the current values from the MIB, so the daisy chain method would best be avoided.

Figure 1: SPI Connections - MIB Master to Slaves

The actual communication using SPI is straightforward. The master and slave simply form a ring buffer, such that when the master transmits its buffer to the slave, the slave transmits its buffer to the master. One transition of the clock shifts the data out of each buffer. The next transition of the clock latches the data into each buffer. Figure 2 shows the timing for a byte transfer. In this transfer, the SS\* is driven low to select the specific slave. Next the master clocks the data transfer. In this case, the falling edge of the clock causes the shift registers to place the next data bit onto MISO and MOSI. On the rising edge, this bit will be sampled and loaded into each buffer. When the transfer ends, the SS\* will return high, thus deactivating

For each SPI device that is selected, it will have a protocol in order to utilize it in the design. Designers should attempt to communicate with other designers to find SPI devices that can be used across designs. This will also simplify the software development, in that the number of protocols would be minimal. For the unique case where we might have MIB to microprocessor communications, NRAO would generate a standard protocol for that communication. In fact via ALMA, a protocol was established by NRAO for this purpose. It would be necessary for the EVLA to modify this protocol in order to use it more effectively.

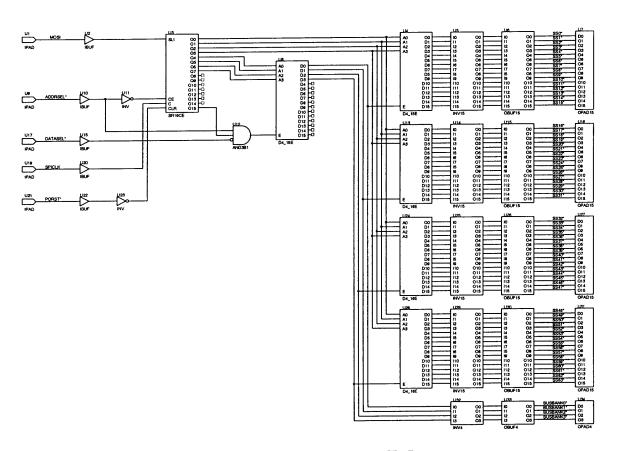

Figure 3: SS\* Line Generator Using SPI Bus

In order to minimize RFI generation, the MIB can provide LVDS signals into and out of the MIB for MOSI, MISO, SCLK, ADDRSEL\*, and DATASEL\* for long distances. Designers should feedback whether or not for short distances, the MIB provides single-ended or LVDS signals.