ALMA Memo 607

## SAO Cycle 3 Development Study Closeout Report Digital Correlator and Phased Array Architectures for Upgrading ALMA

Alain Baudry, Lindy Blackburn, Brent Carlson, Geoff Crew, Shep Doeleman,

Ray Escoffier, Lincoln Greenhill, Daniel Herrera, Jack Hickish, Rich Lacasse, Rurik Primiani, Michael Rupen, Alejandro Saez, Jonathan Weintroub (PI) & André Young

December 22, 2017

#### Abstract

This Closeout Report documents the outcome of a SAO-led ALMA Development Study of a next generation combined correlator and VLBI phased array to take greater advantage of fundamental scientific capabilities, such as sensitivity, resolution and flexibility. ALMA already represents a huge advance in collecting area and frequency coverage making it the dominant instrument for high frequency radio astronomy. We have studied processing architectures that maximize bandwidth, and thus sensitivity, allow flexible ultra high resolution spectral processing, and supports other operational modes, such as VLBI. The ALMA Science Advisory Committee (ASAC) studies *Pathways to Developing ALMA* and *A Road Map for Developing ALMA* (both referenced as Bolatto et al., 2015) comprehensively describe the community view of ALMA upgrades and their key science impact.

The methodology of the Study was to examine a variety of technologies, algorithms, balancing costs and timelines against potential benefits. The scientific impact for the proposed study derives from several key new areas of enhanced capability. The Study is divided into eight technical work packages. This Outcomes Report gives a concise summary of each, and eight detailed appendices are provided. A top-level conceptual framing of the full installation, including specifications and rough equipment costing and schedule, is presented as Phase III of three suggested design phases. Phase I is this Study, now complete.

Figure 1 Study team group photo under the CHIME array taken at the Study closing meeting , NRC-Herzberg, Penticton, BC, Canada, 24 February 2017

## 1 Introduction

We report here on a next-generation ALMA correlator and phased array<sup>1</sup> that quadruples ALMA's current processed bandwidth and provides high spectral resolution, native VLBI capability, and a variety of other features.

Science case précis: Unsurpassed instantaneous bandwidth for spectral line surveys, will provide truly unbiased connections between chemistry and the planet formation process in protoplanetary disks. An order of magnitude increase in the number of spectrally surveyed star forming regions and extragalactic sources will provide entirely new approaches to chemical evolution across a range of exciting sources. Higher bandwidth greatly increases the cosmic volumes accessible via intensity mapping, allowing complete inventories and physics of galactic gas at high-redshifts and new views of galactic evolution across cosmic time. Simultaneous line detection will lead to rapid accumulation of high-z redshift surveys with excellent prospects for unlocking long-standing questions on the build up of stellar mass in galaxies. In the time domain, new evolutionary studies of transients in the millimeter and submillimeter will be possible, providing insight into mechanisms for variability in  $\gamma$ -ray bursts, whose output peaks in the ALMA frequency bands. Cometary studies rely on rapid cadence observations to disentangle coma versus jet emission from these rotating bodies: the key to solving the puzzle of their origin in the solar system. VLBI features will allow ALMA to nimbly form multiple beams to create Earth-sized virtual apertures to push the limits of angular resolution from the earth's surface. By enabling beamforming in Band 7 and beyond we will sharpen our direct views of black hole event horizons, addressing some of the most fundamental questions in astronomy, physics and mathematics.

**Report structure:** The study was broken down into the following eight work packages, each researched in depth by a subset of the study team.

- WP2.1 Scientific requirements & specifications

- WP2.2 Identify DSP F-engine platform

- WP2.3 Determine F-engine architecture given chosen DSP platform

- WP2.4 Identify corner-turn platform

- WP2.5 Identify DSP X-engine platform

- WP2.6 Determine optimal X-engine architecture

- WP2.7 Determine design of VLBI capability

- WP2.8 Staging of new correlator and phased array

The appendix to this report includes a detailed breakdown of each work package into sub-tasks, and shows the team leader and study team members assigned to each. A substantially abridged summary of the results of the work packages is provided in section 2. The appendix also has a full, unabridged report on each work package. The eight appended reports naturally consider alternative approaches in depth, and the trade offs associated with each, while the summary in main body of the report is written to present a clean set of conclusions. However in a system this complicated, the details are important, and the appendix reports these so that it is possible to understand the underpinnings of the recommendations. We find that it is possible with current and projected technology to improve bandwidth and spectral resolution while reducing size and increasing reliability. Increasing ALMA's bandwidth is the least expensive approach to improving the sensitivity of the instrument. Reduction of power, magnified by concomitant reduction in cooling requirements, will reduce costs, and make the entire ALMA system more robust against power disruptions.

## 2 Summaries of work package outcomes

Historically in radio interferometry, XF correlators—cross-correlation first, with Fourier transform in software on the integrated lags—have been favored because expensive wide multipliers are not needed, since the bit-width of the multiplied data in the X-stage remains at the width of the sampled data. The advent of wide multipliers in digital signal processing hardware such as field programmable gate arrays (FPGAs) has effectively reduced the penalty for bit growth in the butterflies of the Fast Fourier Transform (FFT). The well known economy of the Cooley-Tukey FFT

<sup>&</sup>lt;sup>1</sup>Sometimes referred to in this report simply as a *correlator* for simplicity.

algorithm combines with the fact that correlation collapses to bin-wise cross-multiplication in the Fourier domain to yield computational savings, and the number of instantiated multipliers for a given array size and spectral resolution is substantially reduced—the FX architecture allows for great economy in correlators with high spectral resolution and relatively large numbers of antennas. The FX architecture is now widely employed for modern digital correlators in radio astronomy (Primiani, et al., 2016, Hickish et al., 2016), and it is chosen as a baseline assumption for this Study.

Also with wide multipliers, it is possible to process wider bit-widths, thereby improving the digital efficiency of the correlator from 88%, for a two bit machine, to 99% for 4-bits, say, a benefit which applies equally to spectral lines and continuum observations. The present ALMA correlator is limited to 3-bit data. While it computes using 2-, 3- and 4-bit arithmetic depending on mode, the only modes being offered to ALMA users are limited to 2-bit arithmetic and 88% efficiency.

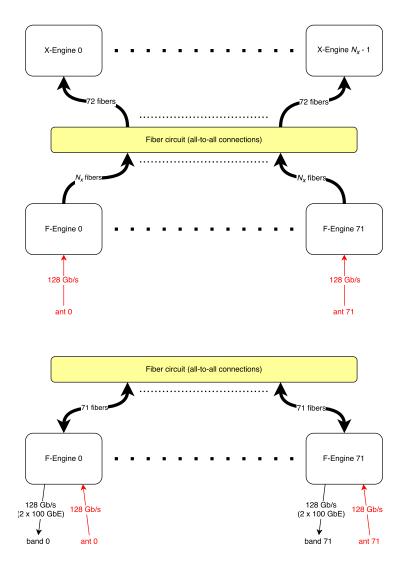

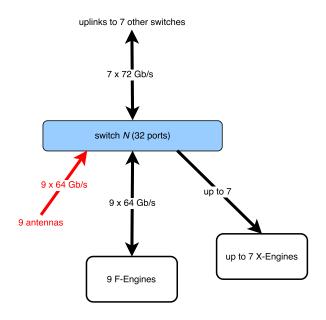

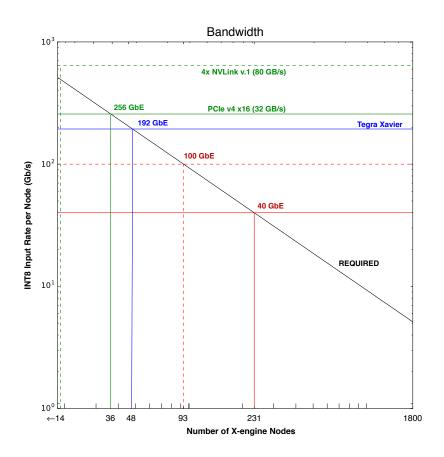

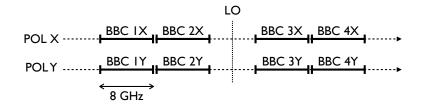

All correlators require an interconnect system to allow communication between F-processing nodes, which operate on full-bandwidth data from a subset of antennas, and X-processing nodes, which operate on data from a relatively small bandwidth from all antennas. Since different ALMA baseband converters (BBCs) handling independent band fractions may be handled by entirely separate and independent correlators, we have considered the implementation of a system for 72 dual-polarization antennas, capable of dealing with 16 GHz of processed bandwidth—8 GHz BBC bandwidth, two polarizations, and one sideband—and 4-bit samples. This amounts to 256 Gb/s per dual-polarization antenna. Quadrupling this system covers the 64 GHz bandwidth of the complete proposed next generationALMA system.

Based on these requirements, a digital system processing a single BBC must be capable of handling a data rate of  $\sim 16$  Tb/s. The feasibility of realizing such a system with different technologies is dependent on specific topology of the interconnect required—for example, how many nodes are required at the input and output of the system. This is heavily dependent on the technologies chosen for the various signal processing engines. For the purposes of this report, we assume that the number of input nodes is 72. In other words, there is one input node per antenna, with each delivering 256 Gb/s. The number of output nodes may vary largely depending on technology; for example, one feasible FPGA implementation may feature a small number of processors, each sinking 500+ Gb/s of data. Alternatively a GPU implementation may feature many small, low-power processors, each processing 200 Gb/s.

In summary, the work breakdown for the study was predicated on a set of baseline assumptions.

- 1. Correlator architecture will be FX.

- 2. Future available bandwidth will be 16 GHz per sideband per polarization, or 64 GHz total usable instantaneous bandwidth, a quadrupling of the current ALMA processed bandwidth.

- 3. Even larger bandwidths still can be handled by modular replication

- 4. Samplers will remain at the antennas with digital data sent over fiber

- 5. Samplers will digitize 8 GHz bandwidth per baseband channel (BBC) at 4-bit resolution

- 6. The number of observation modes of the new digital system will be minimized.

- 7. A maximum number, 72, antennas will be supported over baselines extending to 300 km.

The next subsections give an abbreviated description of the results of each of eight work packages which comprise the study. A more detailed report on the each work package is appended.

#### 2.1 Scientific requirements & specifications

Assumed requirements for the next generation ALMA correlator and phased array are presented in summary in this section (see Table 1). A more detailed set of specifications also with more commentary is in the WP2.1 section in the appendix. We wish, within the frame of the 'ALMA 2030' documents referenced earlier, to interact with ALMA Scientific Advisory Committee (ASAC) and the ALMA Development Working Group to reach consensus on consolidated requirements. We are aware that some of the requirements listed may need more scientific discussions, long-term technical developments and may not be easily translated into engineering specifications. We point out which requirements would benefit from further scientific discussions or technical studies. For example, in addition to funding questions, more discussions need to be conducted for an ALMA Extended Array on the number of additional antennas and maximum baseline. Assumed requirements were needed to set goals for all the other work packages in this Study. In other words requirements were a necessary starting assumption for our Study. We do not claim they represent the consensus of the ALMA community; they are however informed by extensive dialog with scientific and technical colleagues in the ALMA community, and could develop to represent such consensus. Table 1: Abbreviated assumed specifications for the next generation correlator and phased array. An appendix with the full report of the relevant working group has more requirements and more commentary on each. For easier cross-referencing the parameter numbers from that document is kept in this table, despite that a number of requirements lines have been omitted.

|    | Parameter                                                           | Requirement                                                                                             | Comments                                                                                                                |

|----|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1  | Frequency range                                                     | Process digitized IF<br>from all receivers in<br>range $\sim 30 - 950 \mathrm{GHz}$                     | ALMA Bands 1–10: cf. SCI-<br>90.00.00.00-10-00.                                                                         |

| 2  | Number of antennas                                                  | 72                                                                                                      | 72 antennas ( $\sim 10\%$ increase in collecting area) would allow additional antennas for the ALMA Extended Array.     |

| 3  | Maximum baseline                                                    | $\sim 300{ m km}$                                                                                       | SCI-90.00.00.00-220-00.                                                                                                 |

| 4  | Instantaneous band-<br>width                                        | $32{ m GHz/polarization}$                                                                               | 2SB Rx: 16 GHz per SB per pol.                                                                                          |

| 5  | BBC BW                                                              | 8 GHz                                                                                                   | BBC bandwidth of each chunk fed to the correlator after digitization.                                                   |

| 6  | Number of BBCs                                                      | 2/SB and polarization                                                                                   | Required to cover the desired total BW in 8 GHz "chunks."                                                               |

| 7  | Input sample format<br>(digitizer) & Correla-<br>tion sample format | 4-bit & 4-bit per sample                                                                                | 4-bits minimizes quantization losses                                                                                    |

| 9  | Best spectral resolu-<br>tion                                       | $0.01  {\rm km/s} = 1  {\rm kHz}  (\nu/30  {\rm GHz})$                                                  | Resolve lines from cold starless core.<br>From SCI-90.00.00.00-30-00                                                    |

| 13 | Integration and read-<br>out interval                               | 1 msec (auto-correlations)<br>16 msec (cross-correlations)                                              | SCI-90.00.00.00-240-00. Spectral res.<br>limited for fast dump rates, which are<br>needed also for on-the-fly mapping . |

| 14 | Polarization products                                               | 2- or 4-polarization products                                                                           | 2 pol. products reduces data rate SCI-<br>90.00.00.00-310-00.                                                           |

| 15 | Spectral dynamic<br>range                                           | 10,000:1 for weak spectral lines<br>near strong ones<br>1,000:1 for weak lines<br>atop strong continuum | Identical to SCI-90.00.00.00-70-00.                                                                                     |

| 16 | Number of subarrays                                                 | 6                                                                                                       | Must be completely independent—no frequency or control restrictions).                                                   |

| 17 | VLBI                                                                | VLBI output sum port for full<br>phased array or 2 subarrays                                            | One subarray could just be one an-<br>tenna. Ref SCI-90.00.00.00-370-00                                                 |

| 24 | Correlator configura-<br>tion time                                  | < 1.5 sec                                                                                               | Complete configuration should be ac-<br>complished in less than 1.5 sec in all<br>circumstances                         |

## 2.2 Identify DSP F-engine platform

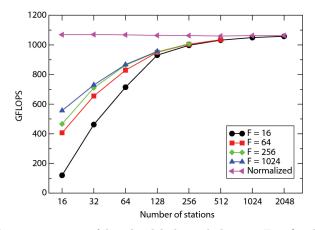

At the heart of the F-engine is a transformation of a wideband digitized signal to a channelized representation, usually computed efficiently using a Fast Fourier Transform (FFT) algorithm, for which the computational cost generally scales slightly faster than linearly with the transform size. In comparing the different platforms the real-time computational efficiency of an FFT of the required size on each was used as a primary performance measure. In the case of multi-stage solutions the sum of the sizes of the stages of the FFT was considered. The real-time execution also drives both compute rate, and the input and output rates that need to be sustained.

Four different technologies were considered: Application-Specific Integrated Circuits (ASIC), Field-Programmable Gate Arrays (FPGA), general-purpose Graphics Processing Units (GPU), and Central Processing Units (CPU). These technologies were compared based on various figuresof-merit to decide on a proposed platform. Table 2 lists F-engine specifications relevant to the comparison of platforms and the performance figure of merit each drives.

| Parameter           | Requirement              | Impact                          |

|---------------------|--------------------------|---------------------------------|

| Maximum baseline    | 300 km                   | Coarse-delay buffer memory      |

| BBC Bandwidth       | $\sim 8 \text{ GHz}$     | Data throughput and FFT size(s) |

| Sample resolution   | 4-bit (in) & 4-bit (out) | Input and output data rates     |

| Spectral resolution | $\sim 1 \text{ kHz}$     | FFT size(s)                     |

Table 2 A small subset of overall specifications are the key drivers of F-engine performance and thus drive the platform selection.

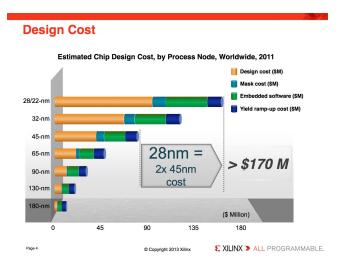

ASICs were essentially ruled out based on the very high costs associated with implementing solutions in these devices, as compared to an FPGA solution. Apart from the logic design, which could reasonably be expected to be similar to that needed for FPGA, lower-level design is also needed. Furthermore, high-speed I/O and other IP crucial to the present application which comes readily available in many high-performance FPGAs might add to the design cost, either in the form of custom-design of these solutions or obtaining license from ASIC IP vendors. Finally, given the relatively low volume of units needed the mask and yield ramp-up adds a considerable per-unit cost for using this technology.

CPUs were eliminated on the basis of poor computational performance in comparison to GPUs without any cost benefit. The capability of contemporary GPUs, in terms of operations-per-second and memory bandwidth relative to cost, is vastly superior to that of the same generation of CPUs, so that achieving the same performance in CPU as in a single GPU would require multiple processors. This would increase cost substantially, not in the least due to the number of CPUs required, but also as a result of additional hardware infrastructure needed to combine multiple processors.

GPUs, which in recent years have become a popular technology in High-Performance Computing (HPC) applications, offer a competitive alternative to FPGAs in terms of both power consumption and per-unit costs. However, the FFT algorithm, especially for large sizes has a relatively low computational intensity — the number of calculations performed per each byte read from memory. In practice this translates to the calculation being memory bandwidth bound, and the compute rate capability of the platform being severely under-utilized.

| Parameter                   | Specification             |  |

|-----------------------------|---------------------------|--|

| Coarse-delay buffer memory  | 128 Mb                    |  |

| Data throughput             | ${\sim}8$ M channels / ms |  |

| Input and output data rates | $64 { m ~Gbps}$           |  |

Table 3 Key F-engine specifications which the chosen platform's performance has to meet or exceed.

Ultimately the FPGA was selected as the preferred platform. They offer a much higher degree of flexibility in terms of routing data between arithmetic units, enabling effective utilization of the overall compute capability. In addition, given that high-speed communication is a technology driving application for FPGAs, current and upcoming generations offer sufficient input and output rates so that the required throughput in the F-engine application can easily be sustained with relatively little additional hardware being required. In table 3 the parameters which the selected FPGA platform need to meet are listed, and indeed the FPGA does have the resources to meet all these requirements.

## 2.3 Determine F-engine architecture given chosen DSP platform

Work Package (WP) 2.2 recommended the use of a Field Programmable Gate Array (FPGA) for the so-called *F-engine* which is the Digital Signal Processing (DSP) engine that transforms the time domain sampled data from the Analog-to-Digital-Converter (ADC) into frequency domain spectra. The purpose of this work package was to evaluate various FPGA-based *architectures* for the F-engine and determine the most effective option—that meets all scientific requirements—for implementation with near-future FPGA families.

Since the ADC for next-generation ALMA is not within this Study's scope, certain assumptions had to be made about the data it will provide to the F-engine. The most critical are:

1. sample rate will be exactly 16 GSps with a sample format of 4 bits, and 2. when the operating mode requires Walshing, the step time of the 90-270 switching (used for sideband separation) will remain exactly 16 ms.

### 2.3.1 Motivation for Two Modes

Over the course of this study it was determined that two constraints, arising from our assumptions and the scientific requirements, when combined drive the complexity of the F-engine architecture beyond reasonable implementation. Briefly summarized these constraints are:

- 1. Walsh switching: to effectively demodulate the 90-270 Walsh pattern there must be an integer number of F-engine input sample windows within on Walsh step; ideally this would be a large number to avoid blanking losses. Additionally, this constraint drives non- $2^n$  transform sizes.

- 2. 1 kHz resolution: the scientific requirement that the correlator provide a final resolution of  $\sim 1$  kHz drives very large transform sizes which mean large input sample windows.

Given the immutability of the sample rate and Walsh step time, a single-mode<sup>2</sup> F-engine implementation cannot reasonably meet both constraints as this would mean very large power-of-5 transforms with large input windows and unacceptable blanking losses; one constraint or the other must be relaxed. Therefore this study group proposes the following two modes for the F-engine:

- 1. Walsh mode: full Walsh switching<sup>3</sup> is enabled but the  $\sim 1 \text{ kHz}$  spectral resolution is increased to  $\sim 100 \text{ kHz}$ , i.e. a relaxation of constraint 2. This would mean small blanking losses of  $\sim 0.06\%$ . Note: this mode still requires a non power-of-two, split-radix transfrom.

- 2. LO-offset mode: no Walsh switching<sup>4</sup> but LO offsets are used for spurious signal rejection, i.e. a removal of constraint 1. This mode incurs no blanking losses (since there's no Walsh switching) and the window size can be large and a power-of-two. Note: in this mode the spectral resolution will not be exactly but instead approximately 1 kHz.

These two modes naturally match the double-sideband (bands 9 and 10) and sideband-separating (bands 1-8) receivers, respectively, of ALMA. However, if an astronomer desires stronger sideband rejection in bands 1-8 then mode 1 can be employed but at the sacrifice of poorer spectral resolution.

#### 2.3.2 Architectures Studied

In the context of general algorithms for the F-engine this working package explored numerous architectures for the transform itself, including: $^5$

- 1. Single-stage channelizer

- 2. PFB followed by per-channel DFT

- 3. Two-dimensional FFT/PFB

- 4. Prime Factor Algorithm FFT

- 5. Tunable Filterbank followed by per-channel PFB

These architectures were explored in the context of the specifications with estimated resource usage determined for a modern FPGA. Additionally, various other sub-systems relevant to the F-engine were investigated such as delay tracking and complex gain multiplication.

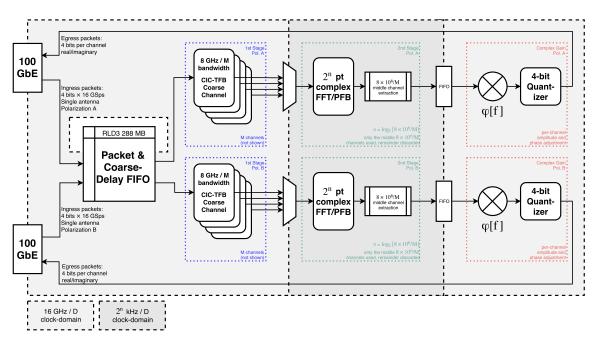

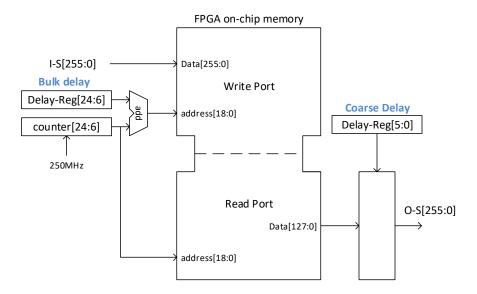

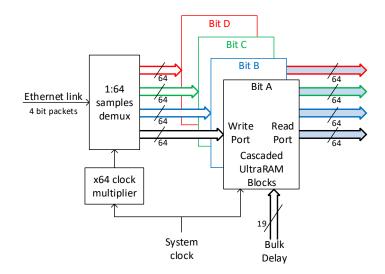

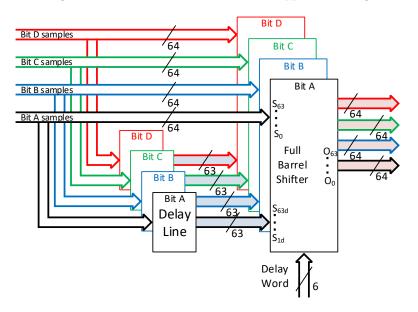

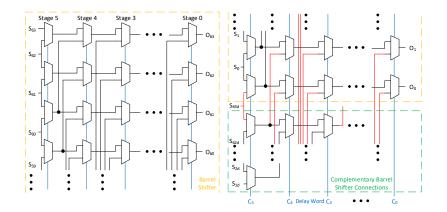

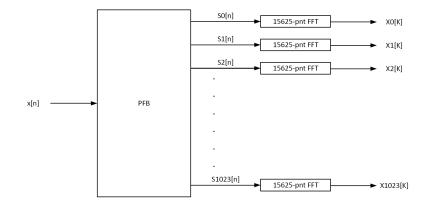

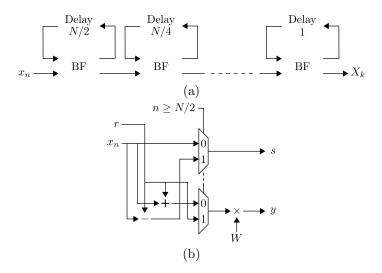

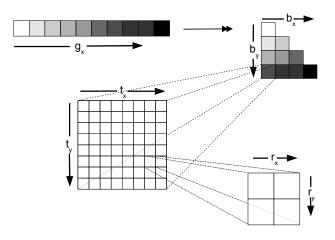

Figure 2 shows the last of the five considered F-engine personalities, which use a "Tunable Filter Bank" or TFB stage for high spectral resolution. Though this exact architecture was ultimately

$<sup>^{2}</sup>$ In this context a *mode* is understood to mean a FPGA personality.

$<sup>^{3}</sup>$ Full Walsh switching means both 0-180 for spurious signal rejection which is taken out with sign flips at the sampler and 90-270 for sideband separation which falls to the correlator

$<sup>^{4}</sup>$ Similarly no switching means neither 0-180 nor 90-270. The LO offsets will take care of spurious signal rejection however are not used for sideband separation

<sup>&</sup>lt;sup>5</sup>Not listed here is the oversampled Polyphase Filterbank architecture which was proposed but time constraints precluded its study.

rejected, the block diagram shows enough relevant detail, ad clearly shows the complexity which is subsumed into the FPGA. . For more details of the proposed transform architecture and of the other F-engine subsystems please see the full report in the study appendix.

Figure 2 An example of a high spectral resolution candidate F-engine gateware personality that uses a TFB first stage channelizer followed by FFT or PFB (selectable) second stage fine channelization per coarse channel. The incoming data packets contain 4-bit samples at 16 GSps; these packets are received with the 288 MB RLDRAM3 modules available on the VCU118 which is also used as a coarse geometric compensation FIFO. The data from each polarization is then fed to the first stage channelizer which contains a series of TFB channels each of which downconverts a sub-band of the full 8 GHz passband; note that the number of TFB channels, M, will generally be a low number, for example, 64, since the TFB logic scales linearly with M. Each TFB channel, containing 8 GHz/M in usable bandwidth, is intentionally oversampled to the next power-of-two in kHz so that the proceeding second stage channelizer can be a power-of-two and the resulting fine channels are exactly 1 kHz wide. Ultimately the number of fine channels leaving the F-engine will be exactly 8 million but we've circumvented ever having to do a non-power-of-two transform. Note that only a single second stage channelizer needs to be instantiated since each TFB output is downsampled by a factor of M canceling out the fact that there are M coarse channels. Following fine channelization the complex gain subsystem provides per-channel complex gain multipliers which can used to implement sub- sample delay adjustment, 90-270 deWalshing, amplitude and phase bandpass corrections, etc. Finally the data is quantized back to 4-bits and shipped out to the BX-engines. Many subsystems are not shown, such as test vectors, monitor-&-control & (de)packetizers.

#### 2.3.3 Conclusion

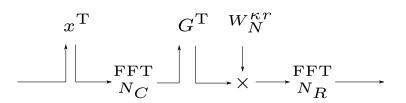

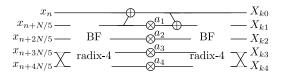

Much time and effort during the study of this working package went into architecting a single-mode F-engine before it was determined that a two-mode system fit the requirements more comfortably. Nevertheless these efforts were not in vain as much overlap exists between the **LO-offset mode** and what would have been a single-mode. After careful consideration of the above listed architectures we recommend the following for the transform architecture:

- 1. Walsh mode: 160 kilopoint (256 x 625) split-radix two-dimensional FFT

- 2. LO-offset mode:  $2^{24}$  point (4096 x 4096) two-dimensional FFT

The appendix for this work package has a great deal of detail on the five alternative architectures considered, and the reasons for the selection of these two modes. The oversampled PFB also shows promise, and is proposed to be explored in the follow-on Project.

## 2.4 Identify corner-turn platform

Interconnection systems may be divided into two classes. Actively switched systems can dynamically route data from a source to any of several endpoints. These systems include Ethernet, Infiniband, and some PCI-Express based motherboards/backplanes. Passively-routed systems simply provide point-to-point connectivity from sources to endpoints. Examples of these systems are simple backplane meshes, and point-to-point connections made with optical fiber or copper cabling. A very brief overview of the applicability of these systems to an upgraded ALMA system is given below.

## 2.4.1 Point-to-Point Interconnect

**LVDS Copper Cabling** The present ALMA correlator uses 16384 LVDS twisted-pair cables operating at 250 MHz, representing "the greatest design challenge in the system" (Escoffier et al., 2007), to connect the station cards (equivalent to F-processors) to the correlator cards (equivalent to the X-processors). With the increased specifications of the next-generation ALMA correlator a corner-turn implementation using the same technology would see the total number of cables increase roughly five-fold, mainly driven by the doubling in bandwidth and sample bitwidth. Even assuming a per-lane speed increase by a factor of two or more, the complexity of such a cabling system is highly undesirable.

**Copper Backplane** The most promising copper backplane standard is the Advanced Telecommunications Computing Architecture (ATCA). The latest standard, PICMG 3.1, supports 40 and 100 Gb/s connections. ATCA enclosures can be purchased off-the-shelf, for  $\sim 10 \,\text{k}$ \$, and provide all-to-all connections between up to 16 computing cards (Figure 3(a)). While some correlator realizations may be compatible with interconnect based on one or more independent ATCA enclosures, in general it may be necessary to externally mesh together multiple such units, resulting in undesirable complexity and cost. Further, requiring computing units to be ATCA-compatible greatly increases the likelihood that they must be custom-designed, with significant associated NRE.

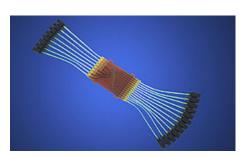

Fiber Circuitry For a one-off NRE fee of  $\sim 10 \text{ k}$  custom fiber-based interconnection circuits can be fabricated, providing practically any routing of inputs to outputs (Figure 3(b)). These devices can be used as part of short-, mid-, or long-range fiber runs. Provided the processing nodes at each end of such a system have adequate independent IO paths to drive the required number of fibers, fiber optic circuitry is a very cost-effective way of providing interconnect. It is already being used in astronomy applications (Hampson et al., 2013). A system involving fiber circuitry interconnect likely involves some engineering NRE to design or adapt a platform to be able to interface with the fiber circuit.

## 2.4.2 Active Switching

**PCIe switches** PCI-Express is a common standard for connecting many processing boards via a backplane type configuration supporting transfer speeds up to 125 Gb/s per endpoint (for Gen3 with 16 lanes). Additionally the standard allows data transfers between slaves by using bus mastering. All PCI-Express endpoints, however, must connect to either a root complex or a switch and given these devices with 16 or more endpoints are rare or non-existent we will not consider this technology for the proposed ALMA correlator.

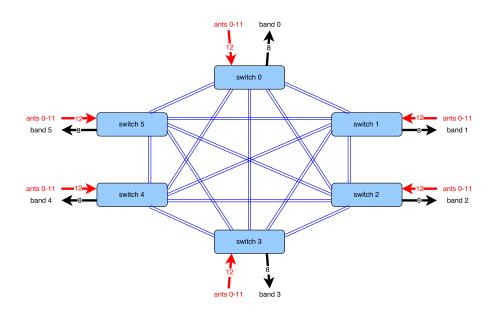

**Ethernet Switching** Ethernet (or Infiniband) switches provide high-speed, flexible interconnect, with industry standard interfaces widely supported by commodity hardware such as FPGA, CPU/GPU platforms. The main draws of Ethernet switch systems are their extreme flexibility, tolerance to system architecture changes, and availability as COTS units, without hardware NRE. Ethernet switches are already being extensively used in the MeerKAT array, which features a digital backend with unprecedented reconfigurability (Manley, 2015). At current prices, the cost of an Ethernet-based interconnect solution for the entire, multi-BBC ALMA system is approximately  $500 \text{ k}^{2} - 1 \text{ M}^{2}$ , depending on choice of switches and cables. However, this cost is likely to fall significantly as the 100 Gb Ethernet standard becomes more mainstream, or 400 Gb Ethernet appears in COTS parts. The cost may also be reduced by a factor of two or more by considering the portreduction schemes suggested by McMahon et al. (2007). Furthermore, the cost of investment in an Ethernet architecture may well be dwarfed by savings associated with being able to use COTS computing hardware for processing modules.

(a) An enclosure with copper mesh interconnect provided by an ATCA standard backplane. This backplane supports 40 Gb/s all-to-all connections for up to 14 cards.

(b) Molex FlexPlane<sup>TM</sup> fiber circuitry provides user-customizable fiber-based mesh interconnect.

(c) Actively switched interconnect, provided by COTS Ethernet switches, with industry standard high-speed ports, operating at 100 Gb/s

Figure 3 Three interconnect options based on current technologies.

#### 2.4.3 Conclusions

The final choice of interconnect technology used by a next-generation ALMA correlator will need to be made in light of a system-engineering overview of the instrument as a whole. If large engineering budgets are to be dedicated to developing custom platforms on which to implement the correlator's signal processing, it way well be the case that integrating support for a fiber circuit interconnect is the most appropriate design decision. However, if a choice is made to adopt general-purpose COTS compute platforms, such as modern FPGA or CPU/GPU platforms, an NRE-free Ethernet switch interconnect is likely to represent a cheaper total cost.

Given that an Ethernet-based interconnect solution is clearly feasible at the scale of the proposed ALMA correlator, and likely represents a relatively small part of the total hardware budget, our opinion is that this technology is the preferred choice, given the uncertainties in the other aspects of the correlator design. Choosing an Ethernet fabric interconnect maximizes the flexibility of the digital backend. Furthermore, should hardware development of a future correlator commence, such a choice would make it easy to prototype an effectively production-ready subset of the complete ALMA system and provides a clear path for staged deployment.

### 2.5 Identify DSP X-engine platform

The X-engine platform will perform element-wise multiplication of spectra for each pair of antennas received from the F-engine, via the network interconnect, and to accumulate the products, for each frequency channel individually. As dictated by the two modes of the F-engine, the packetized X-engine platform will accept data with 1 ms and 0.01 ms Nyquist windows. Delivery of variable time and frequency resolutions for end-use is implemented following and independently of the cross-multiplication, the priority being simplicity, modularity, and minimization of the number of modes and reallocation of resources.

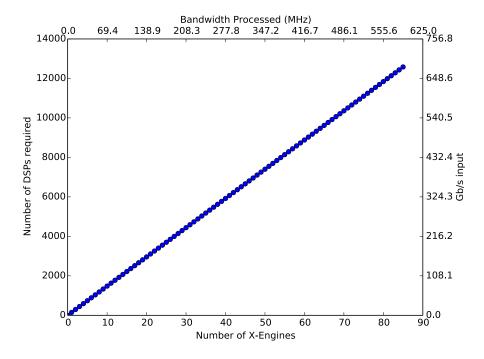

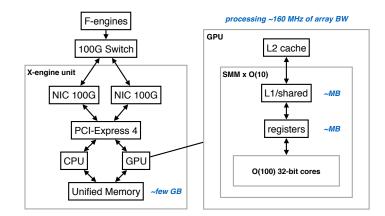

The study considered two leading off-the-shelf technologies for the platform: FPGA and GPU. The computational architectures and models for these are very different (see appendix), but despite that, the primary finding is that with commercially available components as of 2018, both are capable of supporting a low-cost, power-efficient, physically compact X-engine. The caveat to this is that lab development and testing of hardware, software, and firmware are needed to confirm the finding, or identify differences in performance.

Considering the large instantaneous bandwidth of ALMA and the number of antennas, contemporary computational elements (FPGA or GPU) are sufficiently "powerful" that operation is bandwidth-bounded. Bottlenecks, if any are most likely tied to working with the high density of data passing through memory and computing elements. Per computing element, the adopted capture rate from the network is 200 Gb s<sup>-1</sup>. This limit reflects a reasonable scaling of current network link capacities, though in practice, computational elements of the X-engine, scaled into the future, would not be saturated.

Either technical solution for the platform, assuming commercially available components as of

2018, would incur a cost of  $\sim$ \$220K (GPU) and  $\sim$ \$300K (FPGA) to process one dual polarization ALMA BBC. For current engineering assumptions, this would consume 4.4 kW or 2.5 kW depending for the choice of platform, respectively. The estimated total cost of all the core elements of the X-engine serving four BBC pairs would be within  $\sim$ 20% of \$1M, slightly favoring the GPU solution. Total power consumption would be between 10 and 17 kW (not including hot-spare computing and associated network components that add to cost up front but reduce operating costs in the long term).

The primary challenge for the FPGA solution is operation of the necessary firmware at clock rates > 500 MHz for current engineering tools and chips. The next uncertainty prior to detailed engineering analysis and testing, lies in whether off-the-shelf processing boards will meet ALMA requirements cost effectively, or whether custom boards will be required.

In contrast, the complexion of prospective GPU hardware, dictated by industry standards and market drivers (e.g., driverless cars, deep learning), is known. The proposed ALMA scheme relies on four developments: (i) ingest from a pair of (modern) 100 Gb s<sup>-1</sup> links to a single GPU with a system-on-chip architecture (SOC), (ii) inbuilt many-core ARM processor and shared memory, (iii) PCIe4 external bus, and (iv) quad-rate (GPU) 8-bit math capability. The last three are already featured in production hardware, and the primary challenge lies in engineering one-way network capture at 200 Gb s<sup>-1</sup>, without packet loss. The record known capture rate as of 2014 into a server is 80 Gb s<sup>-1</sup>, which is divided between two GPUs, and achieved with low throughput 10 Gb s<sup>-1</sup> links. The target Tegra GPU hardware will be introduced to the retail market in 2018. Examples of requisite individual technologies are already available in products. In particular, present-day non-SOC, GPU cards have been reported to support at least 100 Gb s<sup>-1</sup> ingest.

The secondary challenge tied to a GPU platform is output of autocorrelation spectra for each antenna and BBC pair on time scales O(1-10) ms without bus saturation inside the GPU. In the event the associated memory traffic interferes critically with cross-multiplication and accumulation, the fallback is to rely on the ARM processor to compute self-products and export them (corresponding to < 1.3% of the input data rate) to the network.

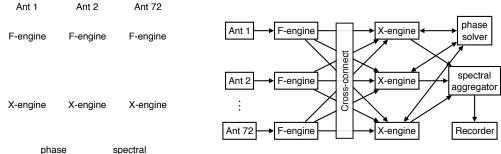

#### 2.6 Determine optimal X-engine architecture

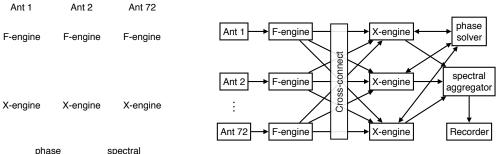

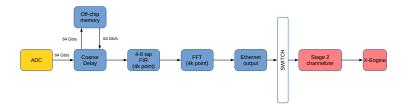

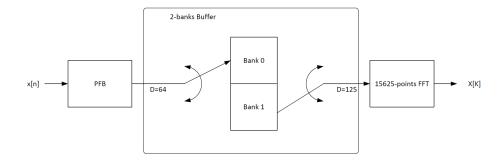

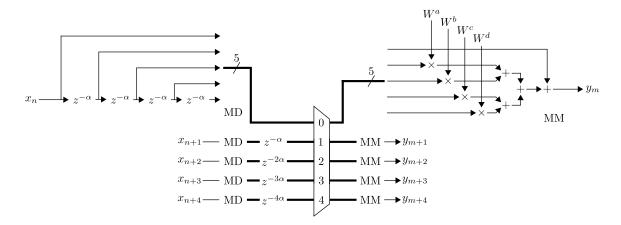

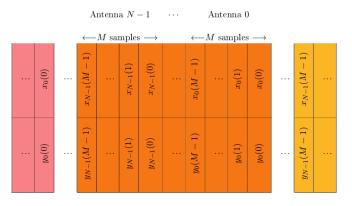

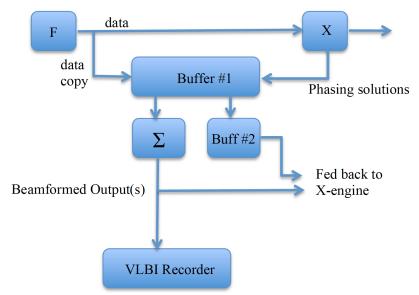

phase spectral solver aggregate

Figure 4 Overall FX correlator system architecture. Each X-engine units accepts as input a small portion of the full spectrum to be correlated from all antennas. The full-polarization cross products are calculated and accumulated before being sent back through the network for further processing. The X-engine also accepts real-time phase calibration solutions from a VLBI phase calibration engine, which are used to beamform the array data to targeted locations in the field-of-view.

The X-engine nodes process spectral data gathered from the F-engines, and send accumulated correlation products and synthesized beams back over the network. Figure 4 shows a simplified system digram with the essential elements of the correlator. Each X-engine unit accepts a fraction of the total bandwidth from all antennas, and the correlation of these spectral ranges are done in parallel. External elements of the special beamforming subsystem include the real-time phase calibrator, which aggregates visibilities across the entire bandwidth in order to solve for a unique set of antenna phases, and the spectral aggregator which accepts slices of beamformed data from all the X-engines in order to reconstruct and reformat a beamformed data stream to a given specification.

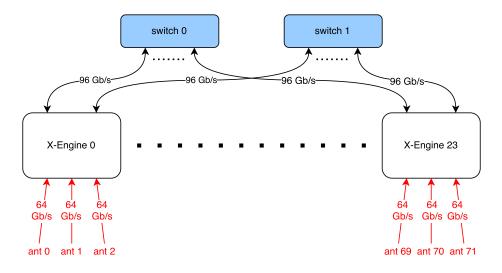

The X-engine platform chosen in the cost and power-comparison study (WP 2.5) is a cluster of Nvidia system-on-chip (SoC) devices connected to the correlator through two 100 GbE NIC over a PCI-Express version 4 backplane. Together the three devices make up an "X-engine unit", and each unit operates independently on a small slice of the total array bandwidth (~160 MHz) prior to final downstream accumulation and processing. Each SoC device includes an ARM multi-core CPU, an Nvidia GPU, both connected to a moderately sized (many GB) block of Unified Memory.

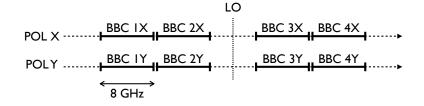

Figure 5 Frequency setup and location of 8 GHz Nyquist-sampled baseband channels (BBC) for one dual-polarization ALMA receiver. Adjacent BBC's may overlap slightly if necessary for continuous coverage of usable bandwidth, although the correlator is designed to be able to process the full  $8 \times 8$  GHz of bandwidth. With 4-bit sampling, the total data rate is  $8 \times 64$  Gbps per antenna.

Table 4 Resource requirements of X-engine, given optimal processing of 4+4 bit complex input data, 32+32 bit complex accumulated output, and 4+4 bit complex beamform output. Output rate is calculated at 100 kHz channelization  $\times$  1 second accumulation, from which figures can be directly scaled to other resolutions. Memory usage and bandwidth are calculated for 1.6 kHz uniform resolution (100k total channels per unit) and 0.1 second initial transpose buffer, plus 4 output beams. Finally we show the equivalent capacity of a hypothetical platform based on the next-generation Nvidia Xavier AI SoC paired with two 100 Gbps NIC's on a PCIe-v4 backplane. DLOP (deep learning operation) refers to one 8-bit multiplication with 32-bit accumulation.

| Resource                                | Total                | per node $(200)$     | Xavier AI unit      |

|-----------------------------------------|----------------------|----------------------|---------------------|

| DLTOPS                                  | 1419                 | 7.1                  | 20                  |

| Input I/O                               | 4.6  TB/s            | $23~{ m GB/s}$       | $25 \mathrm{~GB/s}$ |

| Output I/O                              | $27~\mathrm{GB/s}$   | $0.13~\mathrm{GB/s}$ | $25~\mathrm{GB/s}$  |

| Beamform $I/O$                          | $256~\mathrm{GB/s}$  | $1.3~\mathrm{GB/s}$  | -                   |

| Transpose memory $(0.1s)$               | 9.2 TB               | $4.6~\mathrm{GB}$    | 16-32  GB           |

| Accumulation memory $(1.6 \text{ kHz})$ | 1.7 TB               | 8.4 GB               | 16-32  GB           |

| Memory bandwidth                        | $25.2~\mathrm{TB/s}$ | $126~{ m GB/s}$      | $160~{ m GB/s}$     |

Anticipated specifications for Nvidia Xavier SoC (sampling Q4 2017) are listed in table 4, along with the anticipated resource requirements distributed across 200 units. While future generation hardware is likely to be available by the time of correlator hardware acquisition, this study outlines an X-engine architecture that fits within the limitations of the anticipated Xavier platform.

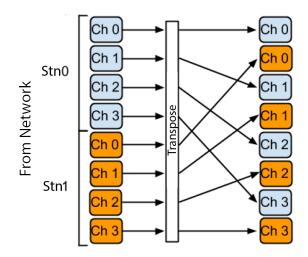

Fundamentally the cross correlation operation performed by an X-engine is trivially parallelized over time and frequency as each spectral point is independent. Efficient pipelining of the staging, correlation and accumulation of antenna data in an FX correlator are available for GPU (Clark et al, 2012) and FPGA (Parsons et al, 2008) based architectures. In both architectures, the input data is first transposed so that data are sent to the X-engine in an order such that nearby data are the ones being accumulated. Beyond this transpose, the X-engine can be relatively agnostic to the specific parameters of accumulation. For GPU correlation, a tiling strategy breaks up the full array matrix outer product into blocks which enables efficient coalesced memory transfer, as well as a high degree of parallelization of smaller calculations across the  $\sim O(\text{hundreds})$  of GPU cores.

A complete time-frequency transpose is not possible for 1 kHz spectral resolution resolution due to the large amount of memory needed to buffer the full integration time of 30 seconds or longer. Instead only a partial transpose ( $\sim 0.1$ s) occurs prior to correlation, and further accumulation is done on temporary accumulation products staged to device memory. Balancing the memory and memory bandwidth requirements of these two buffers (transpose and accumulation) is a challenge given the specifications of the ngALMA correlator. A high-utilization case of uniform 1.6 kHz resolution and 0.1 second initial transpose is shown in table 4. The requirements can be reduced by only keeping a fraction of the bandwidth at such high resolution (zoom mode).

A beamforming sub-system is present in the X-engine design which allows phase alignment and stacking of antenna data to form up to 4 synthesized beams on the sky. For real-time on-source phase calibration, the X-engines send in near-realtime cross visibilities to a single phase calibration engine, which solves for time-dependent antenna-based phase variations due to the atmosphere. The phase solutions are sent back to the X-engine units, which use the residual phase information to stack the data from all 72 antennas coherently at up to 4 phase reference locations within the

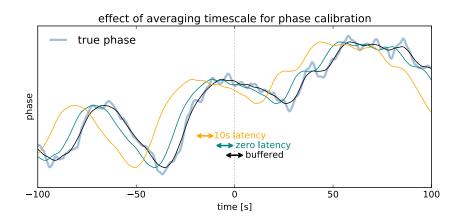

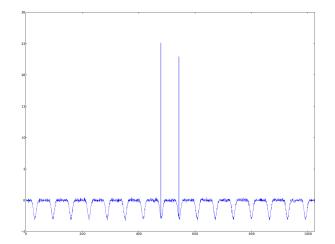

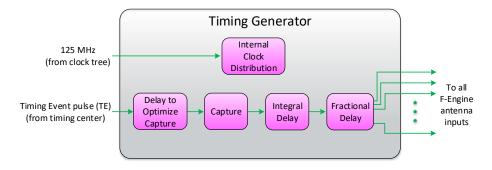

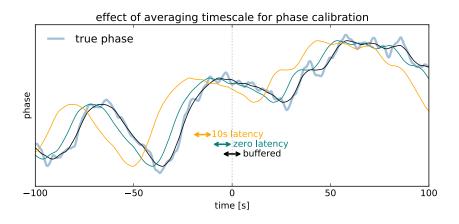

Figure 6 Effect of latency on estimate of antenna phase. The real-time phase calibration feedback latency of the new correlator is expected to be under 1 second, providing more stable band 6 phasing under moderate atmospheric conditions than the existing system. A data input buffer that is  $\sim 25\%$  the atmospheric coherence timescale or longer also significantly improves phasing performance.

primary beam. The effect of latency on antennas phase is illustrated in For a handful of beams, the resource use on the X-engine for this O(N) operation is minimal, and it can easily be supported in parallel with the cross correlation.

## 2.7 VLBI capability

Beamforming the ALMA dishes creates a high sensitivity VLBI capability for ALMA that can be used to anchor centimeter, millimeter and submillimeter VLBI arrays for ultra-high angular resolution and sensitivity science applications. A full science case for ALMA beamforming is detailed in Fish et al (2013). The Next Generation ALMA Correlator will have native beamforming capability that far exceeds that of the present ALMA Phasing System (APS), enabling VLBI at high frequencies and under a variety of atmospheric conditions.

#### 2.7.1 Beamforming requirements

Beamforming for VLBI and pulsar applications imposes several specific requirements, some of which are necessarily dependent on the atmospheric conditions, array configuration and observing Band.

- Phasing efficiency of the antenna grouping in a coherent sum will be > 95%

- Phasing of the array will be done as near to real-time as possible. This requires that either:

- the target phasing efficiency can be achieved in an integration time short compared to the atmospheric coherence time on a calibrator source, *and* that system latencies are also short compared to atmospheric coherence, or

- a buffer is used to store data so that phasing solutions can be applied to the data used in the solution.

- A real-time measure of phasing efficiency should be computed.

- Polarization leakage in the phase sum should be no greater than the average leakage for a single antenna.

- Data output of the phasing system should be available in standard VLBI format (2, or 4-bit data with suitable headers e.g., VDIF).

- Multiple beams may be formed within the primary beam of the ALMA antennas

- Beams may be formed on sub-arrays of antennas and on sub-bands in frequency

- Phasing efficiency shall be as stable as the atmospheric coherence timescale

- Several modes of phasing should be implemented: phasing on in-beam target, phasing on in-beam calibrator, phasing on out-of-beam calibrator.

- Should be capable of correcting for source model and time variable atmospheric screen.

- Phasing should be available for all ALMA Bands.

• For the pulsar case, the requirement is to be able to detect millisecond pulsars with a Dispersion Measure of 3000 pc cm<sup>-3</sup>. This sets an upper limit on channelization of 32 MHz for ALMA Band 1. For pulsars, it is also desirable to maintain the maximum number of bits possible, but 2-bits are sufficient if any auto-leveling system has a time constant greater than 5 seconds.

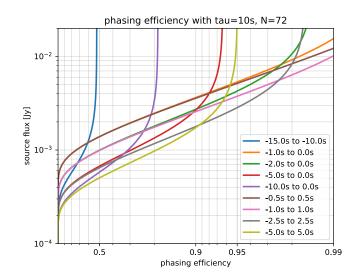

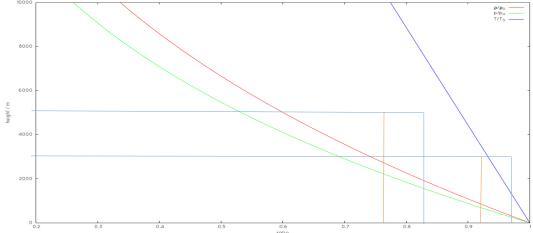

#### 2.7.2 Phasing Flux Density and Integration Time Limits

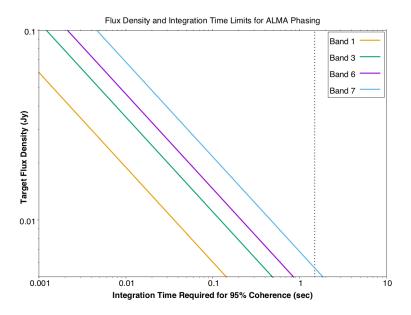

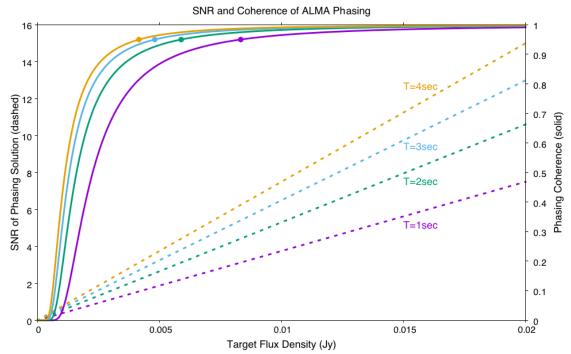

When all 72 antennas are combined and the full 64 GHz BW used to be amform, the required phasing efficiency can be obtained for short integration times that are not affected by atmospheric coherence and on sources down to a flux density of  $\sim 10$  mJy (Fig. 7). Because this figure assumes zero coherence losses due to atmospheric effects, including due to latency of the phasing solution, these flux density limits are understood to be lower limits.

Figure 7 Relationship between flux density of the source used for phasing and the integration time required to achieve 95% coherence in the phased sum for four ALMA Bands. Limits assume 72 dishes, use of the full 64 GHz BW in the phasing solution, and SEFD (Jy) for a single ALMA dish of 1300, 2400, 3200, and 4700 for Bands 1, 3, 6, 7 respectively. The vertical dashed line marks the coherence time of the array in Bands 6 & 7 for a PWV of 3mm (see Matsushita et al 2017). This figure assumes zero coherence losses due to atmospheric phasing effects, including latency. For the Bands shown, one expects to achieve coherent phasing for source flux densities down to 10mJy in integration times that are short compared to the atmospheric coherence time.

#### 2.7.3 Latency and Buffering

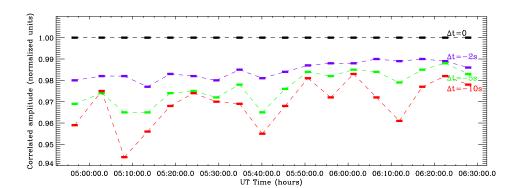

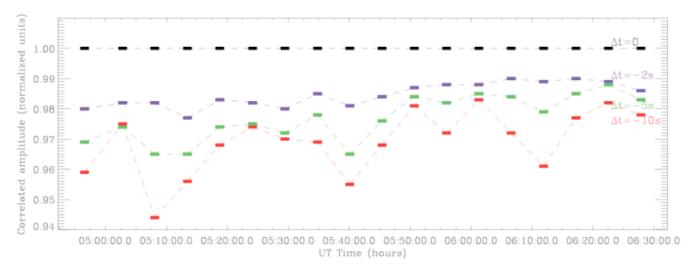

Latency in the context of beamforming is the offset in time between collection of the data for which phasing solutions are found and the application of those solutions to the array. For the current ALMA correlator and phasing system, there is a latency of 8-10 seconds, so that at any given time the coherent sum is being formed using phasing solutions that are 8-10 seconds out of date, and atmospheric turbulence, or changing phasing conditions of any kind, will cause coherence losses. The effect on coherence is shown in Fig. 8. In the next generation ALMA correlator it is expected that streamlining transfer of data, solving for phases, and implementing the solution will reduce latency to 10's of milliseconds. Since this is short compared to atmospheric coherence times, as is the integration time required to phase on typical calibrator sources (Fig. 7), phasing on in-beam targets should not require a data buffer.

For cases where slewing to a phase calibrator is required, a buffer that can store data for the duration of a fast-switching sequence may be useful. Such a buffer ( $\sim 10 - 20$  seconds) could potentially be included in the X-engine architecture. For 72 antennas, 4-bits, 64GHz of bandwidth, each second of buffering requires 4.5 TBytes of memory.

Figure 8 Coherence loss due to latency between the phasing solutions applied to the array and the data used to calculate those phasing corrections. For a 10 second latency, phasing efficiency in relatively good atmospheric conditions (PWV 0.9mm, RMS path length variations of ~ 125 $\mu$ m on 300m baselines: mean conditions at ALMA in May), can drop by 6%. This example uses Band 6 data on quasar 1924-292 from ALMA with phasing done a posteriori in CASA with 16 antennas summed. Figure made by Lynn Matthews.

### 2.7.4 Data Format, Data Transfer & VLBI Recorders

Modern VLBI recorders are essentially packet capture devices, that are currently capable of 16Gb/s. Packet headers, using the VDIF format, contain all the information required for routing of data in a VLBI correlator, including time-tagging. The VDIF format may still be useful in 2022 when the ngALMA correlator is constructed. It is also possible that network appliances that are essentially just packet recorders - perhaps with Solid State Storage - could replace VLBI recorders. Capturing a single 64 GHz beam at 2-bits (256 Gb/s) could potentially be supported by extension of current VLBI recorder architectures, but to capture 4 beams, each 64 GHz bandwidth and 4-bits, the data rate would be 2048 Gb/s, for which a new generation of recorders would be required.

#### 2.8 Staging the new correlator and phased array system

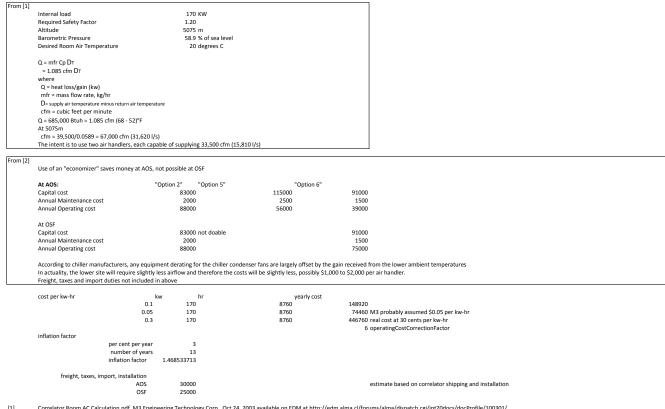

A study of the costs and trade-offs associated with four possible locations for the new correlator was one of the work packages completed. We studied the implications of siting the new correlator at the Array Operations Site (AOS) and the Operations Support Site (OSF). Also, we considered both new construction and re-purposed space in both instances. Both real costs and the costs of lost science and productivity are included in the summary. Table 5 covers construction costs, and table 6 covers operational costs. Assumptions that were made, as well as the basis for various costs, are summarized in the full work package report, included in the appendix.

Table 5 A summary of the costs of construction of a new correlator, including both the direct costs of construction—a function of whether it is sited in existing space or in new construction—and the opportunity cost of observation time lost due to new construction in space presently occupied by mission critical equipment.

| Item              | AOS Existing | AOS New  | OSF Existing | OSF New |

|-------------------|--------------|----------|--------------|---------|

| Rackmount         | \$10k        | \$100k   | \$100k       | \$100k  |

| HVAC              | 164k         | 164k     | 58k          | 158k    |

| Construction      | \$0          | \$1.3M   | 320k         | 708k    |

| Install time      | 50k          | 50k      | 50k          | 50k     |

| Travel            | \$10k        | \$10k    | \$10k        | \$10k   |

| Signal Transport  | \$0          | 20k      | 2.4M         | 2.4M    |

| Total             | 380k 1.644M  | \$3.088M | \$3.426M     |         |

| Lost Science Time | \$10M        | \$0      | \$0          | \$0     |

An interesting point is that the estimate of the cost of lost observation time, which is an opportunity cost based on the capital investment ALMA represents amortized over the expected 30

| Table 6 A summary of the costs of operating a new correlator, including both the direct operational   |

|-------------------------------------------------------------------------------------------------------|

| costs, which depend on where the new system is located, and the imputed cost of lost observation time |

| due to delays in rendering repairs to equipment located at the high site                              |

| Item              | AOS Existing | AOS New | OSF Existing | OSF New   |

|-------------------|--------------|---------|--------------|-----------|

| HVAC              | \$1190k      | \$1190k | \$2247k      | \$2247k   |

| Lost tech prod.   | \$400k       | \$400k  | \$0          | \$0       |

| Vehicle costs     | 62k          | 62k     | \$0          | \$0       |

| High alt bonus    | 37k          | 37k     | \$0          | \$0       |

| Risk to personnel | ?            | ?       | \$0          | \$0       |

| Total             | \$1.689M     | 1.689M  | \$2.247M     | \$2.247MM |

| Lost Science Time | \$59M        | \$59M   | \$0          | \$0       |

year lifetime of the instrument, is the dominant cost in two of the four cases studies. In particular a roughly estimated cost of \$59M was assigned to observation time lost due to the delays in making repairs to faults for equipment located at the high site. While this estimate is highly uncertain it was based on experience with the current correlator, with more details of the calculation in the WP2.8 appendix.

The OSF becomes a viable choice for siting the new equipment if this important opportunity cost is considered. Developments in fast data communications technologies with rates 100Gbps+ have made consideration of siting at OSF possible. As a counterpoint, one benefit of the proposed packetized FX architecture is that if one processor fails another can dynamically be re-assigned. Thus it is at least plausible that the new system may be more reliable, or at least fail in a softer way, which could potentially improve the extremely high opportunity cost of maintenance at AOS estimated here.

We emphasize again that the uncertainty in the numbers is high. Even so, opportunity cost is a real cost, even if not representing a cash outlay, and the potential return estimated here in our opinion means that this siting question warrants further study. We recommend that JAO carefully review the trade-offs and actively participate in the discussion of where best to site this next generation correlator and phased array.

## 3 A conceptual design and buildout roadmap

This section outlines a conceptual design and roadmap for full realization of a next-generation ALMA correlator and phased array with specifications set in section 2.1, and technologies and algorithms based on those selected in this Study. The overall program for development is split into three phases with a timeline that is aimed at completion and commissioning of a new digital system by 2026. Following the general principles described in this Study, the new system will minimize design time, optimize use of the latest "Commercial Off-The-Shelf" (COTS)components, and be capable of supporting all projected ALMA upgrades referenced in the community documents: A Roadmap for Developing ALMA, and Pathways to Developing ALMA. The plan for the full buildout Phase III is of course tentative in nature. It is provided to demonstrate that the Study solutions are broadly feasible on reasonable timelines and at tractable cost.

The three phases of the program are:

- *Phase I Study*: This phase is now complete and the results are described in this document. This phase has assembled an expert team with experience in correlator design for centimeter, millimeter and submillimeter wavelength arrays, including developers of the original ALMA correlator. The study has drafted first science requirements and specifications, identified a design approach, and explored computational platforms and possible architectures.

- *Phase II Project: Prototype*: This phase transforms the results of the Study into a detailed design and construction of a prototype system capable of processing a subset of ALMA antennas and bandwidth: 8-stations, dual-polarization, 8 GHz bandwidth. The project includes comprehensive laboratory testing using an antenna emulator engineered to allow iteration on the design and refinement of cost estimates. Phase II will develop a resourced schedule for building, installing, and commissioning the full system. This phase has been proposed as an ALMA Development Project by the Study team, with participants across ALMA regions.

• Phase III - Implementation, buildout and commissioning: With completion and testing of the prototype, the program continues with a formal review of the concept and a subsequent series of milestones including Preliminary Design Review (PDR), Critical Design Review (CDR), and multiple readiness reviews. Preliminary Acceptance In-house (PAI) and Preliminary Acceptance on-Site (PAS) will be completed for all subsystems, followed by Assembly, Integration and Verification (AIV). Finally Commissioning and Science Verification (CSV) will be completed under the oversight of JAO. During this phase, the final hardware platforms will be decided and procured, software and firmware refined, interfaces to all ALMA systems detailed and integration and testing plans executed.

Phase II (2017-2020) has been specified with a 3-year schedule in detail in our ALMA Development Project Proposal. A tentative and approximate timeline and equipment costing is given for Phase III (2021-2026). Substantial refinement of Phase III is expected as Phase II is executed, and one of the of the deliverables of Phase II will be to identify the work packages for Phase III. Also by the end of the the Phase II stage we will supply a more accurate estimate of the total power and total cost for the full installation. This will naturally depend on whether the choice is made to install the new system at the AOS or the OSF, as studied in WP2.8, which will naturally also impact the cooling requirements.

#### 3.1 System engineering and project management

At its heart, the next-generation Correlator and Phased Array studied herein is the central component of a system-wide bandwidth enhancement for ALMA. As such it presumes availability of wideband receivers, analog-to-digital converters, Digital Transmission System (DTS) and a data pipeline with commensurate increases in capacity and speed. And more than that, this study emphasizes that a next-generation Correlator will necessarily exist within the context of an overall system-engineering plan for ALMA Development. This conceptual design can serve as input to that process.

Our approach to system-engineering for this study is informed by the recently completed ALMA Phasing Project (APP), which was one of the first official ALMA upgrades that went through all phases of the Development Project process. This included close connection with the JAO on:

- Development and Design of the proposed system

- Establishment of Interface Control Documentation (ICD) with other ALMA systems

- Formal Science Requirements, Technical Specifications and Verification Matrix

- Integration and Test Plans

- Design Reviews that adhered to ALMA protocols

- Commissioning Plan

- Identification of impact on JAO personnel and resources

- Acceptance with full documentation, training and support for JAO personnel

Adoption of these project management elements has now resulted in the APP being made available to the ALMA community in Cycle 4 and Cycle 5 observations for ultra-high resolution and sensitivity science in Bands 3 and 6. Just completed Band 3 and 6 VLBI observations with the phased ALMA in April 2017 for Cycle 4 appear to have gone very well, and are testament to the technical, management and resourcing strategies of the APP as well as a strong partnership with the JAO.

With this positive experience as a foundation, our view is that the proposed approach to the next-generation ALMA Correlator, while ambitious and forward looking, can be realized in a staged manner that minimizes risk and maximizes science return per dollar. As an example, we would propose to first build a sophisticated 8 antenna ALMA simulator, with fringe Doppler, delay tracking, programmable SNR, that is capable of producing visibilities for a complex sky image. This enables full testing of next-generation prototypes without the need to stage them at the ALMA site.

## 3.2 Phase II: Prototype

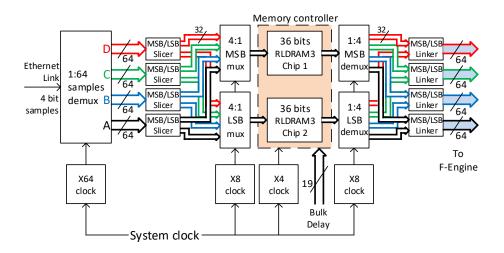

The proposed correlator and phased array is an optimized supercomputer that takes data over a packetized network interface at its input, and delivers data such as cross-correlation fringe visibilities, and coherently phased sum of antennas, at its output. It has dual polarization, and an 8 GHz "BBC bandwidth" which readily scales by replication to the 64 GHz instantaneous sky coverage our Study requirements target. An ultra-fine spectral resolution setting of 1 kHz is available, useful

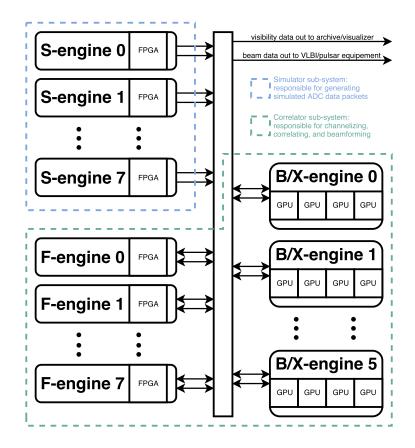

Figure 9 Simplified block diagram of the Project Phase II bench system at the top level showing the simulator and correlator sub-systems as they attach to the 100 GbE switch interconnect (the thin central rectangle). Data from the simulator, emanating from multiple "S-engines", is sent out to the switch in packets mimicking the eventual ADC- sample containing packets expected from the next-generation ALMA DTS system. The data is routed in a one-to-one pattern from S-engine to the channelizer boards, the so- called "F-engines". Both the S- and F-engine will be implemented using the Xilinx VCU118 FPGA and will emit and accept, respectively, two polarizations each. Every F-engine will then divide its outgoing channelized data and route subsets of channels to the corresponding "BX-engines", so called because they simultaneously correlate and beamform. The BX-engines then route the correlated and integrated data out of the correlator to the archive while the beamformed data is sent to either the VLBI or pulsar backends. Note that every arrow in the diagram denotes a single 100 GbE link to the switch, some are used bidirectionally (F- and BX-engines) while others are not (S-engines).

to resolve lines in cold starless cores using ALMA Band 1. This resolution aggressively drives the output data rate, so modes to throttle the data rate need are provided.

The Phase II Project proposes to build a fraction of the system developed in this Study. Parameters are 8 antennas, dual polarization, with an 8 GHz BBC bandwidth per polarization processed. All hardware for this Project will be *Commercial Off The Shelf* (COTS). Phase II is a variation of the FX approach pioneered by the Collaboration for Astronomy Signal Processing and Electronics Research (CASPER, see Hickish, 2016). FGPA processors are arranged around a fast network switch, which implements the crossbar function needed to transform antenna-based input (F-engines) to the baseline antenna pairs which are cross-correlated to produce the fringe visibilities. In the SMA SWARM system (Primiani et al., 2016), F-engines and X-engines are merged onto a single FPGA processor. For the much more demanding requirements of ALMA this Study found that the F-Engine is still optimally implemented with a Field Programmable Gate Array (FPGA) platform, but the X- engines are moved to a separate processor, per WP2.5, best computed on Graphic Processing Units (GPUs). The overall Phase II system block diagram is shown in figure 9.

#### **3.3** Phase III: *Tentative* implementation and buildout outline

The Phase II Project costs out an 8 antenna 16 GHz (8 GHz dual polarization) system with technologies now—in 2017—on the cusp of availability. The purpose of Phase III is to show that the scale up to a full ALMA installation is *already* feasible using these technologies and algorithms selected for the Project. By December 2021—which is cautiously suggested as the start of full construction and the technology freeze date—a review of current technology would require a fresh look at selection and costing of appropriate FPGA, GPU and high speed network technologies. Assuming specifications stay as here proposed it is anticipated that costs of digital hardware should generally decline.

It should be noted that our expectation is for the Cycle 5 Project to allow us to finalize algorithms and codes, all of which are expected to be readily portable to the latest technology selected for the full build. A caveat applying to this section is that we are only able to credibly cost the technology to set a expected upper bound on the costs of the major components; we do not attempt to cost the labor to install, commission and properly document the full system.

Details such as properly installing and cooling the electronics are not discussed, nor is the site decision built in to this top level estimate. Such details would be considered with the assistance of JAO after the completion of the Phase II Project. The schedule is similarly a rough estimate, whose purpose is to show that the architecture and technical approach is in the ball park of feasibility.

Scaling from the project to the full implementation requires scaling by a factor of 4x in bandwidth and 9 times in schedule, or 36-fold in total. So the number of F-engines is 36 x 8 or 288. Each has two network ports, so 576 network ports are required for F-engines. An equal number of ports are required for X-engine GPUs. Further, the antenna data is assumed to be provided in place of the emulator inputs, and the number of switch ports is calculated as 72 antennas x 2 polarizations x 2 sidebands x 2 bandwidth blocs per polarization, also 576 ports needed. These means we need 1,728 100 GigE Ethernet ports for antennas, F-engines and X-engines. To make a cost estimate we assume 32 port switches are \$14,997.50 each (Arista DCS-7060CX-32S-F), and we need 54 of these.

The Project Proposal block diagram shows 8 GPU servers, however an analysis of new NVIDIA Tegra GPU technology, not available when the Project was proposed in January, shows that the number of GPU nodes scale up to 48 units (see WP2.5). The four AMTF servers to house F-engines scale up to 144 units. One network cable is costed per port. Table 7 is a rough calculation of the estimated cost of major components only, It excludes necessary and important items such as equipment racks, uninterruptible power supplies (UPS), power wiring, and similar infrastructure, these will be included in the Phase II Project work.

| Quantity | ntity Item description           |          | Extended Cost |

|----------|----------------------------------|----------|---------------|

| 576      | Xilinx VCU118 FPGA Eval. Board   | \$6,995  | \$4.03M       |

| 144      | AMTF Server SYS-6028TP           | \$8,595  | 1.23M         |

| 48       | Trenton Systems Tegra GPU Server | \$18,200 | 0.873M        |

| 54       | Arista DCS-7060CX-32S-F          | \$14,998 | 0.809M        |

| 1728     | Network Cables CAB-Q-Q-100G-5m   | \$450    | 0.778M        |

Table 7 ALMA Correlator COTS Equipment Cost Summary

Considering the major COTS components in table 7 the cost of equipment only for a 72 antenna 64 GHz total bandwidth correlator and phased array built according to the principals found in this study is just under \$8M.

Table 8 is a power budget which uses these same assumptions, and estimates of per unit power consumption to estimate the total power consumption of the full correlator and phased array system scales to about 110 kW, compared to about 140 kW for the current ALMA correlator. Air conditioner ppwer is not included in either number. Given that the new system processes fourfold the bandwidth, and considering other improvements, this power consumption is considered to be in a reasonable ballpark. With true 2021 technology it is anticipated that power consumption would be reduced with the new system.

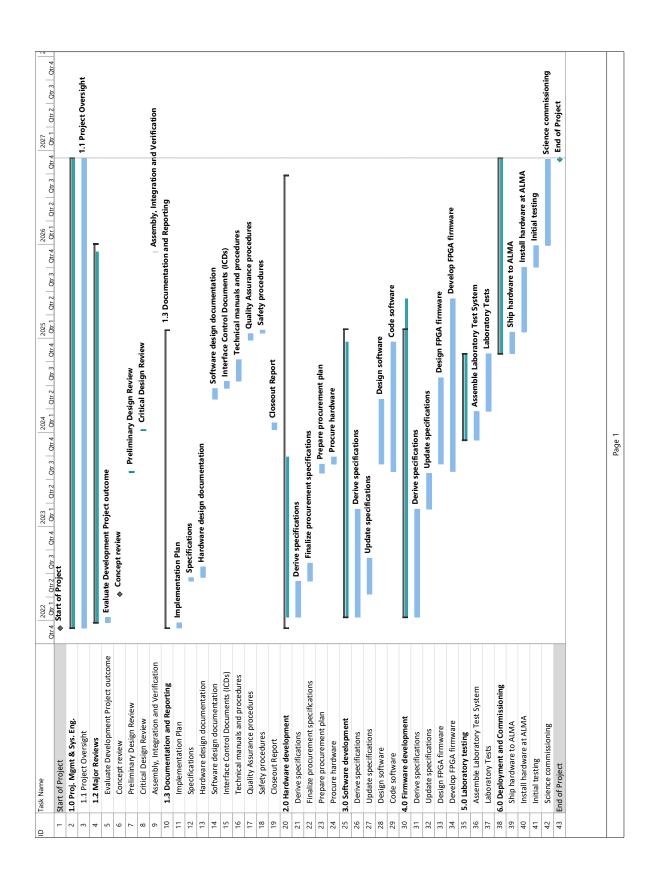

Figure 10 shows the outline of a Gantt chart documenting a schedule to build this Correlator Phased Array system and commission at ALMA starting in December 2021. A five year period of performance is suggested based on very rough estimates of workflow as presented in the Gantt chart. Following this schedule ALMA would be equipped with a fully commissioned digital back end with integrated VLBI capability by December 2026.

| Quantit | ty | Item description                 | power p.u. (kW) | total power (kW) |

|---------|----|----------------------------------|-----------------|------------------|

| 57      | 76 | Xilinx VCU118 FPGA Eval. Board   | 0.12            | 69               |

| 14      | 44 | AMTF Server SYS-6028TP           | 0.1             | 14.4             |

| 4       | 48 | Trenton Systems Tegra GPU Server | 0.375           | 18               |

| [       | 54 | Arista DCS-7060CX-32S-F          | 0.15            | 8                |

Table 8 Estimated power consumption summary

At the starting point of Phase III, the proposed Cycle 5 ALMA Development Project is assumed to be completed, and thus it it is expected that the technical risk of this deployment will be extremely low. Implementation then is an exercise in logistics, infrastructure, and proper ALMA compliant project management and documentation, including ICDs, notably for software.

Figure 10 Simplified possible schedule for five year follow-on to ALMA Development Project starting in December 2021, and culminating in December 2026 with the a fully commissioned 64 GHz bandwidth 72 antenna ALMA correlator and phased array. This sample schedule is expected to change as informed by the outcome of Phase II.

## 4 Summary and closeout

This ALMA Development Study has framed the approach to a design of a next generation correlator and phased array system with which it is possible to upgrade ALMA in a cost-effective manner, quadrupling the instantaneous bandwidth and dramatically increasing spectral resolution.

The Study ran according to the planned schedule starting work on 1 April 2016 and culminating in a closing meeting held as planned in February 2017. The goals have been met and a set of assumed requirements are available in this Study. We welcome comment from the International ALMA community, especially on the assumed requirements. There is a small funding surplus, which we plan to expend on the purchase of some of the specified equipment.

We have proposed for follow on ALMA Development funding for a Project to build a correlator and phased array system supporting eight antennas and 16 GHz total processed bandwidth, split into two polarizations of 8 GHz each. The concluding section of this report shows that it is feasible and cost effective to fit a system designed according to the principals articulated in this report to ALMA and to upgrade the digital systems, in a way assumed to be aligned with other necessary systems, with project completion in late 2026.

The key advances made by this study are summarized in the following bulleted list:

- Our expert international team has studied approaches to correlator design, and framed a risk mitigated three-phase approach to a complete upgrade of the ALMA correlator and phased array, with a projected completion date of December 2026.

- The Cycle 3 Study was completed on time and within budget.

- A follow on Project has been proposed in response to the Cycle 5 call, and is under consideration.

- The proposed approach allows for high performance in respect of bandwidth, spectral resolution, integrated phased array processing, smaller size and power consumption at reasonable and tractable cost.

- It is necessary that the proposed new generation correlator and phased array dovetail with upgrades to receivers, digitization modules, digital transmission system, and software pipelines. Dialog with ALMA management, project managers, and the International ALMA community is recommended. Such dialog, ideally, would culminate in a process of formal system design for the complete next generation ALMA upgrade, considering all subsystems.

- In particular the Specifications of this Study's Work Package 2.1 should be viewed as informed assumptions made by this Study team in consultation with a small group of scientists. The assumptions were necessary to complete the Study, but we do not presume to decide on the specifications of next generation ALMA. We welcome publication and broad feedback on these specifications, and on this Development Study report as a whole.

Expanded documents follow in the appendix, documenting the work breakdown and eight work packages in this study.

## References

Bolatto, A.,D, et al. *Pathways to Developing ALMA*, 2015, https: //science.nrao.edu/facilities/alma/alma-dev/PathwaystoDevelopingALMA.pdf/view

Bolatto, A.,D, et al. *A Road Map for Developing ALMA*, 2015, https://science.nrao.edu/facilities/alma/science\_sustainability/RoadmapforDevelopingALMA.pdf

Clark, M. A., P. C. La Plante, and L. J. Greenhill (2012). Accelerating Radio Astronomy Cross-Correlation with Graphics Processing Units. In: The International Journal of High Performance Computing Applications 27.2, pp. 178–192. doi: 10.1177/1094342012444794. arXiv: 1107.4264 [astro-ph.IM]

D'Addario, L.R., Emerson, D.T. 2000, ALMA Memo#331

Escoffier, R. P., Comoretto, G., Webber, J. C., Baudry, A., Broadwell, C. M., Greenberg, J. H., Treacy, R. R., Cais, P., Quertier, B., Camino, P., Bos, A., and , A. W. Gun (2007) *The ALMA correlator* A&A, 462(2):801 810.

Fish, Vincent; Alef, Walter; Anderson, James; Asada, Keiichi; Baudry, Alain; Broderick, Avery; Carilli, Chris; Colomer, Francisco; Conway, John; Dexter, Jason; Doeleman, Sheperd; Eatough, Ralph; Falcke, Heino; Frey, Sándor; Gab/'anyi, Krisztina; G/'alvan-Madrid, Roberto; Gammie, Charles; Giroletti, Marcello; Goddi, Ciriaco; G/'omez, Jose L.; Hada, Kazuhiro; Hecht, Michael; Honma, Mareki; Humphreys, Elizabeth; Impellizzeri, Violette; Johannsen, Tim; Jorstad, Svetlana; Kino, Motoki; K/"ording, Elmar; Kramer, Michael; Krichbaum, Thomas; Kudryavtseva, Nadia; Laing, Robert; Lazio, Joseph; Loeb, Abraham; Lu, Ru-Sen; Maccarone, Thomas; Marscher, Alan; Mart/'i-Vidal, Iv/'an; Martins, Carlos; Matthews, Lynn; Menten, Karl; Miller, Jon; Miller-Jones, James; Mirabel, F/elix; Muller, Sebastien; Nagai, Hiroshi; Nagar, Neil; Nakamura, Masanori; Paragi, Zsolt; Pradel, Nicolas; Psaltis, Dimitrios; Ransom, Scott; Rodr/'iguez, Luis; Rottmann, Helge; Rushton, Anthony; Shen, Zhi-Qiang; Smith, David; Stappers, Benjamin; Takahashi, Rohta; Tarchi, Andrea; Tilanus, Remo; Verbiest, Joris; Vlemmings, Wouter; Walker, R. Craig; Wardle, John; Wiik, Kaj; Zackrisson, Erik; Zensus, J. Anton (2013) *High-Angular-Resolution and High-Sensitivity Science Enabled by Beamformed ALMA*, arXiv: 1309.3519 Hampson, G.,

Brown, A., Neuhold, S., Bunton, J., Macleod, A., Tuthill, J., and Beresford, R. (2013). Askap advancements in beamformer and correlator optical backplane technology. In 2013 US National Committee of URSI National Radio Science Meeting (USNC-URSI NRSM), pages 11.