A novel clock and timing approach for achieving 200+ km ALMA baselines B. Carlson, Rev. 1 2021-04-09

## A novel clock and timing approach for achieving 200+ km ALMA baselines

Brent Carlson, Herzberg Astronomy and Astrophysics, National Research Council Canada (Brent.Carlson@nrc-cnrc.gc.ca)

Rev. 1, 2021-04-09

#### Abstract

"A topic of particular interest to the NA ALMA Development Program" in the ALMA Cycle 9 Call for Project Proposals is longer baselines "to enable qualitatively new science." Research into the novel approach of "incoherent clocking" (IC) has been underway by the author at NRC-Penticton for the last ~2.5 years and this approach is poised to deliver this capability. In this approach, each antenna is outfitted with its own free-running, independent Local Oscillator (LO)—and thus is incoherent with all other antennas—and it is used as the antenna's local frequency reference to develop all down-conversion and digitization frequencies. Subsequently, using all-digital methods and all-digital fiber optics, both implemented with Commercial Off-The-Shelf (COTS) devices, the antenna LO's (aLO) varying frequency vs time is measured, relative to a central/common reference frequency, and the digitized science data is subsequently digitally corrected to the common reference before correlation and beamforming. The key advantage of this method for ALMA is a substantial increase in baseline length to 200 km or more (meaning fiber reaches of 100 km or more), at the lowest cost possible in terms of equipment and fiber routing for these longer baselines. A second advantage of IC is that the number of sub-arrays is no longer restricted by the number of photonic references—each antenna's observing frequency can be set independently of others, limited only by the agility of frequency synthesizers available at the antenna. Thus, the number of sub-arrays is limited only by the number of antennas available and, of course, by correlator agility in this regard. Finally, a subtle but important advantage of IC is that spurs and low-level spectral copies, due to interleaving in digitizers, do not correlate since they are digitizer clock frequency-dependent and therefore are at different frequencies for each antenna. This leads to better fidelity in visibility data products. What follows in this memo is a deep dive into IC research thus far, to hopefully convince the reader that the IC approach is indeed feasible for ALMA, even for Band 10.

# **Document History**

| Date       | Revision | Person     | Change Description                                                         |

|------------|----------|------------|----------------------------------------------------------------------------|

| 2021-02-14 | Α        | B. Carlson | Initial release for internal review; Abbr & acronyms TBD.                  |

|            |          |            | References still need to be fleshed out and cleaned up.                    |

| 2021-02-15 | В        | B. Carlson | First completed version ready for internal review.                         |

| 2021-02-22 | С        | B. Carlson | Fix some errors: PLL phase noise spurs; notion of                          |

|            |          |            | ReSampler integrated with the Talon VCC OSPPFB;                            |

|            |          |            | resampling error sensitivity loss. Still needs grammar fixes.              |

| 2021-03-02 | D        | B. Carlson | Simplify and clean up the parts of section 3 and section 4.1.              |

|            |          |            | Establish an aLO and Frequency Tracker phase noise budget                  |

|            |          |            | of 20 fsec RMS based on current ALMA antenna electronics                   |

|            |          |            | budget of 65 fsec. Still need to fill in some simulation                   |

|            |          |            | results in section 4.1                                                     |

| 2021-03-03 | Е        | B. Carlson | Fill in numbers for simulation results in section 4.1.                     |

| 2021-03-05 | F        | B. Carlson | Change the ADC jitter equation on p. 14 to 2 <sup>-(ENOBs+2.5)</sup> to be |

|            |          |            | more accurate. This puts the ADC ADEV at ~1.3e-11.                         |

| 2021-04-09 | 1        | B. Carlson | Change the ReSampler diagram Phase DDS and description                     |

|            |          |            | to not require multiple DDDs, just one 'Phase_o' DDS,                      |

|            |          |            | whose output is scaled to the required sky frequency                       |

|            |          |            | before application to the I/Q mixer. Also, don't need                      |

|            |          |            | multiple antenna synthesizers, just agile ones for desired                 |

|            |          |            | tuning flexibility. Internally reviewed by SH and MP, first                |

|            |          |            | full release. Also, add Appendex with derivation of                        |

|            |          |            | equation (5) on p. 29.                                                     |

# Table of Contents

| In  | ntroduction                                                                   | 8                            |

|-----|-------------------------------------------------------------------------------|------------------------------|

| 0   | verview                                                                       | 8                            |

| A   | ntenna clock stability and LPFF requirements                                  | 12                           |

| Te  | echnical descriptions                                                         | 14                           |

| 4.1 | Central-site Frequency Tracker design and performance                         | 14                           |

| 4.2 | Round-trip phase tracker                                                      | 20                           |

| 4.3 | Tracer DDS and discrete-time phase sampling                                   | 23                           |

| 4.4 | The ReSampler                                                                 | 26                           |

| 4.5 | IC tracer synchronization and signaling — "IC_telem" protocol                 | 34                           |

| D   | ynamic end-to-end behaviour                                                   | 35                           |

| Ce  | entral-site timing distribution to Frequency Trackers                         | 37                           |

| IC  | Cand DTS link-loss fail over operation                                        | 40                           |

| FF  | PGA Rx CDR PLLs and PLL frequency synthesizers                                | 42                           |

| IC  | Cimplementation architectures for ALMA                                        | 44                           |

| 9.1 | Architecture A                                                                | 45                           |

| 9.2 | Architecture B                                                                | 47                           |

| 9.3 | Architecture C                                                                | 49                           |

| 9.4 | Architecture D                                                                | 51                           |

| 9.5 | Architecture E                                                                | 52                           |

| 0   | Risk analysis                                                                 | 54                           |

| 1   | Review and conclusions                                                        | 57                           |

| 2   | References                                                                    | 58                           |

| 3   | Appendix – Derivation of the ReSampling DDS' pinc equation (5)                | 60                           |

|     | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>D<br>C<br>(9.1<br>9.1<br>9.2<br>9.3<br>9.4 | 4.2 Round-trip phase tracker |

# Table of Figures

| ♀         |

|-----------|

| .11       |

|           |

| DEF       |

| /E        |

| .14       |

| _         |

| c.        |

| .15       |

| IAL       |

| .16       |

| EC        |

| •         |

| .17       |

| .86       |

| NC        |

| .18       |

| .18       |

| .18       |

| E-7       |

| .19       |

| .20       |

| ), II     |

| ST-       |

| .21       |

| Ξ         |

|           |

| .22       |

|           |

| (1.6      |

| .22       |

| HIS<br>HE |

| .23       |

| HE        |

| HE        |

| ON.       |

| 23        |

| :UIT      |

| ΑY-       |

| .25       |

| .26       |

| RON       |

| .27       |

|           |

| FIGURE 4-17 BLOCK DIAGRAM OF THE "RESAMPLER", WHICH INCLUDES AN INTEGRATED PHASE ROTATOR, BUT DOESN'T INCLUDE T                                              |                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| FREQUENCY TRACKER OR LPFF, SHOWN HERE FOR CONTEXT.                                                                                                           |                    |

| FIGURE 4-18 FPGA RTL SIMULATION WAVEFORMS FOR THE LOWER 37 BITS (OF 64 BITS) OF PINC FED TO THE RES DDS INDICATING                                           |                    |

| ALL BITS ARE BEING "TICKLED" DUE TO THE DITHERING EFFECT OF A NOISYF_TR_DIFF ON EQUATION (5)                                                                 |                    |

| FIGURE 4-19 FPGA RTL SIMULATION WAVEFORMS FOR THE LOWER 36 BITS (OF 64 BITS) OF PINC FED TO THE FEEDBACK DDS OF                                              |                    |

| Frequency Tracker (Figure 4-2) indicating that all bits are being "tickled" due to the dithering effect of a noise                                           |                    |

| F_TRACER_LOOP.                                                                                                                                               |                    |

| FIGURE 4-20 "IC_TELEM" PROTOCOL USED IN THE LAB DEMO DISCUSSED IN [3]. THIS PROTOCOL IS USED FOR RELIABLE IC SIGNALIN                                        |                    |

| BETWEEN THE ANTENNA AND THE CENTRAL SITE. $M$ INIMUM $N$ PR IS PROBABLY $^{\sim}4$ , BUT MAY BE ADJUSTED TO MEET SYSTEM F                                    |                    |

| CADENCE REQUIREMENTS, IF ANY.                                                                                                                                |                    |

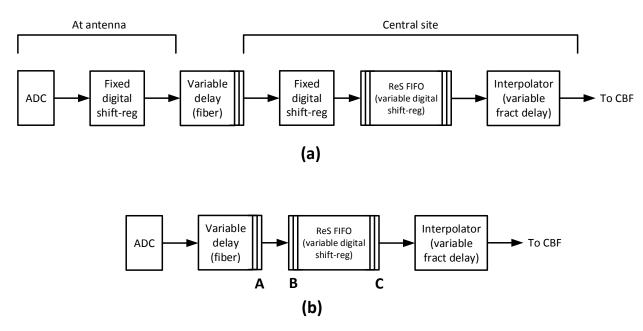

| FIGURE 5-1 DYNAMIC END-TO-END BEHAVIOUR DIAGRAM. THE "FIXED DIGITAL SHIFT-REG" BLOCKS IN (A), ARE EFFECTIVELY ABSOR                                          |                    |

| INTO THE INPUT SECTION OF THE RES FIFO, RESULTING IN THE SIMPLIFIED VIEW SHOWN IN (B)                                                                        |                    |

| FIGURE 6-1 ACTIVE ROUND-TRIP MEASURED METHOD. ROUND-TRIP MEASURED PHASE, ACROSS EACH FULL-DUPLEX DISTRIBUTION (                                              |                    |

| INDEPENDENTLY, IS MEASURED AND SENT TO THE FREQUENCY TRACKER AS A PHASE CORRECTION INTO THE FEEDBACK DDS OF                                                  |                    |

| FIGURE 4-2, IN THE SAME MANNER AS THE ROUND-TRIP MEASURED PHASE CORRECTIONS FROM THE ANTENNA.                                                                | 38                 |

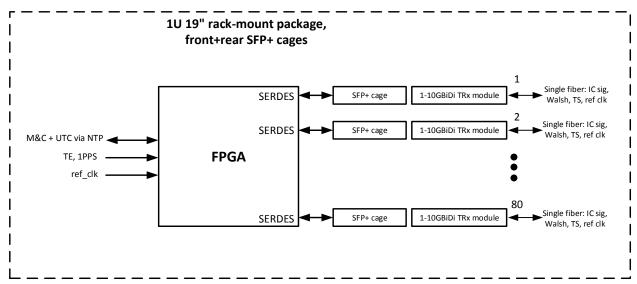

| FIGURE 6-2 SIMPLIFIED LAYOUT DIAGRAM OF A DIGITAL CENTRAL TIMING DISTRIBUTOR (DCTD) FOR ALMA. ALL ROUND-TRIP-                                                |                    |

| MEASURED PHASE CALCULATIONS FOR 80 ANTENNAS CAN BE DONE IN ONE FPGA, WITH CONNECTIONS TO 80 SFP/SFP+ MC                                                      |                    |

| FOR BIDI SINGLE-FIBER CONNECTION TO EACH FREQUENCY TRACKER END-POINT FPGA. 1-10GBPS RATES ARE SHOWN, BUT A                                                   | 4                  |

| LOWER RATE SUCH AS OC-12 622 MBPS (PERHAPS 625 MBPS SINCE IT IS PROBABLY MORE CONVENIENT) OR SOME OTHER                                                      |                    |

| FREQUENCY, COULD BE USED.                                                                                                                                    |                    |

| FIGURE 7-1 FUNCTIONAL BLOCK DIAGRAM OF ICTIMING AND/OR DTS LINK LOSS RECOVERY DIGITAL CIRCUIT.                                                               |                    |

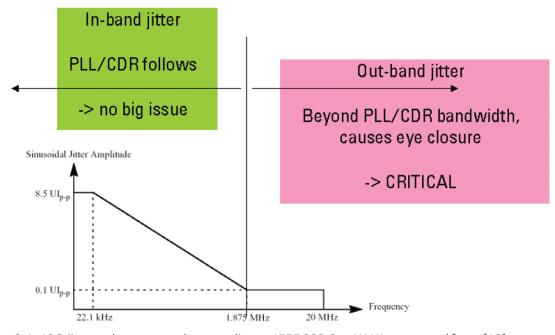

| FIGURE 8-1 10G JITTER TOLERANCE MASK, ACCORDING TO IEEE 802.3AE XAUI, EXTRACTED FROM [19]                                                                    |                    |

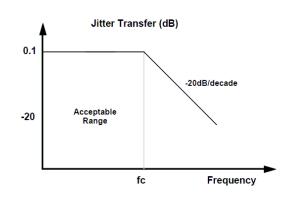

| FIGURE 8-2 JITTER TOLERANCE MASK AND JITTER TRANSFER FUNCTION FOR THE MICREL SY87701, EXTRACTED FROM THE MICREL                                              | DATA               |

| SHEET. THIS CHIP MAY BE USED IF OC-12 (~622 MBPS) IS USED FOR ICSIGNALING INDEPENDENT OF THE DTS. THE JITTER                                                 |                    |

| Transfer plot indicates that all jitter up to $fc^{2}=225$ kHz is passed (with some amplification) to the output,                                            |                    |

| SUGGESTING THAT THIS CHIP WOULD BE A GOOD CANDIDATE FOR A 3R OEO REPEATER FOR LONGER REACH, IF NEEDED                                                        |                    |

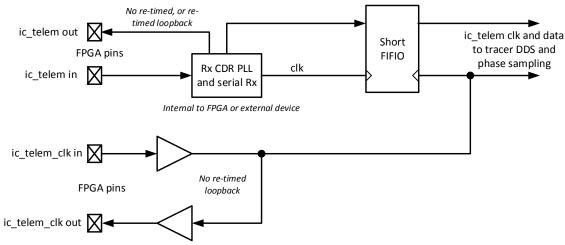

| FIGURE 8-3 CIRCUIT IN FRONT OF PHASE SAMPLING IN THE FREQUENCY TRACKER THAT ELIMINATES ANY FPGA PLLS OR FREQUENCY                                            |                    |

| SYNTHESIZERS IN THE PATH TO THE CLOCK DOMAIN CROSSING POINT OF FIGURE 4-14. A CIRCUIT, SIMILAR TO THIS, CAN ALSO                                             |                    |

| USED FOR THE REF_PH_SAMPLING_CLK AND DECIMATED REF_LOOP_CLK, BOTH ULTIMATELY SOURCING FROM THE DO                                                            |                    |

| 5                                                                                                                                                            |                    |

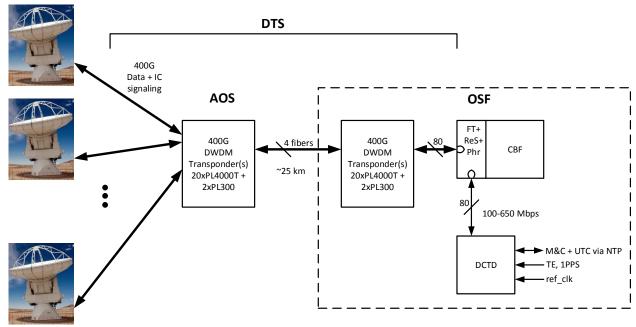

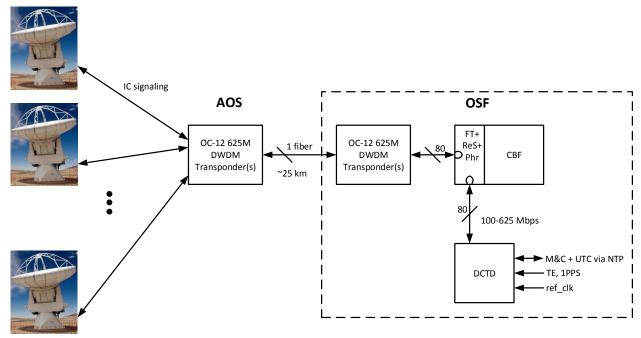

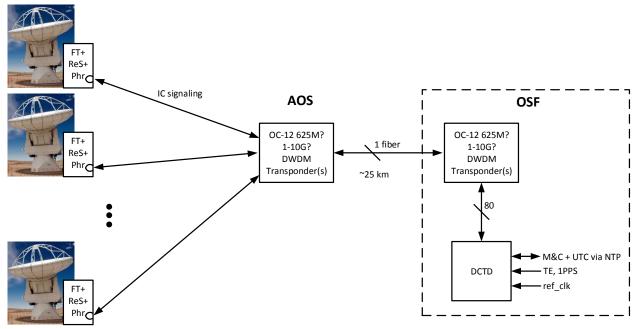

| FIGURE 9-1 ARCHITECTURE A. THE IC_TELEM PROTOCOL IS FULLY INTEGRATED WITH THE DIGITIZED SCIENCE DATA, WITH LOOPBAC                                           |                    |

| LOCATIONS INDICATED. 400G PER ANTENNA CARRIES DATA FOR 40 GS/S, DUAL-POL'N, 5 BITS/SAMPLE. DWDM TRANSPOR                                                     |                    |

| PROVIDE THE FULL-DUPLEX LINK, FOR ALL 80 ANTENNAS, BETWEEN THE AOS AND OSF USING ONLY 4 FIBERS. COTS PACKET                                                  |                    |

| TRANSPONDERS ARE SHOWN—WITH MORE PL4000T EQUIPMENT UP TO 128 ANTENNAS CAN BE SUPPORTED OVER THE SAMI                                                         |                    |

| FIBERS.                                                                                                                                                      |                    |

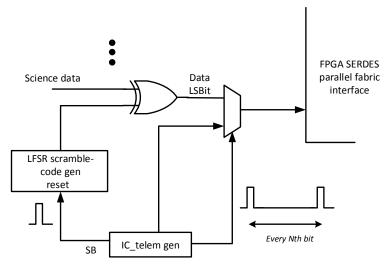

| FIGURE 9-2 INTEGRATION OF THE IC_TELEM PROTOCOL OF FIGURE 4-20 IN A DATA-REPLACEMENT FASHION WITH SELECT LSBITS O                                            |                    |

|                                                                                                                                                              | _                  |

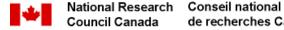

| FIGURE 9-3 ARCHITECTURE B. THE IC TIMING LINK IS DE-COUPLED FROM THE SCIENCE DATA; LIKE ARCHITECTURE A, THE FREQUENC                                         |                    |

| TRACKER AND RESAMPLER ARE LOCATED AT THE OSF IN FRONT OF THE CBF. DATA FLOWS TO THE CBF VIA THE DTS, NOT SI                                                  |                    |

| HERE.                                                                                                                                                        |                    |

| FIGURE 9-4 MORE DETAILED END-TO-END BLOCK DIAGRAM OF ARCHITECTURE B.                                                                                         |                    |

| FIGURE 9-5 ARCHITECTURE C. IN THIS ARCHITECTURE, ALL FREQUENCY TRACKING AND RESAMPLING OPERATIONS ARE PUSHED OUT                                             |                    |

| THE ANTENNA, WITH THE DCTD PROVIDING EACH INSTANCE WITH ITS REFERENCE CLOCK, WITH LINK INSTABILITIES CORRECTED                                               |                    |

| THE ANTENNA VIA A ROUND-TRIP MEASURED PHASE CORRECTION                                                                                                       |                    |

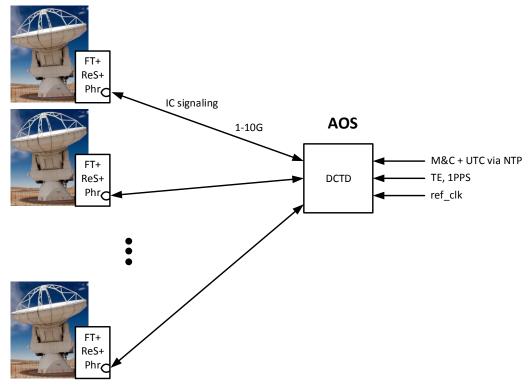

| FIGURE 9-6 ARCHITECTURE D. ALLIC EQUIPMENT IS LOCATED AT THE AOS AND ANTENNAS.                                                                               |                    |

| FIGURE 9-7 ARCHITECTURE E. ALL IC EQUIPMENT IS LOCATED AT THE AOS AND THE ANTENNAS, HOWEVER WITH LESS COMPLEXITY  POWER AT THE ANTENNAS THAN ARCHITECTURE D. | ' AND<br><b>52</b> |

|                                                                                                                                                              | ~ /                |

## List of Abbreviations and Acronyms

1PPS – 1 Pulse Per Second.

3R – Re-timing, Re-shaping, Re-amplifying.

ADEV - Allan Deviation.

ADC – Analog-to-Digital Converter.

aLO – Antenna LO, free-running, independent of others.

AOS - Array Operations Site.

ASIC – Application Specific Integrated Circuit.

BiDi – Bi-Directional data transport on a single fiber, using two different wavelengths.

CDR - Clock Data Recovery.

cLO – Central LO, the reference clock source for the array.

COTS - Commercial Off-The-Shelf.

CRC – Cyclic Redundancy Check.

CTE – Coefficient of Thermal Expansion.

CTR - Central Timing Reference.

DAC - Digital-to-Analog Converter.

DCTD – Digital Central Timing Distributor.

DDS - Direct Digital Synthesizer. A "point-slope" linear synthesizer, where the "point" is phase and "slope" is "pinc" (phase increment.)

DTS – Data Transmission System.

DWDM - Dense Wavelength Division Multiplexing.

ENOB - Effective Number of Bits.

FIFO - First-In First-Out.

FIR - Finite Impulse Response (filter.)

FPGA – Field Programmable Gate Array.

HDL – Hardware Description Language.

IC – Incoherent Clocking.

LO - Local Oscillator.

LOS – Loss Of Signal.

LPFF – Low-Pass FIR Filter. Refers to the filter after the Frequency Tracker.

LSB – Least Significant Bit.

MT – Message Type (of the IC\_telem protocol.)

OCXO – Oven-Controlled Crystal Oscillator.

OEO – Optical-Electrical-Optical.

OSF – Observation Support Facility.

PID – Proportional, Integral, Differential.

PLL – Phase Locked Loop.

ReS – Short form for "ReSampler."

ReSampler – Refers to the entire ReS FIFO, interpolator, phase rotator processing block, including Resampling and Phase DDSs.

RFI – Radio Frequency Interference.

RFSoC – RF System on a Chip.

RT – Round Trip.

RTL – Register Transfer Level. A subset of a HDL, which can be compiled ("synthesized") into FPGA hardware.

rtm - Round-trip multiplier.

SB – Sync Bit (of the IC\_telem protocol.)

SERDES - Serializer/De-serializer. Include a CDR PLL.

SEU – Single Event Upset.

SFP - Small Form factor Pluggable.

SOF – Start of Frame (of the IC telem protocol.)

SSR - Super Sample Rate.

TE – Timing Epoch; for ALMA this marks every 48 msec epoch, coincident with a 1PPS every 6.0 seconds.

TIC – Time Interval Counter.

TL - Timing Link.

Tracer (tracer) – complex tone derived from DDS driven by an appropriate clock. Typically this is ~10 MHz and 16-24-bits in precision.

VLBI – Very Long Baseline Interferometry.

### Introduction

Extending ALMA baselines is a key topic of interest to the NA ALMA Development Program, Cycle 9 Call for Proposals. This interest has prompted the author to write this memo to explore and explain, in considerable detail, the research into "incoherent clocking" (IC) that has been underway at NRC-Penticton over the last nearly 2.5 years. This memo is therefore a key applicable document for a Proposal submission, in response to the Cycle 9 call, to perform an experiment to empirically verify that this method can be used for ALMA, even for Band 10 over 100+ km of aerial fiber.

In this memo, in addition to explaining the research, a number of architectures that may be used for ALMA are developed and described. These are developed within the author's understanding of ALMA infrastructure and informed by descriptions of such contained in [1], including maximum baselines possible due to geographical and geopolitical considerations. The "200+ km baselines", requiring fiber lengths of 100+ km ignores these issues, instead indicating what the technology is capable of doing.

The first notion of IC is described in [2]. Since then, much progress has been made in refining the approach, leading to an all-digital implementation. Of course, "all-digital" does not eliminate the need for an appropriately low phase noise LO reference at the antenna, multiplied up by, and used in, the RF continuous-time domain until the signal is finally digitized in the ADC. "All-digital" therefore refers to all processing performed after this point, including sufficiently accurately measuring the antenna LO ("aLO") frequency vs time relative to a common reference LO ("cLO"), e.g. the H-maser, over digital fiber optics connections and, using these measurements, digitally correcting the digitized science data into the common reference domain before correlation and beamforming.

The ability to do these measurements and apply corrections using all-digital methods and processing seems like a fantastic claim and at this point the reader might be tempted to stop reading. However, in this memo the approach, research results, applicability to ALMA, and risk analysis is done to hopefully convince the reader that the probability that the IC method will not work for ALMA is very low and may even be zero.

#### Overview

The IC approach is a digital method for providing a clock and timing solution for any scale and frequency of radio telescope. It uses a "measure and correct" approach wherein each antenna operates using its own independent LO (aLO), its frequency vs time is measured at a central site relative to a common reference cLO, and then the digitized data is digitally "corrected" (interpolated and phase rotated) before correlation and beamforming.

Since the aLO is measured in a common reference clock domain at a central site, naturally aLO's frequency—or more likely a frequency derived from, and locked to, it—must be transmitted there via a media such as fiber, whose delay is changing with time. Thus, a round-trip measurement is performed to remove this temporal delay uncertainty from the frequency measurement and, additionally, digital filtering is used is remove temporal round-trip measurements on timescales less than some factor times the round-trip delay. Since clock steering is not occurring, what this means is that a longer fiber requires a more stable aLO, however as will be shown, it is always the case that any aLO frequency measurement variations on timescales that are a priori known to not be intrinsically in the aLO can be digitally filtered out. This affords considerable performance improvements over clock steering approaches, allowing

virtually any baseline extent to be accommodated, with the limitation only being the stability of the aLO for the required (highest) observing frequency and fiber reach.

Additionally, digital methods are used for all measurements and to convey a frequency derived from the aLO to the central site. Thus, all measurements and corrections occur in digital devices such as FPGAs, and all signals flowing between the antenna and the central site use COTS digital fiber optic transceiver modules and lowest-cost aerial fiber routing methods. There is, of course, a continuous-time aspect to this approach since it would be impossible to measure aLO's varying frequency using strictly discrete-time processing. Thus, there is something of a "cross-over" between continuous-time and discrete-time in the IC approach, but all-digital methods are nevertheless used.

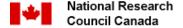

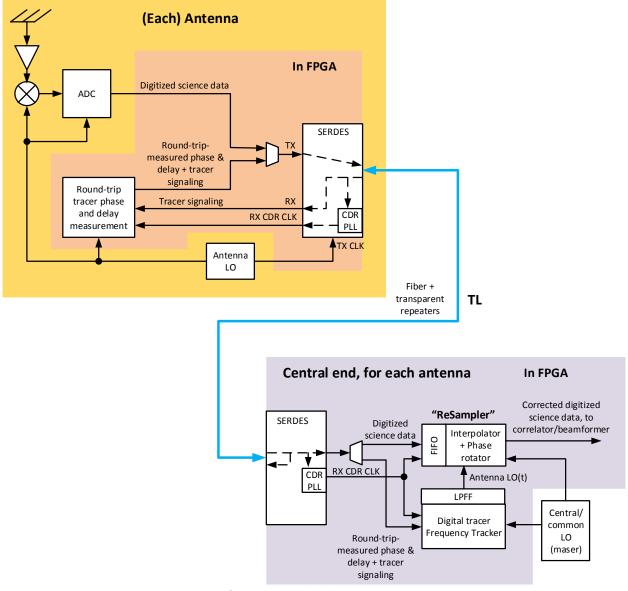

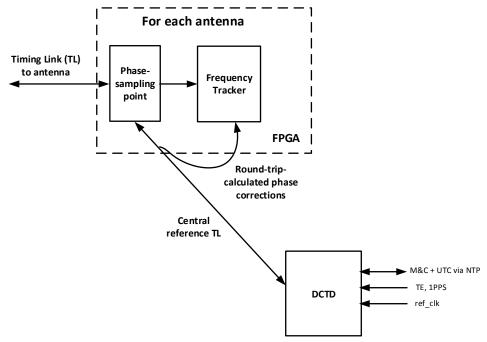

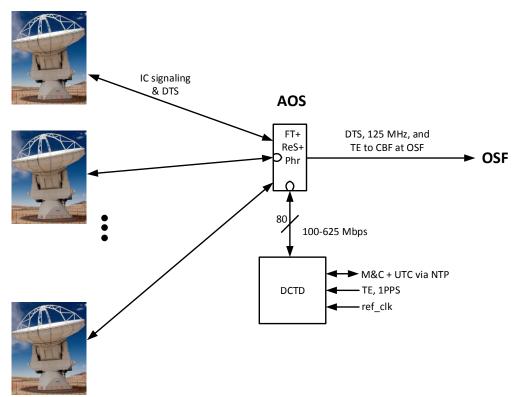

A greatly simplified block diagram of the IC method is shown in Figure 2-1 for a Direct Digital Conversion (DDC) receiver; for a heterodyne receiver such as ALMA one or more down-conversion stages in front of the ADC/digitizer is of course needed.

In this diagram, timing information is conveyed over a full-duplex digital fiber optic "Timing Link" (TL) here containing the digitized data as well, by clocking the serial transmitter with a derivative of the aLO, recovering the clock at the central end with a Clock-Data Recovery (CDR) PLL¹, and then measuring that recovered clock's frequency in the central common (reference) clock domain cLO. This is a typical case, but a link separate from the digitized science data could be used for the TL and indeed, the TL could be wireless (as of course could be the link for the digitized data.)

Figure 2-1 Simplified block diagram of the IC approach.

A more detailed functional block diagram of a typical IC implementation is shown in Figure 2-2 (included here; a more detailed signal flow description can be found in [3].)

In this diagram:

• All down-conversion and digitization clocks are derived from the<sup>2</sup> aLO. Not shown are all of the required derived frequencies for these purposes, just that ultimately all are derived from the

<sup>&</sup>lt;sup>2</sup> If required, there could be more than one independent a LO used, requiring a TL to the central site for each one.

Canada

<sup>&</sup>lt;sup>1</sup> The combination of serial transmit/receive with a receive CDR PLL, in digital terminology is known as "SERDES" (SERializer/DESerializer.)

- same aLO, and that any differential phase noise present in these derivations are inconsequential<sup>3</sup>.

- The digitized science data as well as "Round-trip measured phase & delay + tracer signaling" are integrated onto the same fiber and transmitted to the central end using SERDES and (COTS) digital fiber optic transceivers. Any signal repeating between the antenna and the central end must be "transparent", meaning that timing information is conveyed through them. These repeaters may be "3R" (Re-timing, Re-shaping, Re-amplifying) OEO type or OO type; jitter cleaning may occur, but it must not clean jitter (phase/frequency wander) that is intrinsic in the aLO on timescales that must be measured.

- At the central end, the received signal is looped back and transmitted back to the antenna end. The return fiber/repeater dynamic behaviour, on time scales ≥ the phase/frequency wander of the aLO that must be measured and corrected, must be sufficiently well matched to the incoming direction such that the single-direction phase is simply the round-trip phase measurement divided by 24.

- The "tracer" is a high dynamic range complex digital tone, derived from the receive SERDES CDR PLL clock at the central end and antenna (loopback) end as required. Its phase and frequency therefore changes in precise proportion to CDR PLL clock phase and frequency changes. For example, for a 10G (Gbps) SERDES & digital fiber optic link, the CDR PLL clock present in the FPGA fabric is typically 250 MHz; this 250 MHz clock drives a 16-bit free-running Direct Digital Synthesizer (DDS), with a "pinc" value, typically a prime (relative, to the number of phase steps) number, chosen so that subsequent sampling of the DDS's digital phase across digital clock domains<sup>5</sup> doesn't beat with any clock frequency and that the tracer frequency is sufficient for phase and frequency measurement performance, typically ~10 MHz. Also, since tracer phase is converted to a complex tone after phase sampling into the required clock domain, it has perfect quadraturity<sup>6</sup>, essential for accurate and precise phase and frequency measurements. Finally, the tracer tone is not in itself transmitted across the TL fiber, rather signaling to maintain synchronization of tracer DDSs at various places, is transmitted instead. This greatly decreases the digital bandwidth needed for it.

- At the antenna end, the phase of the returned tracer is continuously measured against the phase of the outgoing tracer and this information is transmitted to the central site on the same fiber optic link as the science data and tracer signaling. Typically, a new 32-bit phase measurement is made and transmitted every ~10 μsec and no attempt is made to digitally filter these measurements since such filtering is provided by the post-Frequency Tracker Low-Pass FIR Filter (LPFF.) Additionally, the round-trip delay is unambiguously measured using a time-interval counter (TIC, clocked by an aLO-derived frequency) between a pulse at the transmitter, and its return, with the measured value also transmitted to the central site on the same link. This

<sup>&</sup>lt;sup>5</sup> Using gray-code and memory methods to ensure no code errors. Discrete-time digital phase sampling also generates phase noise, most of which is filtered out with the post-Frequency Tracker Low Pass FIR Filter (LPFF.) 6 Meaning that the in-phase (cos) and quadrature (sin) components are 90 degout of phase, albeit with noise proportional to the numerical precision used, but with no net bias.

<sup>&</sup>lt;sup>3</sup> Meaning that it doesn't need to be measured and corrected. If it does, then the derived frequency that drives the digital SERDES transmitter must be derived from an appropriate point to capture that information.

<sup>&</sup>lt;sup>4</sup> There is some possibility, TBC, that some mismatch may be calibrated -out by a nalysing the central-end Frequency Tracker PID servo Phase err variable (Figure 4-2) and adjusting the division factor of 2 appropriately to minimize its

round-trip delay provides a sufficiently accurate measurement of the round-trip (and therefore single-direction) delay of the fiber, needed for time-epoch marking of antenna digitized science data (1PPS and/or 48 msec TE) and to facilitate accurate Walsh phase change setting at the antenna (see subsequent discussions of these and associated issues for further details.)

Figure 2-2 Typical IC implementation functional block diagram.

• At the central site, the round-trip-measured phase is applied as a compensating factor in the (digital) Frequency Tracker, which is continuously measuring the tracer frequency at that point, largely removing fiber delay variations from these measurements. As will be shown, only the round-trip measured phase on time scales ≥ aLO phase/frequency changes that must be measured, actually have an effect on the net after-LPFF result.

- Raw Frequency Tracker measurements, typically one every ~10 μsec, are filtered using the LPFF. This filter, whose DC gain<sup>7</sup> must be precisely known, removes any measured frequency measurement variations on timescales ≥ aLO phase/frequency variations that must be corrected. Also, as mentioned, the filter also removes the vast majority of phase noise due to digital phase sampling, fiber delay perturbation effects known not to be in the aLO, and FPGA clock jitter, which is typically 100 to 350 ps pk-pk.

- The LPFF output frequency measurements drive DDSs, which drive the ReSampler (see Figure 4-17.) All digital mathematical operations are sufficiently accurate and unbiased since there is no feedback to determine if the applied corrections are "correct." Such accuracy and unbiased operation can be obtained with, for example, the use of well-known unbiased digital rounding operations.

- The digitized science data output from the ReSampler is now fully-corrected to the reference clock domain, as are similar outputs from other antennas, ready for correlation and beamforming.

# Antenna clock stability and LPFF requirements

As mentioned, in the IC approach, a longer fiber requires a more stable aLO. This is specified in terms of its Allan Deviation (ADEV) using the well-known ADEV equation relating the frequency under consideration, its frequency change, and phase change over a time duration Tau. This is discussed in [3] and presented in the following equations:

$$AD_{c} \leq \frac{\varphi_{RMS} v_{link}}{2L \cdot rtm \cdot fm \cdot v} \tag{1}$$

and:

$$Tau_c \cong \frac{2L}{v_{link}} \cdot rtm \cdot fm$$

(2)

Where:

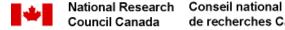

AD\_c is the aLO Allan Deviation at Tau critical, "Tau\_c", according to Figure 3-1.

$\phi_{RMS}$  is the allowed RMS phase noise.

$v_{link}$  is the velocity of signal propagation through the fiber; for single mode it is ~2/3 c.

L is the fiber length.

v is the frequency being considered.

At frequencies other than DC there will, of course, be some gain variation in any LPFF filter. However these gain variations affect only tracer frequency variations, which are very small. A full analysis of required LPFF bandpass ripple requirements for a given a LO ADEV, digitizer frequency, and sky frequency is TBD, noting that the number of LPFF taps can be increased to achieve very low bandpass ripple, typically <0.001 dB, and that no noticeable effects of this kind of bandpass ripple have been found in any testing to date. For example, 0.001 dB gain error at f\_tracer\_er of 1e-4 Hz, results in an error of 2e-8 Hz. Even for Tau=10 sec, this is phase error of 1e-7 cycles.

rtm is the round-trip multiplier—fiber delay changes on timescales short than this factor times the round-trip delay are not reliable and need to be filtered out.

fm is the "filter multiplier" and accounts for the delay of the LPFF; for the case where the FIFO in front of the ReSampler ~matches the delay of the LPFF, fm=1; when not, it is typically ~15.

Total antenna phase noise including the aLO, its frequency synthesizers, mixers & digitizers, the analogue signal, as well as measurement of the aLO by the central-site Frequency Tracker8 must be taken into account. From Table 1 [4], the total phase noise for the current electronics is 65 fsec ~= 23 deg at 1 THz. In that document, however, an allocation for the antenna LO, as delivered by the roundtrip phase-corrected method employed at the Warm Cartridge Assembly (WCA) ingress point [21], could not be found. Therefore a reasonable allocation of ~20 fsec RMS (~8 deg RMS at 1 THz) is chosen here as a minimum phase noise performance requirement for the aLO (Tau < Tau c) and the Frequency <u>Tracker (Tau > Tau c)</u>, since 20 fsec increases the total electronics phase noise to  $\sim$ 68 fsec, a negligible increase.

#### Example:

For ALMA mixers/downconverters at v=1 THz, L=100 km,  $\varphi_{RMS}$ =8 deg, and for rtm=10 [5] leads to an aLO AD\_c~=2e-12 @ Tau\_c~=10 msec.

For ALMA 2030 digitizers @40 Gs/s, 5 ENOBs, the allowable phase noise of the aLO (consistent with, for example, AD9213 data sheet, Figure 90) is  $\sim 2^{-(ENOBs+2.5)} \sim = 5e-3$  cycles RMS at 40 GHz and therefore AD  $c^{-1.4e-11}$ , also at Tau  $c^{-10}$  msec.

Thus, the aLO ADEV requirement for the 1 THz downconverter is the governing value. Of course, the antennas that are much closer to the central site, i.e. L<<100 km, would have a less-stringent requirement, many by at least an order of magnitude, but such depends on digital Frequency Tracker performance as we shall see in section 4.1.

If the ReSampler FIFO depth does not match the LPFF delay, for the ALMA example above at 1 THz with fm=15, the aLO AD c~=1e-13 @Tau c~=0.15 sec, requiring a device that may be difficult and costly to obtain.

<sup>8</sup> It is important to point out that a LO and Frequency Tracker phase noise contributions are mutually-exclusive—for timescales Tau < Tau c the Frequency Tracker is essentially turned off if fm=1 (with fc LPFF according to equation (3)); for times cales Tau > Tau c, aLO phase noise is completely compensated to the precision of the Frequency Tracker.

Figure 3-1 Log/log IC Allan Deviation curve. The ADEV of aLO must be below this curve. On timescales < Tau c, aLO phase/frequency noise/wander is not measured or corrected; on timescales > Tau c, aLO phase/frequency wander is measured and corrected (re-sampled, phase rotated.) Not shown is that for Tau >> Tau\_c, of course, the curve bends over to the limit of aLO absolute frequency tolerance.

To minimize aLO stability requirements, fm=1 and therefore the ReSampler FIFO requires memory to buffer the digitized science data to match the LPFF delay,  $\tau_{LPFF}$ , which can be significant. In order to remove all aLO frequency variations that are not intrinsically in the aLO, we take the cut-off frequency of the LPFF, f<sub>c LPFF</sub>, as:

$$f_{c\_LPFF} \cong \frac{1}{4Tau\_c} \tag{3}$$

The delay through the LPFF, for ~80 dB reject band attenuation and very low passband ripple, has been found to be:

$$\tau_{LPFF} \cong \frac{3}{f_{c\_LPFF}} \tag{4},$$

with a ~100 dB reject band filter, ~15% longer.

For the example above, at Tau\_c~=10 msec,  $f_{c LPFF}$ ~=1/0.04sec=25 Hz and  $\tau_{LPFF}$ ~=3/ $f_{c LPFF}$ ~=0.12 sec. For a 40 Gs/s stream at 5b/sample, a total of 3 GBytes per stream is therefore required for the ReSampler FIFO.

# Technical descriptions

### 4.1 Central-site Frequency Tracker design and performance

The previous section provides the theory to establish aLO stability, f<sub>c LPFF</sub>, and ReSampler FIFO memory requirements. However, a key part of feasibility analysis for any ICapplication is the design and

performance of the central-site Frequency Tracker since its performance is a limiting factor. Thus, this topic is addressed in considerable detail in this section.

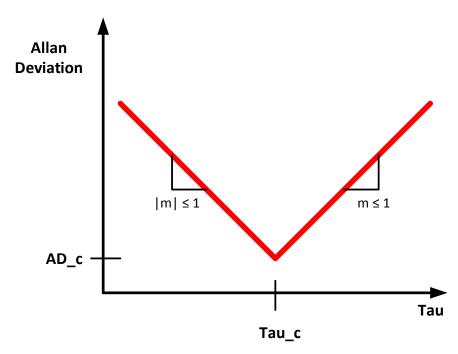

Although it is sufficient for the aLO's ADEV to be below the curve of Figure 3-1, doing so, for the extreme ALMA application of v=1 THz, may require digital logic resources and performance (i.e. tracer DDS clock rate, phase sampling rate, and Frequency Tracker clock rate) to meet the demand of tracking the highest df/dt of the tracer present. If the aLO's ADEV follows the curve of Figure 3-1 for Tau > Tau\_c, df/dt is the same for all Tau > Tau\_c. However, if the aLO curve is more along the lines of Figure 4-1, then df/dt is relaxed, requiring fewer digital logic resources and less digital logic performance, since it is at Tau c where tracking frequency variations needs to start, not where it must be fully doing so. This kind of curve is normally the Allan Deviation of a crystal oscillator anyway, rather than the curve of Figure 3-1.

Actual logic resources and performance may be determined empirically, and the cost (and power) thereof balanced with the cost of the aLO. As will be seen, there is some room for Frequency Tracker performance improvement resulting in lower phase noise and higher df/dt tracking, although pushing the limit does come with increased cost and power, something one should always strive to minimize.

Figure 4-1 Antenna LO log/log ADEV curve requiring less logic performance in the Frequency Tracker. Frequency Tracking starts to occur at Tau\_c, but isn't at full performance until Tau\_c1, which is typically 5x to 10x Tau c.

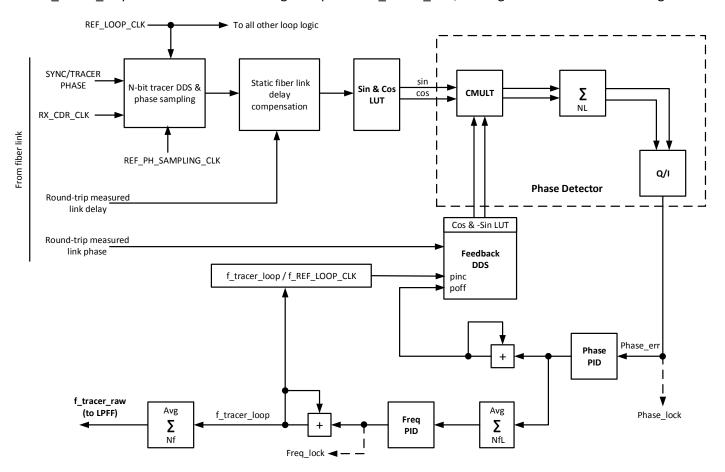

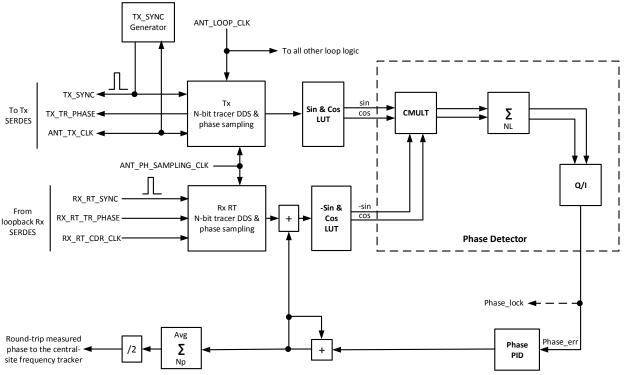

A block diagram of the Frequency Tracker (i.e. one possible design of the Frequency Tracker) is shown in Figure 4-2. Its operation is fundamentally very simple in concept, although not shown in the diagram is the number of bits carried and used for each operation, which vary from 16b to 64b.

The phase detector is the short-term-accumulated complex-conjugate cross-correlation of a high dynamic range tone from the tracer DDS, driven by the received data Rx CDR PLL-recovered clock, with the feedback tracer DDS' high dynamic range tone, driven in the reference clock domain.

The output of the phase detector drives a phase PID calculator, whose output is an accumulated phase correction to the feedback DDS phase input on each iteration of the loop.

The phase correction above drives a frequency PID calculator, whose output f\_tracer\_loop is an accumulated frequency correction to the feedback DDS pinc (phase increment) register. Nf f tracer loop measurements are averaged to produce f tracer raw, which goes to the LPFF for filtering.

Figure 4-2 Frequency Tracker block diagram. Phase lock and Freq lock are asserted when the variation in loop signals at the indicated points are sufficiently low.

The phase PID and frequency PIDs are assigned their own P, I, and D gains and (normally) the former's gains are much higher than the latter's. This means that the phase PID (inner loop) is always phaselocked and tracking the Rx CDR PLL clock-driven tracer DDS, and the frequency PID (outer loop) tracks its frequency changes9. For the kind of phase jitter/wander that the tracer Rx CDR PLL-driven DDS sees, for reasonable phase PID gains, phase-lock is always achieved and assured. It is the frequency PID gain coefficients that determine df/dt tracking and resulting tracer frequency output vs time that is required to meet a given aLO Allan Deviation at the required phase noise for the required maximum frequency.

<sup>&</sup>lt;sup>9</sup> It is possible to only have a phase PIDIoop, with the phase change on each iteration of the loop driving the ReSampler DDS. This option has not been explored in detail and may work just fine if the antenna LO's absolute frequency error is well-constrained.

For Frequency Tracker logic and performance presented in [3] (referring to Figure 4-2: N=16-bit tracer DDS operating at RX\_CDR\_CLK=250 MHz; phase sampling at REF\_PH\_SAMPLING\_CLK=303.75 MHz; PID loop logic operating at REF\_LOOP\_CLK=101.25 MHz—phase-locked to 303.75 MHz; NL=51, NfL=4, Nf=4, phase PID gains<sup>10</sup>= $2^{-11}$ ,  $2^{-23}$ ,  $2^{-17}$ ; freq PID gains= $2^{8}$ ,  $2^{-7}$ ,  $2^{7}$ ;  $f_{c\_LPFF}^{\sim}$ =25 Hz (-15 dB))<sup>11</sup> the best phase noise performance found for a ~3e-5 Hz pk sinusoidal tracer frequency variation (ADEV<sub>aLO</sub> of 2e-12 x 10 MHz x  $\sqrt{2}$ ) at 2.5 Hz (i.e. Tau\_c1=0.1 sec which is  $10^*$ Tau\_c) is ~4.8e-7 cycles RMS at a tracer frequency of ~10 MHz, which translates to ~17 deg RMS at 1 THz, higher than the allocated limit of ~8 deg RMS previously established.

This result was found with a discrete-time MathCad model of the Frequency Tracker that has been found to be consistent with FPGA RTL<sup>12</sup> simulation results ([6], with MathCad-RTL comparison reported at [7].) The MathCad model is used for performance evaluation since it runs ~200-300X faster than an FPGA RTL simulation.

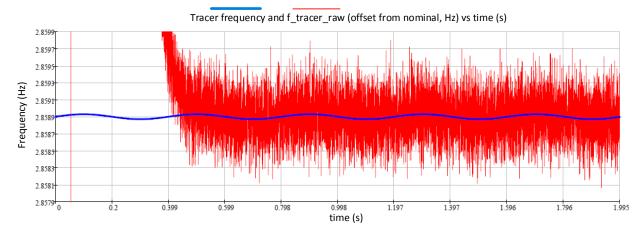

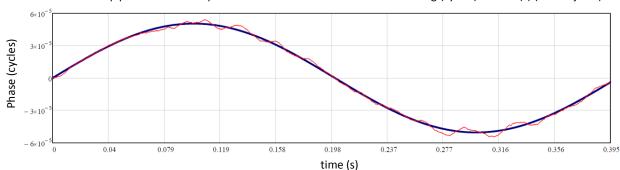

Plots from this simulation are shown in Figure 4-3 to Figure 4-7 below:

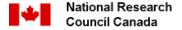

Figure 4-3 Raw Frequency Tracker result before LPFF. In this simulation no fiber link jitter is introduced since the effect of such is well understood [6][8][3]. Here, the tracer frequency is  $\sim$ 10 MHz; it has a constant frequency offset (from nominal) of  $\sim$ 2.86 Hz and a sinusoidal frequency variation of  $\sim$ 3e-5 Hz pk at 2.5 Hz.

<sup>&</sup>lt;sup>12</sup> RTL="Register Transfer Level." This is FPGA HDL (Hardware Description Language) code that is "synthesizable" and maps to a ctual FPGA hardware. A "simulation" of the RTL code precisely indicates how the FPGA will perform as long as timing closure is achieved (i.e. when a chieved, it is guaranteed to run at the required speed(s).)

<sup>&</sup>lt;sup>10</sup> Powers of 2 are used since application of gain entails simple bit shifts. This simplification has limitations in gain selection, although such was not found to be a problem.

$<sup>^{11}</sup>$  As well, using the specified Intel Stratix-10 FPGAI/O PLL clock jitter of 175 psec pk-pk max, assuming a Gaussian distribution and 2.5 $\sigma$  (a reasonable assumption, consistent with the confidentially-obtained "Intel Stratix 10 I/O PLL Validation Report, May 2018"), noting that in the simulations FPGA clock jitter has a much smaller effect on phase noise than discrete-time phase sampling.

Figure 4-4 Frequency Tracker result after stage 1 of the LPFF with  $f_{c\_LPFF\_s1}$ ~=3 kHz. Here, the constant offset of ~2.86 Hz in Figure 4-3 has been removed from the result to more clearly see the imposed sinusoidal frequency variation due to antenna clock instability. In this case the RMS phase error is ~5e-7 cycles of phase at  $f_{tracer} = 10 \,\text{MHz}$ .

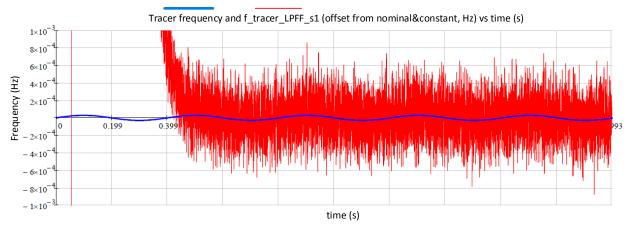

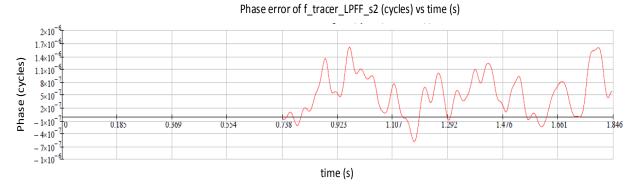

Figure 4-5 Frequency Tracker result after stage 2 of the LPFF with  $f_{c \ LPFF \ s2}$ ~=25 Hz.

Figure 4-6 Frequency Tracker frequency error after stage 2 of the LPFF with  $f_c$  LPFF s2 $^\sim$ =25 Hz.

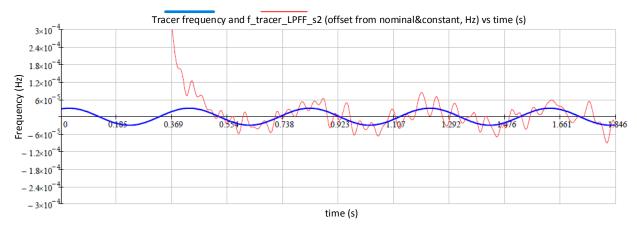

Figure 4-7 Frequency Tracker phase error after stage 2 of the LPFF with  $f_{c LPFF}$ ~=25 Hz. The RMS phase error is  $\sim$ 4.8e-7 cycles at  $f_{tracer} \sim$ =10 MHz, which translates to 17 deg RMS at 1 THz.

From the above results it would seem that there is no utility for stage 2 of the LPFF since the RMS phase error out of each one is approximately the same. However, stage 2 is absolutely essential to remove uncompensated fiber link jitter, not included in this simulation but reported in [6], [8], and [3].

Running the simulation with ADEV~2e-12, the tracer DDS operating at 500 MHz, sampled at 603.75 MHz, processed at 301.875 MHz, a tracer frequency of ~41 MHz, and a proportionally higher tracer frequency variation of ~1.2e-4 Hz pk at 2.5 Hz (with NL=51, NfL=16<sup>13</sup>, Nf=4, phase PID gains=2<sup>-11</sup>, 2<sup>-23</sup>, 2<sup>-17</sup>; freq PID gains= $2^{10}$ ,  $2^{-5}$ ,  $2^{9}$ ;  $f_{c\ LPFF}$ ~= $25\ Hz$ ) yields an RMS phase error (of the 41 MHz tracer) of ~1.6e-6 cycles, which translates to ~14 deg RMS at 1 THz.

This highlights the case (mentioned previously) where aLO stability requirements are driven by the performance of the Frequency Tracker (of course, coupled with maximum observing or digitization frequency), rather than fiber length L. By reducing the aLO's ADEV, Frequency Tracker PID gains can be reduced, resulting in lower phase noise in the measured result.

For example, re-running the previous 10 MHz tracer simulation with an aLO ADEV~=5e-13, resulting in a 2.5 Hz sinusoidal frequency variation of ~7e-6 Hz pk, with phase PID gains=2<sup>-11</sup>, 2<sup>-23</sup>, 2<sup>-17</sup> and freq PID gains=2<sup>7</sup>, 2<sup>-8</sup>, 2<sup>6</sup> yields an RMS phase error of ~2.9e-7 cycles or ~10 deg RMS at 1 THz. Re-running the above 41 MHz tracer simulation with a 2.5 Hz sinusoidal frequency variation of ~3e-5 Hz pk, with freq PID gains=29, 2-6, 28 yields an RMS phase error of ~9.6e-7 cycles or ~8.4 deg RMS at 1 THz

If the aLO must be more stable for a longer Tau as above because of Frequency Tracker phase noise, it also means that the fiber length L can increase beyond the 100 km example used thus far, according to equation (1). For the above curve of ADEV≤5e-13 @ Tau c=10 msec and ADEV≤5e-13 @ Tau c1=0.1 sec, full frequency tracking occurs at Tau~=0.1 sec; evaluation of equation (1) for an ADEV of 5e-13 and  $\phi_{RMS}^{\sim}=8 \text{ deg yields L}^{\sim}=440 \text{ km}.$

If extra fiber length L is not required, then the rtm factor of equations (1) and (2) can be increased by the same factor, in this case ~4x to rtm~=40, by decreasing f<sub>c LPFF</sub> (equation (3)) by the same factor, adding more assurance that fiber delay perturbations are completely removed via round-trip measured compensation and filtering with the LPFF. Here it means that f<sub>c LPFF</sub>~=6 Hz. However, τ<sub>LPFF</sub> then increases by that same factor to ~0.5 sec (equation (4)), which could introduce a latency problem for the ALMA

<sup>&</sup>lt;sup>13</sup> Increased to 16 from the previous 4 to keep within MathCad's array size limitations.

VLBI tied-array feedback loop turn-around time of 1-2 seconds (6.5.10 of [1]), for ~200 km baselines. This leads to the notion that  $f_{c LPFF}$  and ReSampler (Figure 4-17) FIFO delay can be dynamically configured for VLBI sub-arrays, which could be restricted to an aperture size such that  $\tau_{LPFF}$  isn't an issue in this regard.

#### 4.2 Round-trip phase tracker

A block diagram of the round-trip phase tracker circuit, present in the antenna FPGA, is shown in Figure 4-8. Its operation is similar to the Frequency Tracker, except that here accumulated feedback phase is added to the round-trip ("RT") tracer DDS output to close the loop. Then, accumulated feedback phase is averaged Np times, divided by 2, and sent to the central site on the same serial channel as tracer signaling to be used by the Frequency Tracker. In the lab demo described in [3] NL=51, Np=4, and other clock frequencies are the same as the Frequency Tracker defined above. This results in phase measurements being sent to the Frequency Tracker with a cadence of ~10 μsec. Other than some averaging, phase measurements aren't filtered, instead they are effectively filtered by the LPFF after the Frequency Tracker.

Figure 4-8 Round-trip phase tracker block diagram.

ANT PH SAMPLING CLK and ANT LOOP CLK need not be derived from the aLO and can instead use an independent relatively low-quality LO since tracer phase is Nyquist zone-1 sampled. However, what is not shown in Figure 4-8 is that the ANT\_LOOP\_CLK14 is used for the round-trip delay measurement, essentially counting the time between the TX\_SYNC pulse, and the return copy RX\_RT SYNC. By counting in the aLO clock domain, this measurement can be corrected at the central site, using the measured aLO frequency, if required.

<sup>&</sup>lt;sup>14</sup> Or the higher frequency ANT\_PH\_SAMPLING\_CLK if higher time resolution is required.

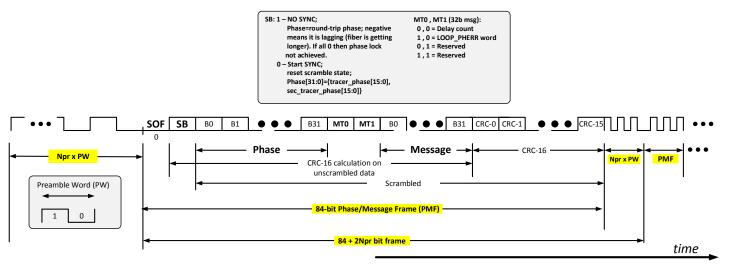

The above block diagram also shows the starting point for tracer phase generation and the method for synchronizing all tracer DDSs. The "Tx N-bit tracer DDS" has an arbitrary initial phase and is free running in the antenna clock domain (ANT\_TX\_CLK). The TX\_SYNC generator generates a pulse on a periodic basis, which captures the current tracer DDS phase TX\_TR\_PHASE. This is then transmitted to the central site using an "IC\_telem" protocol such as that shown in Figure 4-20. There, the tracer phase is loaded into the tracer DDS of the Frequency Tracker. This same IC\_telem stream is looped-back at the central-site and is loaded into the "Rx RT N-bit tracer DDS" at the antenna. In this manner, the "genesis" tracer DDS at the antenna, the tracer DDS at the central site, and the RT tracer DDS all remain synchronized to ensure continuity of phase and frequency measurements. If link loss occurs, signaling is lost but is re-established once the link comes back up. However, of course, during link loss the central Frequency Tracker and round-trip tracer DDS has no Rx CDR PLL clock and so it is no longer tracking. Notions of how to seamlessly fail-over a short term link loss are discussed later.

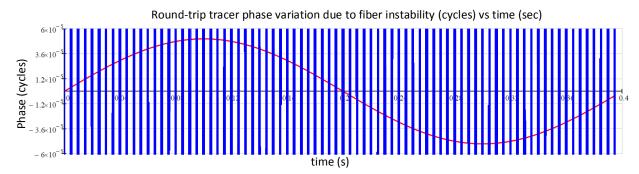

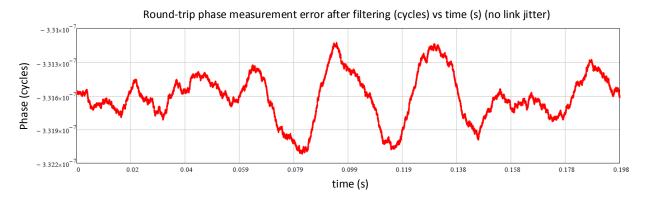

A discrete-time MathCad model of the round-trip phase measurement circuit of Figure 4-8 was run for a ~10 MHz tracer phase variation of ~7e-5 cycles (pk) at 2.5 Hz (i.e.  $f_{c\_LPFF}$  for Tau\_c~=0.1 sec as previously discussed), which needs to be tracked and that is ultimately fully compensated by injection as a cancelling term in the Frequency Tracker's Feedback DDS phase offset input. To this was added ~1 nsec pk-pk total (uncompensated) link jitter at ~100 Hz and ~2.2 kHz, which are ultimately rejected by the LPFF. A frequency-domain low-pass filter<sup>15</sup> with  $f_c$ ~=3 Hz and -80 dB reject-band is used to perform the net result of LPFF filtering (assuming no Frequency Tracker rejection, the worst-case.) Phase-loop PID coefficients are set to  $2^{-17}$ ,  $2^{-29}$ , and  $2^{-23}$ . 7e-5 cycles of phase at 2.5 Hz corresponds to an ADEV of ~5e-11 at Tau=0.1 sec for 300 km of aerial fiber [9]. Results of running this model are shown in the following figures:

Figure 4-9 Modeled tracer phase variation due to fiber instability. The **red** trace is the variation that must be tracked, if not it will be confused with aLO variation. The **blue** trace is variation that must ultimately be rejected in the post-Frequency Tracker LPFF output; its total variation is ~100X the vertical scale shown.

<sup>&</sup>lt;sup>15</sup> i.e. FFT of the entire simulation data set, multiply by the low-pass filter function, then inverse FFT.

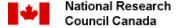

Figure 4-10 Round-trip phase tracker output phase vs time (red trace) and model of the 2.5 Hz variation that must be tracked (blue trace.) Much of the unwanted link jitter (at 100 Hz and 2.2 kHz) has been rejected by the loop, however much remains amounting to  $\sim$ 3e-4 cycles of RMS phase error, over 1000X more than allowed.

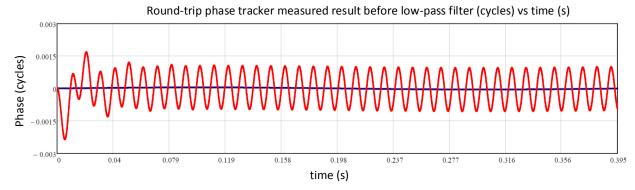

Figure 4-11 Error in round-trip measured phase after -80 dB low-pass filter (cycles) vs time. A phase offset of  $^{\sim}1e$ -5 cycles is present due to the frequency domain low-pass filter, however such is irrelevant. The RMS phase error (i.e.  $\sigma$ ) is 7e-8 cycles (@10 MHz), which corresponds to  $^{\sim}2.5$  deg at 1 THz. Clearly the slow 2.5 Hz variation is being adequately tracked even in the presence of far higher link jitter. The time scale on this plot is  $\frac{1}{2}$  of Figure 4-10 since only the latter  $\frac{1}{2}$  of the data is filtered and analyzed to eliminate confusion from loop initialization/stabilization.

If needed, more LPFF stop-band attenuation can be employed but at some increased delay through the filter, knowing that the ReS FIFO (Figure 4-17) delay can always<sup>16</sup> be increased to match the LPFF delay, (i.e. fm=1 in equations (1) and (2)) thus not affecting aLO stability requirements. For example, a -100 dB LPFF is easily possible, given the 18b+ multipliers available in modern FPGAs, and has a ~15% increase in delay and number of taps compared to a -80 dB filter<sup>17</sup>. This filter, normally multi-stage decimating, is light on FPGA resources since raw frequency measurements are input every ~10 usec.

To see phase tracking of the variation that must be measured due to a changing fiber delay and to see phase noise due only to discrete-time phase sampling and digital processing, the following plots are presented:

<sup>&</sup>lt;sup>17</sup> 0.1 bandpass, 0.001 dB passband ripple, ~2.5% transition band, using the free on-line "TFilter" FIR filter design program.

<sup>&</sup>lt;sup>16</sup> Well, of course, there is a limit, however DDR4 memory has enormous capacity of 256 GB.

Round-trip phase model and phase tracker measured result before filtering (cycles) vs time (s) (no link jitter)

Figure 4-12 Phase model and raw phase tracker measurement before low-pass filtering with no imposed link jitter. This shows tracking performance and phase noise due to digital phase sampling and processing. Without filtering the RMS (i.e.  $\sigma$ ) phase error is ~1e-6 cycles (@~10 MHz.)

Figure 4-13 Phase tracker-measured error, cycles vs time, after -80 dB low-pass filtering, no unwanted link jitter. The RMS (i.e.  $\sigma$ ) phase error is ~2e-10 cycles (@~10 MHz.) The time scale on this plot is ½ of Figure 4-12 since only the latter ½ of the data is analyzed after filtering to eliminate apparent errors from loop initialization/stabilization.

#### 4.3 Tracer DDS and discrete-time phase sampling

In the Frequency Tracker block diagram of Figure 4-2 the tracer phase, from the tracer DDS, must be sampled into the reference clock domain (the REF\_PH\_SAMPLING\_CLK and its decimated & phase-locked companion, REF\_LOOP\_CLK.) This is a critical operation and is quasi-analogue in nature since tracer phase is modulated by aLO variations as well as fiber link-induced perturbations. Both of these effects must be adequately captured, for any aLO offset from the reference frequency<sup>18</sup>, including momentarily very low or no offsets. Clearly, these latter two occurrences, although they should be rare, can occur and cause beating as first reported in [10], which was the case early-on in IC research effort.

Since that report, a superior tracer DDS and phase sampling architecture has been developed that shows no hint of beating effects during discrete-time simulation, for no, very low, some, and large frequency offsets from the reference frequency. A case in point is Figure 4-3, where the offset from the  $^{\sim}10$  MHz tracer frequency is  $^{\sim}2.8$  Hz and clearly no beating occurs.

<sup>&</sup>lt;sup>18</sup> Within the frequency tolerance of the antenna LO, typically +/- a few ppm.

In digital logic it is regularly necessary to transfer data between independent clock domains. There are generally two methods to do so: 1) dual-port memory and, 2) single-bit asynchronous sampling. In 1), the memory cell that contains the data to be transferred stores the information and digital logic on either side accesses it without contention from the other side except that, of course, the memory cell can't be in the process of being changed by one side whilst the other is trying to determine its state. In 2) a single register bit, which can be 0 or 1, is sampled by a register clocked in the other clock domain. If the register bit is changing state as it is being sampled in the other clock domain, that sampling may be successful (i.e. capture the change) or not, but it is accepted and expected that either case may occur. To ensure this transaction takes place it is required that the bit is 0 or 1 long enough to eventually be captured. This method can and does induce a metastability in the capturing register but this is quickly resolved due to the physics of the logic implementation as well as with additional register stages, 2 shown in Figure 4-14, although up to 5 may be more appropriate depending on the launch and capture relative clock rates and their clock rates relative to the clocking registers' gain and speed. Even if the rare clock-domain-crossing error occurs, it will be a glitch that will a) be filtered-out by the LPFF and b) possibly cause a momentary de-coherence for a period of time vastly shorter than the correlator integration time. An Internet search reveals many articles on the nature and behaviour of metastability—what is clear is that it is well understood and managed with proper digital logic design methods and that in no case does it result in a register bit being "stuck" in a state forever 19. Also, it should be clear that it is fundamentally impossible for there to be a net cumulative phase bias in the sampled phase, meaning that it is impossible for there to be a phase drift (i.e. frequency offset) in the sampled phase that is not in the tracer DDS output.

An extension of method 2) is to transfer N bits of data at the same time, but with the restriction that only one of the N bits can change state on any transmit clock cycle and that the receive clock cycle must be sufficiently shorter than it to ensure no bit transitions are missed. This is a well-known method referred to as "Gray-code", employed where appropriate and with timing requirements described for example, in [11].

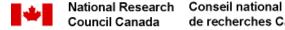

Discrete-time phase sampling employed uses both method 1) and 2) in concert to allow any number of phase bits, with each phase state any arbitrary value, to securely and reliably cross asynchronous clock domains. This greatly increases the parameter space for tracer frequency, number of phase bits, and performance. A block diagram of this method, including the tracer DDS, is shown in Figure 4-14 and based on the above description it should be clear how it works:

<sup>&</sup>lt;sup>19</sup> In the literature, but also the author's personal experience in the design and function of the JVLA WIDAR correlator, where transferring bits a cross a synchronous clock domains was extensively used in FPGAs and the correlator ASIC. In that system there are millions if not billions of these cross-clock domain transactions reliably occurring every second and have been for the last ~10 years.

Figure 4-14 Tracer phase sampling block diagram, including the tracer DDS and simplified IC signaling to it. This circuit can be further simplified by consolidating the 4-bit address counter and the Bin-to-Gray blocks into a single Gray-code counter on the transmit side and using the sampled Gray-code for the rd addr on the receive side.

Critical high-performance timing is limited to a few, in this example<sup>20</sup>, 4-bit registers and these can operate up to ~700-800 MHz (Intel Stratix-10) and even higher in an ASIC. These registers must operate at the full clock rate without parallel/demux operations; the tracer DDS may be pipeline or multi-phased (e.g. "ping-pong") for higher net clock rate operation. The "sdp FIFO" (simple dual-port) may be structured and operated similarly.

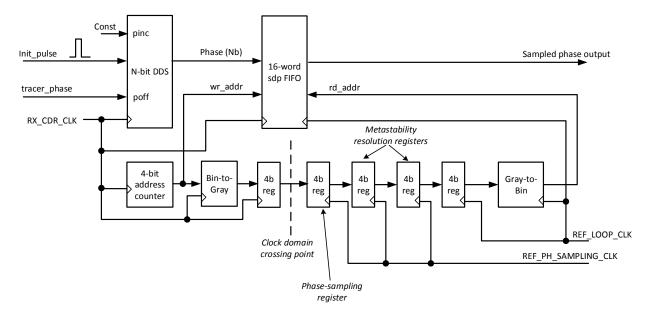

An early "first LED test" of the Frequency Tracker, complete with discrete time phase sampling, was performed using the Xilinx ZCU111 RFSoC evaluation board being used for the lab demo reported in [3]. This test used the Frequency Tracker to measure one of the board's crystal frequencies in the reference clock domain of another of the board's crystals, indicating key circuit status by driving board LEDs. This was a quick test to empirically determine if the Frequency Tracker and phase sampling were working, although no data was acquired since such acquisition requires software, which was not available <sup>21</sup>. A block diagram of the FPGA design for this test is shown in Figure 4-15:

<sup>&</sup>lt;sup>21</sup> As of this writing much software has been developed; the RFSoC FPGA design is complete, tested, and undergoing the usual iterative compile/modify process to a chieve timing closure.

<sup>&</sup>lt;sup>20</sup> And used in the laboratory demonstrator [3] FPGA code.

Figure 4-15 Block diagram of the "first LED test" run on the Xilinx ZCU111 evaluation board RFSoC FPGA.

The first LED test was successful, with LEDs lighting up as expected quickly after circuit start up. Whilst this doesn't quantify the performance of the Frequency Tracker, phase and frequency lock, determined internally in the circuit by analyzing internal variables to produce lock indicators (shown as "Phase lock" and "Freq lock" in Figure 4-2), would simply not have been asserted if lock were not established.

The phase stability of the REF\_PH\_SAMPLING\_CLK at the Clock domain crossing point and for the additional Metastability resolution registers, relative to all other such instances in the same or other devices across a complete radio astronomy system, matters—if there is low-level differential phase wander that is within the passband of the LPFF, it will show up as antenna-based phase wander in correlator output visibilities. Thus, REF\_PH\_SAMPLING\_CLK distribution across the system must be handled sufficiently well to ensure these effects are sufficiently low. The RX CDR CLK's dynamic phase behaviour also matters—changes in it that are within the passband of the LPFF, that are not due to the aLO, will also show up in correlated visibilities as above. Thus, the performance the of round-trip phase measurement to remove fiber delay perturbations, the value of the parameter "rtm" in equations (1) and (2), the phase noise performance of the SERDES Rx CDR PLL, and the phase noise of reference clock distribution must be considered. These topics are discussed in some detail further on.

#### 4.4 The ReSampler

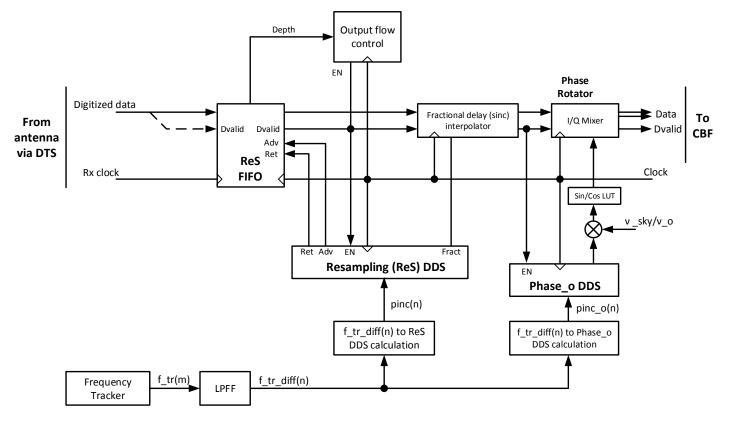

All-digital re-sampling of a digital signal from one sample frequency to another uses the same digital integer-sample and fractional-sample delay methods used in radio astronomy correlator wavefront delay trackers. The re-sampler contains a FIFO, followed by a fractional delay interpolator, and it retards or advances the read pointer, in coordination with fractional delay interpolation, to keep the total endto-end delay constant and, of course, to keep the read and write FIFO pointers from colliding. A graphic showing the equivalent DAC/ADC circuit and its fundamental operation is shown in Figure 4-16; one can immediately see that the delay through this circuit is constant since there are fundamentally no delay elements. All-digital operations avoid the uncertainties that would be introduced, not to mention performance limitations, cost, and power, if actual DAC and ADC devices were used.

Figure 4-16 Re-sampler DAC/ADC equivalent circuit and interpolation operation converting digitized science data from the fa clock domain to the fc clock domain.

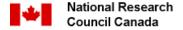

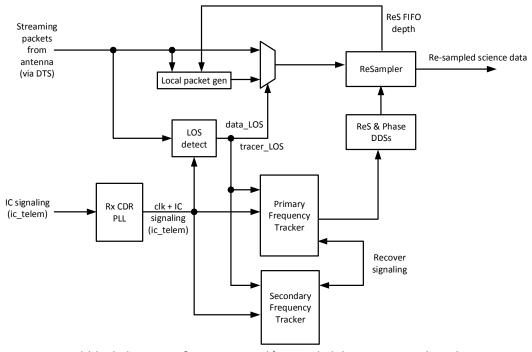

A simplified view of the "ReSampler", which includes the "ReSFIFO" that facilitates the read pointer advance/retard operation mentioned, fractional delay interpolator, and integrated Phase Rotator, is shown in the typical implementation block diagram of Figure 2-2. A more detailed block diagram of the ReSampler is shown in Figure 4-17 and a description of its operation follows.

Figure 4-17 Block diagram of the "ReSampler", which includes an integrated Phase Rotator, but doesn't include the Frequency Tracker or LPFF, shown here for context.

The Frequency Tracker, shown in in Figure 4-2, produces a steady stream of high-time resolution tracer frequency measurements f\_tr(m) into the LPFF. In the lab demo (described in [3]) FPGA firmware, they are produced every ~10 µsec and are 64-bit fixed-point unsigned values with a 36-bit fractional component, providing ~1e-11 Hz of frequency resolution and contain no frequency bias relative to the reference clock. As shown there, these measurements contain confusing fiber link jitter and, as shown in Figure 4-3 and Figure 4-4, contain phase noise from digital phase sampling of Figure 4-14.

Before the LPFF, 64-bit  $f_tr(m)$  numbers are trimmed to 43-bit signed "frequency difference from nominal" numbers (with the same 36-bit fractional component as above), " $f_tr_diff$ ." Such is done for LPFF logic and processing efficiency, allowing for absolute frequency tolerance of the aLO, relative to the reference clock, of +/-10 ppm when using a ~10 MHz tracer frequency. If needed, this tolerance could be expanded with more  $f_tr_diff$  bits.

After the LPFF, the filtered Frequency Tracker measurements, "f\_tr\_diff(n)" are fed to calculators that convert these to "pinc" values fed to the DDS that drive the ReSampler and the Phase\_o Rotator, implemented as a digital I/Q mixer, yielding a complex output. As shown, one calculator is for the Resampling DDS and one is for the Phase\_o DDS.

The Phase\_o DDS produces the phase correction for v\_o, a conveniently-chosen frequency. This phase is then multiplied up to the phase correction at the current v\_sky, which is the (nominal) net down-conversion frequency of the signal being corrected. For this to work, the Phase\_o DDS output (phase) must contain the total phase, integer+fractional, since timing chain (see highlighted paragraph on p. 32)

start up. This seems onerous, but with enough Phase o DDS bits is easily implemented. For example, if v\_o=1.0 GHz, f\_Phase\_o\_DDS=125 MHz<sup>22</sup>, and a +/-10 ppm aLO crystal is used, the worst-case phase change of Phase o DDS output over 10 yrs is 1 GHz x 1e-5 x 125MHz x 3600 s x 24 hrs x 365 days x 10 yrs ~= 4e20 cycles. This requires ~68 bits to capture. Thus, with 68 bits of integer phase and 32 bits of fractional phase, the Phase\_o DDS, for this example, requires a 100-bit DDS—not a difficult logic implementation at 125 MHz—but potentially requiring a timing chain restart every 10 years<sup>23</sup>. The v sky/v o multiplier then needs to be a 100-bit x Nb ratio multiplier, where the ratio of v sky/v o contains an integer and fractional part. For v\_sky\_max = 1THz, with a 1 MHz v\_sky tuning resolution, ~7 significant figures are required, likely meaning Nb ratio~=16 bits is more than sufficient, TBC. Even if there is a low-level error in v\_sky/v\_o digital representation, this error multiplies phase, resulting in a small phase error with no cumulative phase drift component. As well, the 100-bit x 16-bit (in this example) multiplier will require several pipeline stages to yield a result, resulting in a time delay in application of the phase calculation to the I/Q mixer. This delay is constant in the reference clock domain, resulting in no net frequency-dependent effect. Finally, it should be clear that when v\_sky changes to some other tuning and then comes back, no net phase jump occurs since the Phase o DDS operation has been continuous, meaning that coherence on the sky has been maintained.

The DC gain of the LPFF must be precisely known and applied as a rescaling factor after the LPFF, to deal with bit growth that naturally occurs during LPFF (FIR filter) processing. If this rescaling isn't precise, it will cause the ReSampler output to drift in delay and phase. One method that works well in practise is to scale the tap coefficients such that the sum of the (integer) tap coefficients is precisely a power of 2; post-LPFF rescaling then simply involves a bit shift and unbiased rounding operation, guaranteeing required gain accuracy.

For the Resampling DDS, the pinc equation is (see Section 13 Appendix for derivation):

$$pinc_{ReS\_dds}(n) = \frac{2^{(nb_{ReS\_dds} + nb_{tr\_dds})} \cdot R_{a\_t} \cdot f\_tr\_diff(n)}{f_{ck\ ReS\ dds} \cdot pinc_{tr\ dds}}$$

(5)

Where:

*nb<sub>ReS dds</sub>* is the number of bits in the ReSampler DDS.

$nb_{tr\ dds}$  is the number of bits in the tracer DDS.

$R_{a}$  tis the ratio of the ADC sampling frequency to the clocking frequency of the tracer DDS, where both have no error (i.e. their nominal frequency.) E.g. if the ADC is digitizing at 40.0 Gs/s in the aLO clock domain, and the tracer DDS at the central site is clocking at 625.0 MHz using the SERDES Rx CDR PLL-recovered clock, this ratio is 64. Whilst a power of 2 in this ratio is convenient, it is not essential.

f tr diff(n) are the streaming measurements out of the LPFF. If the ADC frequency is higher than nominal, this will be a positive number, if lower, a negative number.

<sup>&</sup>lt;sup>23</sup> Although likely never required if a +/-1 ppm a LO crystal is used and knowing that its frequency will be wandering around between these limits, rather than stuck at one extreme indefinitely.

Canadä

<sup>&</sup>lt;sup>22</sup> i.e. "Clock"=125 MHz, although normally the DDSs operate at sub-Clock frequencies, since Clock is normally the highest frequency that the FPGA can support for the main sample-processing pipeline.

$f_{ck}$  ReS dds is the clocking frequency of the ReSampler DDS.

pinctr dds is the fixed pinc value chosen to be used in the tracer DDSs across the system.

**Example:** for the lab demo described [3]:  $nb_{ReS}$  dds=64;  $nb_{tr}$  dds=16;  $Ra_t$ =1;  $f_{ReS}$  dds=125.0e6;  $pinc_{tr}$  dds=2693; and f tr diff(n) measurements are in the range of +/-127 Hz, with a 36-bit fractional component as described above.

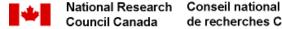

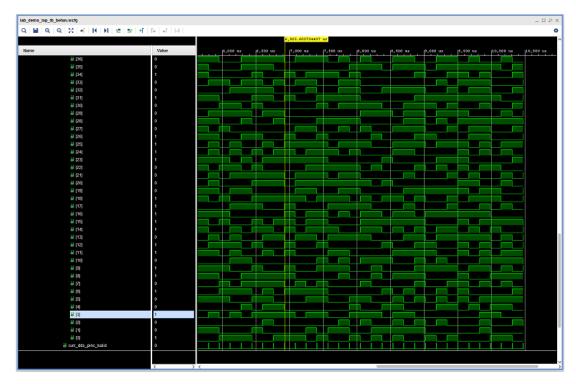

The above calculations are done with fixed-point arithmetic and in any case must ensure there are no biases introduced into the resulting calculation. Biases will accumulate and cause a drift of the resampled output, which will show up in correlated visibilities and eventually cause the over/under-flow of the ReS FIFO if significant enough. Biases in this calculation, which should only happen during the division operation, shouldn't occur due to the dithering effect of a noisy f\_tr\_diff value as in Figure 4-5. Examination of the lab demo [3] end-to-end FPGA RTL simulation waveform data for both the pinc value fed to the ReS DDS of Figure 4-17, and the pinc value fed to the Feedback DDS of the Frequency tracker of Figure 4-2, indicate that all bits are being "tickled", shown in Figure 4-18 and Figure 4-19 below. This does not guarantee that there is no bias, but is an indication of such. Dividers for both of these pinc calculations are implemented using the Xilinx IP Catalog "Divider Generator", described in the Xilinx document "PG151." These descriptions, for the "divider solutions" used, do not seem to explicitly indicate if there are biases in the results or not, but if so should be, in the worst case, at the level of some fraction of a pinc LSBit. For example, the bias of one pinc LSBit of a 64-bit ReS DDS operating at  $f_{Res\ DDS}$ = 250 MHz, after one year leads to a delay error of 4e-4 samples and after 10 years, 4e-3 samples. Similarly for the Phase DDS, but in cycles of phase. Nevertheless, further investigation into this issue is needed and such is identified as a risk in section 10.

Figure 4-18 FPGA RTL simulation waveforms for the lower 37 bits (of 64 bits) of pinc fed to the ReS DDS indicating that all bits are being "tickled" due to the dithering effect of a noisy f tr diff on equation (5).

Figure 4-19 FPGA RTL simulation waveforms for the lower 36 bits (of 64 bits) of pinc fed to the Feedback DDS of the Frequency Tracker (Figure 4-2) indicating that all bits are being "tickled" due to the dithering effect of a noisy f\_tracer\_loop.

The Phase\_o DDS  $pinc_{ph}$  calculation is similar except that  $R_{a}$  is instead  $R_{vo}$ , where  $R_{vo}$  is the ratio of the conveniently-chosen  $v_0$  to the clocking frequency of the tracer DDS. pinc<sub>ph</sub> DDS is a positive number if the netLO at the antenna (i.e. v sky) is higher than nominal and negative if it is lower than nominal. This calculation assumes that the digitized data has the same frequency sense as the sky; if not, a simple "flip the sign of every other sample" correction can be done at an appropriate place, easiest to understand if it is done before the Phase Rotator. For ALMA there is an added complication and that is 180 deg and 90 deg Walsh function switching at the antenna. These phase jumps are in the data and flow through the pipeline to the output of the Phase Rotator seamlessly, requiring no consideration in this circuit.

For both DDSs, their output phase vs time functions reflect the difference between the actual antenna frequency, which is changing with time, and the nominal, which is in the reference clock domain and is therefore constant. For example, if the antenna ADC clock frequency is precisely 1.0 Hz higher than nominal, no matter what the actual ADC clock frequency, the ReSampler DDS output will be a sawtooth function at precisely 1.0 Hz, as measured in the reference clock domain. Similarly for the Phase\_o DDS, multiplied up by  $v_sky/v_o$ .

Referring to Figure 4-17, in order for the ReS FIFO to not overflow or underflow, the write data rate and the read data rate must be matched on average. The ReS FIFO is written, and the write pointer advanced, for every sample<sup>24</sup> arriving from the antenna. This is accomplished by adjusting the read pointer to "keep up with it" by advancing (Adv) or retarding (Ret) the read pointer, compared to where

<sup>&</sup>lt;sup>24</sup> Or "super-sample rate" group of samples.

it would've been without any such adjustment. Such Adv/Ret pulses derive from the Resampling DDS whenever the paccum phase ramp rolls over from max to 0 or vice versa. When the DDS pinc is a positive number, meaning that the antenna ADC frequency is higher than nominal and it is writing into the ReS FIFO faster than nominal, Adv pulses occur; when negative, Ret pulses occurs. The "Output flow control" circuit simply ensures that the ReSFIFO doesn't over or underflow by asserting Dvalid low every so often, going to all of the blocks shown. Thus, the actual "Clock" frequency used for this pipeline in the FPGA must be > the highest data rate that can be written into the FIFO. If desired, the Output flow control circuit could be a DDS, generating Dvalid lows at the required rate. For example, a Clock frequency of 501 MHz, for a data rate of 500 Mwords/s could be used, easily meeting a 10 ppm aLO tolerance requirement<sup>25</sup>.

ReSampler output discrete-time samples then enter the "Fractional delay (sinc) interpolator", where the fractional delay (ramp) from the ReS DDS selects the set of tap coefficients required to apply the correct interpolated value. When Adv or Ret pulses happen, the fractional delay flips accordingly such that there is no net delay change across the transition. This operation, when it happens, can<sup>26</sup> be made entirely glitchless [12][13][14] such that, save for the fidelity of the fractional delay coefficients, there is no discontinuity in the data.

The reader might observe that this is not a stateless circuit and such is indeed the case —the digital signal chain from the ADC sampling point in the antenna until the output of the ReSampler is part of the timing chain of each antenna<sup>27</sup>. If there is an undetected glitch or discontinuity in this chain, then coherence on the sky is lost. Various methods are available and should be used to "bullet-proof" this circuit: PLLs' lock indicators; data transport sample counting and error detection; detection of unusual discontinuities in Frequency Tracker f tr(m) measurements; comparison of a counter value in and out of the ReS FIFO to detect any slips, etc. The robustness of this chain and the IC measurement timing chain, including momentary link dropouts, is discussed later.