# NATIONAL RADIO ASTRONOMY OBSERVATORY Charlottesville, Virginia

Electronics Division Internal Report No. 134

A 512-CHANNEL INTEGRATOR AND MULTIPLEXER

C. Pace and J. Payne

OCTOBER 1973

NUMBER OF COPIES: 150

# TABLE OF CONTENTS

# PAGE

| 1.0  | Introduction                                                      | L |

|------|-------------------------------------------------------------------|---|

| 2.0  | Principle of Operation                                            | 1 |

| 3.0  | Integrator/Multiplexer Card                                       | 3 |

| 4.0  | Control Logic and Computer Interface                              | 6 |

| 5.0  | Meter Circuits                                                    | 9 |

| 6.0  | Power Supplies 10                                                 | С |

| 7.0  | Constructional Details 10                                         | D |

|      | Figures                                                           |   |

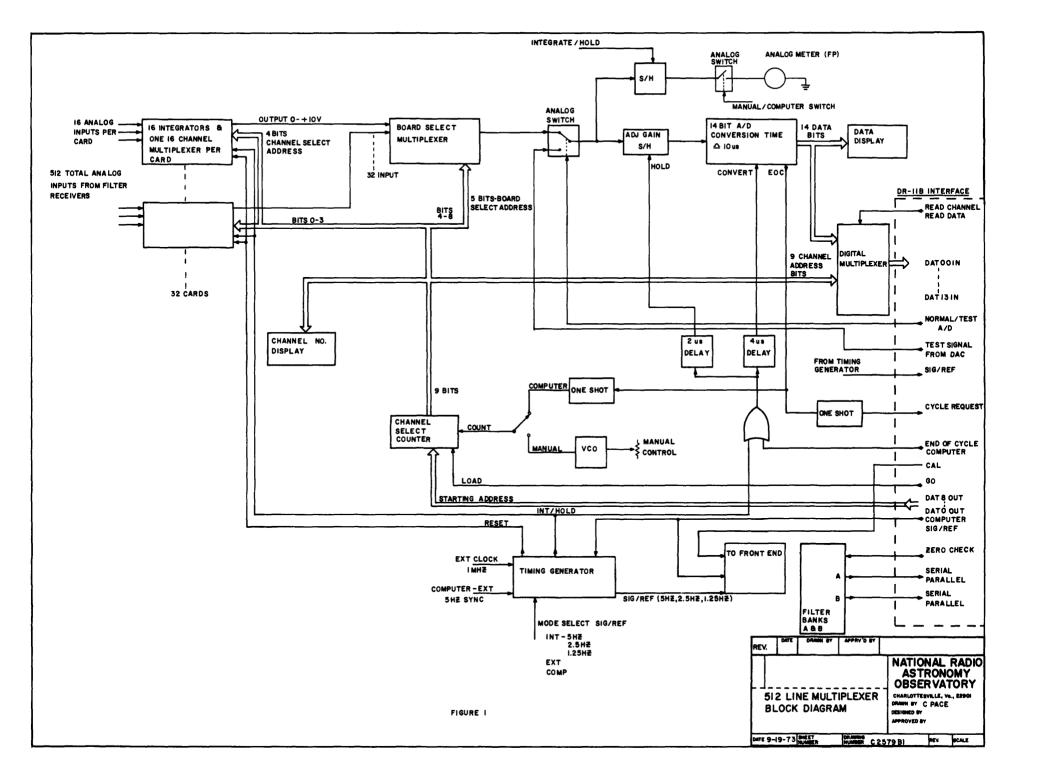

|      | 1. Block Diagram of Multiplexer                                   |   |

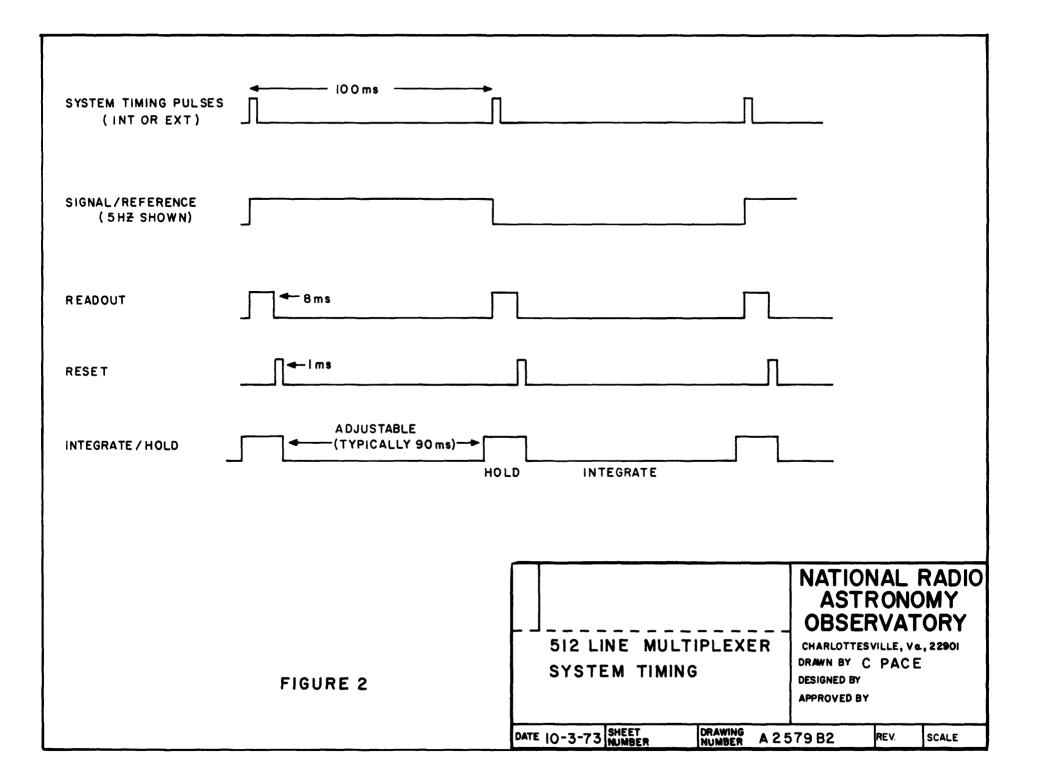

|      | 2. System Timing Diagram                                          |   |

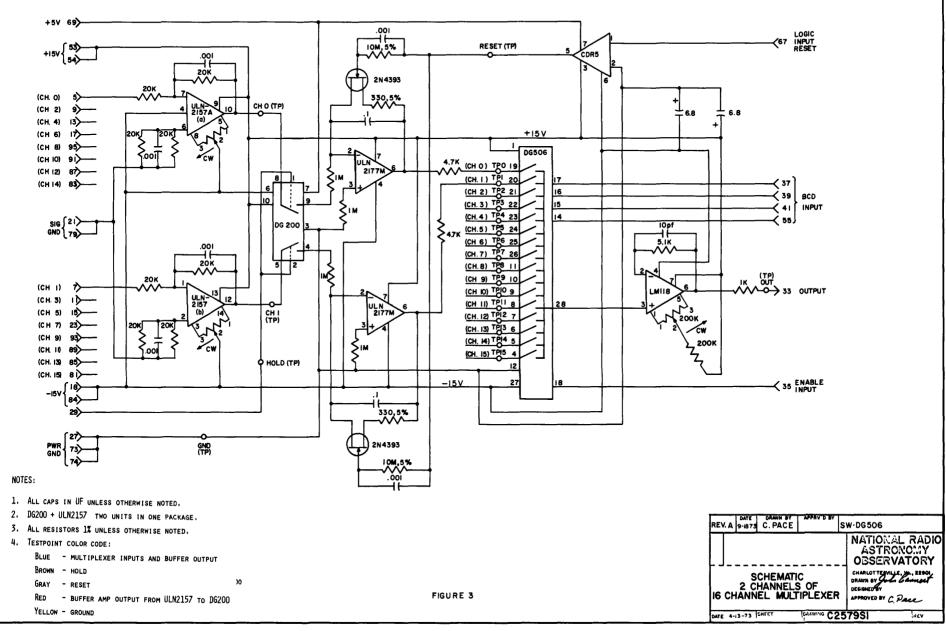

|      | 3. Circuit of Integrator Card                                     |   |

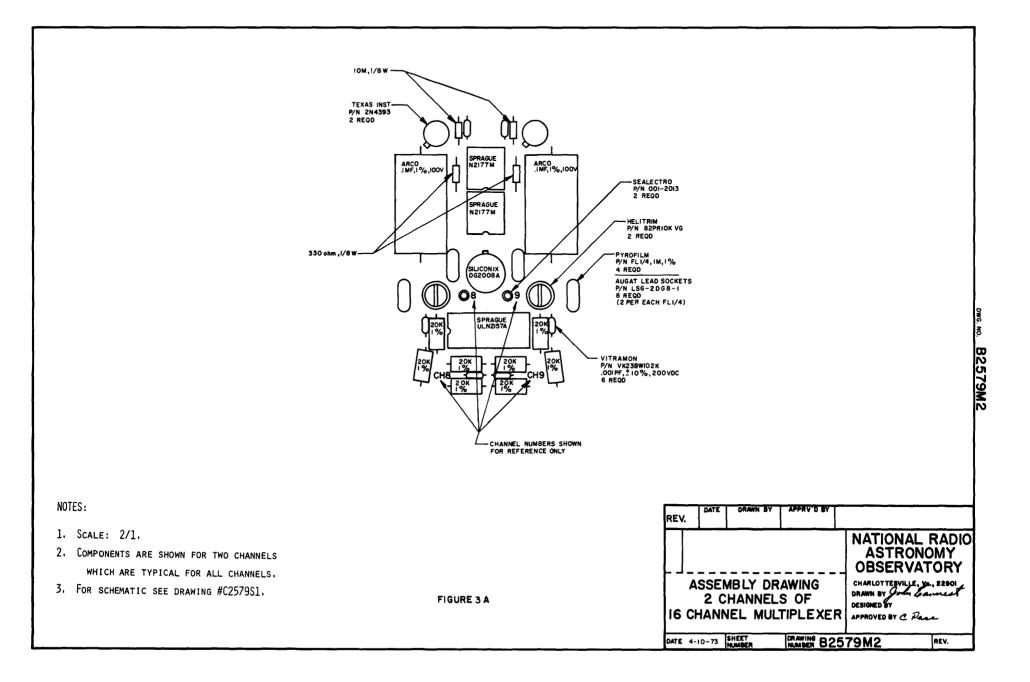

|      | 3A. Assembly Drawing 2 Channels of 16 Channel<br>Multiplexer Card |   |

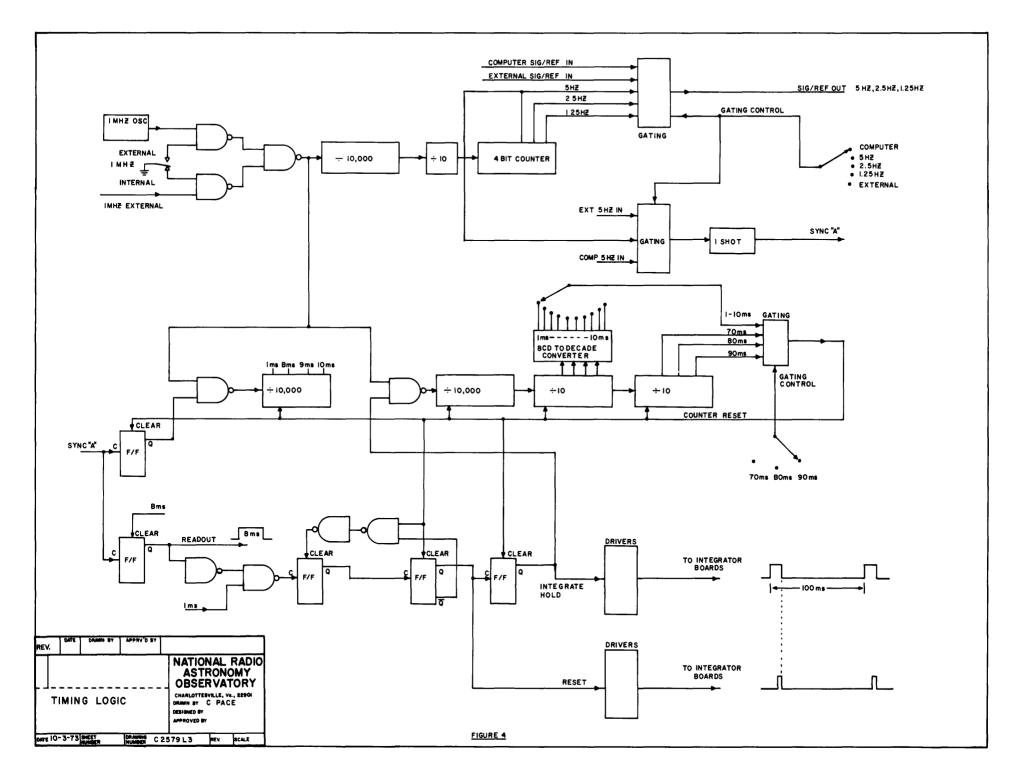

|      | 4. Control Logic                                                  |   |

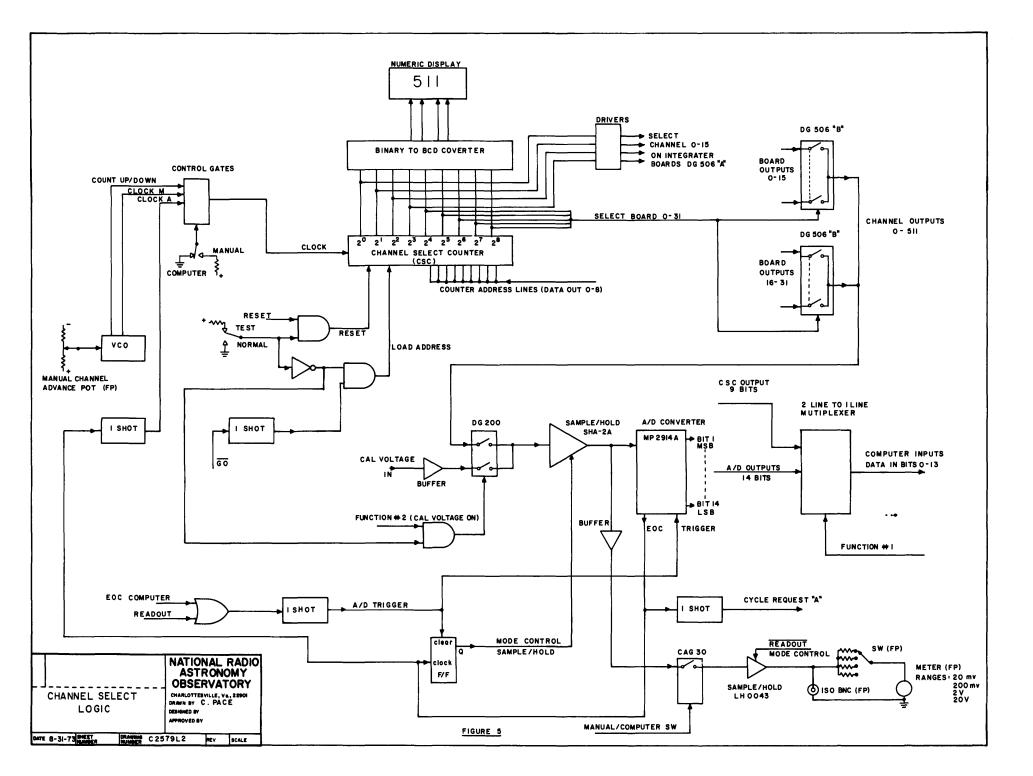

|      | 5. Control Logic                                                  |   |

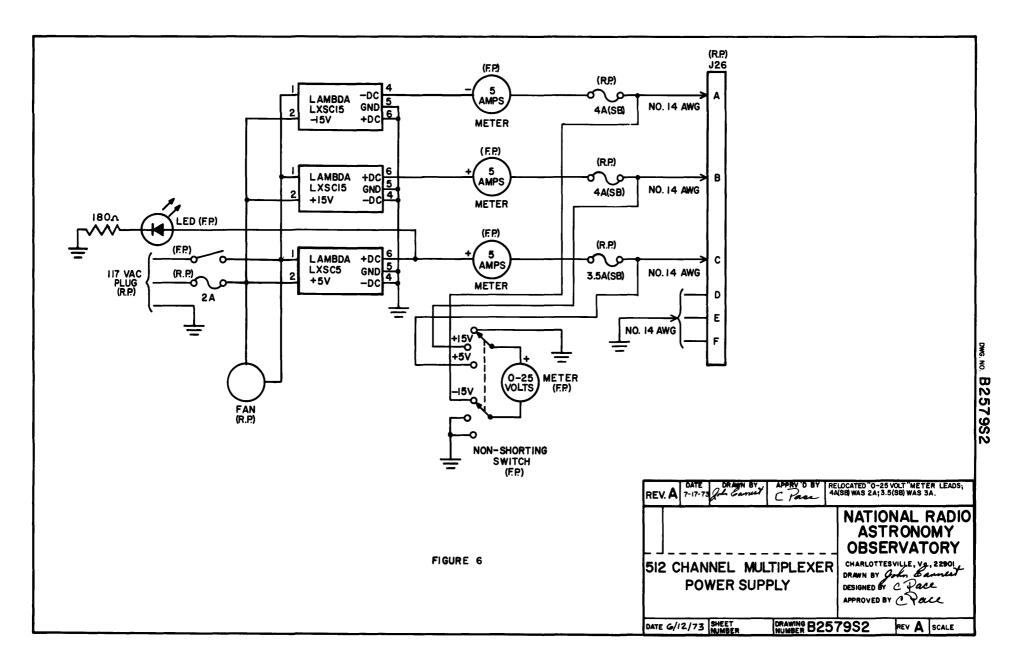

|      | 6. Power Supplies                                                 |   |

| DATA | SHEETS                                                            |   |

|      | 1. DG 506 16 Channel Multiplexer                                  |   |

|      | 2. DG 200 Analog Switch                                           |   |

|      | 3. MP 2914A A/D Converter                                         |   |

## 1.0 Introduction

This report describes the interface between the newly developed 256 channel filter receivers and the PDP-11 computer. The same general principles are used as in previous systems (E.D. Internal Report #101) but because of the greater number of channels a more compact form of construction is used.

# 2.0 Principle of Operation

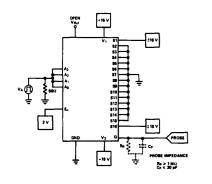

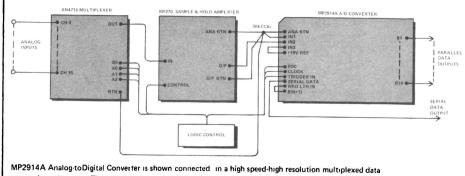

A block diagram of the interface is shown in Figure 1.

The analog inputs from each channel of the filter receiver are first buffered to reject common mode signals then integrated with a true integrator for an exact period. This period is adjustable and will be set to about 90 ms. At the end of the integration period the integrators are switched to a hold mode, the output of each integrator is sampled, converted to 14 bit binary number and fed to the computer. This scanning, converting and read in process takes about 8 ms for the 512 channels. The integrators are then reset and another integration period begins.

The data flow between the multiplexer and the PDP-11 is controlled by a general purpose direct memory access interface to the PDP-11 unibus. This interface (the DR11-B), rather than using program controlled data transfers, operates directly to the memory, moving data to and from the multiplexer.

A typical read out sequence would take place in the following way. The address of the first channel to be converted is loaded into the channel select counter (this is to permit read outs of banks of channels other than 512). At the start of the hold period the first channel is converted by the 14 bit A/D converter. The end of conversion (E.O.C.) signal from the converter is used to request a data transfer from the DR-11B interface and also to advance the channel select counter to the next channel. When the transfer is complete the DR-11B issues an end of cycle signal that starts the next conversion. This data exchange continues until the prescribed number of transfers has taken place. This is indicated by the overflow of a register internal to the DR-11B that has previously

-1-

been loaded by the program with the desired number of data transfers. At the end of a block transfer the program may check that the final channel selected by the channel select counter is the correct one.

A feature is included to permit testing of the A/D converter under computer control by providing it with a variable input from a DAC.

DAT 14 IN is used to indicate if the data being sampled is the result of a signal or reference integration. Signals are also provided that indicate if the filter receivers are being used in the serial or parallel mode.

The multiplexer is also used as an interface between the computer and the radiometer. The computer may provide the signal/reference waveform rather than the internal timing generator in the multiplexer. Also provided by the computer are calibration and zero check signals to the front end and filter receivers.

The timing generator provides the integrate/hold and reset signals to the integrator cards, and also the signal/reference waveform to the front end (or L.O.). The signal reference squarewave is available at 5 Hz, 2.5 Hz and 1.25 Hz so that a signal or reference period may consist of one, two or three integration periods. The timing generator may be synchronized to an external 5 Hz signal (for use with a chopper wheel or nutating subreflector). A 1 MHz clock internal to the timing generator is normally used for generating the various waveforms but provision is made for an external 1 MHz clock.

Manual scanning of integrator outputs is useful for checking correct operation of the filter receivers and multiplexer. A V.C.O. is used to drive the channel select counter up or down at whatever rate is desired. The channel number is displayed both in binary and decimal form. The channel output is displayed on a moving coil meter, the value at the end of an integration period being stored in a sample/hold circuit.

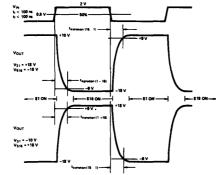

The system timing diagram is shown in Figure 2.

-2-

# 3.0 Integrator Multiplexer Card

The basic printed circuit card used in the integrator/multiplexer consists of 16 channels, each channel being made up of a buffer amplifier, and a true integrator with hold and reset capability. Also on the card is a 16 channel multiplexer integrated circuit. Thirty two of these cards are used to give the 512 channel capability.

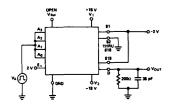

A circuit diagram of two channels, together with the 16 channel multiplexer and output amplifier is shown in Figure 3 and an assembly drawing of two channels is shown in Figure 3A.

# 3.1 Buffer Amplifier

The buffer amplifier used was a Sprague ULN 2157. Two of these amplifiers are packaged in a 14 pin dual in line plastic package. The relevant performance specifications of this amplifier are as follows:

|                                      | TYP             | MAX             |

|--------------------------------------|-----------------|-----------------|

| Input offset voltage                 | <u>+</u> 1.5 mV | <u>+</u> 5.0 mV |

| Input offset current                 | <u>+</u> 5 nA   | <u>+</u> 25 nA  |

| Input bias current                   | 70 nA           | 250 nA          |

| Input offset voltage/<br>temperature |                 | 10µV∕°C max     |

## 3.2 Integrate/Hold Switch

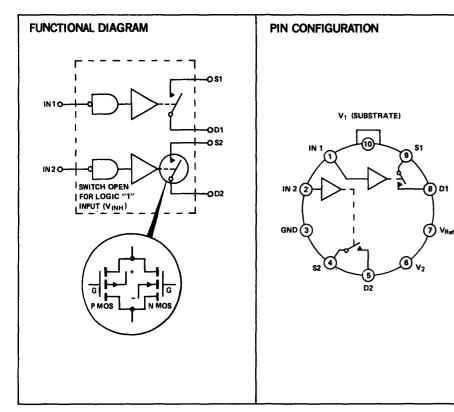

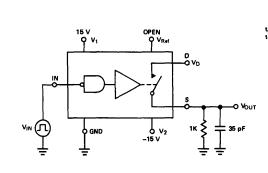

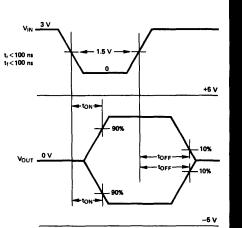

To perform the switching functions in the integrate/multiplexer we made extensive use of the CMOS analog switches that have become available over the last year. The switch used for performing the integrate/hold function is a DG 200 manufactured by Siliconix, Inc. The DG 200 has two independent analog switches, each switching function being controlled directly from TTL logic. The "on" resistance is <100 ohms and is not very dependent on input signal level or

-3-

temperature. The switch operated from  $\pm 15V$  power supplies and will switch analog signals of  $\pm 15V$ .

## 3.3 Integrator

The operational amplifier used for the integrator is a ULN 2177 manufactured by Sprague. The time constant of integration of 100 ms was satisfied with a 1 M $\Omega$  input resistor and a 0.1µF polystyrene capacitor. The input offset currents are critical in this case and the important specifications of the amplifier are listed below:

|                        | TYP             | MAX           |

|------------------------|-----------------|---------------|

| Input Offset Voltage   | <u>+</u> 1.5 mV | <u>+</u> 5 mV |

| Input Offset Current   | <u>+</u> 0.4 nA | <u>+</u> 1 nA |

| Input Bias Current     | 0.8 nA          | 2 nA          |

| Open Loop Voltage Gain | 150 V/mV        |               |

A polystyrene capacitor was used for low leakage and low dielectric absorption.

A junction F.E.T. was used for resetting the integrator because the discharge current would be slightly too high for CMOS device. A CDR5 level shifter is common to all reset transistors on a card and serves to change the TTL input signal to  $\pm 15$ suitable for switching the F.E.T.s.

# 3.4 Multiplexer Chip

To sample the output of each integrator while in the "hold" mode a 16 channel CMOS multiplexer with 4 line binary addressing is used. This multiplexer chip, a DG 506, is manufactured by Siliconix and enjoys the same advantages as CMOS analog switches in general. Resistors were included in series with each analog input to the device to limit the input current needed to charge the common drain capacitance when switching between analog inputs of different levels. This current should be limited to avoid burning out the F.E.T. switches and also to avoid overloading the integrator. A later

-4-

version of this chip (produced by Harris Semiconductor) includes these resistors. The additional time constant introduced by these resistors is not significant.

# 3.5 Output Amplifier

The output amplifier associated with the multiplexer is used in a unity gain non-inverting mode to give a high input impedance. This is important to avoid errors introduced by variations in "on" resistance of the different channels of the DG 506.

## 3.6 Performance of Integrator/Multiplexer Card

All gain determining components on the card are  $\pm 1$ %. Tests on the prototype card gave a highest channel gain of 1.005 and lowest gain of 0.992. The variations in gain for different channels with temperature over the range of 0-45°C were  $\frac{\Delta G}{\Delta T} = \pm 1.0 \times 10^{-4}$ /°C minimum and  $\frac{\Delta G}{\Delta T} = \pm 3.5 \times 10^{-4}$ /°C maximum. The rise time at the output of the card was measured and found to correspond to a time constant of 0.4µs. To permit settling to within one bit of the 14 bit A/D converter a 4µs delay between selection of a channel and the start of the conversion is used.

The zero offset voltage of each channel may be adjusted to zero by means of the offset potentiometer associated with the buffer amplifier.

# 3.7 Cost Per Channel

The cost per channel is as follows:

| Component cost per channel            | \$15.38 |

|---------------------------------------|---------|

| Printed circuit card cost per channel | 1.38    |

| Construction cost per channel         | 2.50    |

|                                       | \$19.26 |

This cost refers just to integrator multiplexer cards and does not include the control logic or A/D converter.

-5-

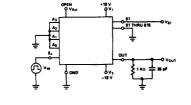

# 4.0 Control Logic

# 4.1 Timing Logic

The readout, reset, integrate signals are generated by the 1 MHz internal oscillator or 1 MHz external oscillator. A 5 Hz squarewave from the computer, subreflector (sync input) or the internal 5 Hz gives the starting pulse (SYNC A) (Fig. 4) for the generation of the readout, reset, integrate cycle.

The readout, an 8 ms positive pulse, is generated by dividing the 1 MHz clock. The reset is a 1 ms positive pulse and is used to reset all integrators to zero. When in the TEST mode the reset is used to reset the channel select counter (CSC). At the end of reset the 1 MHz clock is divided by decade counters to generate the integrate period, Fig. 4. This is a variable time period and can be varied from 70-90 ms by selector switches behind the front panel.

# 4.2 Signal/Reference

Signal/reference can come from three sources, internal, computer and external (Fig. 4).

Internal signal/reference is generated from the 1 MHz and can be varied by a front panel switch for 1.25 Hz, 2.5 Hz or 5 Hz operation. This signal also available on BNC connectors on the back panel in either 3C or TTL logic.

External signal/reference comes from a BNC on the back panel and can be either 3C or TTL logic input. It should be no higher frequency than 5 Hz.

The computer signal reference is generated by Data Out 14 from the computer and should be no higher frequency than 5 Hz.

An external sync must also be supplied when in the external or computer position. This signal generates Sync "A" and should be a 5 Hz TTL signal. When in external position J21 on the back panel is used and the sync output of the nutating subreflector can generate Sync "A". When in the computer position Data Out 15 is switched at a 5 Hz rate to generate Sync "A". Sync "A" is used to start the readout cycle.

# 4.3 Channel Select Counter

Channels can be selected in two ways manual or computer. In the manual mode the clock pulses (Clock M) to advance the CSC are generated by a VCO, the frequency of the VCO is controlled by the manual channel advance pot on the front panel (Fig. 5).

An up-down counter is used and the manual advance can make the channels advance up or down to the desired channel.

In the computer mode the end of cycle from the A/D (Clock A) advances the counter. It only allows the counter to count up. When the test-normal switch is in normal the CSC is loaded by the computer.

The four least significant bits of the CSC are buffered because they drive the DG 506's (A) on the 32 integrator boards. The next five bits select which board is displayed or sent to the computer by driving DG 506 (B) on Board W. The MSB  $2^8$  is an enable that selects channels 0-255 or 256-511 by enabling the DG 506 (B) on Card W.

The load lines from the computer load the CSC when in computer-normal mode. The load command is generated by the "GO" command from the computer.

A one shot is used to reset the CSC when switching from computer to manual mode.

The binary output of the CSC is displayed by L.E.D.s on the front panel. This output is also converted to BCD and is displayed on the Numeric Display (Fig. 5).

# 4.4 Interface

# Inputs from computer to multiplexer

GO is used to generate the load data pulse for CSC. The  $\overline{GO}$  bit triggers a N8162A one shot that produces the load pulse (Fig. 5).

END of cycle from the computer (EOC computer) along with the readout produce the trigger for the A/D and reset the S/H mode control F/F (Fig. 5).

-7-

Data Out 13 is used to generate the cal "on" signal. A F/F used as a latch stores the data until it is updated.

Data Out 12 is used to generate the zero check.

Data Out 15 is used to generate Sync "A" computer.

Data Out 14 is used to generate Sig/Ref computer.

Funct #1 - This computer output is used to select what type of data will go to the computer either channel data or the last count in the CSC (Fig. 5).

Funct #2 - This is used to test the calibration of the A/D. Funct 2 allows either channel voltages or a cal voltage from the computer to be applied to the A/D (Fig. 5).

# Output of Multiplexer to Computer

Cycle REQ A is generated on the falling edge of the EOC from the A/D. It is a .5  $\mu$ sec pulse and is generated by a one shot (Fig. 5).

DATA IN LINES  $0 \rightarrow 13$  can either contain the data from the various channels or the final count of the CSC. These are selected by function 1 (Fig. 5).

STATUS B&C. These inputs come from the filter banks and by a switch closure select the parallel or serial mode of operation.

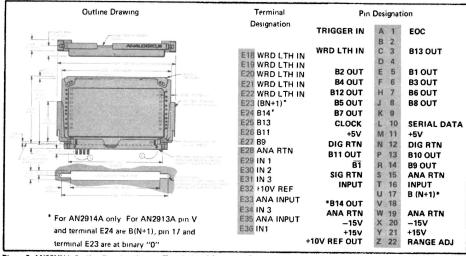

# 4.5 A/D Converter

The A/D converter is an Analogic MP2914A (Fig. 5). It has 14 bit output with 10  $\mu$ sec conversion time. The MSB is Bit 1 and LSB is Bit 14. The input to the A/D is buffered by an Analog Devices SHA-2A Sample Hold Amplifier. To insure that the input to the A/D does not change during the conversion of data the SHA-2A is put into the hold mode before the A/D starts conversion.

## Input to A/D

The input to the A/D can come from two sources - computer or integrators. When the input comes from the integrators Funct 2 is in a "Hi" state. This means that normal data transfer between the computer and multiplexer is taking place. When Funct 2 is low

-8-

a calibration output from the computer can be fed into the A/D to check its calibration. The cal voltage input must be positive.

# Calibration of A/D

Refer to the enclosed data sheet on the MP2914A.

# Logic Inputs & Outputs A/D

The trigger input to the A/D is generated by the readout or the end of cycle from the computer. The A/D trigger is a 4  $\mu$ sec positive pulse and conversion takes place on the NEGATIVE edge of this pulse. The trigger also generates the mode control for the SHA-2A.

## End\_of Cycle from A/D (EOC)

This is a 10  $\mu$ sec pulse that goes positive during conversion and negative when conversion is finished. The EOC pulse is used to advance the CSC and send a request A to the computer and clocks the mode control F/F for the SHA-2A.

# 5.0 Front Panel Meter Circuit

The input of the A/D is buffered and this signal is the input to the meter circuit (Fig. 5).

A CAG 30 is used to control this input and is only closed when in manual mode. The LH 0043 is a sample Hold module and its hold mode is controlled by readout. When in readout the input is sampled. The input to the meter circuit is also connected to an isolated BNC on the front panel.

The gain of the meter circuit can be varied by a switch on the front panel. The ranges are 20 mV, 200 mV, 2V, 20V full scale.

# 6.0 Power Supplies

The multiplexer requires  $\pm 15$  volts at 2.5 amps and  $\pm 5V$  at 3 amps. The power supplies are mounted in a separate chassis with current and voltage metering as shown in Figure 6.

# 7.0 Constructional Details

A total of 36 cards are used in the multiplexer, 32 integrator boards, 3 wirewrap logic boards and one A/D printed circuit board.

The chassis used to house these boards was designed by Arthur Shalloway and Gene Runion and was found to be ideal for this purpose.

A specially designed power plane distributes power to the board connectors. Wirewrap connectors are used throughout. Moulded plastic card guides and a simple constructional technique make the chassis inexpensive and simple to produce. Two large quiet fans insure adequate air flow over the circuit boards.

Connections are made to the filter receivers via four 140 pin Elco connectors and two 56 pin Elco connectors are used for the computer interface. BNC connectors are used for connections to the standard receiver and front end.

DWG NO C2579S

# Preliminary Data, January 1972

DG200

# MILITARY (A SUFFIX) -55 to +125°C INDUSTRIAL (B SUFFIX) -20 to +85°C

Type Package DG200AA TO-100 DG200BA TO-100

**DUAL SPST CMOS** ANALOG TRANSMISSION GATE

# MONOLITHIC CMOS SWITCH WITH DRIVER

- +15 V Analog Signal Range

- +15 V Supplies

- r<sub>DS</sub> < 100 Ohms Over Full Temperature and Signal Range

- Break-Before-Make Switching Action

- TTL, DTL, and CMOS Direct Control Interface Over Military Temperature Range Without Need For Interface Components

## **ABSOLUTE MAXIMUM RATINGS**

| Vs or VD to V1       0, -32 V         Vs or VD to V2       0, 32 V         Vs or VD to V2       0, 32 V         V1 to Ground       16 V         V2 to Ground       -16 V         Current, Any Terminal Except S or D       30 mA         Current, S or D       5 mA         Operating Temperature       -55 to 125°C         Storage Temperature       -65 to 150°C | $V_{IN}$ and $V_{Ref}$ to Ground | -0.3 V. V1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|

| Vs or VD to V2       0, 32 V         V1 to Ground       16 V         V2 to Ground       -16 V         Current, Any Terminal Except S or D       30 mA         Current, S or D       5 mA         Operating Temperature       -55 to 125°C                                                                                                                           | Vs or VD to V1                   |            |

| V1 to Ground         16 V           V2 to Ground         -16 V           Current, Any Terminal Except S or D         30 mA           Current, S or D         5 mA           Operating Temperature         -55 to 122°C                                                                                                                                              | Vs or Vp to V2                   |            |

| V2 to Ground         -16 V           Current, Any Terminal Except S or D         30 mA           Current, S or D         5 mA           Operating Temperature         -55 to 125°C                                                                                                                                                                                  | V <sub>1</sub> to Ground         | 16 V       |

| Current, Any Terminal Except S or D         30 mA           Current, S or D         5 mA           Operating Temperature         -55 to 125°C                                                                                                                                                                                                                       |                                  |            |

| Current, S or D                                                                                                                                                                                                                                                                                                                                                     |                                  |            |

| Operating Temperature                                                                                                                                                                                                                                                                                                                                               | Current, S or D                  | 5 mA-      |

|                                                                                                                                                                                                                                                                                                                                                                     |                                  |            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                  |            |

| Power Dissipation (Package)*                                                                                                                                                                                                                                                                                                                                        |                                  |            |

\*All leads welded or soldered to PC board. Derate 6 mW/°C above 75°C.

# **ELECTRICAL CHARACTERISTICS**

|    |                |                        | teristic Typ<br>25°C |      |         | Max I | imits |         |       | Tes                                        | t Conditions                                               |                                                |  |

|----|----------------|------------------------|----------------------|------|---------|-------|-------|---------|-------|--------------------------------------------|------------------------------------------------------------|------------------------------------------------|--|

|    | Characteristic |                        |                      |      | DG200AA |       |       | DG200BA |       | Init                                       |                                                            | Otherwise Noted)                               |  |

|    |                |                        | -55°C                | 25°C | 125°C   | -20°C | 25°C  | 85°C    |       | v <sub>1</sub> - 15 v, v <sub>2</sub> - 15 | , Gnd = 0, V Ref = Open***                                 |                                                |  |

| 1  | I              |                        |                      |      | -0.01   | -10   |       | -0.01   | -10   |                                            | V <sub>IN</sub> = 2 V                                      |                                                |  |

| 2  | N<br>P         | <sup>I</sup> าทท       |                      |      | 0.01    | 10    |       | 0.01    | 10    | ] [                                        | V <sub>IN</sub> = 15 V                                     |                                                |  |

| 3  | i<br>T         | I<br>IN(Peak)          | -120                 |      |         |       |       | 1       |       | μA                                         |                                                            |                                                |  |

| 4  |                | INL.                   |                      |      | -0.01   | - 10  |       | -0.01   | -10   | ] [                                        | V <sub>1N</sub> = 0,8 V                                    |                                                |  |

| 5  |                |                        | 65                   | 70   | 70      | 100   | 80    | 80      | 100   | Ω                                          | V <sub>D</sub> = 10 V                                      |                                                |  |

| 6  |                | DS(ON)                 | 85                   | 70   | 70      | 100   | 80    | 80      | 100   | "[                                         | $V_{\rm D} = -10 \text{ V}$                                | V <sub>IN</sub> = 0.8 V, I <sub>S</sub> = 1 mA |  |

| 7  | 0<br>l         | ,                      | 0.1                  |      | 2       | 1000  |       | 5       | 500   |                                            | V <sub>S</sub> = 15 V, V <sub>D</sub> = -15 V              |                                                |  |

| 8  | T              | IS(OFF)                | -0, 1                |      | -2      | -1000 |       | - 5     | - 500 |                                            | $v_{g} = -15 V, v_{p} = 15 V$                              | v <sub>IN</sub> = 2 v                          |  |

| 9  | r<br>L<br>T    |                        | 0,1                  |      | 2       | 1000  |       | 5       | 500   |                                            | $v_{\rm D} = 15 \text{ V}, v_{\rm S} = -15 \text{ V}$      |                                                |  |

| 10 | •              | D(OFF)                 | -0.1                 |      | -2      | ~1000 |       | - 5     | -500  | ~ ~ (                                      | $v_{\rm D} = -15 \text{ V}, v_{\rm S} = 15 \text{ V}$      |                                                |  |

| 11 |                | L                      | 0.1                  |      | 2       | 1000  |       | 5       | 500   | {                                          | V <sub>D</sub> = V <sub>S</sub> = 15 V                     |                                                |  |

| 12 |                | <sup>1</sup> D(ON)*    | -0.1                 |      | -2      | -1000 |       | -5      | -500  |                                            | $v_{\rm D} = v_{\rm S} = -15 \text{ V}$                    | V <sub>IN</sub> = 0.8 V                        |  |

| 13 |                | 1,                     | 2.5                  |      | з       |       |       | 3       |       |                                            | Both Channels : ONE . V                                    | •                                              |  |

| 14 | P<br>O         | 12                     | -2.5                 |      | -3      |       |       | -3      |       | m∧                                         | Both Channels 'ON', V =                                    | v                                              |  |

| 15 | E              | 1 <sub>1</sub> Standby | 1.7                  |      | 2       |       |       | 2       |       | 1121                                       |                                                            |                                                |  |

| 18 | R              | I <sub>2</sub> Standby | -1.7                 |      | -2      |       |       | -2      |       |                                            | Both Channels OFF', V <sub>1N</sub>                        | N <sup>* 5 V</sup>                             |  |

| 17 |                | ton                    | 400                  |      | 1000    |       |       | 1000    |       |                                            | · · · · · · · · · · · · · · · · · · ·                      |                                                |  |

| 18 |                | toff                   | 230                  |      | 500     |       |       | 500     |       | ns                                         | See Switching Circuit                                      |                                                |  |

| 19 | PY             | C <sub>S(OFF)</sub>    | 8,5                  |      |         |       |       |         |       |                                            | $v_{\rm S} = 0, v_{\rm IN} = 5 v$                          |                                                |  |

| 20 | N A            | CD(OFF)                | 8.5                  |      |         |       |       |         |       |                                            | VD= 0, 1N - 31                                             |                                                |  |

| 21 | M<br>1<br>C    | C <sub>ds(off)</sub>   | 1                    | -    |         |       |       |         |       | pF                                         | $V_{D} = V_{S} = 0, V_{IN} = 5 V$                          | f = 140 kHz to 1 MHz                           |  |

| 22 | Ĩ              | CD(ON)                 | 22                   |      |         |       |       |         |       |                                            | V <sub>D</sub> = V <sub>S</sub> = 0, V <sub>1N</sub> = 0 V |                                                |  |

| 23 |                | OFF<br>Isolation**     | 65                   |      |         |       |       |         |       | dB                                         | $V_{1N} = 5 V, R_1 = 1 k\Omega, C_1$                       | 10 pF, V <sub>S</sub> - 3 VRMS, f = 1          |  |

\*\* OFF V.

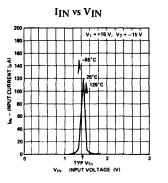

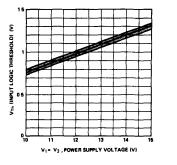

Functional operation is possible for  $10 \le \sqrt{pp}$  (and  $\sqrt{s}, 1 \le 13 \sqrt{s}$ ), but the input logic threshold will shift To maintain TTI threshold voltage compatibility a reference voltage of  $1.5 \sqrt{s}$  in the applied to the  $\sqrt{tep}$  terminal. The  $\sqrt{tep}$  terminal has  $\sqrt{tep}$  terminal has  $\sqrt{tep}$  terminal has  $\sqrt{tep}$  terminal.

A = output terminal of 'OFF' switch, B = any other switch terminal.

# DG200

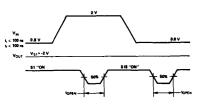

# SWITCHING CIRCUIT AND DEFINITIONS

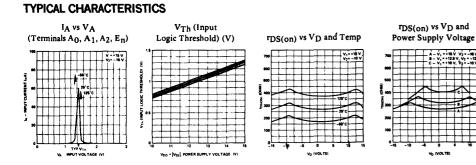

# TYPICAL CHARACTERISTICS

VTh (Input Logic Threshold) vs Power Supply Voltage

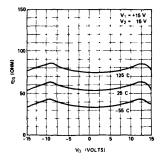

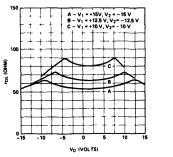

## rDS vs VD and Temp

rDS vs VD and Power Supply Voltage

DG200

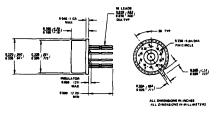

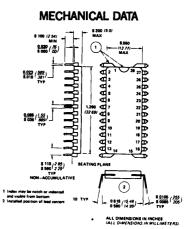

**MECHANICAL DATA**

TO-100 DG200AA, BA

Specifications subject to change without notice

Siliconix incorporated

## Preliminary Data, January 1972

DG506

# MILITARY (A SUFFIX) -55 to +125°C INDUSTRIAL (B SUFFIX) -20 to +85°C

Package Type DG506AB MO-013 DG506BR MO-015

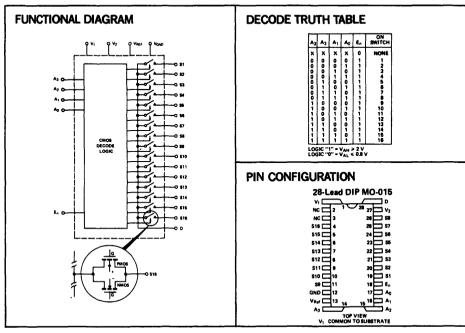

# MONOLITHIC CMOS MULTIPLEXER WITH 4-LINE BINARY DECODE

- +15 V Analog Signal Range

- row < 500 Ohms Over Full Temperature and Signal Range

- Break-Before-Make Switching Action

- TTL, DTL, and CMOS Direct Control Interface Over Military Temperature Range Without Need For Interface Comnonente

- 4-Line Binary Input Selects 1 of 16 Channels

- 5th Line Binary Imput (En) Allows Output Line To Be Common To Several Other Units

- 36 mW Typical Standby Power

The DG506 is a single-pole 16-position (plus OFF) electronic switch array which employs 16 pairs of complementary MOS (CMOS) field-effect transistors designed to function as analog switches. In the ON condition each switch will conduct current in either direction, and in the OFF condition each switch will block voltages up to 30 V peak-to-peak. The ON-OFF state of each switch is controlled by drivers, which are in turn controlled by a 4-bit binary word input plus an Enable-Inhibit input. The truth table below shows the binary word required to select any one of the 16 switch positions, provided a positive logic "1" is present at the Enable input. With logic "0" at the Enable input all switches will be OFF. The logic decoder and the Enable inputs will recognize voltages between -0.3 and 0.8 V as logic "0" voltages, and voltages between 2 and 15 V as logic "1" voltages. The input can thus be directly interfaced with TTL, DTL, RTL, CMOS, and certain special P-MOS circuits. Switch action is break-before-make.

# **16-CHANNEL ANALOG MULTIPLEXER** COMPLEMENTARY MOS (CMOS)

# DG506

## ABSOLUTE MAXIMUM RATINGS

| VIN (A, En, or VRef) to Ground                                                                                                                          | -0. 3   | v, v <sub>1</sub> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|

| Vs or VD to V1                                                                                                                                          | . 0,    | -32 V             |

| $V_S \text{ or } V_D \text{ to } V_2 \dots \dots$ | . 0,    | 32 V              |

| V1 to Ground                                                                                                                                            |         | 16 V              |

| V2 to Ground                                                                                                                                            | • • • • | -16 V             |

| Current (Any Terminal, Except Analog Source/Drs                                                                                                         | ıin) .  | 30 mA             |

| Current (Analog Drain)                                                                                                                                  |         | 10 mA             |

| Current (Analog Source) 1         | i mA |

|-----------------------------------|------|

| Operating Temperature             | 25°C |

| Storage Temperature               | 50°C |

| Power Dissipation (Package)* 1200 | mW   |

\*All leads soldered or welded to PC board. Derate 10 mW/°C shove 70°C

ICAB-4

# **ELECTRICAL CHARACTERISTICS**

All DC parameters are 100% tested at 25°C. Lots are sample-tested for AC parameters and high and low temperature limits to assure conformance with specifications.

|             | _        |                      |                                   | No           |             |       | · · · ·     | Max          | Limite |             |             |            | Test Conditions (Unless Otherwise Noted)                               |                                                                         |  |

|-------------|----------|----------------------|-----------------------------------|--------------|-------------|-------|-------------|--------------|--------|-------------|-------------|------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

|             |          | Characteristic       | Measured                          | Teste<br>Per | Тур<br>20°С |       | A Suffix    |              |        | B Suffix    |             | Unit       |                                                                        | <pre>0 V, Ground = 0, V<sub>Ref</sub> = Open<sup>000</sup></pre>        |  |

|             | <b>.</b> |                      |                                   | Temp         |             | -55°C | 20°C        | 120°C        | -20°C  | 85°C        | 55°C        |            | 1                                                                      | Ref                                                                     |  |

|             | 1        | <sup>r</sup> ds(ON)  | S to D                            | 10           | 250         | 400   | 400         | 500          | 450    | 450         | 580         | n          | V <sub>D</sub> = 10 V, I <sub>g</sub> =-100 μA                         | Sequence each switch on                                                 |  |

|             | 2        |                      |                                   | 10           | 250         | 400   | 400         | 500          | 450    | 450         | 550         |            | V <sub>D</sub> = -10 V, I <sub>S</sub> =-100 μA                        | V <sub>AL</sub> = 0.5 V, V <sub>AH</sub> = 2 V                          |  |

|             | 3        | AT DS(ON)            |                                   |              | 20          |       |             |              |        |             |             | ą.         | $\Delta r_{D6(ON)} = \left(\frac{r_{D6(ON) MAX}}{r_{D6(O)}}\right)$    | $\frac{1}{1000} \frac{r_{DS(ON) MIN}}{r_{OAVE}}, -10V \le V_{S} \le 10$ |  |

| W           | 4        | ].                   | 8                                 | 10           | -0, 00      |       | ±1          | <u>+</u> 50  |        | <u>+</u> 5  | <u>+</u> 50 |            | V <sub>S</sub> = 10 V, V <sub>D</sub> = -10 V                          |                                                                         |  |

| Ť           | 8        | <sup>1</sup> 5(OFF)  |                                   | 10           | -0, 00      |       | ±1          | ±50          |        | ±5          | <u>+</u> 50 |            | V <sub>S</sub> = -10 V, V <sub>D</sub> = 10 V                          | v - •                                                                   |  |

| н           | •        |                      | D                                 | 1            | -0, 3       |       | ±10         | ±500         |        | <u>+</u> 20 | ±500        |            | V <sub>D</sub> = 10 V, V <sub>S</sub> = -10 V                          | V <sub>En</sub> = 0                                                     |  |

|             | 7        | <sup>I</sup> D(OFF)  | 5                                 | 1            | -0,3        |       | ±10         | <u>+</u> 500 |        | <u>+</u> 20 | ±500        |            | V <sub>D</sub> = -10 V, V <sub>S</sub> = 10 V                          |                                                                         |  |

|             | •        | ],,,                 | D                                 | 10           | -0, 3       |       | ±10         | ±800         |        | <u>+</u> 20 | ±500        | 1          | V <sub>S(All)</sub> = V <sub>D</sub> = 10 V                            | Sequence each switch on                                                 |  |

|             | •        | (MO)                 | 5                                 | 16           | -0,2        |       | <u>+</u> 10 | ±500         |        | <u>+</u> 20 | ±500        |            | V <sub>S(All)</sub> = V <sub>D</sub> = -10 V                           | V <sub>AL</sub> = 0.0 V, V <sub>AH</sub> = 2 V                          |  |

|             | 10       | ,                    | A <sub>0</sub> , A <sub>1</sub> , | 0            |             |       | -10         | -30          |        | -10         | -30         |            | V <sub>A</sub> = 2,4 V                                                 |                                                                         |  |

|             | 11       | IAH                  | A2. A3.                           | 0            |             |       | 10          | 30           |        | 10          | 30          | 1          | V <sub>A</sub> = 15 V<br>See Curve "I <sub>A</sub> vs V <sub>A</sub> " |                                                                         |  |

| I N         | 12       | 1 <sub>A(Peak)</sub> | En                                | 0            | -60         |       |             |              |        |             |             |            |                                                                        |                                                                         |  |

| P<br>U<br>T | 13       | 1 <sub>AL</sub>      | ^0. ^1.<br>^2. ^3                 | 4            |             |       | -10         | -30          |        | -10         | -30         | <b>A</b> 4 | V <sub>En</sub> = 2 V                                                  | All V_ = 0                                                              |  |

|             | 14       |                      | En                                | 1            |             |       | -10         | -30          |        | -10         | -30         | 1          | V <sub>En</sub> = 0                                                    | <b>∧</b>                                                                |  |

|             | 15       | t rensition          | D                                 |              | 0.6         |       | 1           |              |        |             |             |            | See Fig. 1                                                             |                                                                         |  |

|             | 10       | topen                | D                                 |              | 0, 2        |       |             |              |        |             |             |            | See Fig. 2                                                             |                                                                         |  |

| DY          | 17       | <sup>t</sup> on(En)  | D                                 |              | 0,8         |       | 1.0         |              |        |             |             | щe         | A., m. A                                                               |                                                                         |  |

| Ń           | 10       | <sup>t</sup> off(En) | D                                 |              | 0, 3        |       | 1           |              |        |             |             | 1          | See Fig. 3                                                             |                                                                         |  |

| Ŵ           | 19       | "OFF" Isolation**    | D                                 |              | 00          |       |             |              |        |             |             | dB         | V <sub>En</sub> = 0, R <sub>L</sub> = 200 Ω, C <sub>L</sub> = :        | 9 pF, V <sub>S</sub> = 3 VRMS, I = 500 kHz                              |  |

| ċ           | 20       | C <sub>S(OFF)</sub>  | 8                                 | 10           | 8           |       |             |              |        |             |             |            | V <sub>8</sub> =0                                                      |                                                                         |  |

|             | - 21     | CD(OFF)              | D                                 | 1            | 40          |       |             |              |        |             | -           | pF         | V <sub>D</sub> = 0                                                     | V <sub>En</sub> = 0, f = 140 kHz to 1 MH                                |  |

|             | 22       |                      | D to S                            | 10           | 1           |       |             |              |        |             |             |            | v <sub>s</sub> = 0, v <sub>p</sub> = 0                                 |                                                                         |  |

| 8           | 23       | 11                   | v <sub>1</sub>                    | 1            | 0, 2        | 14    | 10          | 7            |        | 10          |             |            | ¥ - •¥                                                                 |                                                                         |  |

| P           | 24       | 12                   | v <sub>3</sub>                    | 1            | -0, 2       | -14   | -10         | -1           |        | -10         |             | 1          | V <sub>En</sub> = 0 V                                                  |                                                                         |  |

| PL          | 25       | I Standby            | v <sub>1</sub>                    | 1            | 1.2         | 3.0   | 2,5         | 3            |        | 2.0         |             | mA         |                                                                        | A)1 V <sub>A</sub> = 0                                                  |  |

| VI Y        | 26       | I Standby            | V <sub>2</sub>                    | 1            | -1, 2       | -3,0  | -2.0        | -2           | [      | -2,0        | · · · ·     | 1          | v <sub>En</sub> -o                                                     |                                                                         |  |

#### 5

\*"OFF" leolation \$ 20 log input to "OFF" switch, V = output due to Ver

l operation is possible for supply voltages less than 15 V, but the input logic threshold will shift, For V1 = - V3 = 10 V, 1.5 V may be applied to the Vnot terminal. The Vnot terminal has RIN #13 KO.

DG506

**DG506**

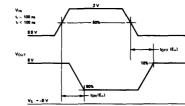

# SWITCHING INFORMATION

Figure 1

Figure 2

MO-015 28-Pin Dual-In-Line Package DG506AR, BR

Specifications subject to change without notice

# Siliconix incorporated

## GENERAL DESCRIPTION

Analogic's MP2913A and MP2914A are the fastest 13 and 14 hit analog-to-digital converters available at lowest cost in the smallest package. Housed in a  $2'' \times 4'' \times 0.4''$  MODUPAC <sup>TM</sup>, these extremely fast and highly precise ADC's (10 microseconds for 14 bits) provide substantial space and cost economies in high speed-high resolution digitizing systems. The high accuracy and differential linearity (.006%) plus the high stability (gain tempco is 7 PPM/°C and differential linearity tempco is 3 PPM/<sup>O</sup>C) of these units assure true 13 and 14 bit resolution

## PERFORMANCE ACHIEVEMENTS

The high digitizing rate of 100,000 conversions per second with an accuracy and differential linearity of 006% of the MP2913A and MP2914A is achieved by incorporating three separate ground planes and a unique stroping comparator. While accelerating the conversion process, these design innovations virtually eliminate major electrical interferences thus minimizing noise. Implementing these and similar techniques with the optimum components available assures that the MP2913A and MP2914A have the high accuracy and linearity consistent with high speed 14 bit conversion.

Combining the MP2914A with Analogic's AN4716 Multiplexer and MP270 Sample and Hold modules will provide analog-to-digital conversions of more than 75,000 per second.

Figure 1. MP2914A Functional Block Diagram

# FEATURES

- Extremely Fast Conversion to 14 bits

- Highly Accurate and Linear.... ----within 006%

- Highly Stable... -----3 PPM/°C Differential Linearity Tempco

- Small Shielded Module...

- Low Cost

#### APPLICATIONS

- · Fast thru-put Systems

- High Speed Computer Interfacing

- · Wide Band Data Digitizing

- Multi-channel Process Control

Audubon Road

Wakefield, Massachusetts 01880 Tel (617) 246-0300 TWX (710) 348-0425

MP2913A & MP2914A SPECIFICATIONS ANALOG INDUT Input Voltage / Full Seals Danas 10V to +10V 0V to +10V 5V to +5V OV to +5V (pin selectable. See Fig. 5) Depends on ESB. See Fig. 5 Input Impedance ACCURACY I @ 220CL Absolute Accurac Same as relative accuracy after calibration Delative Accuracy 0000 500 Differential Linearity 006% ESP Quantizing Erro ±1/2 LSB Reference Maire 005% ESP P.P. referred to input Guaranteer STABILITY Tempoo of Differential Linewith C+3 00M/00 ESP Tempco of Gain Tempco of Offset <17 PPM/<sup>O</sup>C Readin Clock Stability ±0.1%°C Pourst Cumply Constituit ±0.0012% change in supply voltage **Becalibration Interval** 6 months Repeatibility Defined by Noise and Accuracy CONVERSION TIME 10usec Total Conversion DIGITAL SIGNALS Compatibility Standard TTL Compatible Parallel Output Binary B1 B1 to B12 or B14 2 weit loads/line Serial Output Negative pulses simultaneous with clock pulse for "0". Max load 30pF Trioner Innut '1" for 1 usec min. Trigger Input Transiti <200 risec (90% to 10%) "1" to "O" level transition, End of Conversion FOC after LSB data pulse. 9 unit loads FOC Transit <20 nsec (10% to 90%) Clock Output Standard TTL compatibl Clock Output External C 30 oF ectable Word Length POWER SUPPLY +15V +3% 60mA -15V ±3% 60mA +5V ±5% 300mA ENVIRONMENTAL, PHYSICAL, & RELIABILITY Maximum Input Without Damage ±200% Full Scale Range Missing Codes None Warm-up Time to Stated Accuracy 5 minutes Operating Temperature  $0^{\circ}$ C to +70°C Storage Tempera -25°C to +85°C Relative Humidity 5% to 95% (non-co

# Neg. going pulse from binary "1", 50 nsec min. duration at binary "0", must have been at binary ninally 100 nsec 30 pF maximum allowable 2 to 13 bits (MP2913A), 2 to 14 bits (MP2914A)

Electrical Shielding RFI 6 sides: EMI 5 sides Machanical Protect 6 sides Packaging MP29XXA 2" x 4" x 0 39" Modupa Packaging AN29XXA MP29XXA on plug in P.C. card

# **Binary Output Coding**

The particular output binary code desired can be selected in accordance with the accompanying table. \*

| 14 BIT RESOLUTION                                                                                                     | 13 BIT RESOLUTION                                                                                                  |                                             |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Unipolar binary :                                                                                                     | Unipolar binary :                                                                                                  |                                             |

| +9.9994V = 11 111 111 111 111 111<br>0.0000V = 00 000 000 000 000<br>Pin Label = B1, B2                               | +9.9988V = 1 111 111 111 111<br>0.0000V = 0 000 000 000 000<br>Pin Label = 81, 82                                  | میں دور |

| Offeet binary:                                                                                                        | Offset binary:                                                                                                     |                                             |

| +9.9988V = 11 111 111 111 111<br>0.0000V = 10 000 000 000 000<br>-10.0000V = 00 000 000 000 000<br>Pin Label = B1, B2 | +9.9976V = 1 111 111 111 111<br>0.0000V = 1 000 000 000 000<br>-10.0000V = 0 000 000 000 000<br>Pin Label = B1, B2 |                                             |

| Two's compliment* * :                                                                                                 | Two's complement** :                                                                                               | HOMOLEY SPORTA                              |

| +9.9988V = 01 111 111 111 111<br>0.0000V = 00 000 000 000 000<br>10 0000V = 10 000 000 000 000<br>Pin Label = 61, 82  | +9.9976V = 0 111 111 111 111<br>0.0000V = 0 000 000 000 000<br>-10.0000V = 1 000 000 000 000<br>Pin Label = B1, 82 | 25.233 -                                    |

| *10 volt unit only. For 5 volt units di                                                                               | vide input voltage by 2,                                                                                           | 170 30 5000                                 |

| ** To change to offset binary, use B1                                                                                 | instead of B1.                                                                                                     |                                             |

|                                         | THE ODINE PULS |                 |      |        | Æ           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------|----------------|-----------------|------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |                | <u>i u u u</u>  |      | ццг    | ny          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ove the                                 |                |                 | -1-  | PERNOS | <u> </u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         |                |                 |      |        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | 111            |                 | 11   |        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         |                |                 | 1    |        | #1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | n              |                 | 11   |        | H.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| a.11                                    | n              | int i           | TI   |        | Ŧ,          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| out                                     |                |                 |      |        | Π.          | PARABLES<br>OWNERS<br>BALA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2111                                    |                | n               | 말씀생활 |        | <b>H</b> .( | Participation of the second se |

|                                         | 1              | LIT             | 11   |        | Ξ.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |