## NATIONAL RADIO ASTRONOMY OBSERVATORY CHARLOTTESVILLE, VIRGINIA

CTRONICS DIVISION INTERNAL REPORT NO.

# ADIOS — ANALOG-DIGITAL INPUT OUTPUT SYSTEM FOR APPLE COMPUTER

## G. WEINREB AND S. WEINREB

April 1981

NUMBER OF COPIES: 150

## ADIOS - ANALOG-DIGITAL INPUT OUTPUT SYSTEM FOR APPLE COMPUTER

## TABLE FOR CONTENTS

Page

| I            | Introduction .  | • | • | • | • | • | • | • | •  | • | •  | • | • | • | • | •   | • . | • | • | • | • | • | • | • | • | • | • | • | 3  |

|--------------|-----------------|---|---|---|---|---|---|---|----|---|----|---|---|---|---|-----|-----|---|---|---|---|---|---|---|---|---|---|---|----|

| <b>II.</b> , | Synchronization |   | • | • | • | • | • | • | •  | • | •  | • | • | • |   | •   | •   | • | • | • | • | • | • | • | • |   | • | • | 9  |

| III.         | Analog Input .  | • | • | • | • | • | • | • | ·. | ٠ | .• | • | • | • | • | •   | •   | • | • | • | • | • | • | • | • |   |   | • | 11 |

| IV.          | Analog Output   | • | • | • | • | • | • | • | •  | • | •  | • | • | • | • | •   | •   | • | • | • |   | • | • |   |   |   |   | • | 14 |

| V.           | Digital Input   | • | • | • | • | • | • | • | •  | • | •  | • | • | • | • |     |     |   |   |   |   |   |   |   |   |   |   |   | 14 |

| VI.          | Digital Output  | • | • | • | • | • | • | • | •  | • | •  | • |   |   |   |     |     |   |   |   |   |   | • |   |   |   |   |   | 16 |

| VII.         | Calibration .   | • | • | • | • | • | • | • |    |   | •  |   | • |   | • | • 1 | •   | • | • | • | • | • | • | • |   |   |   |   | 17 |

|              |                 |   |   |   |   |   |   |   |    |   |    |   |   |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |    |

### APPENDICES

| Appendix 1 | Initialization Program - ADIOS INITB          | 0 |

|------------|-----------------------------------------------|---|

| Appendix 2 | Test Program - ADIOS TEST                     | 2 |

| Appendix 3 | AMD9513 Utilization                           | 5 |

| Appendix 4 | Logic Diagrams                                | 1 |

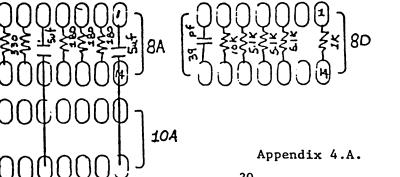

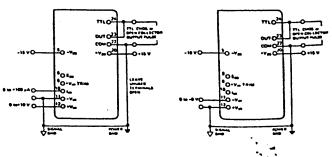

|            | A. Digital IC Location Guide                  | D |

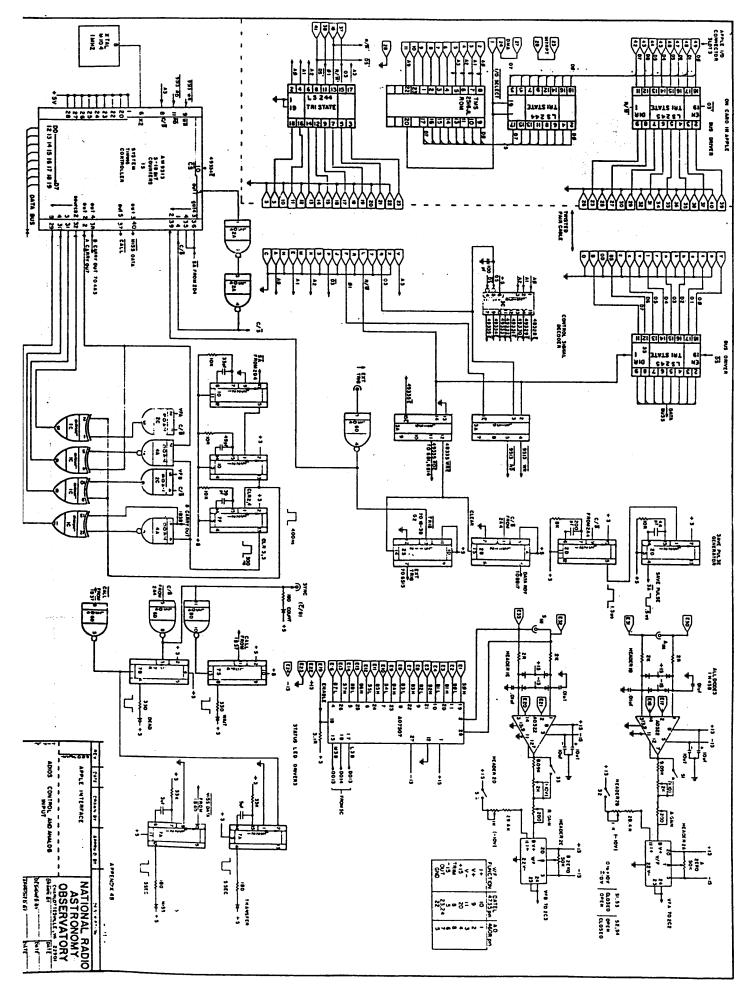

|            | B. ADIOS Control and Analog Input             | 1 |

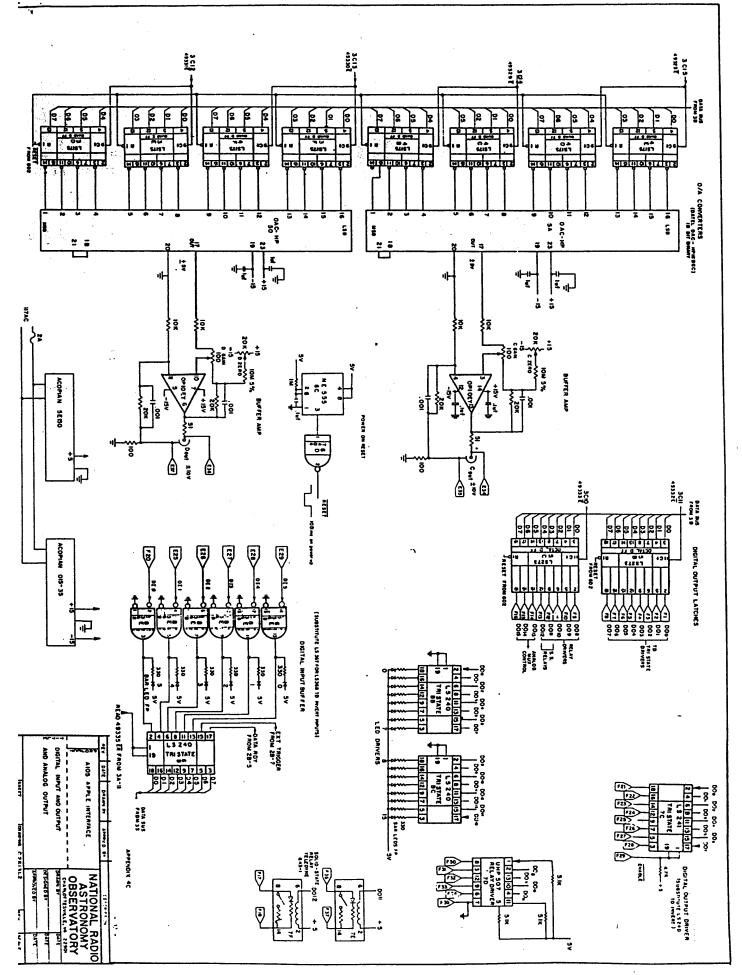

|            | C. Digital Input and Output and Analog Output | 2 |

| Appendix 5 | Manufacturers Data                            |   |

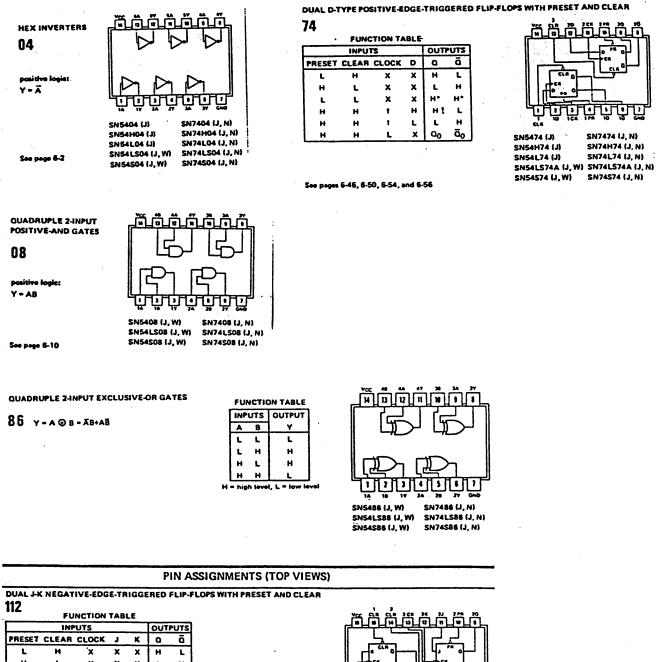

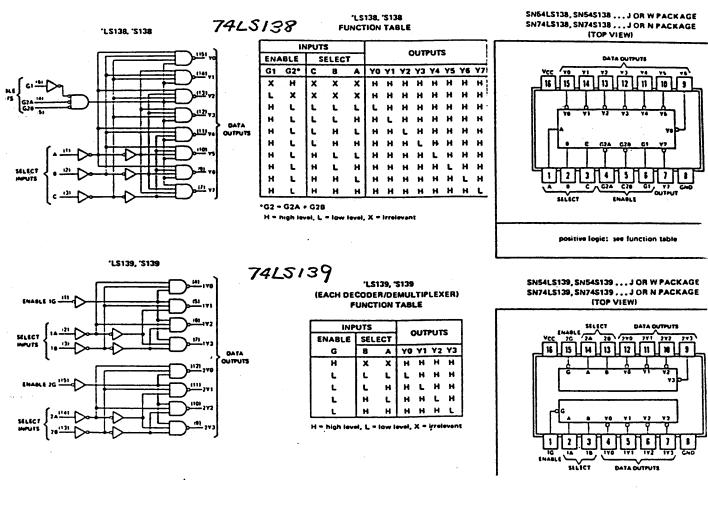

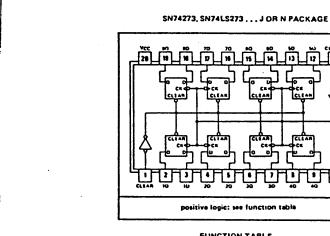

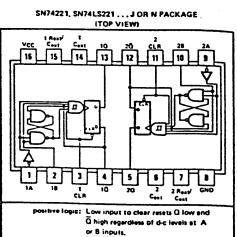

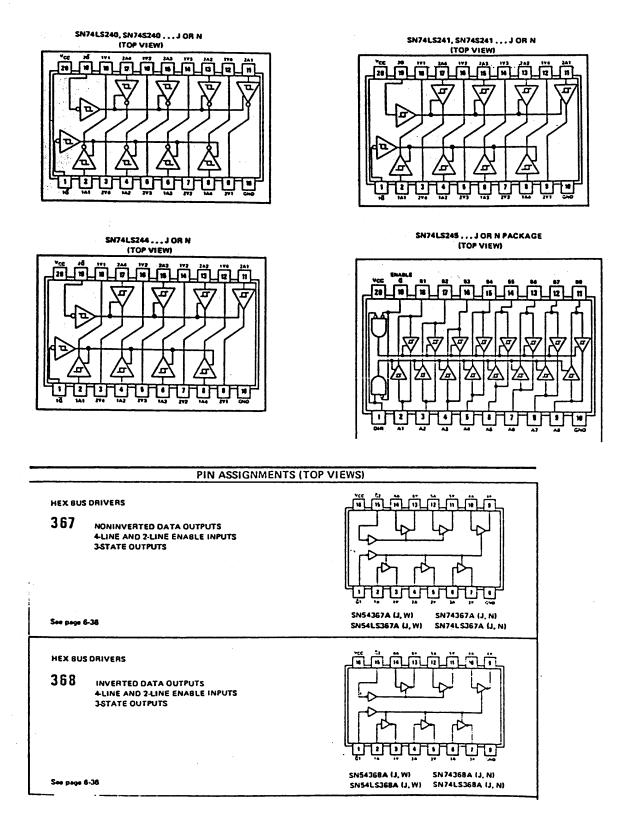

| •          | A. TTL IC Pin Layouts                         |   |

|            | B. Teledyne Philbrick 4735 V/F Converter      | 7 |

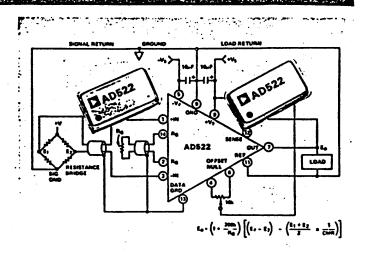

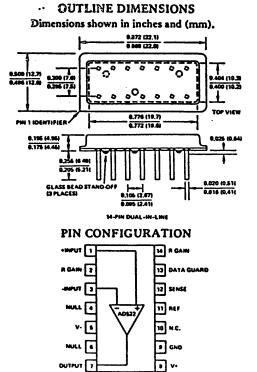

|            | C. Analog Devices AD522 Instrumentation Amp   |   |

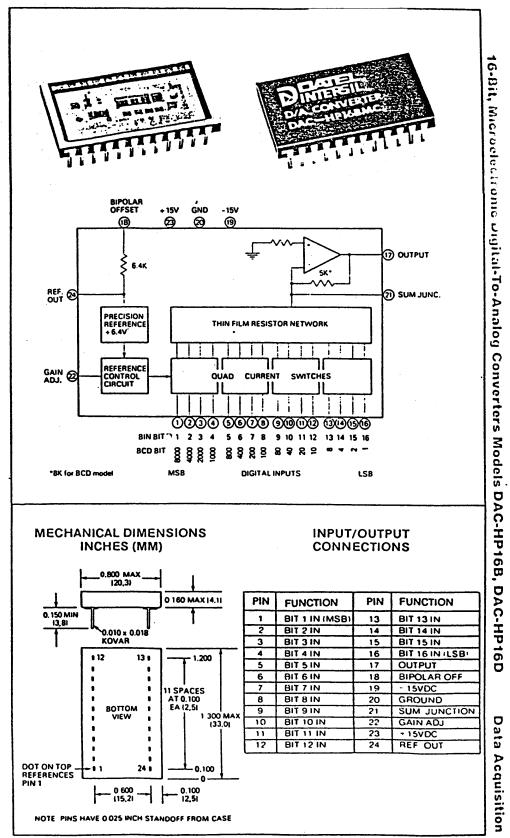

|            | D. Datel-Intersil DAC-HP16BGC                 |   |

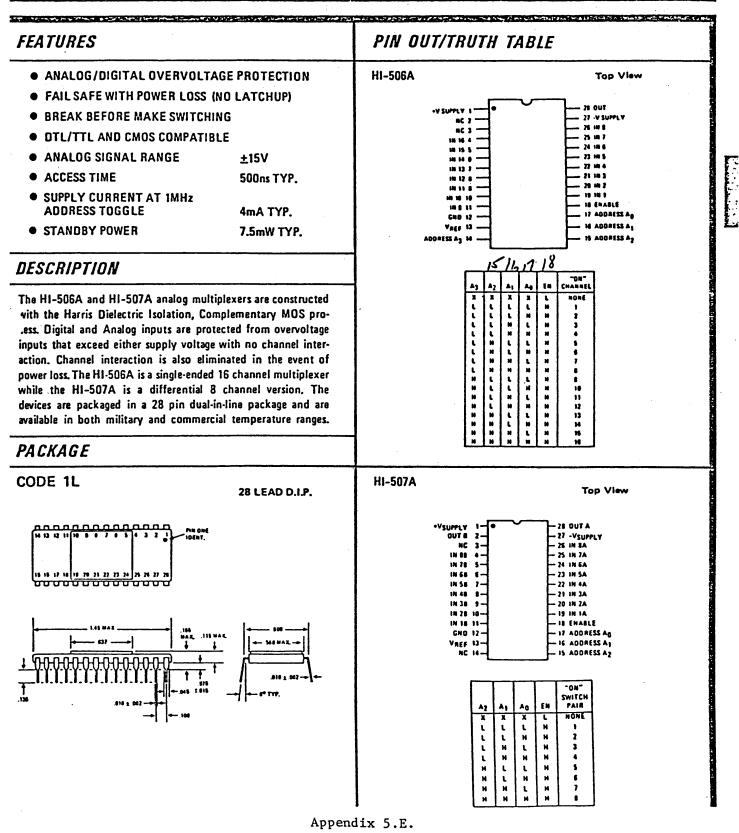

|            | E. Harris HI-506A Multiplexer                 | 7 |

|            | F. Sprague UHP-507 Relay Driver               |   |

|            | G. Teledyne Solid-State Relays                |   |

|            | H. Advanced Micro Devices AM9513 51           | 1 |

|            | I. Analog Devices 460K V/F Converter          | 6 |

## FIGURES

| Figure 1 | ADIOS Block Diagram                            |

|----------|------------------------------------------------|

| Figure 2 | ADIOS Module and Apple Card (Photograph)       |

| Figure 3 | Complete Apple/ADIOS System (Photograph) 6     |

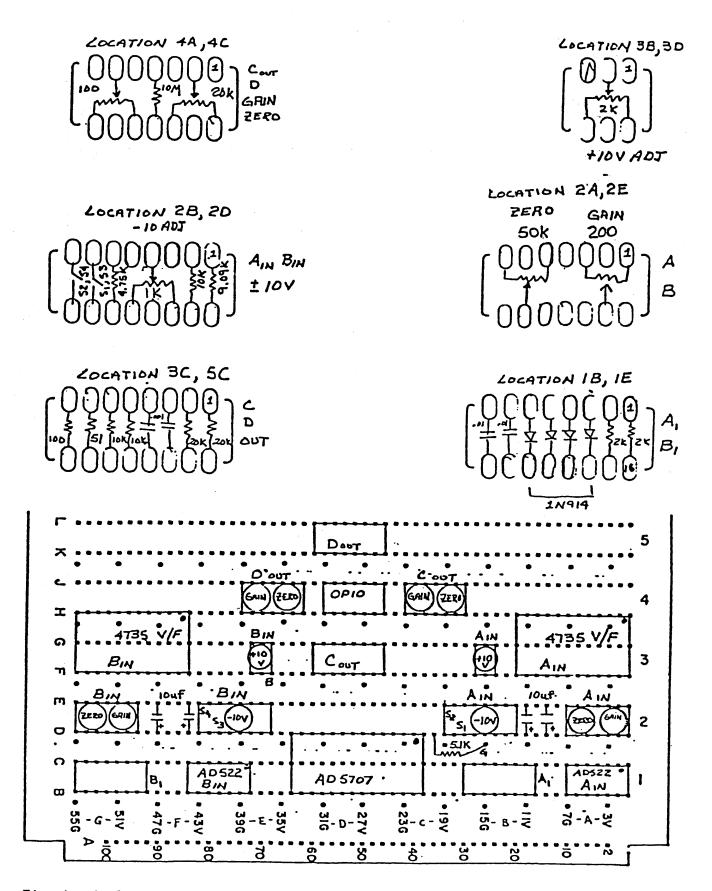

| Figure 4 | Analog Component Location                      |

| Figure 5 | ADIOS-INITB Assembly Listing                   |

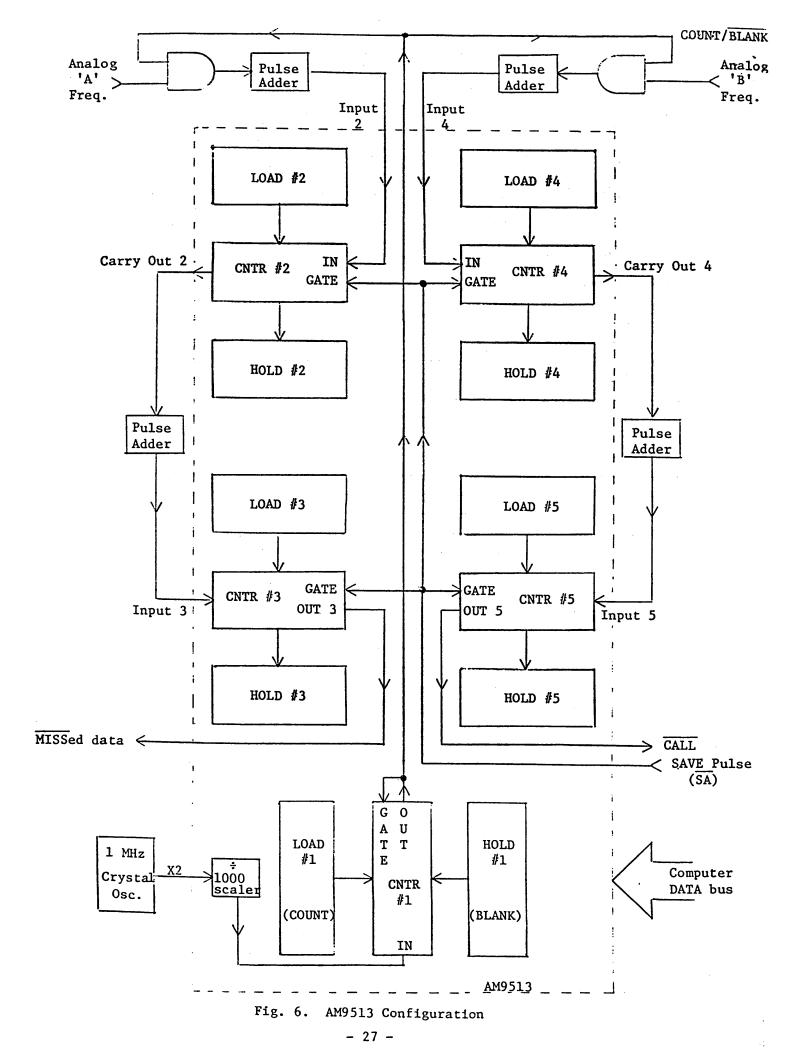

| Figure 6 | AM9513 Configuration                           |

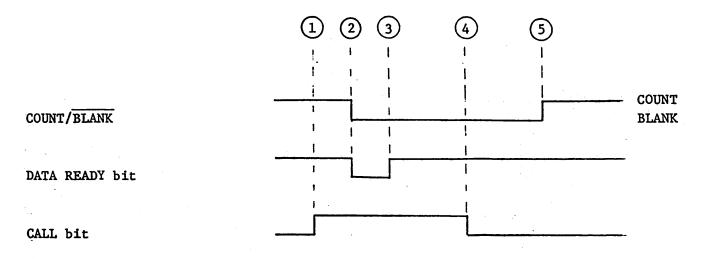

| Figure 7 | ADIOS-Apple Synchronization                    |

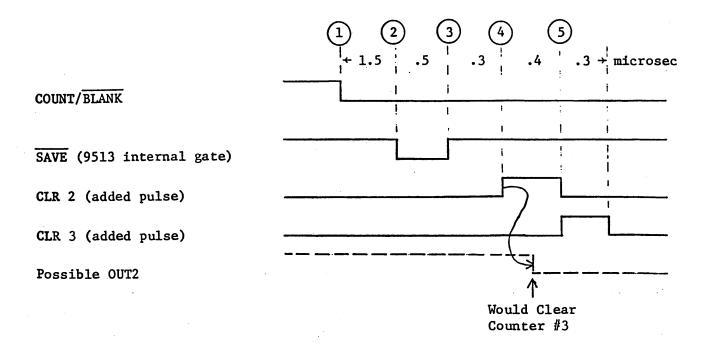

| Figure 8 | Timing Diagram of AM9513 Counting Operation 29 |

## TABLES

| Table | I | Apple/ADIOS Addresses                 | • | <br>• | • | • |  | • |  | 8 |

|-------|---|---------------------------------------|---|-------|---|---|--|---|--|---|

|       |   | Front-Panel Connector Pin Assignments |   |       |   |   |  |   |  |   |

|       |   | D/A Converter Code                    |   |       |   |   |  |   |  |   |

|       |   | ADIOS-INITB Initialization Addresses  |   |       |   |   |  |   |  |   |

## ADIOS - Analog-Digital Input Output System for Apple Computer

G. Weinreb and S. Weinreb

#### I. INTRODUCTION

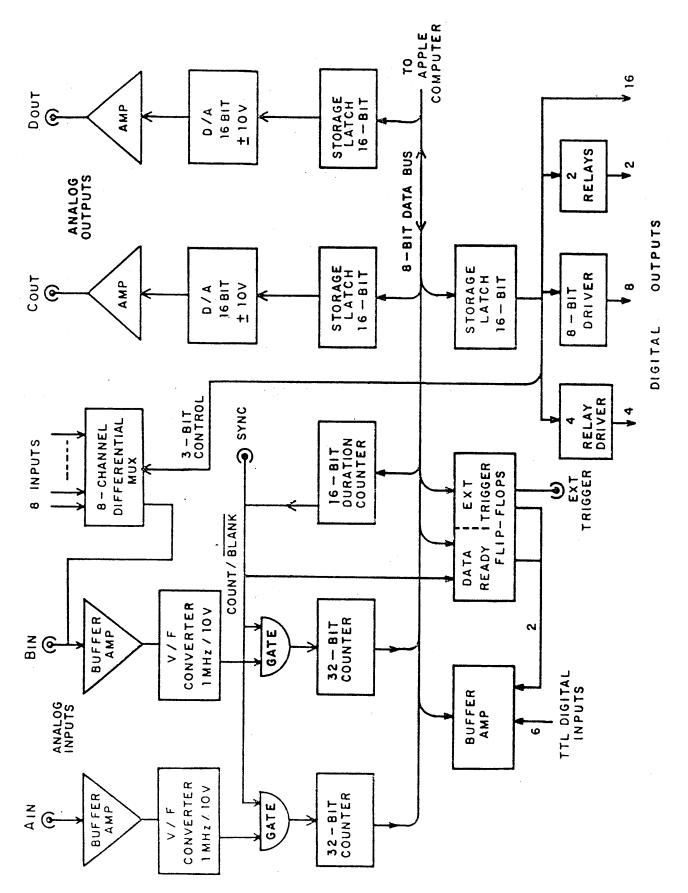

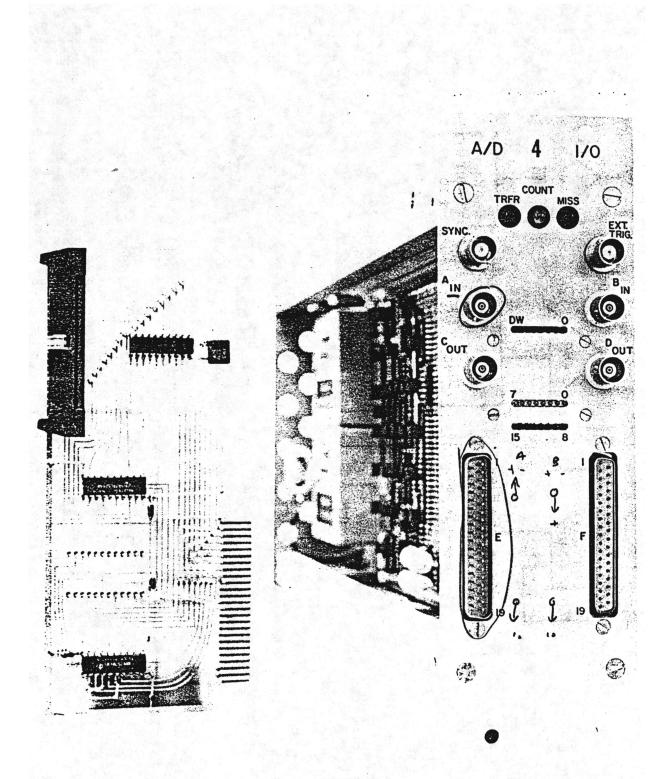

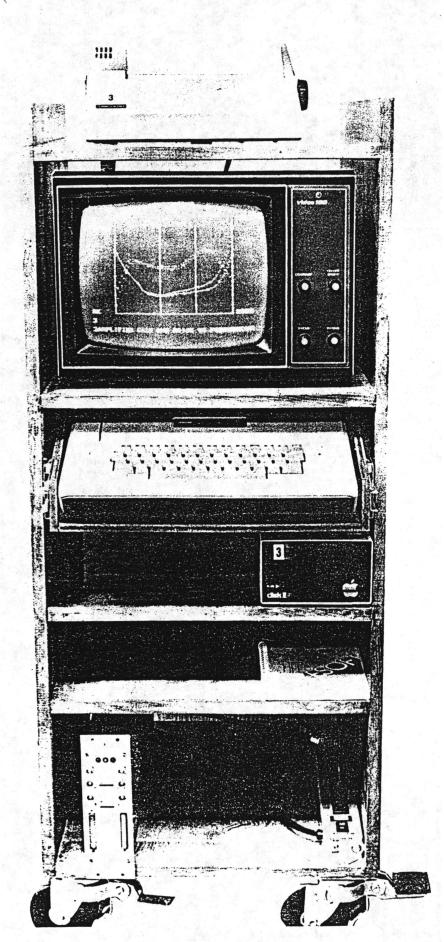

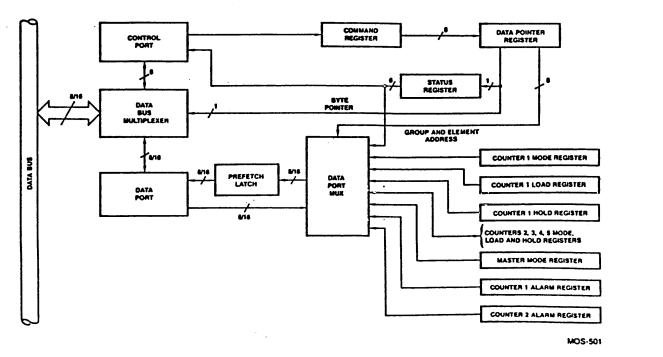

ADIOS is a general purpose analog and digital input and output system for use with the Apple II Plus computer; a block diagram of the system is shown in Figure 1 and photographs of the ADIOS hardware and a complete Apple laboratory computer system are shown in Figures 2 and 3.

The system provides two .01% accuracy analog inputs denoted as AIN and BIN, two 16-bit accuracy analog outputs denoted as COUT and DOUT, six 1-bit TTL logic level digital inputs, and a 16-bit digital output which can be routed through an 8-bit bus driver, a 4-bit relay driver, or two solid-state relays. Three of the digital output bits can be used to control an 8-channel multiplexer on the BIN analog input. The hardware and software aspects of these functions are discussed together for each analog and digital input and output in subsequent sections of this report.

The A/D conversion is a slow integration method rather than a fast sampling type of conversion; the intention is to achieve high precision by averaging of noisy inputs. The integration is performed by counting of voltage-to-frequency (V/F) pulses for a duration denoted as COUNT time which is software controllable. After each integration the V/F pulses are not counted for a duration denoted as BLANK time which is also software controllable. In normal operation the ADIOS output analog and digital variables change near the beginning of BLANK time and transients caused by the change of these variables should decay before the

- 3 -

Fig. 1. ADIOS Block Diagram

Fig. 2. ADIOS components - Apple I/O card and main module. The I/O card contains signal isolation drivers and a socket for a ROM containing future utility programs. Within the module are power supplies, V/F converters, counters, D/A converters, digital output drivers, and control logic.

Apple system on laboratory cart with ADIOS module on bc shelf. A typical measurement of noise and gain of a mi amplifier is displayed on the screen.

next COUNT time starts. The lower limits for COUNT and BLANK times are software dependent; practical limits are of the order of 100 milliseconds for a BASIC program. The maximum duration is approximately 65 seconds.

Before ADIOS can be used it must be initialized by a subroutine such as the machine language program, ADIOS INITB, described in Appendix 1. The initialization subroutine sets the values of COUNT and BLANK and also directs a programmable integrated circuit, the AM9513, which performs all counting, to the desired mode of operation. The subroutine is loaded from disk and executed with the following calling program:

319 REM NEXT INITILIZES A/D INTERFACE AND SETS UP INTEGRATION CYCLE 320 GOSUB 7000: REM POKE COPY OF ADIOS-INITB 330 REM BLOADED 85 = \$55 BYTES IN 7986 = \$1F32 340 COUNT = 400:BLANK = 80350 CS = 10 / COUNT 360 COUNT = COUNT / 10:BLANK = BLANK / 10 370 CH% = COUNT / 256:BL% = BLANK / 256 REM NEXT LOADS COUNT AND BLANK TIMES INTO ADIOS 380 390 POKE 7988, COUNT - 256 \* CH%: POKE 7989, CH% POKE 7990, BLANK - 256 \* BL%: POKE 7991, BL% 499 410 CALL 8018: REH STARTS ADIOS

To change COUNT or BLANK, change line 340 and then execute lines 340 thru 410; to restart after removal of ADIOS power, execute CALL 8018.

All of the Apple address locations associated with ADIOS are summarized in Table I. It is assumed in this Table that ADIOS is plugged into peripheral slot 3 of the Apple; if slot N is used, substitute N+8 for the third character of the hex address (=B for N=3) or add 16(N-3) to the decimal address. These addresses may be accessed by machine language programs (i.e., ADIOS INITB) or by BASIC programs using PEEK and POKE. Analog and digital output are accomplished by POKE'ing bytes into the appropriate registers; the details for doing this are discussed in IV and VI of this report. Digital input is also accomplished in a straightforward manner by PEEK'ing at address 49335. Analog input is slightly more

| READ<br>OR<br>WRITE | м            | M            | M             | м            | M                        | м                         | R/W                                                                                     | М                                                          | Å                                                                                  | M                                                                      |           | M                                                                                              | м                                                                  | М                                                             | Μ                                                                  | м                                                                  |

|---------------------|--------------|--------------|---------------|--------------|--------------------------|---------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

|                     |              |              |               | •            |                          |                           | : 49342)                                                                                |                                                            | BITS                                                                               |                                                                        |           | (COUNT/BLANK)                                                                                  | LSW)                                                               | (MSM)                                                         | LSW)                                                               | (MSM)                                                              |

| DESCRIPTION         | COUT LS BYTE | COUT NS BYTE | DOU'T LS BYTE | DOUT MS BYTE | DIGITAL OUTPUT BITS, 0-7 | DIGITAL OUTPUT BITS, 8-15 | AND9513 DATA REGISTER<br>(Internal registers addressed thru AMD9513 command register at | CLEARS DATA READY AND EXT TRIGGER FLIP FLOPS IN WRITE MODE | READS DATA READY AND EXT TRIGGER FLIP FLOPS AND DIGITAL INPUT BITS<br>IN READ MODE | WRITES INTO AMD9513 COMMAND REGISTER, CR.<br>SOME USEFUL COMMANDS ARE: | CR ACTION | 9 (or 17) PRESENTS LOAD (OR HOLD) REGISTER OF COUNTER 1 (COUN<br>AT DATA REGISTER PORT (49334) | 10 (or 18) PRESENTS LOAD (OR HOLD) REGISTER OF COUNTER 2 (AIN LSW) | 11 (or 19) PRESENTS LOAD (OR HOLD) REGISTER OF COUNTER 3 (AIN | 12 (or 20) PRESENTS LOAD (OR HOLD) REGISTER OF COUNTER 4 (BIN LSW) | 13 (or 21) PRESENTS LOAD (OR HOLD) REGISTER OF COUNTER 5 (BIN MSW) |

| HEX<br>ADDRESS      | COBO         | COBI         | C0B2          | COB3         | C0B4                     | COB5                      | COB6                                                                                    | COB7                                                       | _                                                                                  | COBE                                                                   |           |                                                                                                |                                                                    |                                                               |                                                                    |                                                                    |

| DECIMAL<br>ADDRESS  | 49328        | 49329        | 49330         | 49331        | 49332                    | 49333                     | 49334                                                                                   | 49335                                                      |                                                                                    | 49342                                                                  |           |                                                                                                |                                                                    |                                                               |                                                                    |                                                                    |

complicated as the desired data is located in internal registers of the AMD9513 which can be PEEK'ed at address 49334 by POKE'ing AMD9513 internal addresses into 49342; this is discussed in III.

#### **II. SYNCHRONIZATION**

The COUNT/BLANK cycle can be triggered in one of three (3) modes:

1) Free Run - COUNT starts immediately after BLANK with the timing of the cycle determined by when the initialization routine was run.

2) Software Trigger - Each COUNT cycle is triggered by an Apple command.

External Trigger - An external trigger signal starts the COUNT cycle.

Only the Free Run mode, accessed with a BASIC program, will be discussed in this report.

The Apple can POKE outputs at anytime and also PEEK at inputs at anytime relative to the COUNT/BLANK cycle. However, to produce meaningful results from an experiment it will usually be necessary to make output changes at the beginnin of BLANK time and also to know the time period pertaining to an analog signal integration.

The synchronization of the program to the free running COUNT/BLANK cycle is accomplished by a Basic WAIT command and a DATA READY bit which is set =0 by hardware at the beginning of BLANK time. The following program lines accomplish this:

4250 WAIT 49335,128,128: REM WAIT UNTIL DATA READY BIT = 0 AT BLANK TIME START

4260 POKE 49335,128: REM RESET DATA READY BIT

4265 REM NEXT PROGRAM LINES CHANGE OUTPUTS DURING BLANK TIME

(See IV AND VI for details)

4320 REM BLANK TIME MAY NOW END 4325 REM NEXT PROGRAM LINES READ ANALOG INPUT COUNTERS

• (See III for details)

•

4400 RETURN: REM COMPUTER MAY NOW DO OTHER TASKS BUT MUST RETURN TO 4250 BY END OF COUNT TIME

Five indicator LED's on the ADIOS front panel indicate the status of initialization and synchronization. The large, green COUNT/BLANK LED is on during COUNT time after ADIOS has been initialized. Four other indicators, TRANSFER, MISS DEAD, and WAIT, will function only if the program contains the following lines involving the CALL and MISSED DATA bits which are internal AMD9513 flip-flops accessible through the AMD9513 data register:

4205 REM NEXT 4 LINES SET UP CALL BIT TO OPERATE STATUS INDICATORS 4210 POKE 49342,20: REM ADDRESSES 9513 HD4 4220 ZZ = PEEK (49334): REM DUMMY PEEK TO ADVANCE 9513 DATA POINTER 4230 POKE 49334,174: REM SETS CALL BIT HIGH 4240 IF PEEK (49335) < 128 THEN 4500: REM IF DATA READY BIT IS ZERO PREVIOUS DATA WAS MISSED (Followed by WAIT statement and I/O lines previously described) • 4370 POKE 49342,19: REM ADDRESS 9513 HD4 4380 ZZ = PEEK (49334): REM DUMMY PEEK TO ADVANCE 9513 DATA POINTER 4390 POKE 49334,168: REM CLEAR CALL BIT 4500 REM TURN ON MISSED DATA LIGHT 4510 POKE 49342,18: REM ADDRESS 9513 HD1 4520 ZZ = PEEK (49334): REM DUMMY PEEK TO ADVANCE 9513 DATA POINTER 4530 POKE 49334,172: REM CLOCKS MISSED-DATA ONE-SHOT 4540 POKE 49342,18: REM ADDRESS 9513 HD1 4550 ZZ = PEEK (49334): REM DUMMY PEEK TO ADVANCE 9513 DATA POINTER 4560 POKE 49334,168: REM CLEARS MISSED-DATA CLOCK 4570 POKE 49335,0: REM SET DATA READY BIT 4580 GOTO 4250

Lines 4210, 4220, 4510, 4520, 4540, and 4550 are obscure code necessary becaus of a quirk of the Apple POKE statement and also the 9513 addressing system. The Apple POKE command causes a PEEK followed by a POKE to be executed; the PEEK

- 10 -

causes the 9513 to advance its data pointer register. Thus a lower 9513 register must first be addressed to POKE into the desired address.

With the inclusion of the above lines TRANSFER lights for 0.5 seconds after each data transfer, MISSED DATA lights for 0.5 seconds if an integration is not read by the Apple, and WAIT is on while the Apple is waiting for the DATA READY bit.

#### III. ANALOG INPUT

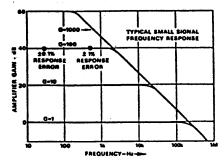

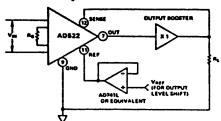

A block diagram of the analog input system was given in Figure 1; detailed schematics and data sheets are included at the end of this report.

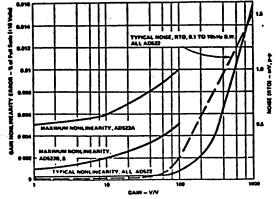

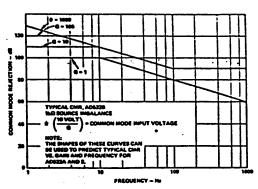

Inputs AIN and BIN are through front-panel BNC jacks or connector pins E30-33 as described in Table II. Inputs to BIN may also be through an 8-channel differential multiplexer with pins E1-16 as described in Table II. The multiplex is addressed by bits 5(LSB), 6, and 7(MSB) of the digital output byte, address 49333. Input resistance is 1000 megohms differential and common mode for inputs in the range  $\pm$  14 volts. Common mode rejection is > 75 db for common mode voltag within  $\pm$  10 volts. The inputs are protected against overvoltage.

The full scale range of the analog inputs are controlled by two internal switches (see location drawing) for each input as follows:

| SWITCH<br>Sl or S3 | SWITCH<br>S2 or S4 | V/F LOWER LIMIT<br>O HZ | V/F UPPER LIMIT<br>1 MHz |

|--------------------|--------------------|-------------------------|--------------------------|

| OPEN               | CLOSED             | OV                      | + 10.000 V               |

| CLOSED             | OPEN               | - 10.000 V              | + 10.000 V               |

(The switch lever should be pushed towards the red dot for positive-only operation.) Thus each mode requires a different scaling in the program to convert counts to volts. The zero drift for the bipolar modes is typically 0.6 mV/°C and is much greater than the 0.01 mV/°C typical zero stability of the 0 to +10V range.

- 11 -

| TABLE | II | - | Pin | Assignments | for | Front-Panel | Connectors |

|-------|----|---|-----|-------------|-----|-------------|------------|

|                  | Male - Cinch DC-37P      | F is Female - Cinch DC-37S |

|------------------|--------------------------|----------------------------|

| PIN              | FUNCTION                 | PIN FUNCTION               |

| El               | вон                      | F1 DOO                     |

| E2               | BOL                      | F2 D01                     |

| E3               | він                      | F3 DO2                     |

| E4               | B1L                      | F4 D03                     |

| E5 ·             | B2H                      | F5 D04                     |

| E6               | B2L                      | F6 D05                     |

| - E7             | взн                      | F7 D06                     |

| E8               | B3L ANALOG INPUTS TO MUX | F8 D07 DIGITAL OUTPU       |

| E9               | В4Н                      | F9 D08                     |

| E10              | B4L                      | F10 D09                    |

| E11              | в5н                      | F11 D010                   |

| E12              | B5L                      | F12 D011                   |

| E13              | в6н                      | F13 D012                   |

| E14              | B6L                      | F14 D013                   |

| E15              | в7н                      | F15 D014                   |

| E16              | B7L                      | F16 D015                   |

| E17              |                          | F17 DO12 RELAY -           |

| E18              | AIN GAIN PROGRAMMING     | F18 DO12 RELAY +           |

| E19              | MUX ENABLE               | F19 +5 VOLTS               |

| E20              |                          | F20 DIO DIGITAL INPUT      |

| E21              | BIN GAIN PROGRAMMING     | $F_{21}$ DOO               |

| E22              | +15 VOLTS                | F22 D01                    |

| E23              | GROUND                   | F23 D02                    |

| E24              | -15 VOLTS                | F24 D03                    |

| E25              | DII                      | F25 D04 DRIVER OUTPUTS     |

| E26              | DI2                      | F26 D05                    |

| E27              | DIGITAL INPUTS           | F27 D06                    |

| E28              | DI4                      | F28 D07                    |

| E29              | DI5                      | F29 DRIVER ENABLE          |

| E30              | AIN H                    | F30 RELAY B+               |

| E31              | AIN L                    | F31 D08                    |

| E32 <sup>°</sup> | BIN H                    | F32 D09                    |

| E33              | BIN L                    | F33 D010 RELAY DRIVER      |

| E34              | COUT H                   | F34 D011                   |

| E35              | COUT L                   | F35 GROUND                 |

| E36              | DOUT H                   | F36 D011 RELAY -           |

| E37              | DOUT L                   | F37 DO11 RELAY +           |

|                  |                          |                            |

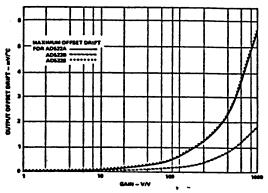

The full scale sensitivity of the analog inputs can also be increased by adding resistors between pins E17 and E18 for AIN and E20 and E21 for BIN. This increases the gain of the AD522 input amplifier by a factor of 1 + 200K/R where R is the value of the added resistor. In later versions of ADIOS, the internal bipolar/unipolar switches and also switches to give 1 volt full scale will be added to the front panel.

The 1 MHz V/F converter outputs are counted by 32-bit counters within the AM9513. At the end of COUNT time the contents of these counters are automatically transferred into 16-bit HOLD registers within the AM9513. This assumes that the initialization program of Appendix 1 (appropriate for Free Run mode) is used. The AM9513 can also be programmed to allow transfer to the HOLD registers under softwar control. AIN is stored in HOLD 2 (LSW) and HOLD 3 (MSW); BIN is stored in HOLD 4 (LSW) and HOLD 5 (MSW). The HOLD registers are read out by POKE'ing appropriate addresses into the AM9513 command register at address 49342 (see Table I). One byte at a time is then read by PEEK(49334) commands. The leastsignificant byte is read first and the AM9513 data pointer automatically advances to the most significant byte for the next PEEK(49334). (However, it does not automatically advance to the most significant word; this must be done with another POKE to 49342.) BASIC program lines to perform these tasks are given below:

510 MK = 256: MM = 65536: CS = 10/COUNT: CZ = 0: REM THESE ARE FOR 0 TO +10V MODE

520 REM FOR -10V TO +10V MODE USE CS = 2\*CS AND CZ = 10000

(After DATA READY WAIT and output POKES) 4330 POKE 49342,18: REM ADDRESS 9513 FOR LSW OF AIN 4335 REM FOR BIN USE POKE 49342,20 4340 AIN = PEEK (49334) + MK\*PEEK (49334) 4350 POKE 49342,19: REM ADDRESS 9513 FOR MSW OF AIN 4355 REM FOR BIN USE POKE 49342,21 4360 AIN = AIN + MM\*PEEK (49334) 4365 REM MSB OF MSW NOT NEED FOR COUNT TIME < 16.77 SECONDS 4368 MV = CS\*AIN - CZ: REM MV IS AIN IN MILLIVOLTS

## IV. ANALOG OUTPUT

The interface contains two Datel/Intersil DAC-HP16BGC D/A converters (see data sheet) which directly provide  $\pm$  5 volt output with 16 bit resolution. These outputs are buffered and amplified X2 by an OP10-EY dual op-amp which has zero and gain trim adjustments. The two resulting  $\pm$  10 volt outputs are designated COUT and DOUT and are available on front-panel BNC jacks and also on pins E34 (COUT H), E35 (COUT L), E36 (DOUT H), and E37 (DOUT L) of the 37-pin E front-panel connector. The outputs can sense ground at the desired load but 100 ohms is presented by the output return lead to chassis ground.

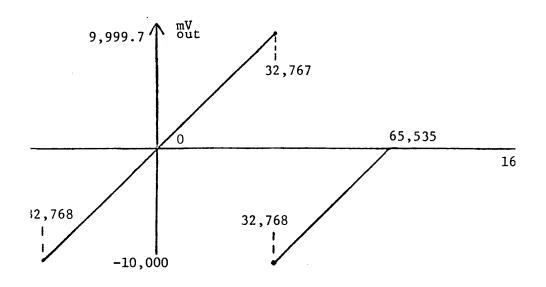

COUT and DOUT are each accessed by two bytes within the Apple address space. If the interface card is plugged into slot 3, the addresses are given in Table I. The output voltage vs bit configuration is given in Table III.

The analog outputs are controlled by the computer POKE'ing bytes into the appropriate registers of Table I; two bytes must be POKE'ed for each output. A BASIC subroutine which converts a BASIC floating point variable, MV, equal to the desired output of COUT in millivolts, to the required bytes, ML% and MH%, is illustrated below:

20000 REM D/A SERVICE ROUTINE 20010 IF MV > 9999.7 THEN MV = 9999.7 20020 IF MV < -10000. THEN MV = -10000 20040 MT% = 3.2768\*MV 20050 MH% = MT%/256: ML% = MT% - 256\*MH% 20060 POKE 49328,ML%: REM POKE 49330 FOR DOUT 20070 POKE 49329,MH%: REM POKE 49331 FOR DOUT 20080 RETURN

#### V. DIGITAL INPUT

The six digital input lines are available on pins F20 (LSB, DIO) and E25 (DI1) thru pin E29 (MSB, DI5) of the 37-pin front-panel connectors. Input is standard TT

| Output      | He  | x          | •                 |

|-------------|-----|------------|-------------------|

| Voltage, mV | LSB | MSB        | Decimal           |

| 9,999.7     | FF  | <b>7</b> F | 32,767            |

| 5,000.0     | 00  | 40         | 16,384            |

| 0.00        | 00  | 00         | 0                 |

| - 0.30      | FF  | FF         | 65,535 or -1      |

| - 5,000.0   | 00  | C0         | 49,152 or -16,384 |

| - 9,999.7   | 01  | 80         | 32,769 or -32,767 |

| - 10,000.0  | 00  | 80         | 32,768 or -32,768 |

|             |     |            |                   |

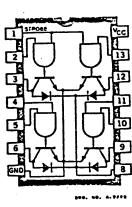

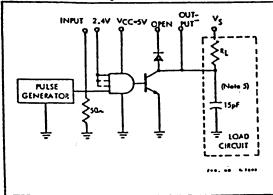

logic levels; a "1" is > +2.0 volts (drawing < 40 µA at 2.4V) and "0" is < 0.8 volts (supplying < 1.6 mA at 0.4 volts). The inputs may be inverted by installing a 74LS367A in position 8E in place of the 74LS368A. No storage flip-flops are provided; the computer senses the input lines at the time a PEEK(49335) is executed. This time can be controlled by waiting for the DATA READY bit thru WAIT 49335,128,128 as discussed in II. The state of the input lines is indicated by the 6 right-most white bar-LED's on the ADIOS front-panel; a lighted LED indicates a "1" input.

#### VI. DIGITAL OUTPUT

The 16-bit digital output word is stored in two bytes; each byte is in a 74273 octal flip-flip IC within ADIOS. One byte, bits DOO - DO7, is controlled by a POKE 49332,B command where B is the decimal value of the byte (B = O to 255); these bits are available on pins F1 - F8 of the F front-panel connector. The second byte, bits DO8 - DO15, is addressed at 49333, and is available on pins F9 - F16. The flip-flop outputs can sink 16 mA at 0.4V and drive 0.8 mA at 2.4V. All 16 bits are indicated by front-panel bar LED's; a lighted LED indicates a "1".

The flip-flop outputs are connected to three types of drivers within ADIOS. Bits DOO - DO7 drive an octal tri-state bus driver, the 74LS241 in location 7C (substitute 74LS240 to invert bits), with outputs on pins F21 - F28. The tristate driver is held disabled by a 4.7K resistor to +5V on its  $\tilde{G}$  input; the driver may be enabled by connecting pin F29 to pin F35 (ground).

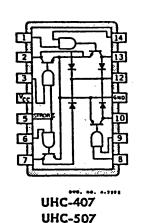

Bits DO8 - DOll drive a quad relay driver, the UHP-507, which can switch 100 volts at 250 mA output pins are F31 - F34. The driver contains transient protection diodes which should be connected to the positive relay supply voltage thru pin F30. The negative relay supply voltage should be connected to pin F35 which is tied to chassis ground.

- 16 -

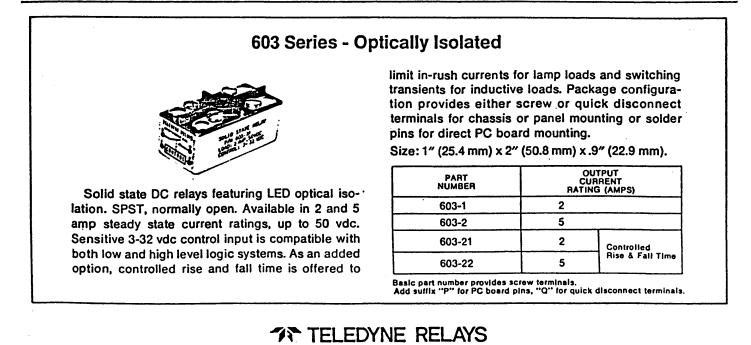

Bits DOll and DOl2 drive two solid-state relays, Teledyne 643-1, which can switch 60 volts at 200 mA. The switch terminals are available on pins F36(-) and F37(+) for DOll, F17(-), and F18(+) for DOl2. The switch terminals may float up to 2500 volts with respect to ground but the voltage polarity across the open contacts must be as indicated. Other Teledyne relays which are pin-compatible and handle AC voltages are described in a data sheet in IX.

The BIN analog multiplexer is connected to bits DO13 - DO15. These bits may also be used as digital outputs (pins F14 - F16) but do not feed a driver.

#### VII. CALIBRATION

ADIOS contains 12 4-turn pots, located as shown in Figure 4, which adjust zero and gain for the two analog outputs (4 adjustments) and two analog inputs, each having two ranges (8 adjustments). It is most convenient to first calibrate the analog outputs using an accurate 4-digit DVM and then use these outputs as voltage standards for input calibration. A program such as ADIOS TEST, listed in Appendix 2, is useful as it allows the outputs to be set by keyboard entry and displays the input readings.

Output calibration is as follows:

- Command output to 0; adjust COUT ZERO and DOUT ZERO for 0 + 1 mV output.

- Command output to 9900 mV; adjust COUT GAIN and DOUT GAIN for 9900 + 2 mV output.

- 3. To check operation, command output to -9900 mV; outputs should be  $-9900 \pm 3 \text{ mV}$ .

The 0 to +10 volt input range should be calibrated next as these adjustments also affect the  $\pm$  10 volt range adjustments (which do not affect 0 to +10 calibration). The 4 internal DIP switches should be set in the red-dot position

- 17 -

Fig. 4. Analog component and calibration adjustment location guide. A digital IC layout is given in Appendix 4.

(S2 and S4 open, S1 and S3 closed) and then proceed as follows:

- 4. Command output to 50 mV; adjust AIN and BIN ZERO for 50  $\pm$  1 output display.

- 5. Command output to 9900 mV; adjust AIN and BIN GAIN for a 9900  $\pm$  2 display.

- 6. Repeat 4, above.

Next, the -10 volt to +10 volt range is calibrated; the internal DIP switches should be set away from the red-dot position. The ADIOS TEST program scales input counts assuming the 0 to +10 volt range; this is accounted for in the desired outputs described below:

- 7. Command output to -9900 mV and adjust the -10V pots for an output display of 50  $\pm$  1.

- 8. Command output to 9900 mV and adjust the +10V pots for a display of 9950  $\pm$  3.

- 9. Repeat 7, above.

After completion of calibration, operation can be checked by putting DIP switches in the red-dot position and running the RAMP mode of ADIOS TEST. Finally, the DIP switches should be set for the desired mode of operation; typically this will be with AIN in the 0 to +10 mode and BIN in the bipolar mode.

## Appendix 1. Initialization Program - ADIOS INITB

ADIOS-INITE is a binary (machine language) program that initializes the AM9513. This is necessary in order for ADIOS to input analog signals and control synchronization. The program loads sixteen, 16-bit internal registers of the 9513 with certain values dictating the exact internal configuration of the AM9513. Two of the registers are loaded with values that control the duration of COUNT and BLANK. This initialization program also arms the counters to commence operation of the COUNT-BLANK cycle.

In order to use "ADIOS-INITB," one must first put it on a disk. This can be done by typing the object code (shown in Fig. 5) into memory with the SYSEM MONITOR and then issuing a "BSAVE ADIOS-INITB, A\$1F32, L\$55" command.

Once the program is in memory, one can modify the COUNT and BLANK initializa values. Table IV shows the addresses of ADIOS-INITB which contain these values that are loaded into the AM9513 upon execution ("CALL 8018"). Refer to the BASIC program listing, line 310, in Appendix II, for information on how to utilize ADIOS-INITB from a BASIC program.

Figure 5 contains an assembly listing of ADIOS-INITB. The actual binary program is enclosed in a box.

| TABLE | IV. | ADIOS-INITB | Initialization | Addresses |

|-------|-----|-------------|----------------|-----------|

|       |     |             |                |           |

| Address | Contents*      |

|---------|----------------|

| 7988    | COUNT time MSB |

| 7989    | COUNT time LSB |

| 7990    | BLANK time MSB |

| 7991    | BLANK time LSB |

\*values are in units of 10 mS.

- 20 -

|                |                      | ា វត្តធ្វត្ត                                                                               |

|----------------|----------------------|--------------------------------------------------------------------------------------------|

| Hex.           | Machine              | 1010 * G.WEINREB 8/11/80 "ADIOS-INITB"                                                     |

| addr           | code                 | 1020 * INITIALIZE 9513 ROUTINE; ASSEMBLER: "ASMOISE 4 A"                                   |

|                | TTPCTUB              | 1030 * CARD IN SLOT 3                                                                      |

|                |                      | 1043 .OR \$1F32                                                                            |

|                |                      | 1047 * OBJECT CODE IS 85=\$55 BYTES PLACED IN ADDRESS \$1F32 →                             |

| C08E-          |                      | 1050 *9513 1/0 ADDRESSES                                                                   |

| C086-          |                      | 1050 COMM .EQ \$C0BE COMAND REGISTER<br>1070 DATA .EQ \$C0B6 DATA REGISTERS                |

|                |                      | 1080 ×                                                                                     |

|                |                      | 1090 *DATA FOR 9513'S REGISTERS-                                                           |

| 1F32-          | E6 0F                | 1100 *DATA IN TABLE IS IN IN FORMAT WHERE LSB IS FIRST                                     |

| 1F34-          | 64 66                |                                                                                            |

| 1F36-          | 1                    | 1120 LD1 .HS 6400 1 SECOND COUNT Modifiable<br>1130 HD1 .HS 6400 1 SECOND BLANK Modifiable |

| 1F38-<br>1F38- | HU 42<br>100 00      | 1140 CM2 .HS AD42 C                                                                        |

| 1F3C-          | 00 00                |                                                                                            |

| 1F3E-          |                      | 1170 CH3 .HS A893                                                                          |

| 1F40-<br>1F42- |                      | 1180 LD3.HS0000the internal configur-<br>ation of the AM9513                               |

| 1F44-          | AD 84                | 1190 HD3 .HS 0000 atton of the AM9513.                                                     |

| 1F46-          |                      | 1210 LD4 .HS 0000                                                                          |

| 1F48-<br>1F48- |                      | 1220 HD4 .HS 0000<br>1230 CM5 .HS 0865 <                                                   |

| 1F4C-<br>1F4E- |                      | 1230 CM5 .HS A865 <                                                                        |

|                | 60 00                | 1250 HD5 .HS 0000                                                                          |

| 1F<br>1F50-    | 60 90                |                                                                                            |

|                |                      | 1280 MAMO .HS 0090 C MASTER MODE REGISTER                                                  |

|                |                      | 1300 *INIT. PROGRAM*                                                                       |

| 1F52-          | A9 FF                | 1310 *<br>1320 INIT LDA #\$FF                                                              |

| 1F54-          | 80 BE CØ             | 1330 STA COMM CMASTER RESET                                                                |

| 1F57-          | A9 01                | 1340 LDA #\$01                                                                             |

| 11,00-         | 8D BE CO             | 1350 STA COMM SET DATA POINTER<br>1360 *LDA REGISTERS*                                     |

| 1F50-          | · 🖬 🧭 1919           | 11 / /// LDV ##CC C C 도                                                                    |

| 1561-          | BD 32 60<br>80 86 00 | 1380 BEGN LDA CH1,X GET DATA                                                               |

| 1F64-          |                      | 1390 STA DATA PUT IN 9513 REG:STER                                                         |

| ·1F65-         | A9 33                | 1410 LDA #\$33 CLR Z FLAG                                                                  |

| 1F67-<br>1F69- |                      | 1420 CPX #30 FINISHED?                                                                     |

| 1F6B-          | 4C 5E 60             | 1430 BEQ DONE IF SU, END<br>1440 JMP BEGN DO IT AGAIN P                                    |

|                |                      | 1450 *SET MM REGISTER+                                                                     |

| 1F5E-          | H9 17                | 1460 DONE LDA #\$17                                                                        |

| 1F73-          | 8D BE CØ<br>AD 50 60 | 1470 STA COMM SET DATA POINTER TO MM REGISTER                                              |

| 1F76-          | 8D 86 CØ             | 1490 STA DATA PUT IN MM REG.                                                               |

| 1579-          |                      | 1500                                                                                       |

| 1F70-          | AD 51 60<br>80 86 C0 |                                                                                            |

|                |                      | 1520 STA DATA PUT IN MM REG<br>1530 *ARM COUNTERS*                                         |

| 1F7F-<br>1F91- | A9 7F                | 1540 LDA #\$7F                                                                             |

| 1F84-          | 8D BE C0<br>60       |                                                                                            |

|                | L                    | 1555 RTS END OF PROGRAM                                                                    |

|                |                      |                                                                                            |

## Fig. 5. ADIOS-INITB Assembly Listing

÷

ай 8-м 40(08 (EST PROGRAM OF 3/23/8) 50 60T0 220: REM INITIALIZE 100 PRINT "THIS PROGRAM ALLOWS A FIXED NUMBER OR A 0 TO 9900MV RAMP TO BE OUTPUT FROM C AND D. THESE SHOULD BE CONNECTED TO A AND B INPUTS. THE FIXED NUMBER OR RAMP IS ALSO APPLIED TO THE TWO DIGITAL OUTPUT BYTES."; 101 PRINT "DIGITAL INPUT BITS ARE ALSO READ AND DISPLAYED. COUNT=400 AND BLANK =80; CHANGE IN 340 IF YOU WISH. PROGRAM SCALING ASSUMES ADIOS IS IN 0 TO +10V MODE (ALL DIP SHITCHES ON)" 104 PRINT مور بن بنیور دو. مور با معدور دو 110 INPUT "RAMP(R) OR FIXED(F) INPUT? ";X\$ 112 PRINT IF X\$ = "R" GOTO 900 120 125 IF X\$ = "F" GOTO 200 130 GOTO 110: REM INVALID REPLY; TRY AGAIN 199 REM FIXED OUTPUT ROUTINE 200 PRINT "FIXED OUTPUT. USE CONTROL C TO STOP; GOTO 200 TO CHANGE VALUE" 210 INPUT "MILLIVOLTS? ";F 211 60SUB 4200 215 MV = AIN \* CS:MY = BIN \* CS $216 \ D6\% = D1\% - 128$ 218 PRINT F;" ";MV;" ";MY;" ";06% 220 GOTO 211: REM REPEAT 230 REM INITILIZATION ROUTINE 240 D = CHR(4) 250 TEXT : HOME : PRINT 310 REM NEXT INITILIZES A/D INTERFACE AND SETS UP INTEGRATION CYCLE 320 GOSUB 7000: REM POKE COPY OF ADIOS-INITB 330 REM BLOADED 85 = \$55 BYTES IN 7986 = \$1F32 340 COUNT = 400: BLANK = 80 350 CS = 10 / COUNT 360 COUNT = COUNT / 10: BLANK = BLANK / 10 370 CH% = COUNT / 256:BL% = BLANK / 256 380 REM NEXT LOADS COUNT AND BLANK TIMES INTO ADIOS 390 POKE 7988, COUNT - 256 \* CHX: POKE 7989, CHX 400 POKE 7990, BLANK - 256 \* BL%: POKE 7991, BL% 410 CALL 8018: REM STARTS ADIOS 420 REM GOSUB 5300 TO TURN ON PRINTER 430 REM CALL 1013 TURNS OFF PRINTER 450 POKE 33,40: REM NORMAL TEXT WINDOW 500 REM CONSTANTS FOR DATA TRANSFER 510 MC = 3.2768: MJ = 128: MK = 256: MM = 65536 600 GOTO 100 899 REM 900 REM RAMP TEST 910 PRINT "COUT AND DOUT WILL RAMP FROM 0 TO 9900MV IN A SELECTED STEP SIZE. IF AIN AND BIN DISAGREE WITH COUT AND DOUT BY MORE THAN DMAX=10MV (CHANGE IN 1010) THEN: " PRINT 911 913 INPUT "ERROR MESSAGE IS NONE(0), BEEP(1), OR PRINTER LINE(2)? ";J 915 PRINT INPUT "STEP SIZE IN MILLIVOLTS? ";ST 920 1005 NR = 0: REM NR (S NUMBER OF READS SINCE LAST ERROR 1910 <u>0</u>MAX = 50 1020 FOR F = 000 TO 9900 STEP ST Appendix 2

```

1941) जन्म<u>न्त</u>्र कहेलेखे

1060 \text{ MO} = 410 + 08:\text{MV} = 610 + 08

1070 06% = 01% - MUX: REM SUBTRACT DATA READY BIT

";MV;" ";MY;"

1080 PRINT F - ST;"

";06%

1090 IF F = 0 GOTO 1220

1100 D = ABS (F - ST - HV)

1110 IF D > DMAX THEN CALL

- 211: GOSUB 1500

1150 E = ABS (F - ST - MY)

IF E > DMAX THEN CALL - 211: GOSUB 1500

1160

1210 NR = NR + 1

1220

NEXT F

1230

GOTO 1010: REM REPEAT RAMP

1500

REM ERROR MESSAGE

1510

ON J GOTO 1587,1560

1520 NR = 0: RETURN : REM

NO MESSAGE IF J=0

GOSUB 5300: REM TURN ON PRINTER

1560

PRINT F - ST; ";HV; ";HY; ";DG%;"

1570

";NR

1580

CALL 1013

1587

CALL - 1059: REM BEEP!

1589 NR = 0

1590

RETURN : REM

4200 REM

DATA TRANSFER ROUTINE WITH PARAMETERS MC1 FOR NOISE

SOURCE ON),F(OUTPUT TO LO) AND AIN (INPUT FROM RECEIVER)

4201 FC = F: IF F < 0 THEN FC = F + 20000

4202 MT = FC * MC: REM OUTPUT F TO COUT

4203 MH% = MT / MK: ML% = MT - MK * MH%

4204 OH% = F / MK:OT% = F - MK * OH%: REM F MODULO 256 FOR DIGITAL

OUTPUT

4205 REM NEXT 4 LINES TO SET UP 9513

4210 POKE 49342,20: REM

ADDRESSES 9513 HD4

4220 ZZ = PEEK (49334): REM ZZ IS DUMMY

4230 POKE 49334,172: REM CALL BIT SET HIGH

4240

IF PEEK (49335) < 128 THEN 4500

4250 WAIT 49335,128,128: REM WAIT UNTIL DATA READY BIT =0 AT BL

TIME START

4260

POKE 49335,128: REM RESET DATA

READY BIT

4270

OUTPUT BITS DOØ TO DO7

POKE 49332.0T%: REM

428Ø

POKE 49333.0T%: REM

OUTPUT BITS DO8 TO DO15

4290 DIX = PEEK (49335): REM DIGITAL INPUT

4300 POKE 49328, ML .: REM

COUT LSBYTE

4310

POKE 49329, MHX: REM

COUT MSBYTE

4313

POKE 49330, MLX: REM COUT LSBYTE

4315

POKE 49331 MH%: REM

COUT MSBYTE

4320

REM BLANK TIME MAY NOW END

4330 POKE 49342,18: REM ADDRESS 9513

TO OUTPUT LSWORD OF AIN

4340 V1 = PEEK (49334):V2 = PEEK (49334)

4350 POKE 49342,19: REM ADDRESS 9513 TO OUTPUT MSWORD OF AIN

4360 V3 = PEEK (49334)

4365 AIN = V1 + MK * V2 + MM * V3

4366 POKE 49342,20: REM ADDRESS 9513 FOR BIN

4368 Y1 = PEEK (49334):Y2 = PEEK (49334)

4370 POKE 49342,21

4372 Y3 = PEEK (49334)

4376 BIN = Y1 + MK * Y2 + MM * Y3

POKE 49342,20: REM ADDRESS 9513

4378

HD4

4380 ZZ = PEEK (49334): REM DUMMY PEEK

POKE 49334.168. REM CLEAR CALL BIT

4390

44NØ

REMEN

4-1111

REP TURN ON MISSED DATA LIGHT

```

```

Appendix 2

```

4505 PRINT "MISSED DATA", COUNT, BLANK 4510 POKE 49342,18: REM ADDRESS HOLD1 4520 ZZ = PEEK (49334); REM DUMMY 4530 POKE 49334,172: REM CLOCKS MISSED DATA ONE-SHOT 4540 POKE 49342,18 4550 ZZ = PEEK (49334). 4560 POKE 49334,168: REM / CLEARS MISSED DATA CLOCK 4570 POKE 49335,0: REM CLEAR FLAG 4580 GOTO 4250 5299 REM 5300 -REM TURNS ON TRENDCOM 200 PRINTER 5310 REM : GOTO 5400: REM FOR APPLE PRINTER 5315 PR# 1: PRINT CHR\$ (0): REM FIRST CHARACTER NOT PRINTED 5320 POKE 1913,6: POKE 1785,72: REM MARGINS 5330 POKE 1657,80: REM LINE LENGTH 5340 RETURN 5400 REM TURN ON APPLE PRINTER 5410 PRINT CHR\$ (4);"PR#1" 5420 Q\$ = CHR\$ (17): REM PRINT Q\$ TO DUMP GRAPHICS 5430 POKE - 12524,0: REM BLACK ON WHITE PLOT 5440 POKE - 12528,7: REM DARK PRINT 5450 POKE - 12527,8: REM LEFT MARGIN 5460 RETURN 5999 REM 6000 REM FORMATTED LIST 6005, POKE 33,33 6010 GOSUB 5300: REM TURN ON PRINTER 6060 LIST 6065 PRINT : PRINT 6190 CALL 1013 6195 END : REM 6999 REM NEXT READS ADIOS INITE AS DATA STATEMENTS 7000 FOR I = 7986 TO 8070: READ A: POKE I,A: NEXT : RETURN 7010 DATA 230,15,100,0,100,0,173,66,0,0,0,0,168,131,0,0,0,0,173,132,0,0,0 ,0,168,101,0,0,0,0,0,144,169,255,141,190,192,169,1,141,190,192,162,0,189,5 0,31,141,182,192,232,169,51,224,30,240,3,76,94,31,169,23,141,190,192,173,8 0,31,141,182,192,173 7020 DATA 81,31,141,182,192,169,127,141,190,192,96,2,205

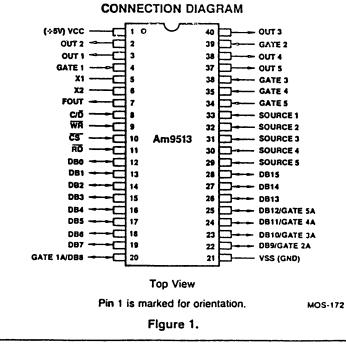

#### Appendix III - AM9513 Utilization

This section describes the AM9513 utilization in the "Free Run" mode of synchronization as described in Section II. The 9513 is a fairly complex chip described in a 26-page data brochure available from Advanced Micro Devices (5 pages of this are included in Appendix 5.H). This brochure should be read in order to understand this Appendix. However, these steps are not necessary unless modifications must be made to ADIOS.

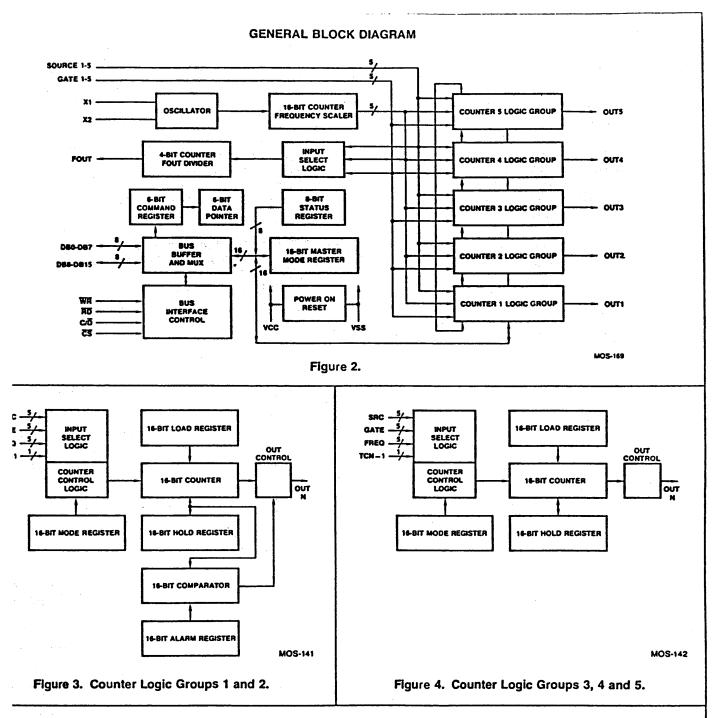

Figure 6 shows the AM9513 configuration as used in the ADIOS "Free Run" mode; a timing diagram is shown in Figure 7. The first counter group is used to generate the COUNT/BLANK signal. The duration of COUNT is determined by the contents of the LOAD register where the duration of BLANK is determined by the HOLD register. When the counter is armed, it will be loaded with the contents of the LOAD or HOLD register (depending on the current state of OUT1) and begin counting down. When TC (0001) is reached, the output will begin to toggle and the counter will be reloaded with the other register and will commenc to count down. This cycle will be repeated continuously until the counter is either reset or disarmed. The count-source of counter 1 is software selectable. However, in this manual, 100 HZ (F5) is used. This is derived from an external 1 MHz crystal oscillator which is divided down.

Counters 2, 3, 4, and 5 count the frequencies produced by the two V/F converters. Only counters 2 and 3 will be discussed since the operation of counters 4 and 5 is identical. Counters 2 and 3 are cascaded to provide 32 bits  $(4.295 \times 10^9)$  of potential counting storage for the AIN frequency. With a 1 MHz V/F, one could take data for a maximum period of 71 minutes.

- 25 -

The frequency from the AIN V/F is inhibited by the C/B signal. The two counters use operation mode "Q" so that the gate ("SAVE") is used to place the counter contents into the HOLD register and the first pulse into the counter (from the input) is used to clear the counter by initiating a reload from the empty LOAD register. The "pulse adders" are used to provide this CLR (Clear) pulse. This all takes place within the 5  $\mu$ s after COUNT time ends and is illustrated in Figure 8.

The computer can read the contents of the HOLD registers at anytime that is convenient until the next COUNT to BLANK transition occurs. OUT3 ( $\overline{\text{MISS}}$  DAT and OUT5 ( $\overline{\text{CALL}}$ ) cna be in either the state of GND (CM bit 2 = 0) or HIGH IMPEDANCE (CM bit 2 = 1) and are controlled by the computer writing data into the AM9513 Command registers.

- (1) The computer sets the CALL bit and begins to wait until BLANK commences. If the DATA READY bit is low at this point, a cycle has been missed, (by the computer) and the MISSed Data line is pulsed. The WAIT LED is illuminated between the marks (1) and (2).

- (2) The 4 counters stop counting, are saved and cleared, all within 5 µs. The DATA READY bit is set in order to tell the computer that it can begin outputting new data.

- 3) The DATA READY bit is cleared under software control.

- All data has been outputted. The CALL bit is cleared under software control. The TSFR LED is initiated to illuminate for .5 seconds. The computer can input data from the analog inputs between now and the next COUNT to BLANK transition.

- (5) All outputs should be settled. The counters commence counting. The COUNT LED illuminates.

Fig. 7. ADIOS-APPLE Synchronization

1) The counter's input is gated off.

- A pulse is applied to the internal gate of Counters 2 and 3. This pulse, labeled "SAVE", causes the contents of the counters to be placed in the HOLD registers at mark (3).

- (4) A pulse is applied/added to the input of Counter 2. This first pulse of integration clears the counter. The pulse is not recorded.

- 5 A pulse is applied/added to the input of Counter 3. This clear pulse is inhibited by OUT2. If OUT2 is clocked by the CLR 2 pulse, Counter 3 will automatically be cleared.

- NOTE: When a counter reaches FFFF, it will commit itself to outputting a terminal count pulse initiated by the next input clock pulse. Once committed, it cannot be disrupted by:

- a) the internal gate signal ("SAVE")

- b) the clearing of the counter

- c) the saving of the counter's contents

Due to this characteristic, OUT2 must inhibit CLR 3 for OUT2 becomes the "extra" pulse initiated by CLR 2 and not intended to be counted.

Fig. 8. Timing Diagram of AM9513 Counting Operation.

5341 9 11 œ å -^- v š v v Ğ v. E- V Ĝ Ğ v G - D--G 10 104 < 74L5221 . 9 9F C 741 5240 7465367 7425290 8 **8**A RD 88 8Ę A ഗ 20 643-1 7465221 643-1 7474 7465240 UHP 507 7 7E 70 78 7A 7F 70 • 11• . ਜੂ 202 **^81** - <ដ r B ŝ มพื∙ يت 24 <<u>.</u> . . ٢Ň Z цр з.г 7415240 Чн 742509 555 41 կլվ 6 İnf 68 6D 6C × HPIGBGC HPIGBGC Г 7425 273 74 45 273 5 5D 5B 5C 5A ㅈ • \_ 74175 74175 4D 74175 74175 7400 74175 4 48 4F 4Ë **4**A H • • ٠ • • G 74175 3E 7445 245 7425175 74 175 7445138 7415139 3 .3A 3F 3D 36 38 m • • . ٠ m mili 7465 112 7408 74221 742504 4.1% 2 4.7 K 20 28 2C 28 Ο • • • . 18 C TWHS 250 7465221 74L586 õ AM9513 1E 10 10 ω. 434 36-0-27 23G 30-E-30 20-E-35 - 15- В- IZ 55G 3-4-8 - 2 476 - G - ۲ Þ 8 20 ÷ **0**0 ц З ้ซื ้ง Š ō

- 30 -

1

ã

- 32 -

## Appendix 5. Manufacturers Data

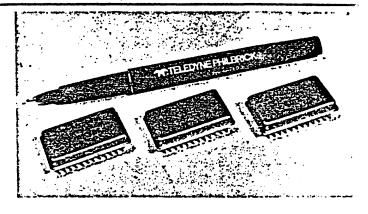

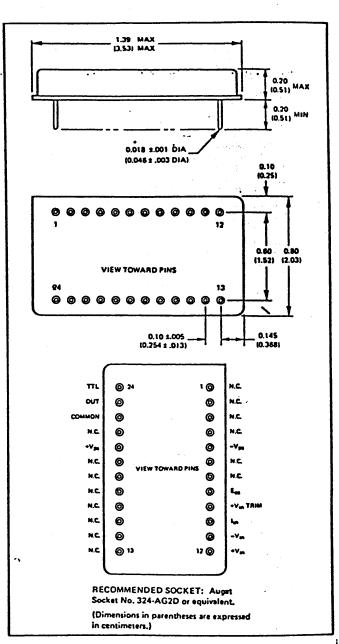

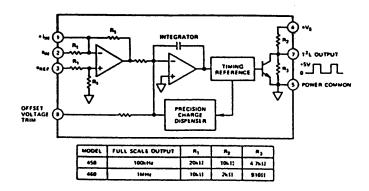

- Appendix 5.B. Consists of pages 1, 5, and 6 of a six-page report. The complete report can be obtained from Teledyne Philbrick, Allied Drive at Route 128, Dedham, Massachusetts 02026.

- Appendix 5.D. Consists of pages 1, 2, and 4 of a four-page report. The comple report can be obtained from Datel Intersil, 11 Cabot Boulevard, Mansfield, MA 02048.

- Appendix 5.H. Consists of pages 1-5 of a 26-page report. The complete report can be obtained from Advanced Micro Devices, Inc., 901 Thompson Place, P. O. Box 453, Sunnyvale, California 94086.

- Appendix 5.1. Analog Devices 460K V/F converter used as a substitute for Teledyne 4735 due to unavailability.

· •

| PRESET | CLEAR | CLOCK | J | ĸ | Q        | ā   |

|--------|-------|-------|---|---|----------|-----|

| L      | н     | Ϋ́.   | x | X | н        | L   |

| н      | L     | x     | x | x | L        | н   |

| . L    | L     | x     | x | x | н۰       | н•  |

| н      | н     | 1     | L | L | 00       | ō0  |

| н      | н     | 1     | н | L | H        | L   |

| Н.     | н     | 1     | L | н | L        | н   |

| н      | н     | 1     | н | н | TOG      | GLE |

| н      | н     | н     | x | x | 00       | ã0  |

| Н      | Ŷ     | L     |   |   |          | 3   |

| -      | •.    |       |   |   | <u>.</u> | ~   |

See pages 8-56 and 8-58

SN54L5112A (J, W) SN74L5112A (J,N SN54S112 (J, W) SN74S112 (J, N)

Appendix 5.A.

| EACH FLIP-FLOP |       |   |          |  |  |  |  |

|----------------|-------|---|----------|--|--|--|--|

|                |       |   |          |  |  |  |  |

| CLEAR          | CLOCK | D | <b>a</b> |  |  |  |  |

| L              | x     | x | L        |  |  |  |  |

| н              | t     | н | н        |  |  |  |  |

| н              | 1     | L | L        |  |  |  |  |

| н              | L     | x | 00       |  |  |  |  |

12

18

Appendix 5.A.

#### FUNCTION TABLE

| (EACH MONOSTABLE)                  |         |   |   |              |  |  |  |

|------------------------------------|---------|---|---|--------------|--|--|--|

| IN                                 | OUTPUTS |   |   |              |  |  |  |

| CLEAR                              | A       | 8 | a | ā            |  |  |  |

| L                                  | x       | x | L | н            |  |  |  |

| ×                                  | н       | x | L | н            |  |  |  |

| ×                                  | ×       | L | L | н            |  |  |  |

| н                                  | L       | 1 | ٦ | $\mathbf{v}$ |  |  |  |

| н<br>1                             | i<br>L  | H | 5 | ሯ            |  |  |  |

| Also see description and switching |         |   |   |              |  |  |  |

| characteristics                    |         |   |   |              |  |  |  |

# 10 kHz 100 kHz 1MHz HIGH RELIABILITY 4731/4733/4735 FREQUENCY CONVERTERS

This series of low drift voltage-to-frequency converters provide an output-pulse-train repetition rate that is a precision linear function of the input voltage. These low drift, ultra linear, 10 kHz/100 kHz/1 MHz Full Scale V-to-F's have the ability to handle positive, negative, and differential input signals over a wide range of power supply voltages ( $\pm 9$  V to  $\pm 18$  V). They operate over the wide temperature range of  $-55^{\circ}C$  to  $\pm 125^{\circ}C$ .

With 126 dB of dynamic range, 70 dB CMRR, and 100% overrange, these V-to-F's provide linear operation with input voltages from  $\pm 10 \,\mu$ V to  $\pm 20$ V. The current pin (the summing point of an op amp) resolves currents as low as 1000 pA (4731/4733), which makes operation with full scale input voltages from less than 250 mV to greater than 100 volts possible.

The 4731/4733's 0.005% nonlinearity is the equivalent of 16 bits end point linearity, while differential nonlinearity and dynamic range approach 20 bits. With this combination of features and specifications, the 4731/4733/4735 stand alone as sixth generation devices, capable of operation from power supply voltages as low as  $\pm 9$  V.

|      | NOMINAL FREQUENCY/ | NONLINEARITY<br>1% F.S. |         |        | FULL SCALE<br>Temp, Coef, 1PPM/°C |            |  |

|------|--------------------|-------------------------|---------|--------|-----------------------------------|------------|--|

|      | MAX. OVERRANGE     | Typical                 | Guarant | beet   | Typical                           | Gueranteed |  |

| 4731 | 10 kHz/21 kHz      | .002                    | .005    | () Hot | 4                                 | 15         |  |

|      | •                  |                         |         | Cold   | 7                                 | 25         |  |

| 4733 | 100 kHz/210 kHz    | ,002                    | .005    | () Hot | 6                                 | 20         |  |

|      |                    |                         |         | Cold   | 10                                | 30         |  |

| 4735 | 1 MHz/2.1 MHz      | .005                    | .015    | 0      | 30                                | 50         |  |

For maximum reliability and performance these V-to-Fs are offered with 100% screening similar to MIL-STD-883 Method 5008. Refer to Table 2 for details as to methods and test conditions.

| MODEL                         | OPERATING<br>TEMPERATURE<br>RANGE | SCREENED to<br>MIL-STD-883<br>METHOD 5008                                                                                                        |

|-------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 4731<br>4733<br>4735          | −55°C to +125°C                   | Internal Visual<br>Stabilization Bake<br>Constant Acceleration<br>Seal, Fine and Gross Leak<br>External Visual                                   |

| 4731-83<br>4733-83<br>4735-83 | -55°C to +125°C                   | Internal Visual<br>Stabilization Bake<br>Constant Acceleration<br>Seal, Fine and Gross Leak<br>Burn-In<br>Temperature Cycling<br>External Visual |

- 37 -

### **FEATURES**

- 100% Screening Similar to MIL-STD-883, Method 5008

- Power Supply Range ±9 V to ±18 V

- Ultra Linear

- 100% Overrange

- 126 dB Dynamic Range

- 70 dB CMRR

- Low Full Scale Drift

- Low Zero Offset Voltage Drift

- TTL, CMOS, HNIL Compatible Output

#### - APPLICATIONS

- No Drift Integrate/Hold

- High Common Mode Voltage Isolation

- 2-Wire Digital Transmission

- Analog-to-Digital Converters—20 Bit

- Optical Data Link

### HOW TO USE THE 4731/4733/4735

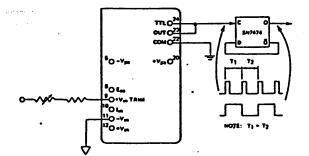

When used as shown in Figure 1A & 1B, the factory trimmed V-to-F operates as specified without additional components. Pin 9 the  $+V_{in}$  trim and pin 12 the  $+V_{in}$  are both inputs for a positive input signal. Pin 12 can be used when accuracy to  $\pm 0.1\%$  of F.S. is needed with no external components. Pin 9 is usually used when greater accuracy is required using an external trim, see Figure 2A.

## 4731/4733/4735

### Output Protection (+Vcc, Common, -Vcc)

The V-to-F output (collector of Q2) may be shorted to ground indefinitely without damage, however, since Q2 is ON most of the time, a short to  $+V_{CC}$  will cause certain catastrophic failure in about 5 seconds. A short to TTL (pin 24) and  $-V_{CC}$  simultaneously will cause instant catastrophic failure.

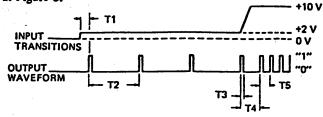

### Square Wave Output

The output of the 4731/4733/4735 is a train of pulses 20 usec/2  $\mu$ sec/.2  $\mu$ sec (see Figure 7). A symmetrical (square wave) output for driving highly capacitive or noisy transmission lines is obtained with a D or JK flip flop as shown in Figure 8.

|      | Typical Ti | me in M | icro-Sea | conds |     |

|------|------------|---------|----------|-------|-----|

|      | T1         | T2      | T3       | T4    | T5  |

| 4731 | 0 to 500   | 500     | 20       | ≈200  | 100 |

| 4733 | 0 to 50    | 50      | 2        | ≈30   | 10  |

| 4735 | 0 to 5     | 5       | 0.2      | ~3    | 1   |

Figure 7. Typical Waveforms, Showing Timing Relationships

Figure 8. Square Wave Output Using D - Type Flip Flop

| Test                   | Methods and Conditions                                                                                                                                        | Purpose                                                                                                           |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| *Internal Visual       | Method 2017                                                                                                                                                   | Removes potentially delective units with respect to materials, construction, and workmanship.                     |

| *Stabilization Bake    | Method 1008, Condition C<br>24 hours at 150 °C                                                                                                                | Preconditioning treatment to stabilize circuit<br>components prior to conducting further testing<br>and trimming. |

| *Constant Acceleration | Method 2001, Condition A<br>Y1 Axis, 5,000 g                                                                                                                  | Removes potential failures due to weak wire or chip bonding.                                                      |

| *Seal, Fine and Gross  | Method 1014, Fine Leak<br>Condition A & C<br>Bomb time 1 hr. at 30 psi; Leak Rate<br>< 5 X 10 <sup>-7</sup> cc/sec; Gross Leak, Condi-<br>tion C1, no bubbles | Verifies Integrity of hermetic package                                                                            |

| Burn In                | Method 1015 Condition B<br>160 hours at 125°C                                                                                                                 | Reduces inlant mortality rate                                                                                     |

| Temperature Cycling    | Method 1010, Condition B<br>10 cycles from<br>-55 °C +0 °C<br>-5 °C 10 +125 °C +3 °C<br>-0 °C                                                                 | Removes potential failures due to weak wire or chip bonding.                                                      |

| *External Visual       | Method 2009                                                                                                                                                   | Removes delective units with respect to materia<br>construction, and workmanship.                                 |

\*These tests are for both standard and "-83" models 4731, 4733 and 4735 Screening Program to MIL-STD-883

## 4731/4733/4735

SPECIFICATIONS @ +25 °C, ±Vcc, ±15 V lunless otherwise indicated)

|                                                                                    | TYPICAL                        |                   |             | GUARANTEED                                                                                                                              |

|------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| FULL SCALE (FS)                                                                    |                                | •                 |             |                                                                                                                                         |

| later the state framewing                                                          | ·                              |                   |             | $f_{out} = \frac{(V_{in})(I_A)}{10 V} = \frac{(I_{in})(I_A)}{H_B} \odot$                                                                |

| deal Transler Function                                                             |                                |                   |             | out 10 V L. (7)                                                                                                                         |

|                                                                                    |                                |                   |             | f <sub>A</sub> = 10 kHz (4731)/100 kHz (4733)/1 MHz (4735)                                                                              |

| +Vin trim                                                                          |                                |                   |             | 9.9 V 10.5% trimmable to 10.00 V                                                                                                        |

| +Via                                                                               |                                |                   |             | 10.00 V 1.05 V                                                                                                                          |

| +lin                                                                               |                                |                   |             | 100 µA ±25% (4731/4733); 1 mA ±25% (4735)                                                                                               |

| Range (for specified nonlinearity) O                                               |                                |                   |             | •                                                                                                                                       |

| +Vin Terminal                                                                      | +10 µV to +21 V                |                   |             | +100 µV to +12 V                                                                                                                        |

| -V <sub>in</sub> Terminal & V <sub>cc</sub> = ±18 V                                | -10 µV to (-V <sub>cc</sub> +5 |                   |             | -100 µV to (-V <sub>cc</sub> +7.0 V)                                                                                                    |

| +lin Terminal                                                                      | +1 nA to +210 µA4              |                   |             | +1 nA to 120 #A (±25%) (4731/4733)                                                                                                      |

|                                                                                    | 10 nA to +2.1 mA (             | 4735)             |             | 10 nA to 1.2 mA (4735)                                                                                                                  |

| Differential $[(+V_{in}) - (-V_{in})] \Phi$                                        | ±12 V                          |                   |             | 111 V, (1Vcc fault)                                                                                                                     |

| Dver Range Max., +V <sub>iR</sub> , (–V <sub>in</sub> = 0)<br>Dynamic Range        | +Vin = 21 V, fout =<br>126 dB  | · 21 KH2/210 KH2/ | 2.1 10112   | +V <sub>in</sub> = +20 V, f <sub>out</sub> = 20 kHz/200 kHz (4731/4733); +V <sub>in</sub> = +15 V, f <sub>out</sub> = 1.5 MHz<br>100 d8 |

| Common Mode Voltage Ø                                                              | (+Vcc -4 V), (-Vcc             | +5 V1             |             | (+V <sub>cc</sub> -5 V), (-V <sub>cc</sub> +7 V)                                                                                        |

| CMRR, CMV - ±10 V                                                                  | 70 dB                          |                   |             | 60 d8                                                                                                                                   |

| NONLINEARITY :%FS                                                                  | 4731/4733                      | 4735              |             | 4731/4733 4735                                                                                                                          |

| Vin (+100 µV to 12 V)                                                              | .002                           | .005              |             | .005 .015                                                                                                                               |

| +Via (+100 µV to 12.0 V) @ @                                                       | .002                           | .005              |             | .005 .015                                                                                                                               |

| -Vie (-100 µV to -Vcc +7.0 V)                                                      | .01                            | .02               |             | .02 .05                                                                                                                                 |

| elin (1 nA to 120 µA) (4731/4733)                                                  | .002                           |                   |             | .005                                                                                                                                    |

| Hin (1 nA to 120 µA) (4731/4733) @ @                                               | .002                           |                   |             | .005                                                                                                                                    |

| Hin (10 nA to 1.2 mA) (4735)                                                       |                                | .005              |             | D15                                                                                                                                     |

| Hin (10 nA to 1.2 mA) (4735) @ @                                                   |                                | .005              |             | D15                                                                                                                                     |

| +Via (+100 μV to +12.0 V) Φ                                                        | .005                           | .01               |             | .01 Hot; .03 Cold                                                                                                                       |

| +Vin (+100 µV 10 20 V) (4731/4733) @ ●                                             | .02                            |                   |             | .05                                                                                                                                     |

| +Vin (+100 μV to 15 V) (4735) @ Φ                                                  |                                | .02               |             | 05                                                                                                                                      |

| NPUT                                                                               |                                | <u></u>           |             |                                                                                                                                         |

| Zero Offset Voltage, Initial Untrimmed                                             | ±1 mV                          |                   |             | 15 mV (trimmable to zero)                                                                                                               |

| Impedance @ +Vin                                                                   |                                |                   |             | 100 kn ±25% (4731/4733); 10 kn ±25% (4735)                                                                                              |

| Impedance @ -Vin                                                                   | 100 MΩ                         |                   |             | 10 MΩ                                                                                                                                   |

| Impedance @ +IIn (op amp summing point)                                            | Virtual Ground                 |                   |             | <0.1 Ω                                                                                                                                  |

| STABILITY OF FULL SCALE FACTOR                                                     | 4731                           | 4733 .            | 4735        | 4731 4733 4735                                                                                                                          |

|                                                                                    |                                |                   | 0           |                                                                                                                                         |

| •                                                                                  | Hot Cold                       | Hot Cold          | -           |                                                                                                                                         |

| Tempereture Coefficient (+Vin, -Vin) ±PPM/°C @                                     | 4 7                            | 6 10              | 30          | 15 25 20 30 50                                                                                                                          |

| Tempereture Coefficient (+1in) ±PPM/*C @                                           | 4 7                            | 6 10              | 30          |                                                                                                                                         |

| Temperature Coefficient (+Vin, -Vin) ±PPM/°C @                                     | <b>8</b> 10                    | 12 15             | 30          | 25 50 30 50 50                                                                                                                          |

| Power Supply Sensitivity 1PPM/%AV <sub>CC</sub> @<br>Drift: Per Ozy/Per Month 1PPM | 10<br>10/30                    | 10<br>10/30       | 15<br>10/30 | 20 20 35                                                                                                                                |

| Norm Up Time 10.01%/.002% of F.S.                                                  | 1 s/100 s                      | 1 1/100 1         | 1 3/100 1   |                                                                                                                                         |

|                                                                                    |                                |                   |             |                                                                                                                                         |

| STABILITY OF ZERO OFFSET VOLTAGE #V/°C                                             | 4731/4733                      | 4735              |             | 4731/4733 4735                                                                                                                          |

| Tempereture Coefficient µV/°C @                                                    | 15                             | 110               |             | 120 150                                                                                                                                 |

| Temperature Coefficient µV/°C ©                                                    | 120                            | 115               |             | ±100 Hot; ±50 Cold ±50                                                                                                                  |

| Power Supply Sensitivity 24V/% Vcc O                                               | 3                              | 5                 |             | 20 10                                                                                                                                   |

| Drift : Per Day/Per Month                                                          | 20 µV/60 µV                    | 20 µV/60 µV       |             |                                                                                                                                         |

| RESPONSE                                                                           |                                |                   |             |                                                                                                                                         |

| Setting Time to .01% for FS step input                                             |                                |                   |             | 1 to 2 pulses of new frequency +5 µs                                                                                                    |

| Overlead Recovery (Vin = +100 V to Vin = +10)                                      | 0.14 ms (4731/473              | 3); 70 #\$ (4735) |             | 0.5 ms (4731/4733); 0.2 ms (4735)                                                                                                       |

| er ( $I_{in} = 1 \text{ mA to } I_{in} = 100 \mu \text{A}$ )                       |                                |                   |             |                                                                                                                                         |

| OUTPUT WAVEFORM                                                                    |                                |                   |             | TTL compatible pulses adaptable to                                                                                                      |

| Mah Januara Inana Hama                                                             |                                |                   |             | CMOS, HNIL (see Figure 4)                                                                                                               |

| High (Double logic "1")                                                            |                                |                   |             | +2.4 V to +5 V (up to 10 TTL Load)                                                                                                      |

| Low (positive logic "0")<br>Pulse Width                                            |                                |                   |             | < 0.4 V P -16 mA Sink Current                                                                                                           |