# A Proposed WIDAR Correlator for the Expansion Very Large Array Project:

# Discussion of Capabilities, Implementation, and Signal Processing

NRC-EVLA Memo# 001

Brent Carlson, May 18, 2000

National Research Council of Canada, Herzberg Institute of Astrophysics

#### **ABSTRACT**

A new architecture has been developed for the Expansion Very Large Array (EVLA) correlator project. This architecture is called WIDAR—an acronym for Wideband Interferometric Digital ARchitecture—and it uses novel digital filtering, anti-aliasing, and decorrelation methods to efficiently process wide bands with high spectral resolution and high spectral dynamic range. Additionally, the WIDAR technique permits fully digital 1/16<sup>th</sup> sample geometric delay compensation. The correlator must correlate up to eight, 2 GHz basebands from each of up to 40 antennas. In the proposed system, 16384 spectral channels are available per baseline to be flexibly deployed across one or more 2 GHz basebands. In narrowband modes, up to 1/4 million spectral channels can be deployed across one or more digitally filtered sub-bands. A full 4-bit system is envisioned that, along with decorrelation techniques, will enable greater than 10<sup>3</sup> spectral dynamic range even in the presence of powerful narrowband signals. This is important for the EVLA since it must, at some frequencies, operate in a severe interference environment. High spectral dynamic range and high spectral resolution allows for post-correlation interference excision where spectral channels containing interference are simply nulled out after correlation. This is a straightforward and effective method for dealing with interference in continuum observations. An upgrade path is available to allow the correlator to use adaptive interference cancellation techniques should such techniques eventually prove to be feasible. The architecture is well suited to providing fully digital phased-array capabilities where the VLA antennas will be phased together for high sensitivity VLBI. This document describes the correlator's capabilities and proposes an implementation of the correlator system for the EVLA. In the appendices it describes in some detail WIDAR signal processing and presents representative simulation results that clearly illustrate the performance capabilities of the correlator. This is a working document that is intended to stimulate further discussion and refinement.

## **Table of Contents**

| 1 EX           | XECUTIVE SUMMARY                                  | 11 |

|----------------|---------------------------------------------------|----|

| 2 SI           | IMPLIFIED CORRELATOR SYSTEM LAYOUT                | 14 |

| 3 O            | BSERVING MODES                                    | 16 |

| 3.1            | The Observer's View of the Correlator             | 16 |

| 3.1.1          |                                                   |    |

| 3.1.2          | · · · · · · · · · · · · · · · · · · ·             |    |

| 3.1.3          | Baseline Correlations                             | 17 |

| 3.2            | Observing Mode Nomenclature                       | 18 |

| 3.3            | Representative Observing Mode Tables              | 20 |

| 4 PI           | ROPOSED HARDWARE ARCHITECTURE                     | 29 |

| 4.1            | Architecture Overview                             | 29 |

| 4.2            | Individual Hardware Module Descriptions           | 34 |

| 4.2.1          | Station Board                                     | 34 |

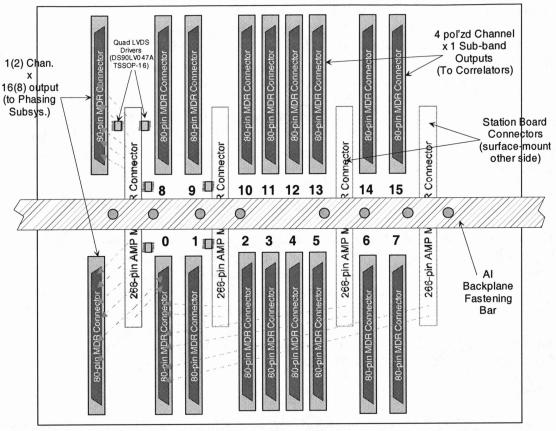

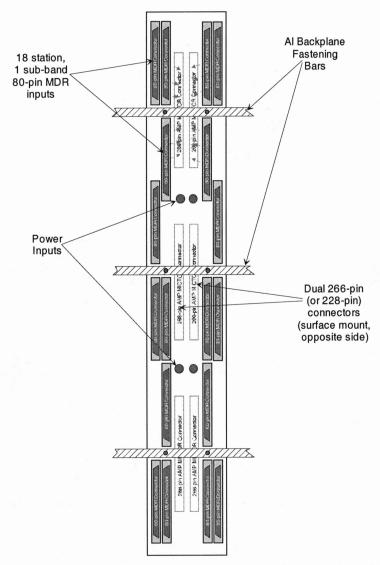

| 4.2.2          | Sub-band Distributor Backplane                    | 39 |

| 4.2.3          |                                                   |    |

| 4.2.4          |                                                   |    |

| 4.2.5          | J - r -                                           |    |

| 4.2.6          |                                                   |    |

| 4.2.7          |                                                   | 49 |

| 4.2.8          |                                                   |    |

| 4.2.9          | 0 1                                               |    |

| 4.2.10         | 0 EVLA Phasing Board                              | 52 |

| 4.3            | Correlator Rack Layout                            | 54 |

| 4.4            | Data, Model, and Timing Formats                   |    |

| 4.4.1          | <b>7</b> <del>6</del>                             |    |

| 4.4.2          |                                                   |    |

| 4.4.3<br>4.4.4 |                                                   |    |

| 4.4.4          |                                                   |    |

| 4.4.5          |                                                   |    |

| 4.4.7          |                                                   |    |

| 4.5            | Power System, Hot Swapping, and Remote Monitoring | 66 |

| 4.5.1          | Power System Design                               |    |

| 4.5.2          |                                                   |    |

| 4.5.3          |                                                   |    |

| 4.5.4          | 11 0                                              |    |

| 4.5.5          | •                                                 |    |

|                | -                                                 |    |

| 5                        | PRELIMINARY COST ESTIMATE                        | 71          |

|--------------------------|--------------------------------------------------|-------------|

| 6                        | CONCLUSIONS                                      | 73          |

| 7                        | REFERENCES                                       | 74          |

| 8 ,                      | APPENDIX I – WIDAR SIGNAL PROCESSING             | 75          |

| 8.1                      | Basic WIDAR Technique                            | 75          |

| 8.2                      | Sub-band Cross-power Amplitude Corrections       | 78          |

| 8.3<br>8.3<br>8.3<br>8.3 | 3.2 Total Power (Geometric Mean)                 |             |

| 8.4                      | Aliased Transition Band Decorrelation            | 87          |

| 8.5                      | Quantization Noise Decorrelation                 | 89          |

| 8.6                      | Digital Mixer Phase Dithering                    | 91          |

| 8.7                      | Digital Sub-sample Delay Interpolation/Tracking  | 93          |

| 8.8                      | Phased-Array Operation with WIDAR                | 94          |

| 8.9                      | Adaptive Interference Cancellation               | 90          |

| 8.10                     | Windowing                                        | 97          |

|                          | APPENDIX II – REPRESENTATIVE WIDAR CORRELATOR SI |             |

| 9.1                      | Simulation Methods                               | 100         |

| 9.2                      | Plots of Some Simulation Results                 | 103         |

| 10                       | GLOSSARY OF TERMS                                | <b>12</b> 1 |

| 11                       | INDEX                                            | 126         |

## **Table of Figures**

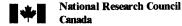

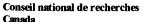

| Figure 2-1 Simplified correlator system layout. The station electronics takes 8, 2 GHz basebands from each antenna and produces 16 sub-bands for each baseband. The output of each sub-band goes to an 8BB sub-band correlator where all of the correlations for that sub-band are performed                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

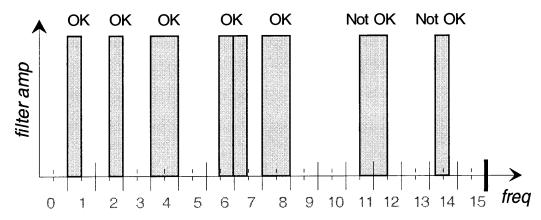

| Figure 3-1 Example allowed and not allowed sub-band filter placements for 1/16 and 1/32 bandpass slots.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

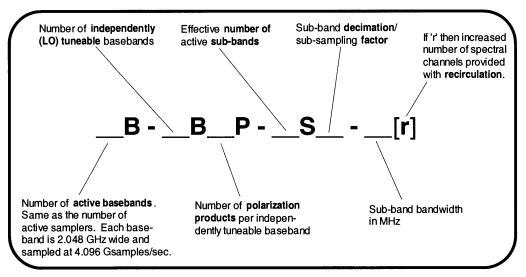

| Figure 3-2 Observing Mode Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 4-1 Proposed WIDAR EVLA Correlator overall hardware architecture showing the number of instances required for each module for the full correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

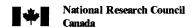

| Figure 4-2 Proposed WIDAR digital phasing subsystem. Each phasing board produces phased output for multiple sub-arrays and one sub-band of one baseband                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

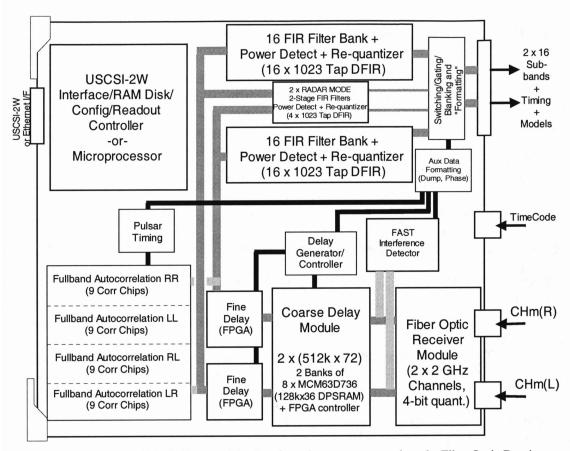

| <b>Figure 4-3</b> Station Board block diagram. The data from the antenna enters into the Fiber Optic Receiver Module where it comes out in N=16 time-demultiplexed format. From there it goes into the coarse delay module and fine delay that performs delay compensation to +/- 0.5 samples at the 4 Gs/s rate. FIR filters then generate sub-bands at up to 256 Ms/s each                                                                                                                                                                                                                                                                                      |

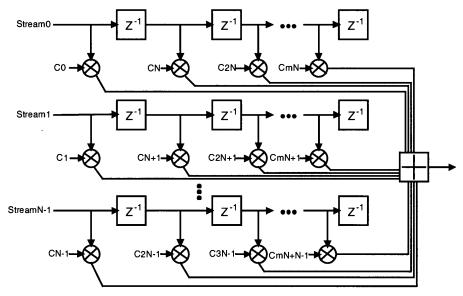

| Figure 4-4 DFIR (Demultiplexed FIR) chip architecture. Bandpass filtering and decimation results in an efficient parallel architecture. Note that a DFIR chip could be cascaded in width and length for larger N and/or more taps                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4-5 The Station Sub-band Distributor Backplane. This backplane re-routes the data so that each of 16 cables going to the correlator contain all of the data, timing, models, and synchronization for one sub-band. Cables going to the Phasing Subsystem are arranged to carry multiple sub-bands from 1 (or 2) baseband pairs                                                                                                                                                                                                                                                                                                                             |

| Figure 4-6 Example 45-station baseline matrix. Each correlator board does 81 baselines, requiring input from 9 'X' stations and 9 'Y' stations for a total of 18 stations. 15 correlator boards are required to do all baselines                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4-7 Station Data Fanout Board. This board fans out data from one station (all basebands, one subband) to up to 5 correlator (Baseline) boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

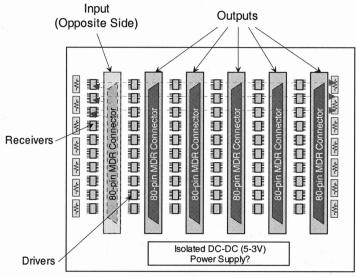

| <b>Figure 4-8</b> Baseline Entry Backplane. This backplane routes the data from up to 18 stations (all baseband pairs, one sub-band) to a Baseline Board. This board contains no drivers or active circuitry42                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

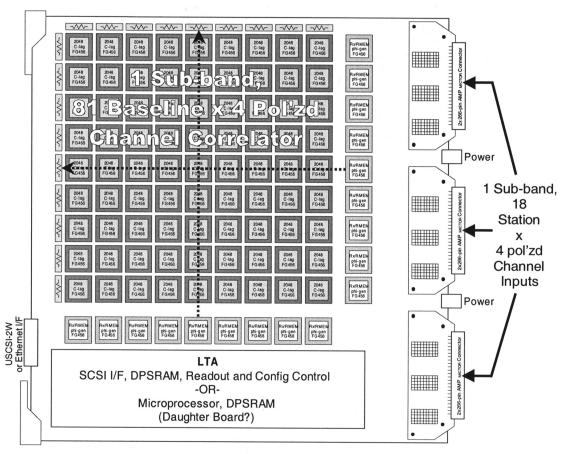

| Figure 4-9 Baseline Board layout/block diagram. The board shown does 81 baselines with 18 station inputs although for a 40-station correlator it may be better to do 64 baselines with 16 station inputs. Data from each station goes to a receiver chip complete with recirculation memory, a delay-to-phase lookup table, and drivers to be able to drive correlator chips on a tapped transmission line as shown                                                                                                                                                                                                                                               |

| Figure 4-10 Proposed cross-correlator architecture. The phase is carried with data and final fringe rotation is performed at each lag. Since the phase rates are small compared to the sample rates, the phase does not contribute to the power dissipation of the device. If, as in other VLBI XF correlator chip architectures, the Y-station in-phase and quadrature data is generated with a fringe rotator at one end of the delay line, additional power will be generated by the chip as it carries the now quickly changing complex data along the delay line                                                                                             |

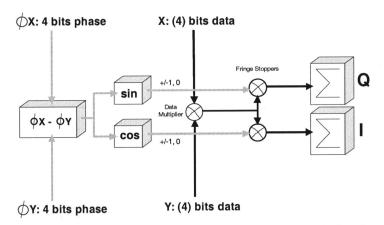

| <b>Figure 4-11</b> Correlator chip lag. 4-bit quantized phase is differenced to form the baseline phase. This goes into sin and cos lookup tables whose outputs are +/-1 and 0 for 3-level fringe rotation or +/-2, +/-1, and 0 for 5-level fringe rotation. 5-level fringe rotation achieves a 6 to 8 dB improvement in spectral dynamic range in the presence of strong narrowband signals compared to 3-level fringe rotation. This design has an advantage in that only one 4-bit multiplier is required—which is then further qualified by a shift and/or sign change in the fringe stopper. This could have a significant impact on the feasibility of a 4- |

| bit correlator chip. A full 4-bit/15-level system with 5-level fringe rotation incurs a total sensitivity loss of about 1 – (0.985*0.985*0.975) = 5.5%                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-12 Phased EVLA Station Breakout Board. This board breaks out multi-sub-band data for one baseband to individual connectors which can then each be routed to one Phasing Board                                                                                                                                                                                                                                                                                                                                                                                           |

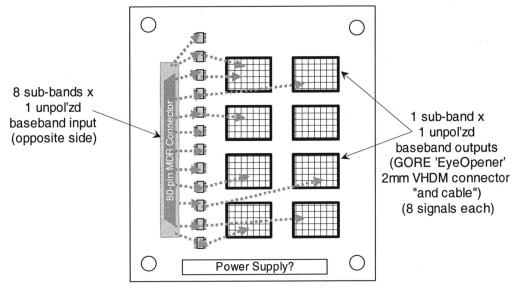

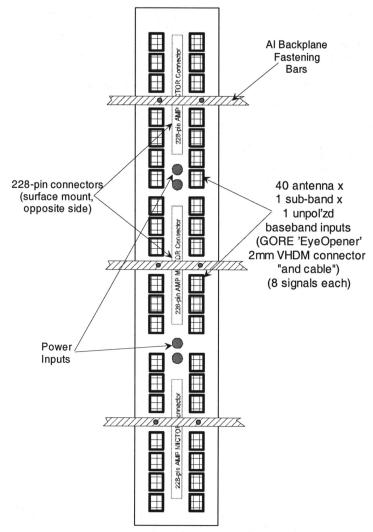

| Figure 4-13 The EVLA Phasing Board Backplane. This board facilitates entry of data from 40 stations—1 sub-band of one baseband (one sample stream) from each station—into a Phasing Board                                                                                                                                                                                                                                                                                                                                                                                        |

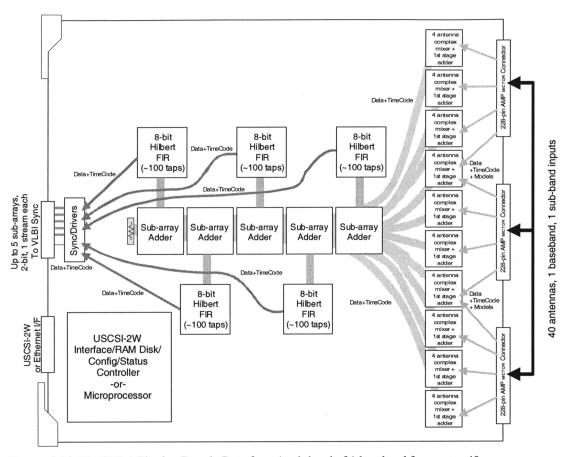

| Figure 4-14 The EVLA Phasing Board. Data from 1 sub-band of 1 baseband from up to 40 antennas/stations are phased together in one or more sub-arrays. The board is completely digital, and if the VLBI clock is locked to the VLA clock, does not require a D/A and A/D step                                                                                                                                                                                                                                                                                                     |

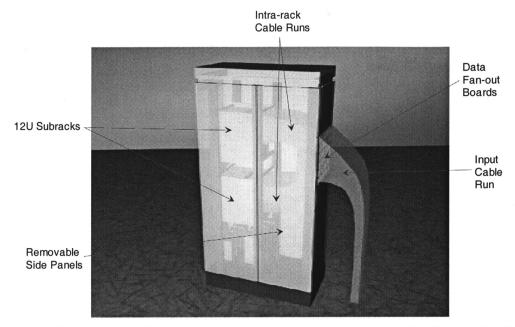

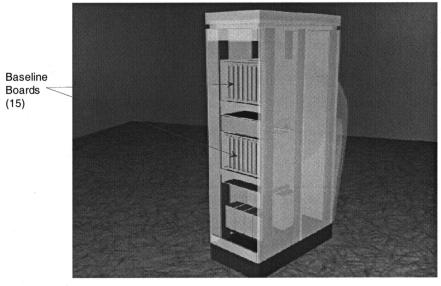

| Figure 4-15 Side-view of possible layout of a sub-band correlator rack containing Baseline Boards. The blue "ducting" are cable runs for the sub-band data cables coming from the Station Boards (Sub-band Distributor Backplane). Each sub-rack contains up to 8 Baseline Boards. There will be 16 such baseline racks and 10 similar station racks in the correlator system.                                                                                                                                                                                                   |

| Figure 4-16 Front-view of possible layout of a sub-band correlator rack containing Baseline Boards 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

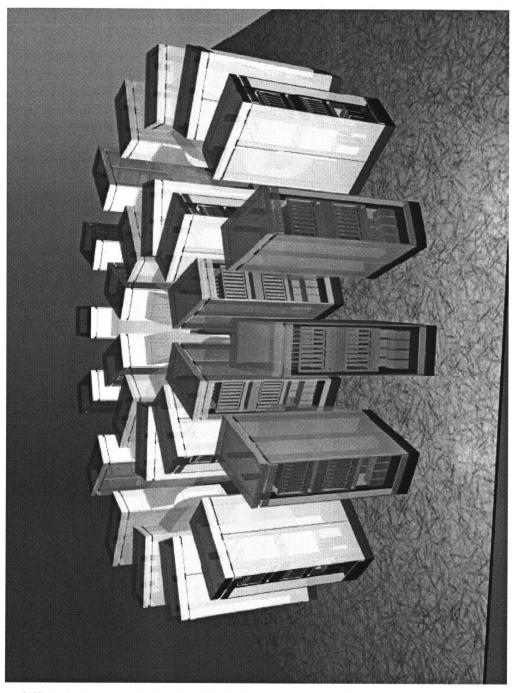

| Figure 4-17 Artist's concept of what the full correlator system might look like. The inner racks are station racks and the outer ones are baseline racks. This arrangement may be useful to keep station-to-baseline cabling reasonably phase-matched and of minimum length for best signal fidelity                                                                                                                                                                                                                                                                             |

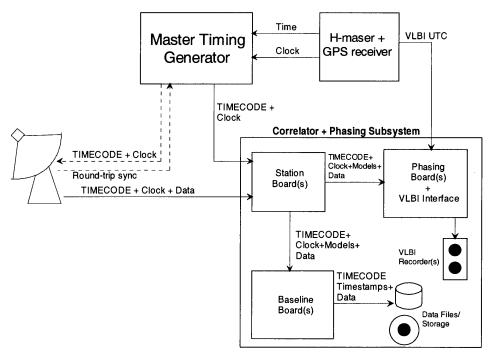

| Figure 4-18 Simplified EVLA timing diagram. The dotted lines are conceptual and beyond the scope of this document. The correlator is fed with a TIMECODE signal and 256 MHz clock that is locked to the sampler clocks and (probably) ultimately a Hydrogen Maser time standard. TIMECODE gets distributed to Baseline Boards and Phasing Boards along with the data from the Station Boards                                                                                                                                                                                     |

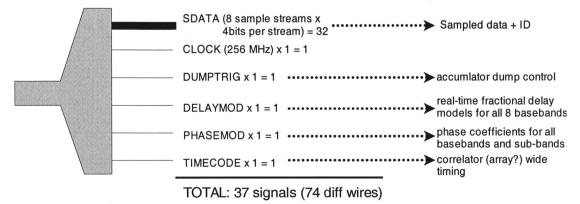

| Figure 4-19 Sub-band cable output. All signals are (differential) LVDS and fit on one commercially available GORE cable. The data and clock rates are always at a constant frequency of 256 MHz                                                                                                                                                                                                                                                                                                                                                                                  |

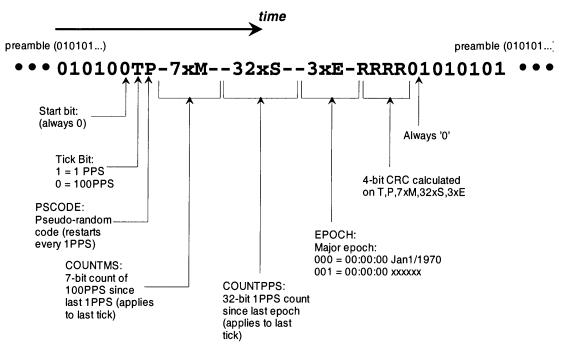

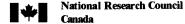

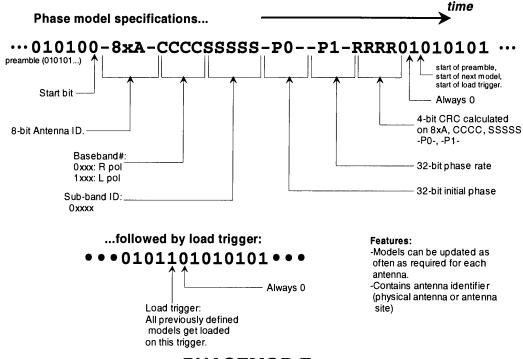

| Figure 4-20 Proposed TIMECODE format. This signal contains all absolute timing information required by the correlator. TIMECODE gets generated at one location and propagates through the correlator (and, perhaps, the entire array) with the data. All actions within the correlator use this as a reference, and all output data gets timestamped with timestamps using TIMECODE as a reference. TIMECODE requires an additional 256 MHz clock signal. 1PPS is a tick that occurs once per second, and 100PPS is a tick that occurs 100 times per second                      |

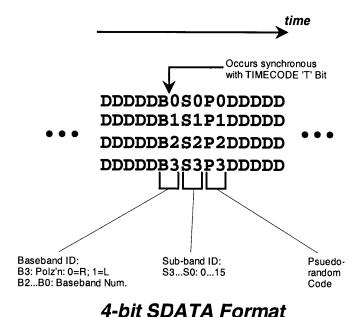

| <b>Figure 4-21</b> Proposed SDATA (Sampled DATA) format. Identifiers embedded in the data are synchronized to TIMECODE. The data is (nominally) 2's complement notation from -7 to +7 with the unused -8 state being used for flagging invalid or gated data. The embedded data will be set to the -8 state before going to the correlator chip so that no false correlation of embedded information occurs                                                                                                                                                                      |

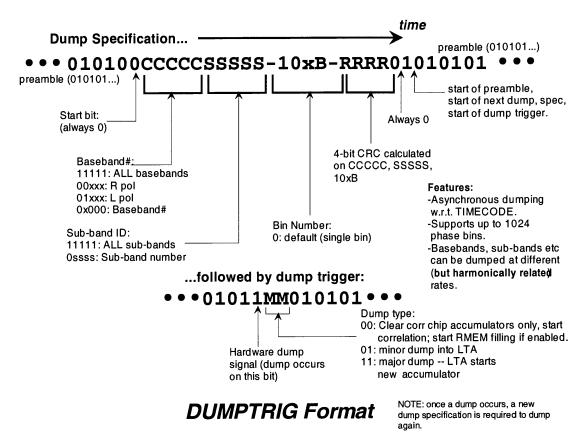

| Figure 4-22 Possible DUMPTRIG format. With this format, dumps that are to be performed are set up and then executed with a "dump trigger". Dumping can occur synchronized to pulsar timing or external events. All of the dump control signals are embedded in the signal including capabilities for phase binning and long-term accumulation. Dumping of each sub-band within each of the 8 basebands can be different but it is necessary for dump timing within a given station to be harmonically related. When data gets dumped, it is timestamped with TIMECODE timestamps |

| Figure 4-23 Proposed DELAYMOD format. The signal contains real-time delay models for all 8 basebands. There is a synchronization bit every 100PPS that is synchronized to TIMECODE so that proper framing can be done. The 8 bits of fractional sample delay is for very fine delay in the EVLA. The additional 2 bits of integer sample delay is for VLBI.                                                                                                                                                                                                                      |

| Figure 4-24 Proposed PHASEMOD format. This signal contains the phase generator coefficients for all basebands and sub-bands for the station. It also contains an Antenna ID that uniquely identifies the source of the data (i.e. in the cable the PHASEMOD signal is part of).                                                                                                                                                                                                                                                                                                  |

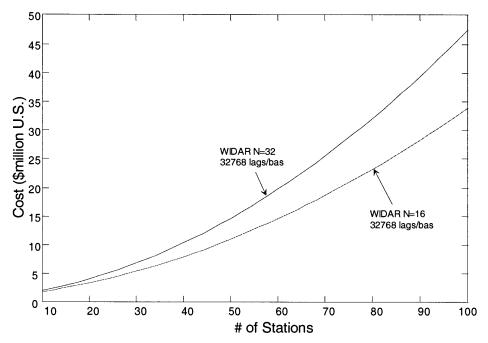

| <b>Figure 5-1</b> Total cost curve for an N=16 and N=32 WIDAR correlator for up to 100 stations/antennas. This cost includes the phasing subsystem and NRE costs but does not include labour or explicit                                                                                                                                                                                                                                                                                                                                                                         |

| contingencies. An N=32 correlator (for the same spectral resolution) is more expensive because of the additional Baseline Boards and overhead logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

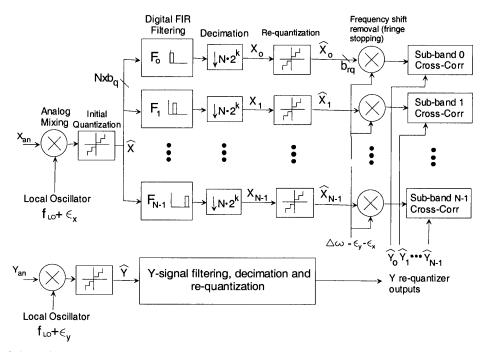

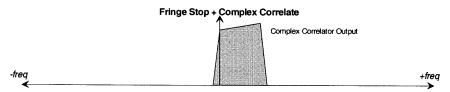

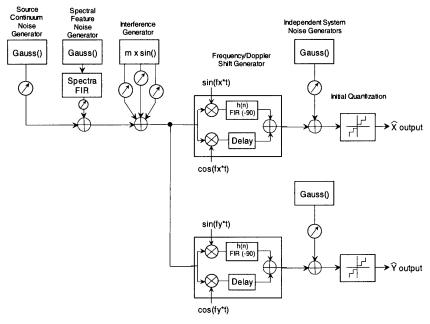

| Figure 8-1 Basic WIDAR signal processing block diagram. There is a different Local Oscillator offset in each antenna. This offset is removed in the correlator, causing aliasing to decorrelate and allowing digital filter generated sub-bands to be seamlessly stitched together to produce the wideband result. It is important to note that the mixers in the correlator are simple digital multipliers. In an XF correlator, the mixers use either 3-level, or as proposed for the EVLA correlator, 5-level approximations to sine and cosine functions—a standard technique in VLBI.                                                                                                                                                                                 |

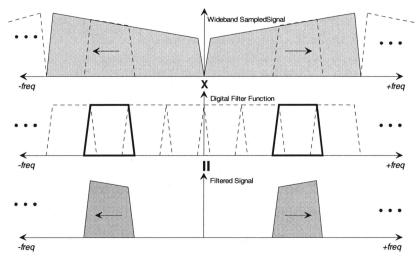

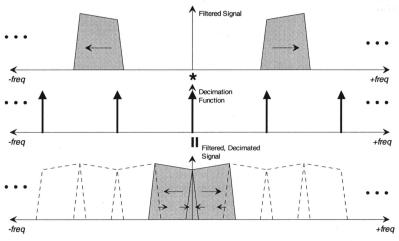

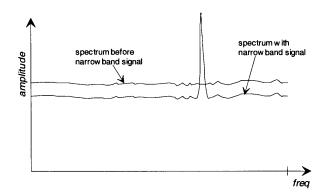

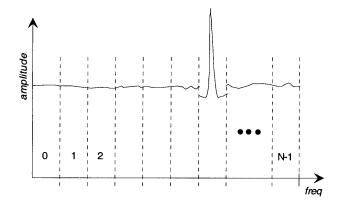

| Figure 8-2 Basic sub-band filtering operation. The wideband sampled signal is shown in the top of the figure. The slope in the bandpass is just used to indicate frequency sense. The arrows indicate the direction of the frequency shift from the Local Oscillator which is different in each antenna. The middle of the figure shows the digital filter function in the frequency domain. The bold is the bandpass that's going to be used for this sub-band and there are N=4 possible sub-bands, the outline of the others shown in dotted lines. The bottom of the figure shows the filtered sub-band before decimation—a signal that is not actually available anywhere since filtering and decimation occurs in one step for FIR filter implementation simplicity. |

| Figure 8-3 Sub-band decimation. The bandpass filtered signal is mixed to the new baseband with the decimation/sub-sampling function. In this case, since the bandpass is on an even frequency slot (slot 2 of 4—counting from 0), the signal shows up with the same frequency sense. If the bandpass was on an odd slot, then the frequency sense would be flipped and can be corrected by changing the sign of every other sample. The arrows show the frequency sense of the main part of the passband and the different aliased and non-aliased transistion bands.                                                                                                                                                                                                      |

| Figure 8-4 The final integrated cross-power spectrum of the sub-band from the previous figures. The aliased transition bands decorrelate and all that is left is the desired sub-band. Note that in this example, the transistion bands overlap into frequencies outside the strict sub-band boundaries. This overlap correlates, suffers $\sqrt{2}$ SNR degradation, but provides the required information to allow adjacent sub-bands to be seamlessly stitched together.                                                                                                                                                                                                                                                                                                |

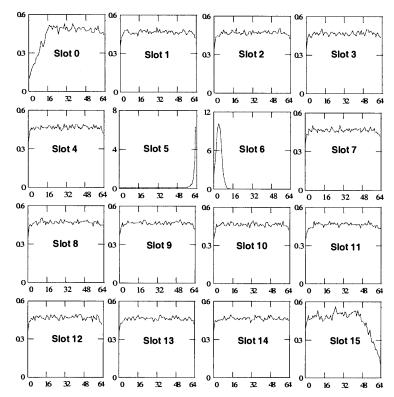

| Figure 8-5 Example plots of individual sub-band spectra. In each plot, the vertical axis is correlation coefficient amplitude, and the horizontal axis is frequency bin number. These are individual sub-band correlator results before applying the sub-band correction terms. Note the amplitude scales of the individual sub-bands. Also, the transition band roll-off is visible in each case                                                                                                                                                                                                                                                                                                                                                                          |

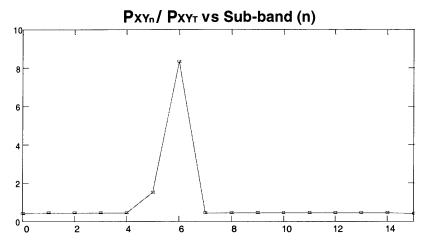

| <b>Figure 8-6</b> Plot of the sub-band scaling term for every sub-band for the correlations shown in Figure 8-5. $P_{XYT}$ arithmetic mean total power normalization is used and, because of the powerful narrowband line, continuum sub-bands are depressed by this term and sub-bands containing the narrowband signal are amplified (i.e. depressed and amplified compared to the amplitudes shown in the previous figure)                                                                                                                                                                                                                                                                                                                                              |

| Figure 8-7 Example corrected and stitched-together WIDAR correlator data (from Figure 8-5) and reference (ideal wideband) correlator data. Sub-bands can be seamlessly stitched together once the WIDAR correction equation has been applied to each sub-band. In this case, the arithmetic mean total power normalization is used                                                                                                                                                                                                                                                                                                                                                                                                                                         |

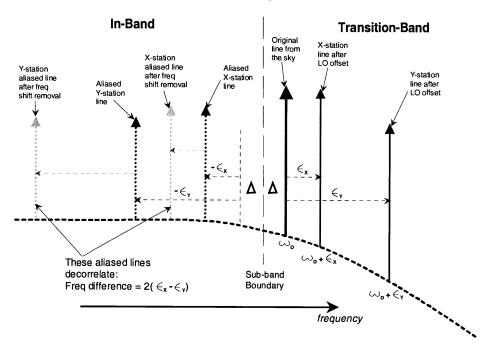

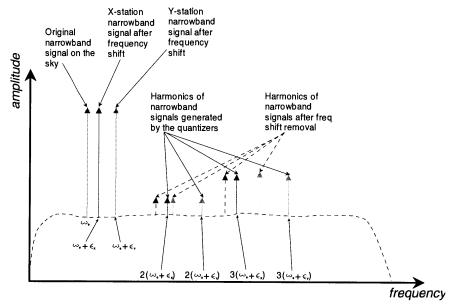

| Figure 8-8 Diagram illustrating how, with sine waves ( $\delta$ functions in the frequency domain), the aliased transition band decorrelates. The solid signals are the originals, and the dotted signals are the aliased components. The "Original line from the sky" does not actually exist in the system except in the integrated cross-power spectrum. A fine point to note is that the Local Oscillator frequency shifts should be in the same direction (same sign), otherwise the aliased components move closer together after fringe stopping in the correlator—reducing the desired decorrelation effect.                                                                                                                                                       |

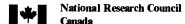

| <b>Figure 8-9</b> Fringe washing decay (decorrelated amplitude) versus integration time for a 10 kHz X and Y antenna Local Oscillator frequency difference. For comparison, the noise decay is shown for a ~250 Ms/s sample rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 8-10 Decorrelation of quantizer generated harmonics. Harmonics of narrowband signals decorrelate since the frequency shift that they have is the Local Oscillator shift times the harmonic number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

NAC - CNAC

| When the frequency shift is removed in the correlator, it prevents the harmonics from overlapping in frequency and therefore prevents them from correlating                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

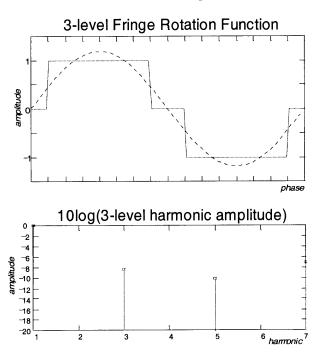

| <b>Figure 8-11</b> 3-level fringe rotation/digital mixer function time domain (top) and frequency domain (bottom) representations. The dotted line in the top plot is a perfect sine wave that the digital function is trying to model. Harmonics of the digital mixer are about 6 dB lower than the fundamental. Note that even though the digital mixer function is a voltage, only 10log() of the harmonic amplitude is used to obtain its performance since the mixer is a "one sided" voltage multiplier in the correlator chip90                                                               |

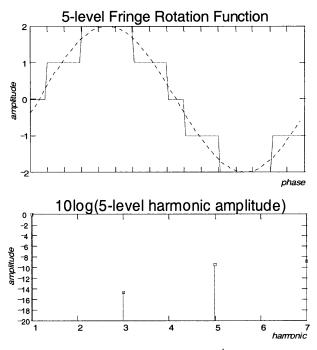

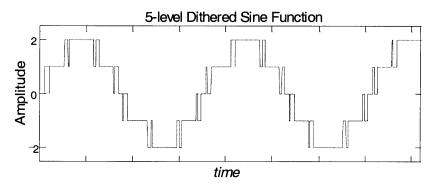

| Figure 8-12 5-level fringe rotation/digital mixer function. The 3 <sup>rd</sup> harmonic is about 8 dB lower in this function than the 3-level function. This will enable the WIDAR correlator to generally provide about 14 dB better spectral dynamic range than a correlator without frequency shifting. This is especially important in the presence of powerful narrowband signals. The 5-level fringe rotation function also reduces the sensitivity loss in the correlator to about ½ the 5% loss from a 3-level function                                                                     |

| Figure 8-13 5-level dithered sine function produced when baseline phase is formed from differencing quantized station-based phase. The Local Oscillator offsets should be chosen so they are not harmonically related to ensure that phase dithering always occurs in order to avoid possible modulation of correlator amplitudes if phase differencing wanders in and out of dithering                                                                                                                                                                                                              |

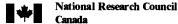

| <b>Figure 8-14</b> Fully digital sub-sample delay tracking is realized with the WIDAR correlator. Integer delay tracking at the wideband sample rate introduces a phase slope that is 0 at DC and alternates between +/-90° at the upper edge of the band. When sub-band filtering is performed, the phase excursion within the sub-band due to the wideband tracking is $1/16^{th}$ (N=16) of the wideband plus a phase offset that changes with delay. The phase offset is tracked by offsetting the phase of the fringe rotators in the correlator94                                              |

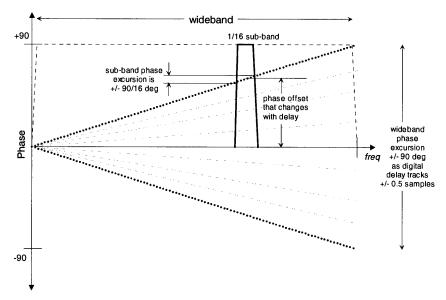

| Figure 8-15 Phased-array operation with WIDAR. FIR filter sub-band outputs (which could be the same ones used for correlation) go to complex mixers where the frequency shift (and antenna Doppler shift) is removed with many-level sine and cosine functions. The complex data from all antennas in the phased-array are then added together—the results of which get converted to simple data with a -90° phase shift (implemented in a Hilbert FIR filter) and add as shown. Finally, the simple data is requantized (if desired and not shown in the figure) for further processing             |

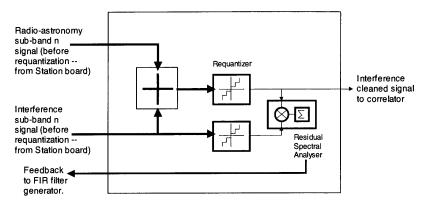

| Figure 8-16 Block diagram of an adaptive cancellation add-on to the correlator. The radio astronomy signal is added to a cancellation signal containing only the inverted interference signal. The result is requantized and compared with the cancellation signal to allow fine-tuning of the cancellation signal amplitude. Ideally, the interference-cleaned signal that goes to the correlator contains no interference 96                                                                                                                                                                       |

| Figure 9-1 Simulator's noise generator block diagram. Common noise, spectral features, and interference that will correlate goes into separate frequency shift generators implemented as digital single-sideband mixers. Independent/uncorrelated noise is added to the frequency shift data before initial quantization. All operations before initial quantization are double precision floating-point                                                                                                                                                                                             |

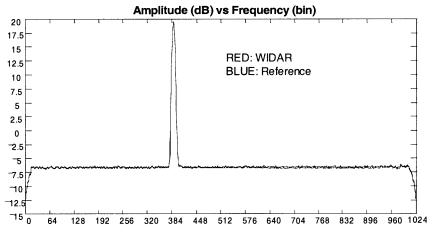

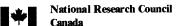

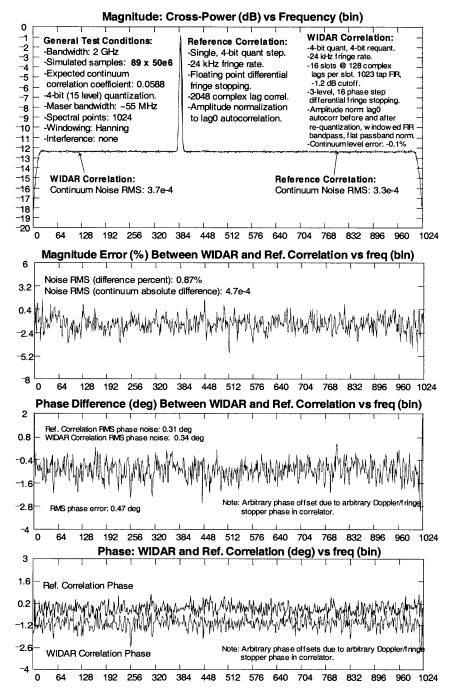

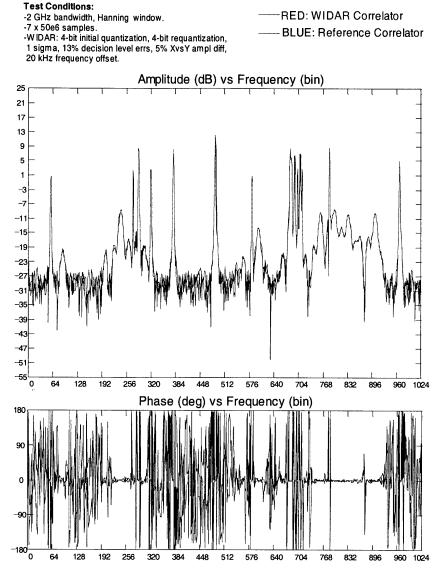

| Figure 9-2 Continuum and strong maser simulation with independent test vectors. The WIDAR amplitude was normalized using the "Sub-band Power" method for $P_{XYT}$ so that the correct continuum level is obtained in the presence of the strong narrowband signal. Only one integration of 500 million samples was simulated—the degradation of the noise generator is seen in the ragged spectra near the edges of the band. Window method #2 is used                                                                                                                                              |

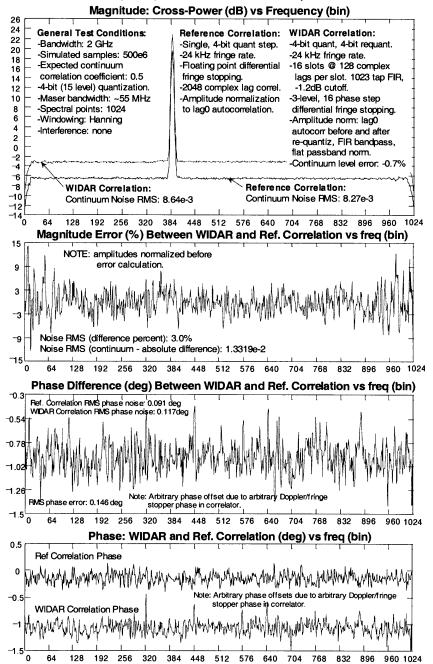

| Figure 9-3 Continuum and strong maser simulation with <i>identical</i> test vectors. This is the same as the previous figure only the test vectors into the reference correlator and the WIDAR correlator are the same—resulting in a very sensitive test. In this case, noise waveforms are being compared—resulting in seemingly large amplitude differences at sub-band boundaries since this is where aliased and decorrelated independent noise will be present (i.e. the aliased transistion band represents independent noise compared to the reference correlator). Window method #2 is used |

| Figure 9-4 Continuum and weaker narrowband signal. 89 dumps of 50 million samples each were incoherently integrated to produce this result. The noise behaviour is better than the previous two plots. Independent test vectors were used and different noise generator seeds were used for each dump. Arithmetic mean total power normalization was used for both correlation results                                                                                                                                                                                                               |

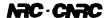

| <b>Figure 9-5</b> Continuum with narrowband signal and narrowband interference. WIDAR does a good job with unresolved lines that are on sub-band boundaries like the interference line near frequency bin 320. This simulation integrated 100 dumps of 50 million samples each—125 milliseconds of real-time correlator time at 4 Gs/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 9-6</b> Continuum with narrowband line and uncorrelated interference (in the same locations as the previous figure) in the X-station only. This demonstrates that the WIDAR normalization equation can stitch together sub-bands even though there may be some narrowband power that does not correlate. Ten dumps of 50 million samples each were integrated for this test                                                                                                                                                                                                                                                                                                                                                                                                                      |

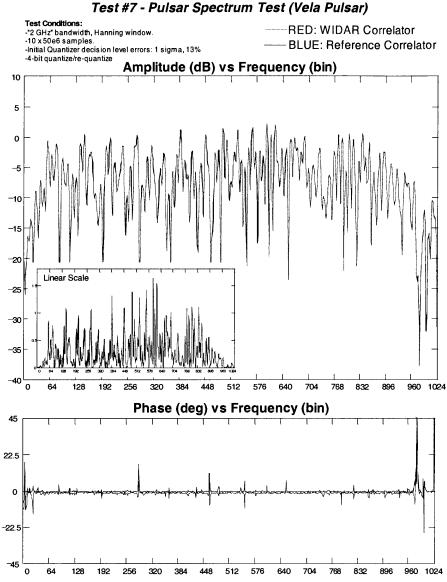

| <b>Figure 9-7</b> Simulation of the on-pulse spectrum from a real pulsar. The actual bandwidth of this spectrum is 16 MHz, but in the simulator it is used as 2 GHz (its all discrete-time so it doesn't matter). Significant phase differences occur where the power is weak and therefore noisy—as expected. This spectrum was chosen for simulation because of its complex amplitude shape                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Figure 9-8</b> High dynamic range test with a number of (FIR filter generated) narrowband lines and interference lines (sine waves). The WIDAR correlator does as well as the reference correlator (4-bits, floating-point fringe stopping) except at about frequency bin 20. This artifact was later found to be due to digital mixer (fringe stopper) harmonic correlation with re-quantizer generated narrowband harmonics. In this test a 3-level fringe stopper was used—5-level fringe stopping would yield better results                                                                                                                                                                                                                                                                        |

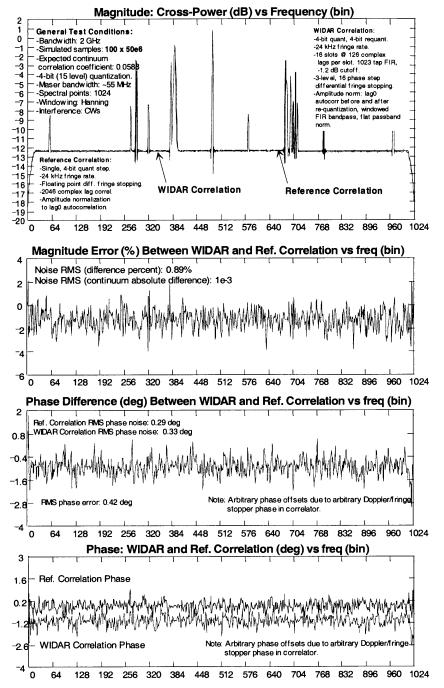

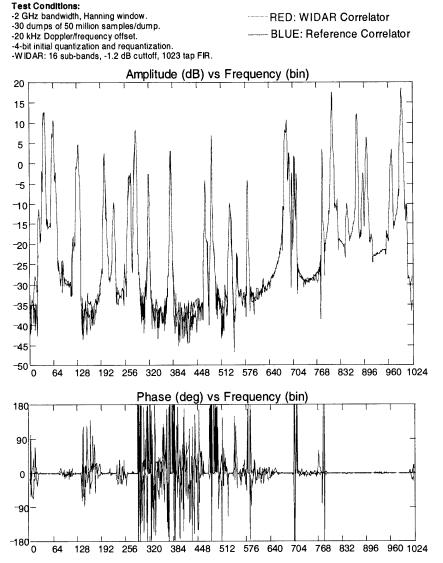

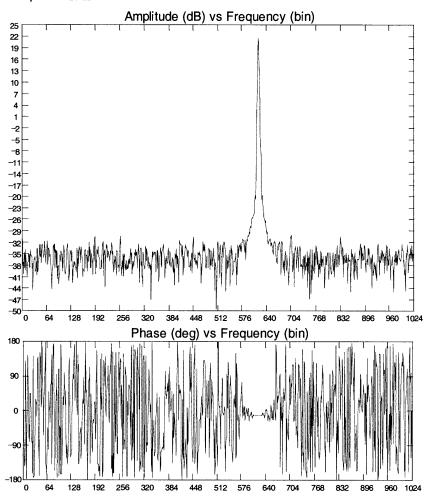

| Figure 9-9 Very high dynamic range test comparing WIDAR correlator results and fullband/wideband correlator results without frequency shifting. The decorrelation effect is clear. The fullband correlation result is the best that could be achieved in this "pathological" case with a full 4-bit correlator without frequency shifting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 9-10 High dynamic range absorption spectrum. The spectral shape was generated with the noise generator's FIR filter. Differences between WIDAR and the reference correlator occur where the signal is weak—as expected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

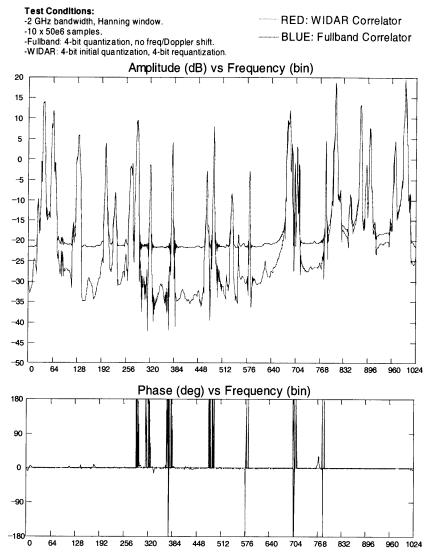

| Figure 9-11 This high dynamic range and high SNR broad spectral structure test compares WIDAR correlation results with a fullband/wideband correlator with no frequency shifting. The decorrelation effect yields better results (see bins 384 to 448) but, as it turns out, not quite as good in this case as the reference correlator. Three-level fringe stopping was used in the WIDAR correlator. The rather artificial-looking structure was generated with the noise generator's FIR filter                                                                                                                                                                                                                                                                                                         |

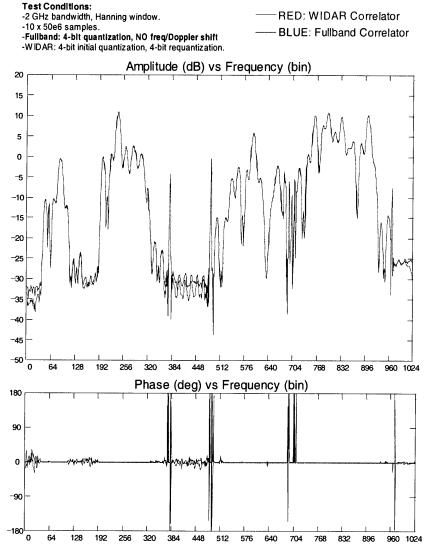

| Figure 9-12 Lower SNR broad spectral structure test comparing the WIDAR correlator results with the reference correlator with floating-point fringe stopping. This plot illustrates that there are no strange effects occurring at the sub-band boundaries where there is no correlation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9-13 WIDAR correlator simulation results with a single "+33 dB maser". This is a test that clearly illustrates the spectral dynamic range limitation of the WIDAR correlator in the presence of powerful narrowband signals. About 90% of the total power in the band (going into the initial quantizer) is contained within this "+33 dB maser". The dotted line is simulation results for a fullband 4-bit correlator without frequency shifting. The spectral dynamic range improvement with WIDAR is clear. The "skirting" of the narrowband line starting at about -20 dB is due to an effect of the noise generator FIR filter. This effect is not entirely known but does occur with very narrow FIR bandpasses and is not predicted by the Fourier transform of the FIR's tap coefficients. |

| <b>Figure 9-14</b> WIDAR correlator simulation results with a single "+23 dB maser". In this case, about 30% of the total power going into the quantizer is contained within the narrowband signal. This simulation ran for several weeks and, because of the relatively low SNR, the noise was only "beaten-down" to demonstrate a spectral dynamic range of about 50 dB. Harmonics of the narrowband signal are not detectable in this simulation. In this case, it would take a few <i>years</i> of simulation to drop the noise level to be able to demonstrate 60 dB of spectral dynamic range                                                                                                                                                                                                        |

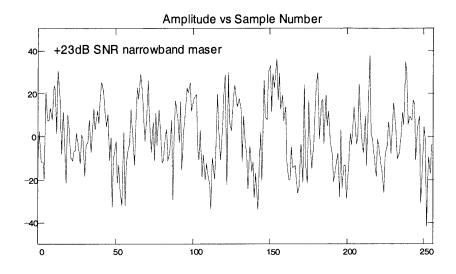

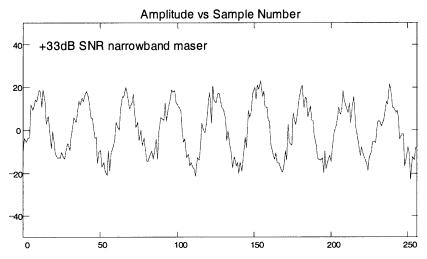

| <b>Figure 9-15</b> Plots of voltage waveforms (for +23 dB and +33 dB narrowband line tests) into the initial quantizer. For these plots, the line was moved down in frequency so the sine-wave pattern would be clear. The "+33 dB maser" plot clearly shows a sine pattern which will result in reasonably strong quantizer-generated harmonics                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

NAC CNAC

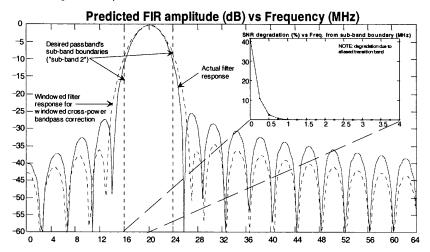

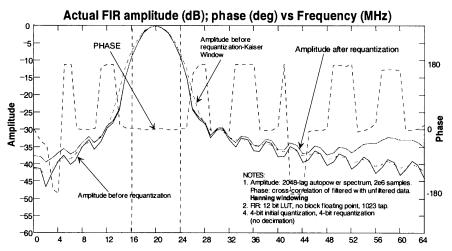

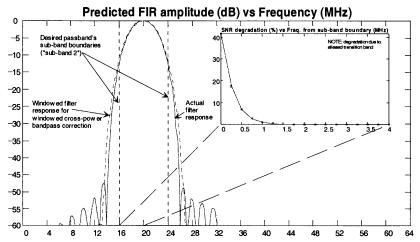

| Figure 9-16 Test of 1023-tap FIR filter with a 1/256 (of 2 GHz) bandpass. The top is the predicted FIR response from the FFT of the tap coefficients and the bottom is the actual response—including phase. Note that phase is well behaved across the entire sub-band and so all data within the sub-band can be used and properly corrected in amplitude. From this test, it seems reasonable to conclude that 1/256 bandpass filtering with 1023-tap FIR filters is feasible although the sidelobe levels in this plot may be too high 118 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

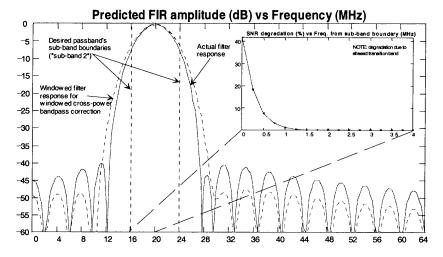

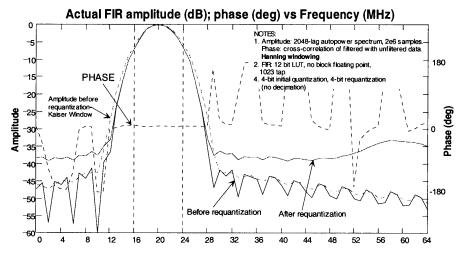

| Figure 9-17 Another test of 1/256 bandpass with a 1023-tap FIR filter. In this case, the sidelobes are lower at the expense of a wider main lobe with the penalty being a larger SNR degradation region near the sub-band boundary (insert plot in top plot)                                                                                                                                                                                                                                                                                  |

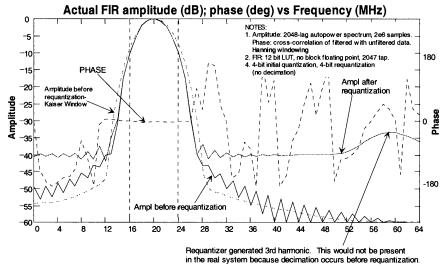

| <b>Figure 9-18</b> Test of 1/256 FIR filter response with a 2047-tap FIR filter. There is some improvement over the previous plot but the sidelobe levels are more than predicted by the FFT of the tap coefficients. This is the same "skirting" action noticed in the noise generator FIR filter when generating very narrow passbands and is not completely understood. Note that the sidelobes in the sub-bands adjacent to the passband will                                                                                             |

| da a a malata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### 1 Executive Summary

The Expansion Very Large Array (EVLA) project will significantly increase the bandwidth and number of antennas in the VLA. This will improve its sensitivity and dynamic range by at least an order of magnitude over the existing VLA. A significant part of the project is a new correlator that will have a large impact on the science output of the upgraded instrument. The new correlator must handle up to 16 GHz of bandwidth from each of up to 40 antennas and must operate in a severe interference environment. In an effort to meet these demanding requirements, a new correlator called **WIDAR** (Wideband Interferometric Digital ARchitecture) has been developed and studied in some detail. This correlator is designed to provide unprecedented signal processing capability to make maximum scientific use of the EVLA.

#### **Basic Correlator Capabilities**

The WIDAR correlator that will be described in this document will provide the following basic capabilities:

- In <u>wideband modes</u>, provide 16384 spectral channels across 16 GHz of total bandwidth (consisting of 8 x 2 GHz analog bands) on every baseline. Number of bands used and number of spectral channels per band is flexible.

- In <u>narrowband modes</u> (e.g. many programmable 8 MHz bands), provide up to <u>0.25 million</u> spectral channels per baseline. Mixed wideband and narrowband modes are possible.

- Provide 1 Hz spectral resolution in narrowband radar mode.

- Simultaneous, fully digital, phased-VLA operation for VLBI.

- <u>Spectral dynamic range</u> >10<sup>5</sup> even in the presence of powerful narrowband signals.

- Each antenna is equipped with 2 GHz baseband systems and 4 GHz samplers. *All narrowband signals* are generated in the correlator with digital filters from these wide bands, eliminating the need for costly narrowband analog baseband systems.

- Multiple sub-array capability.

#### **Interference Mitigation**

A key requirement of the correlator is that it enable the EVLA to observe in severe RF interference environments. This interference is mostly narrowband in nature and can originate from terrestrial and satellite-based sources. The WIDAR correlator plans to use the following interference mitigation techniques.

- Provide high spectral resolution and spectral dynamic range >10<sup>5</sup> even in the presence of strong narrowband signals for post-correlation interference excision.

- Generate <u>correlated output amplitudes that are immune</u> to the modulating effects of time-variable interference.

- Provide <u>real-time recognition of burst-like interference</u> with subsequent correlator inhibit capability.

- Provide a reasonable <u>upgrade path to allow installation of adaptive cancellation</u> hardware should such techniques ultimately prove to be feasible.

Using digital FIR filters to "notch out" interference has also been considered, but it was found that excessively long filters are required to provide adequate performance. Post-correlation excision seems to provide better performance given the spectral resolution and spectral dynamic range provided by WIDAR.

#### **WIDAR Signal Processing Overview**

The WIDAR correlator relies heavily on digital filtering and techniques for decorrelation of aliased signals and sampler-generated narrowband interference harmonics. Digital filters can be quickly programmed (and thus reconfigured), have linear-phase characteristics, have calculable amplitude responses, and are immune to time-variable instabilities. Details and simulation results can be found in the appendices.

The correlator back-end is an XF<sup>1</sup> VLBI correlator and, combined with Local Oscillator techniques, can handle antenna arrays with baselines from zero to thousands of kilometers. The digital filters provide the front-end that allow the XF correlator back-end to be the most efficient possible—two correlator lags always produce one spectral output point. Since the dominant cost in a large XF correlator is the baseline correlator hardware (including the correlator chips), this efficiency ensures that a cost-effective solution is always obtained where high spectral resolution is required—even for very wide bandwidths and large antenna arrays.

Finally, a unique aspect of the WIDAR correlator design is that it can provide *fully digital* sub-sample (<1/16<sup>th</sup> sample) delay interpolation—eliminating the extra complication of circuitry that modifies the phase of the sampler clocks.

#### **Cost and Power Requirements**

A reasonably detailed cost estimate indicates that the 40-station correlator presented in this document can be constructed for \$11 million U.S. This estimate includes some contingency but does not include the samplers, mains power system (UPS), or office space. A power estimate indicates that the correlator system will require about 100 kW from a power source with about a 135 kVA capacity.

<sup>&</sup>lt;sup>1</sup> The XF architecture was chosen over 'FX' because it uses minimum bandwidth in data transmission from station-based to baseline-based hardware. This results in a significant savings in cost and complexity in a large, wideband correlator.

ніл-інл

NRC-EVLA Memo# 001 13

#### **Simplified Correlator System Layout** 2

A simplified layout of the correlator system<sup>2</sup> is shown in Figure 2-1.

Figure 2-1 Simplified correlator system layout. The station electronics takes 8, 2 GHz basebands from each antenna and produces 16 sub-bands for each baseband. The output of each sub-band goes to an 8BB sub-band correlator where all of the correlations for that sub-band are performed.

In this layout, there are M stations (antennas) and each station has 8, 2 GHz basebands (each baseband is defined as the output of a 4 Gs/sec sampler). These 8 basebands (8BB) can be arranged in polarization pairs up to 4 baseband pairs (4BBP). The electronics for each station in the correlator contains 'N' sub-band digital FIR filters for each baseband. N is chosen to be 16 because resulting sub-band sample rates can be processed with existing and emerging digital technologies and there are not a significant number of sub-band boundaries. The output of a particular sub-band's filters for all basebands goes to an 8BB sub-band correlator. Thus, since N is 16, there are 16, 8BB sub-band

Canada

<sup>&</sup>lt;sup>2</sup> For a discussion as to why this correlator layout was chosen as opposed to other possible layouts, please see Section 4.2.7.

correlators. Each sub-band correlator correlates all base*lines* for all base*bands* for a particular sub-band.

The primary purpose of the sub-band filters is to split the wide 2GHz band into narrower sub-bands operating at lower sample rates than can be handled by digital hardware. WIDAR uses techniques to seamlessly stitch together the individual sub-band correlations to reproduce the wide band spectrum.

In standard wideband modes, the correlator operates as shown in Figure 2-1 and as mentioned, seamlessly stitches the sub-bands together to yield the wideband spectrum. However, if less total bandwidth is required, then each sub-band correlator can be programmed to:

- 1. <u>Correlate fewer basebands</u> and increase the spectral resolution on the basebands that are being correlated.

- 2. <u>Correlate fewer sub-bands</u>. Increased spectral resolution is obtained by using each sub-band correlator to correlate one section of the overall lag chain on fewer sub-bands.

- 3. <u>Decrease the sub-band bandwidth</u>. Increased spectral resolution is obtained by lowering the sub-band sample rate while operating the correlator at the highest sample rate possible using **recirculation** memory. A squared increase (with decreasing sub-band bandwidth) in spectral resolution is obtained using this method.

- 4. A combination of <u>one or more of the above</u>. Each sub-band filter in each baseband is programmable in width and placement<sup>3</sup> within the 2 GHz baseband.

The following sections will elaborate on the basic layout just described. The very basic concept though, is that there are 16 sub-band correlators driven by sub-band filters from each station/antenna. Each sub-band correlator can be programmed to perform different functions depending on what bandwidth and spectral resolution are required.

<sup>&</sup>lt;sup>3</sup> With a 'slot' and 'slot width' restriction explained in the next section.

....

#### Observing Modes

This section contains a description of correlator observing modes. The section starts out with a basic description of the capabilities of the correlator that observers should be cognizant of to make maximum use of the system. It then defines a nomenclature for describing observing modes and finally presents a number of tables of representative observing modes.

#### 3.1 The Observer's View of the Correlator

#### 3.1.1 Sub-arrays

The correlator produces the same correlation products on every baseline within a subarray. There can be any number of sub-arrays—each sub-array can be thought of as a separate array with its own correlator much like a separate process, or window on a UNIX computer. Separate sub-arrays can have antennas that are in common, but all baselines within any sub-array must use the same observing mode or set of modes. It is acceptable for an antenna that is common to two sub-arrays to have (for example) two observing modes active—one mode applies to one sub-array and the other mode applies to the other sub-array. It is not possible to utilize correlator resources (spectral channels/correlator chips) assigned to two antennas that are (currently) part of mutually exclusive sub-arrays.

#### 3.1.2 Antennas, Basebands, and Sub-bands

Each antenna can have up to 8, 2.048 GHz basebands (sampled at 4.096 Gsamples/sec<sup>4</sup> each). Each baseband can have its own delay/phase center on the sky and could have its own independently tunable Local Oscillator (if the actual antenna receivers are so equipped). The basebands can be arranged in up to 4 baseband (polarization) pairs.

<u>Each</u> baseband (and there are 8) of each antenna can be split with digital filters into up to 16 sub-bands. Each sub-band can be anywhere from 1/16<sup>th</sup> of the baseband bandwidth to 1/256th of the baseband bandwidth. In wideband modes, adjacent sub-bands can be seamlessly 'stitched' together to yield wider total bandwidths up to the baseband bandwidth of 2.048 GHz.

One additional 'special purpose' radar mode filter for each baseband can split the baseband into a sub-band with anywhere from  $(1/16^{th})^2$  to  $(1/256^{th})^2$  of the baseband bandwidth. Each special purpose filter—consisting of two cascaded filters—will normally be used only for the narrowband radar mode but could be used for other narrowband observing modes if desired. If this filter is active, then one of the normal sub-band filters for the baseband cannot be used.

<sup>&</sup>lt;sup>4</sup> Chosen to be compatible with standard VLBI sample rates.

Conseil national de recherches Canada

Each of the 16 sub-band filters (for each of 8 basebands) is individually programmable in bandwidth and placement within the baseband (within defined constraints). Each sub-band filter passband can only be within one of the integer 'slots' of the baseband that is the same as the bandwidth fraction of the filter. (Additionally, it is acceptable for more than one filter to occupy a given slot.) This is shown in Figure 3-1 for a sub-band bandwidth of 1/16 and 1/32 of the baseband. In the diagram there are 6 sub-band filters present—5 at 1/32 and 3 at 1/16—all of which could be within the same baseband. Slot numbering in the diagram is for 1/16 slots. The filter placements on the right of the figure are illegal.

Figure 3-1 Example allowed and not allowed sub-band filter placements for 1/16 and 1/32 bandpass slots.

**Example:** If the filter is  $1/16^{th}$  of the baseband, then the passband of the filter must be within one of the 16 integer slots of the baseband.

**Example:** If the filter is  $1/256^{th}$  of the baseband, then the passband of the filter must be within one of the 256 integer slots of the baseband.

All correlated spectra up to and including the 'slot boundaries' of the filter passband are good data except that at the channel containing the slot boundary (a.k.a. the sub-band boundary) there is a  $\sqrt{2}$  degradation in SNR (which quickly tapers off to negligible degradation within ~0.5 MHz of the edge of the sub-band in non-radar modes).

#### 3.1.3 Baseline Correlations

The correlator effectively consists of 16 sub-band correlators each of which processes sub-bands from up to 8 basebands (or up to 4 baseband pairs). Thus, each sub-band correlator could be viewed as a separately programmable correlator for each sub-array. For each baseline within each sub-band correlator there are effectively 2048 lags<sup>5</sup> (resulting in 1024 frequency points) that correlate the sub-band data from up to 8 of the basebands. If all polarization products are desired from all 4 baseband pairs, then 16 correlations must be performed—each one using 128 lags of each sub-band correlator. Additionally, in narrowband modes (e.g. 1/256<sup>th</sup> sub-band—8 MHz), there can be up to

<sup>&</sup>lt;sup>5</sup> Which is actually within one correlator chip.

National Research Council Con

32768 lags per baseline in each sub-band correlator when 'recirculation' is active. <u>The lags in each sub-band correlator can be used independently or in combination with lags from other sub-band correlators to produce an increasing number of spectral points.</u>

For one baseline within one sub-band correlator, each of the 8 basebands can be a different bandwidth (and therefore a different bit rate) and in fact in a different frequency slot in each baseband. Each of these single baseline sub-band correlators can perform 'recirculation' on only 4 basebands (or 2 baseband pairs)—a memory width limitation. It is illegal to mix recirculation and normal processing and it is illegal to mix different recirculation modes in the same sub-band correlator on the same baseline. Thus, if recirculation is active on one of these sub-band baseline correlators, then non-recirculation modes (or different recirculation modes) cannot be used at the same time on the same sub-band correlator. In this case, it is necessary to use a different sub-band correlator for the non-recirculation or different recirculation mode.

#### 3.2 Observing Mode Nomenclature

The **Observing Mode** in the following tables indicates the number of basebands, number of polarizations, number of sub-bands, and the sub-band bandwidths that are used for that mode. The <u>number of spectral channels</u> that can be used for the particular mode is very flexible and is thus <u>not part of the mode designation</u>. The Observing Mode nomenclature is shown in Figure 3-2:

Figure 3-2 Observing Mode Nomenclature

### **Example:** 8B-4B2P-16S16-128

In this example, there are 8 active basebands (8B), arranged as 4 baseband pairs (independently tuneable basebands), with 2 polarization products per baseband pair (4B2P). 16 sub-bands are used with a decimation factor of 16 (16S16). Each subband has a bandwidth of 128 MHz (128). This is the mode in the first row of Table 3-1.

#### **Example:** 1B-1B1P-1S256-8r

In this example there is 1 active baseband (1B), arranged as 1 baseband with an independently tuneable LO, with 1 polarization product (1B1P). 1 sub-band is active with decimation factor of 256 (1S256) and a sub-band bandwidth of 8 MHz (8). The 'r' designator indicates that recirculation is active in the correlator to produce a maximum number of spectral channels. This is the mode in the first row of Table 3-2.

#### Example: 1B-1B1P-1S(64x128)-0.25r

In this example, there is 1 active baseband (1B), arranged as 1 baseband with an indepedently tuneable LO, with 1 polarization product (1B1P). Narrowband radar mode is active on one sub-band (1S(64x128)) where two FIR filters are cascaded, the first with a 1/64 bandpass and the second with a 1/128 bandpass. The sub-band bandwidth is 0.25 MHz and recirculation is active (0.25r). This is the mode in the second row of Table 3-6.

#### **Example: 2B-1B2P-8S16-128**

In this example, there are 2 active basebands (**2B**), arranged as 1 baseband pair with an independently tuneable LO, with 2 polarization products (**1B2P**). Only 8, 128 MHz sub-bands per baseband are used with a decimation of 16 (**8S16-128**). This illustrates what might be specified when observing at L-band for 1 GHz of contiguous bandwidth (although there is nothing in the mode that forces the sub-bands to be adjacent). This is the mode in the 12<sup>th</sup> row of Table 3-1.

#### 3.3 Representative Observing Mode Tables

These tables define representative observing modes that the proposed correlator can provide. Each entry in the table uses the entire correlator capacity but what is not shown is that there is some flexibility in assignment or arrangement of the number of spectral channels allocated to a given cross-power result. The tables are not an exhaustive definition of what can be done with the correlator since many different modes can be combined to provide virtually an unlimited number ways of configuring the correlator.

A convenient way to use the tables is as follows:

- Step 1: Determine the desired bandwidth per final cross-power result that one is interested in. This can be found in the tables by looking at column four—labeled "BW per cross-power spectrum".

- Step 2: Decide what the desired spectral resolution is or how many frequency channels are required across the bandwidth of interest. This is found in columns six ("Spectrl resolution") and five ("Max Spectral Channels per cross-power spectrum per bsln") respectively.

- Step 3: Looking to the left across the row, the maximum number of cross-power results that can be obtained *per baseline* is in the second column ("# of cross-power")

**spctra per bsln**"). Find the number of cross-power results that are needed. Where entries from Steps 1, 2, and 3 in different rows are the same, it is necessary to look at the **Mode** to determine the desired number of baseband pairs and polarization products that are required.

**Example:** Step 1: We want a bandwidth per cross-power result of 2.048 GHz—look in column 4 to find the appropriate table. Step 2: We want 8192 frequency channels (spectral resolution of 250 kHz) per cross-power result—look in column 5 (or 6). Step 3: We want 2 cross-power results from 2 polarization products from 1 baseband pair—look in colums 2 and 1. Looking at Table 3-1, this is mode 2B-1B2P-16S16-128

| Mode                  | # of<br>cross-<br>power<br>spctra<br>per<br>bsln | Total<br>BW<br>(GHz) | BW per<br>cross-<br>power<br>spectrum<br>(GHz) | Max Spectral Channels per cross- power spectrum per bsln | Spectrl<br>res-<br>olution<br>(kHz) | Decima-<br>tion<br>Factor | Sub-band<br>bandwidth<br>(MHz) | Spectral<br>channels<br>per sub-<br>band<br>spectrum |

|-----------------------|--------------------------------------------------|----------------------|------------------------------------------------|----------------------------------------------------------|-------------------------------------|---------------------------|--------------------------------|------------------------------------------------------|

| 8B-4B2P-<br>16S16-128 | 8                                                | 16.384               | 2.048                                          | 2048                                                     | 1000                                | 16                        | 128                            | 128                                                  |

| 8B-4B4P-<br>16S16-128 | 16                                               | 16.384               | 2.048                                          | 1024                                                     | 2000                                | 16                        | 128                            | 64                                                   |

| 8B-8B1P-<br>16S16-128 | 8                                                | 16.384               | 2.048                                          | 2048                                                     | 1000                                | 16                        | 128                            | 128                                                  |

| 4B-2B2P-<br>16S16-128 | 4                                                | 8.192                | 2.048                                          | 4096                                                     | 500                                 | 16                        | 128                            | 256                                                  |

| 4B-2B4P-<br>16S16-128 | 8                                                | 8.192                | 2.048                                          | 2048                                                     | 1000                                | 16                        | 128                            | 128                                                  |

| 4B-4B1P-<br>16S16-128 | 4                                                | 8.192                | 2.048                                          | 4096                                                     | 500                                 | 16                        | 128                            | 256                                                  |

| 2B-1B2P-<br>16S16-128 | 2                                                | 4.096                | 2.048                                          | 8192                                                     | 250                                 | 16                        | 128                            | 512                                                  |

| 2B-1B4P-<br>16S16-128 | 4                                                | 4.096                | 2.048                                          | 4096                                                     | 500                                 | 16                        | 128                            | 256                                                  |

| 2B-2B1P-<br>16S16-128 | 2                                                | 4.096                | 2.048                                          | 8192                                                     | 250                                 | 16                        | 128                            | 512                                                  |

| 1B-1B1P-<br>16S16-128 | 1                                                | 2.048                | 2.048                                          | 16384                                                    | 125                                 | 16                        | 128                            | 1024                                                 |

| 2B-2B1P-<br>8S16-128  | 2                                                | 2.048                | 1.024                                          | 8192                                                     | 125                                 | 16                        | 128                            | 1024                                                 |

| 2B-1B2P-<br>8S16-128  | 2                                                | 2.048                | 1.024                                          | 8192                                                     | 125                                 | 16                        | 128                            | 1024                                                 |

| 2B-1B4P-<br>8S16-128  | 4                                                | 2.048                | 1.024                                          | 4096                                                     | 250                                 | 16                        | 128                            | 512                                                  |

**Table 3-1 Representative Wide-band Observing Modes**

| r                     | T                                                |                      |                                                |                                                          |                                     |                 |                                |                                                      |