VLA TECHNICAL REPORT #17

MODULE F6

RF SPLITTER

Sander Weinreb

July 1975

# TABLE OF CONTENTS

| Figure 1 1<br>Figure 2 1<br>Figure 3 1<br>Figure 4 1<br>Figure 4.1 | RF Splitter Front Panel<br>RF Splitter Side View<br>RF Splitter Block Diagram<br>Log Detector output voltage etc.<br>Input and output connections<br>on and Adjustment | 2-<br>2-                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 H<br>Figure 3 H<br>Figure 4 H<br>Figure 4.1               | RF Splitter Side View<br>RF Splitter Block Diagram<br>Log Detector output voltage etc.<br>Input and output connections                                                 | 2-<br>2-<br>2-<br>2-                                                                                                                                                                                                                                                                                    |

| Figure 3 H<br>Figure 4 H<br>Figure 4.1                             | RF Splitter Block Diagram<br>Log Detector output voltage etc.<br>Input and output connections                                                                          | 2<br>2<br>2                                                                                                                                                                                                                                                                                             |

| Figure 4 1<br>Figure 4.1                                           | Log Detector output voltage etc.<br>Input and output connections                                                                                                       | _                                                                                                                                                                                                                                                                                                       |

| Figure 4.1                                                         | Input and output connections                                                                                                                                           | 2-                                                                                                                                                                                                                                                                                                      |

| •                                                                  |                                                                                                                                                                        | 2-<br>3-                                                                                                                                                                                                                                                                                                |

| nplementatio                                                       | on and Adjustment                                                                                                                                                      | 3-                                                                                                                                                                                                                                                                                                      |

|                                                                    |                                                                                                                                                                        | 5-                                                                                                                                                                                                                                                                                                      |

| Figure 5 S                                                         | Splitter Network Interior View                                                                                                                                         | 3-                                                                                                                                                                                                                                                                                                      |

| Figure 6 J                                                         | RF Splitter Switch Driver                                                                                                                                              | 3-                                                                                                                                                                                                                                                                                                      |

| Figure 7 H                                                         | RF Splitter Attenuator Driver                                                                                                                                          | 3-                                                                                                                                                                                                                                                                                                      |

| Figure 8                                                           | Log Detector Amp for RF Splitter                                                                                                                                       | 3-                                                                                                                                                                                                                                                                                                      |

| Figure 9 I                                                         | Detector output as function of load resistance, etc.                                                                                                                   | 3-                                                                                                                                                                                                                                                                                                      |

|                                                                    | Figure 6<br>Figure 7<br>Figure 8<br>Figure 9                                                                                                                           | Figure 5 Splitter Network Interior View<br>Figure 6 RF Splitter Switch Driver<br>Figure 7 RF Splitter Attenuator Driver<br>Figure 8 Log Detector Amp for RF Splitter<br>Figure 9 Detector output as function of load<br>resistance, etc.<br>ill of Materials, Specifications and<br>Manufacturers' Data |

| I. | RELATED DOCUMENTS                                      |           |                        |

|----|--------------------------------------------------------|-----------|------------------------|

|    | TITLE                                                  |           | NRAO NUMBER            |

|    | Block Diagram                                          |           |                        |

|    | Block Diagram, RF Splitter                             |           | C13170B3               |

|    | Bill of Materials                                      |           |                        |

|    | Driver Circuit                                         |           | A13170Z42              |

|    | Log Amplifier<br>Major Parts                           |           |                        |

|    | -                                                      |           |                        |

|    | Schematic Diagrams                                     |           |                        |

|    | Driver Circuit Schematic                               |           | C13170S9               |

|    | Log Amplifier Schematic                                |           | C13170S10              |

| •  | Assembly Drawings                                      |           |                        |

|    | Driver Circuit                                         |           | C13170P4               |

|    | Log Amplifier                                          |           | 0152/014               |

|    |                                                        |           |                        |

|    | Printed Circuit Boards                                 |           |                        |

|    |                                                        | Artwork   | Mechanical             |

|    | Driver Circuit                                         | B13170AB3 | C13170M84              |

|    | Log Amplifier                                          | A13170AB4 |                        |

|    | Mechanical Drawings                                    |           |                        |

|    |                                                        | 2         | 51 61 Found            |

|    | Plate, Side Left Front                                 |           | B13179M81<br>C13170M82 |

|    | Bar, Support, Top and Bottom<br>Plate, Side, Left Rear |           | C13170M82<br>C13170M83 |

|    | Panel, Front                                           |           | B13170M85              |

|    | Enclosure, Log Amplifier                               |           | C13170M87              |

|    | Guide                                                  |           | B13050M4               |

|    | Fastener, Perforated Cover                             |           | B13050M17              |

|    | Perforated Cover                                       |           | C13050M7               |

|    | Panel, Rear                                            |           | B13180M1               |

|    | RF Network Drawings                                    |           |                        |

|    |                                                        |           | 010170011              |

|    | RF Splitter Schematic                                  |           | Cl3170S11<br>Al3170A5  |

|    | AB Detector/Coupler<br>CD Detector/Coupler             |           | A13170A5<br>A13170A6   |

|    | AB Attenuator                                          |           | A13170A8               |

|    | CD Attenuator                                          |           | A13170A8               |

|    | Transfer Switch                                        |           | A13170A9               |

|    | Transfer Switch                                        |           | A13170A10              |

|    | Power Dividers                                         |           | A13170A11              |

|    | Drawing List, RF Splitter Network,                     | CMI4352   | A13170245              |

|    | Darte List DE Colittar Natwork                         |           | A13170245              |

A13170246

Parts List, RF Splitter Network

RF Network Drawings (continued)

| Access Port Cover, RF Splitter Network                 | A13170M91 |

|--------------------------------------------------------|-----------|

| RF Splitter Network, CMI4352, Outline/Mounting         | B13170M92 |

| Housing and Covers, RF Splitter Network, CMI4352       | C13170M93 |

| AB and CD Channel Attenuator S/A's RF Splitter Network | C13170M94 |

| AB and CD Channel Detector/Monitor Coupler S/A         | C13170M95 |

| Transfer Switch S/A, RF Splitter Network               | C13170M96 |

| Power Divider S/A, RF Splitter Network                 | C13170M97 |

|                                                        |           |

### II. FUNCTION

The RF Splitter Module couples two front-end dewar outputs, AB and CD, into four Frequency Converter inputs, A, B, C, and D. Each dewar-output is at 4.5 to 5.0 GHz and has passed thru the cooled paramp (+30 dB), transistor amplifier (+35 dB), isolator (-0.5 dB), and ~1.5m of 3mm-coaxial cable (-1.5 dB). This 63 dB of gain produces a Splitter input level of -22 dBm with 300° system temperature and 800 MHz of RF bandwidth. Specifications and data sheets for the transistor amplifier and isolator are included in Section IV of this manual.

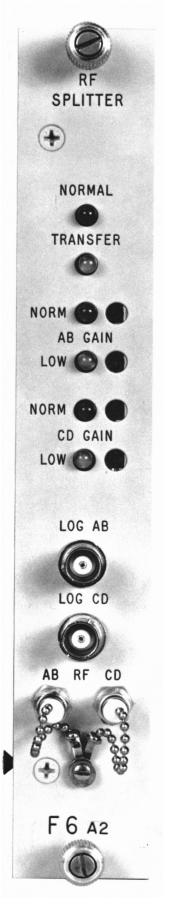

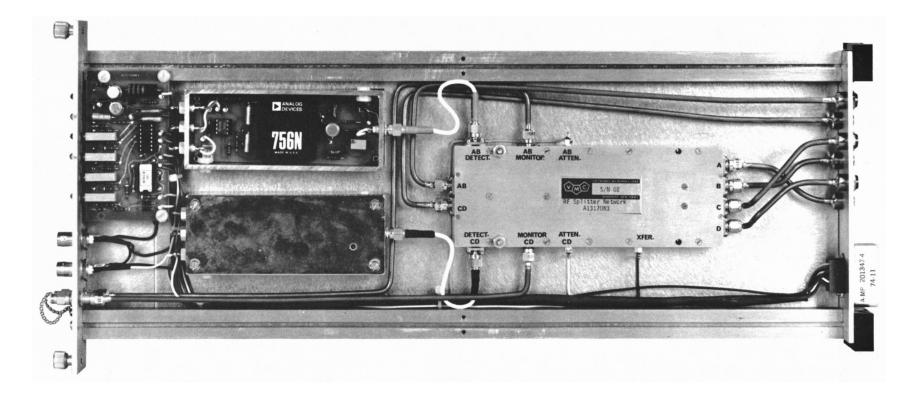

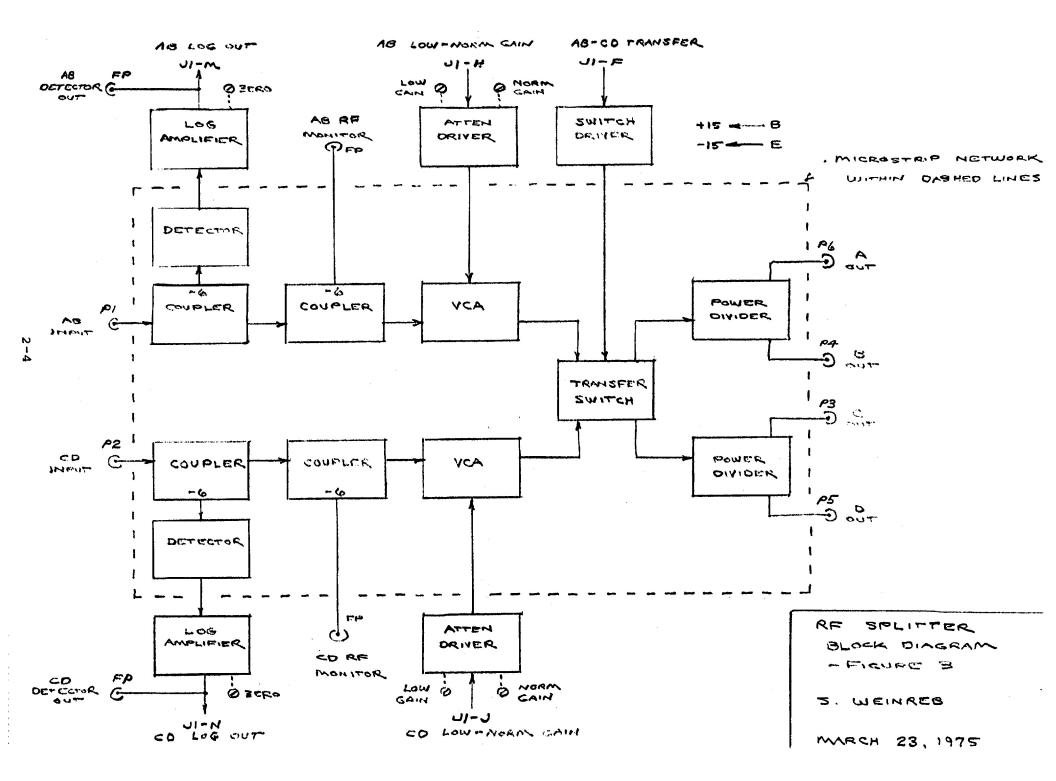

Photographs of the module are shown in Figures 1 and 2 and a block-diagram is presented in Figure 3. The functions of the Splitter are as follows:

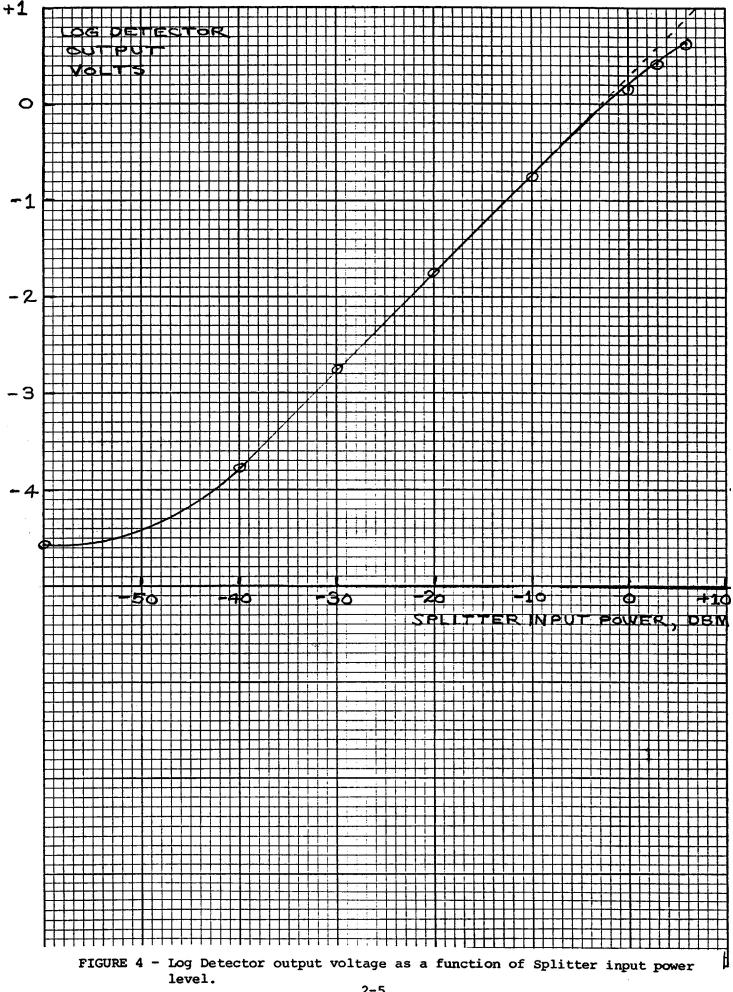

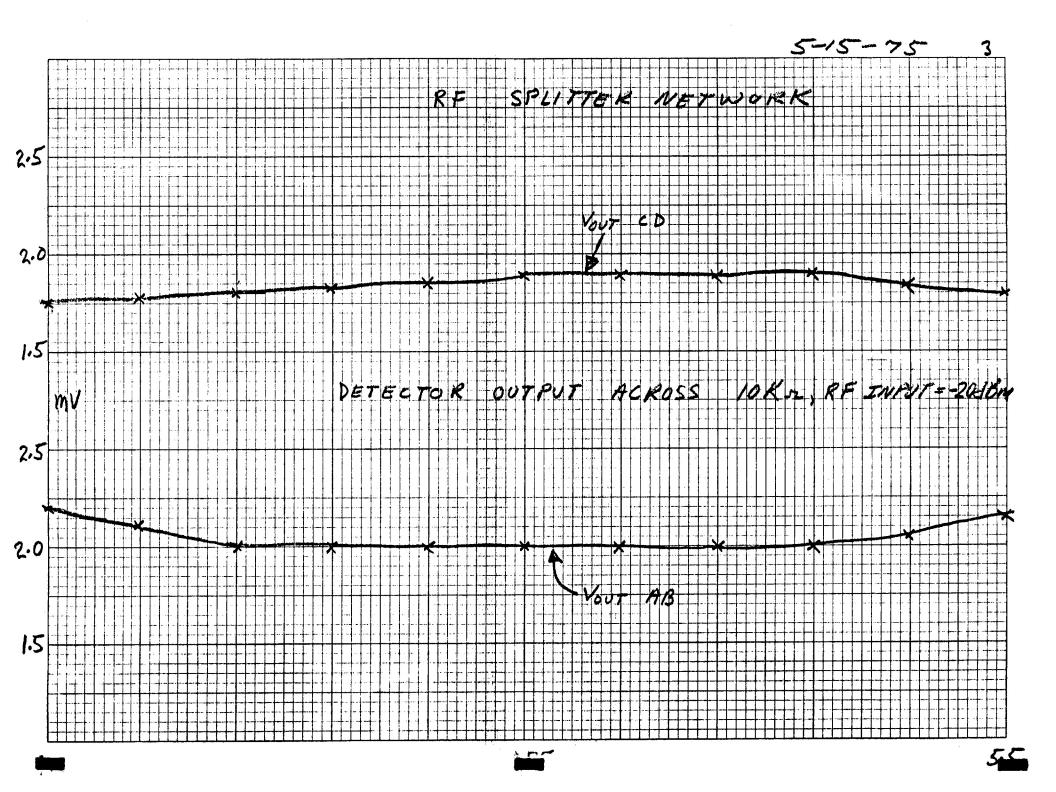

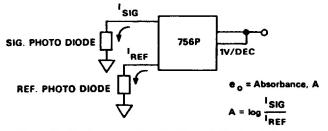

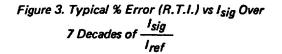

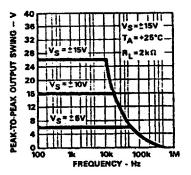

a) Log Detector Monitoring - Each input is coupled to a detector and logarithmic amplifier to provide a DC output as shown in Figure 4. This output is within a few percent of 10 dB per volt for input levels of -33 dBm to -3 dBm (output level of -3 volts to 0 volts). This signal is for swept frequency testing of the front-end; the sweep generator output level should be adjusted so the peak Log Detector output level is ∿0 volts.

b) <u>RF Monitoring</u> - RF samples approximately 8 dB below the input signal levels are available on front-panel SMA connectors for the purpose of spectrum analyzer RFI Analysis or for phase stability testing.

c) Level Adjustment - A voltage-controlled attenuator is provided in each signal path to allow front-panel adjustment of output signal level. The attenuators can be switched between two settings, NORMAL GAIN and LOW GAIN, under computer control. The total loss of the splitter can be adjusted from  $\sim 9$  to  $\sim 20$  dB with the NORMAL GAIN range pots (initial adjustment, 13 dB) and  $\sim 9$  to  $\sim 30$  dB with the LOW GAIN pots (initial adjustment, 23 dB). The switch-able gain is needed to allow solar observations.

d) <u>Transfer Switch</u> - In NORMAL mode the AB input is connected to A and B outputs whereas in TRANSFER mode it is connected to C and D outputs; the complementary statement applies to the CD input. The purpose of this switch is to facilitate calibration of polarization measurements and to aid in isolation of malfunctions.

e) <u>Power Division</u> - Each front-end channel must feed two Frequency Converters; the Splitter contains isolated power dividers to accomplish this task.

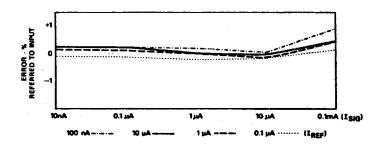

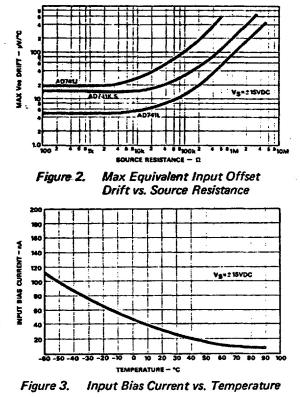

Input and output connections are given in Figure 4.1.

2-1

# FIGURE 1 RF SPLITTER FRONT PANEL

# FIGURE 2 RF SPLITTER SIDE VIEW

| RACK |                       | MODULE:       | RF Splitter            | TYPE: F6               |

|------|-----------------------|---------------|------------------------|------------------------|

| LIST |                       | BY:           |                        |                        |

|      | ECTOR TYPE: 14 PIN    | CONNECTOR PAG |                        |                        |

| PIN  | FUNCTION              | WIRE TYPE     | External<br>Connection | Internal<br>Connection |

| A    |                       |               |                        |                        |

| В    | +15                   | Red           |                        | Driver - E5            |

| С    | +5                    | Orange        |                        | Driver - E8            |

| D    | GND                   | Black         |                        |                        |

| E    | -15                   | Yellow        |                        | Driver - E9            |

| F    | Transfer Control      | Brown         | G10J1-z                | Driver - El            |

| н    | AB Attenuator Control | Red           | G10J1-a                | Driver - E2            |

| J    | CD Attenuator Control | Orange        | G10J1-b                | Driver - E2            |

| ĸ    |                       |               |                        |                        |

| L    |                       |               |                        |                        |

| М    | AB Log Out            | Blue          | G10J2-AA               | Log amp - out          |

| N    | CD Log Out            | White         | G10J2-BB               | Log amp - out          |

| Р    |                       |               |                        |                        |

| R    |                       |               |                        |                        |

| Pl   | AB Input              | .141          | ZDP1                   |                        |

| P2   | CD Input              | .141 😽        | ZDP2                   |                        |

| Р3   | C Output              | .141          | G8P2                   |                        |

| P4   | B Output              | .141          | G6P2                   |                        |

| P5   | D Output              | .141          | G9P2                   |                        |

| P6   | A Output              | .141          | G5P2                   |                        |

# FIGURE 4.1 - Input and output connections.

### III. IMPLEMENTATION AND ADJUSTMENT

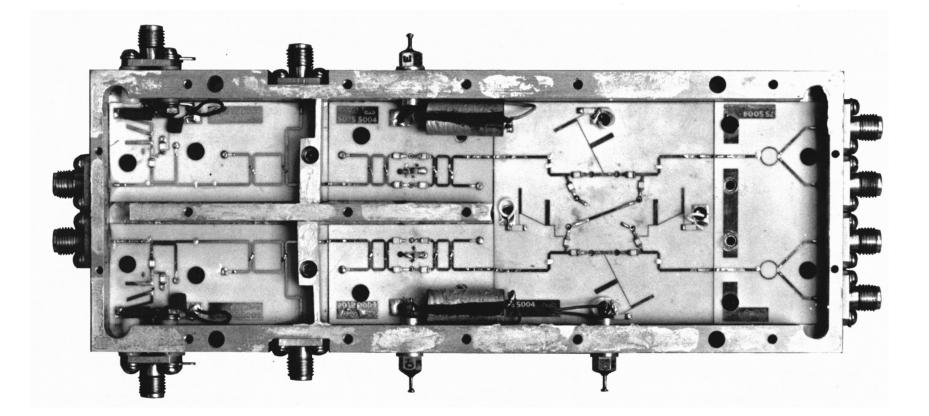

The heart of the RF Splitter Module is an integrated microstrip network which performs all of the required RF functions in an economical, compact manner. A photograph of the interior of the network is shown in Figure 5. Specifications (Al3170N3) of the network and manufacturers data are included in Section IV. If there is a malfunction in the network it should be examined under a lower-power microscope for loose connections (especially at SMA connector interface) and diodes should be checked with an ohmmeter. If this does not reveal the fault the unit should be returned to the manufacturer.

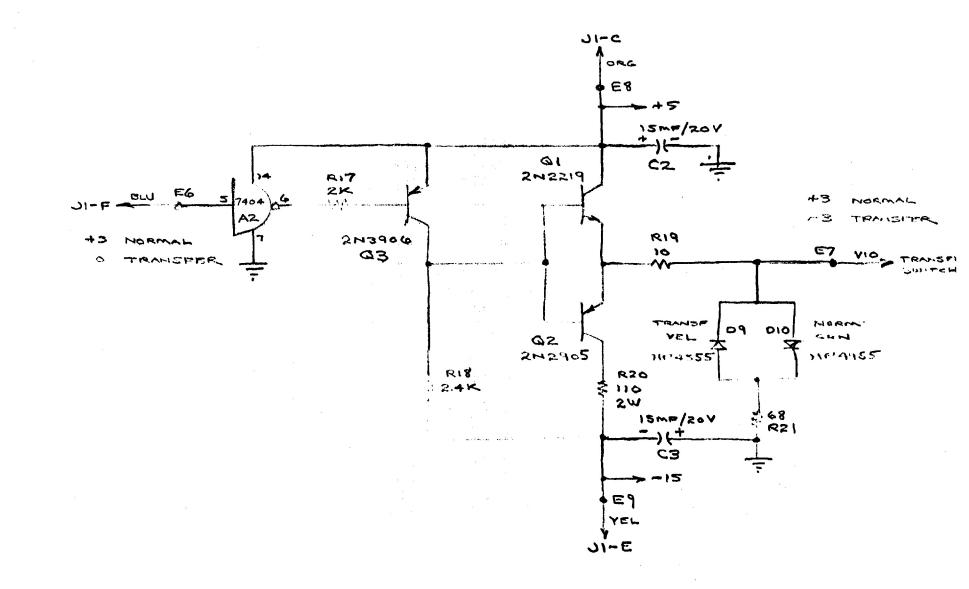

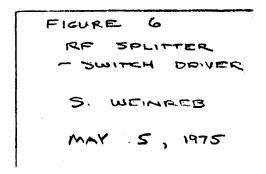

The network transfer switch and attenuators are driven by driver circuits shown in Figures 6 and 7. The transfer-switch driver translates a TTL input ("1" = NORMAL, "0" = TRANSFER) into +3 volts (NORMAL) and -3 volts (TRANSFER) into a 50 ohm switch-control input. The attenuator driver allows either a NORMAL GAIN pot or a LOW GAIN pot to control the current thru PIN diodes in the network; the current is varied from 0 to 4 mA for 0 to 20 dB of attenuation.

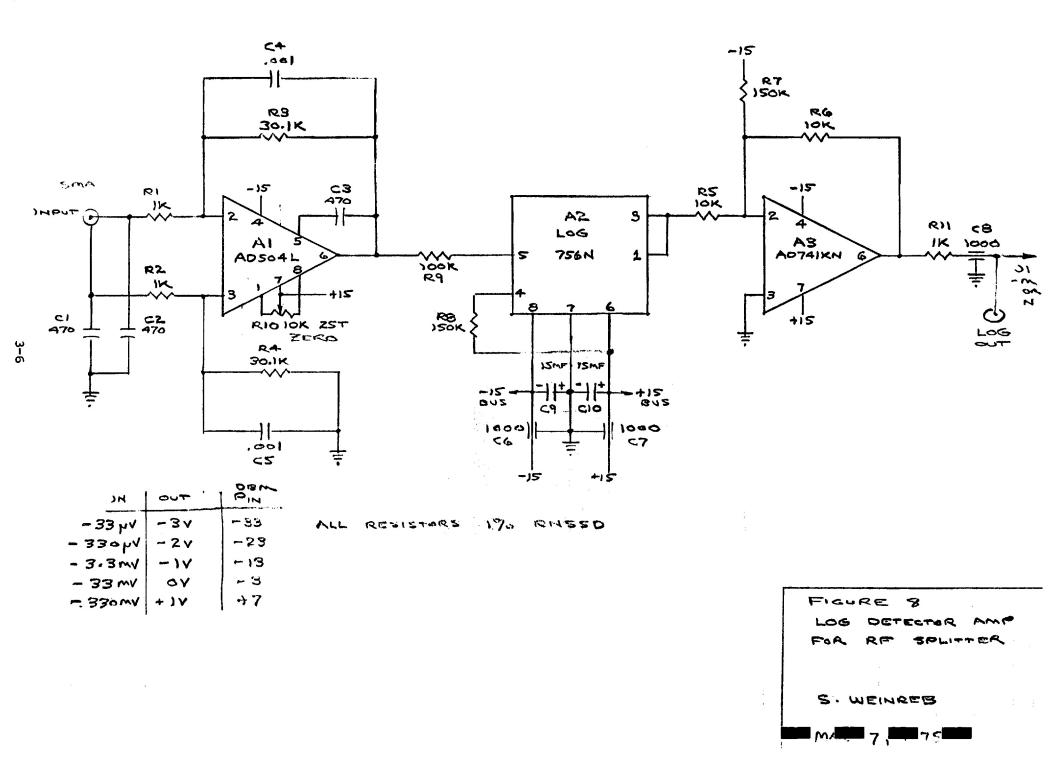

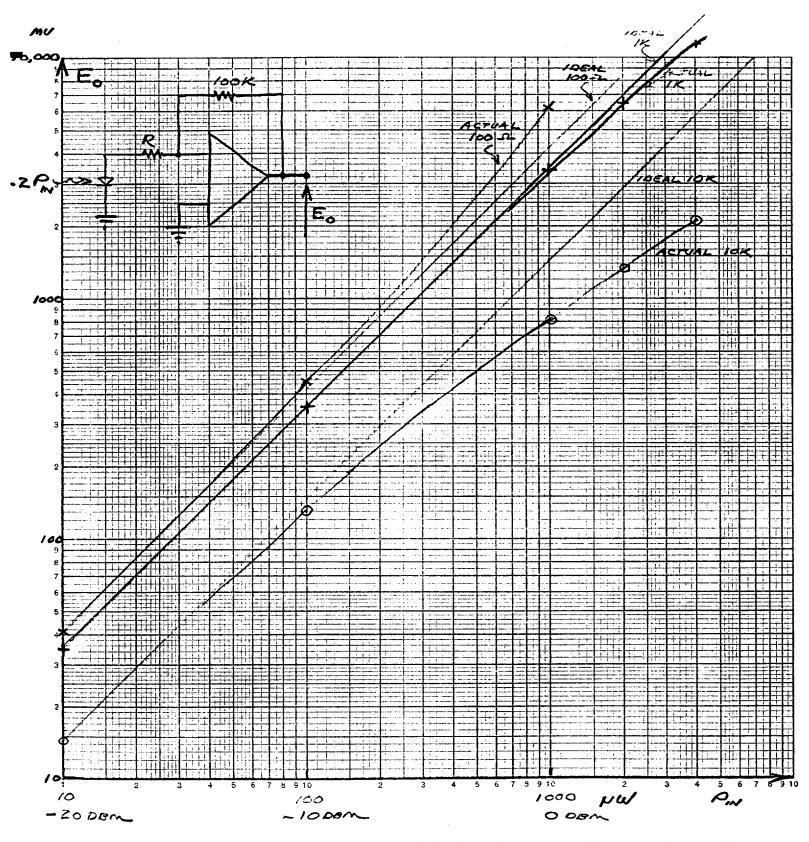

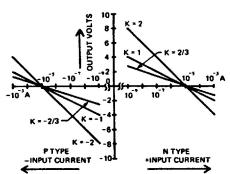

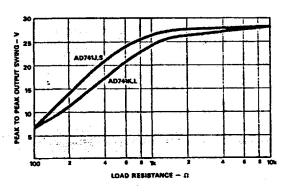

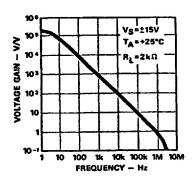

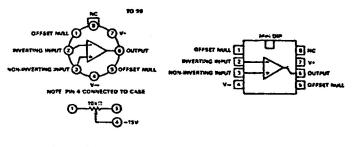

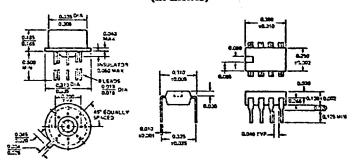

A schematic of the Log Detector Amplifier is shown in Figure 8. Tests of square-law detector error vs detector load resistance revealed that a load resistance of 1K gave least error as shown in Figure 9. The first-stage of the Log Detector Amplifier presents this load resistance and provides a gain of -30 in a low drift  $(1\mu V/^{\circ}C)$  operational amplifier. The amplifier output is applied to a plug-in logarithmic conversion module (AD756N) which is described in the manufacturers data sheet included in Section IV. The log module output is inverted and offset by an output op amp, A3. A log module output of +4 to +1 volts produces -3 to 0 volts output of A3. A maximum output of 0 volts for good square-law accuracy has been chosen so the top of a response curve can be expanded by increasing oscilloscope gain without getting a large offset; i.e. 0.1 volt per division gives 1 dB per division.

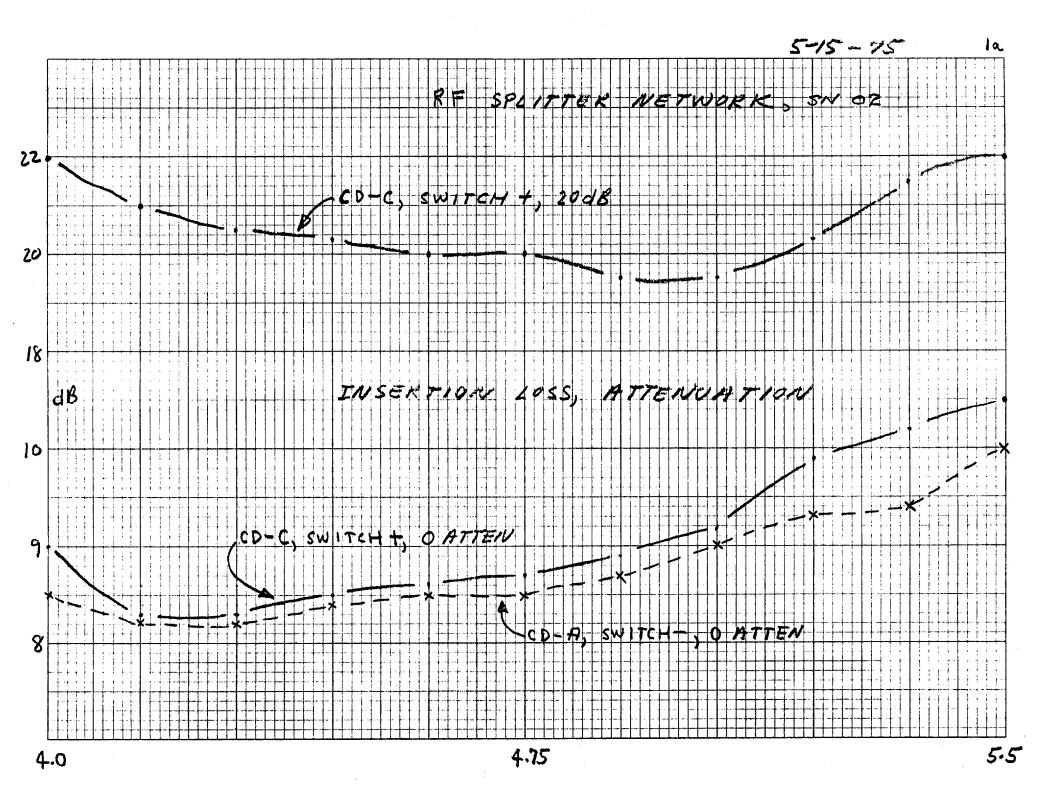

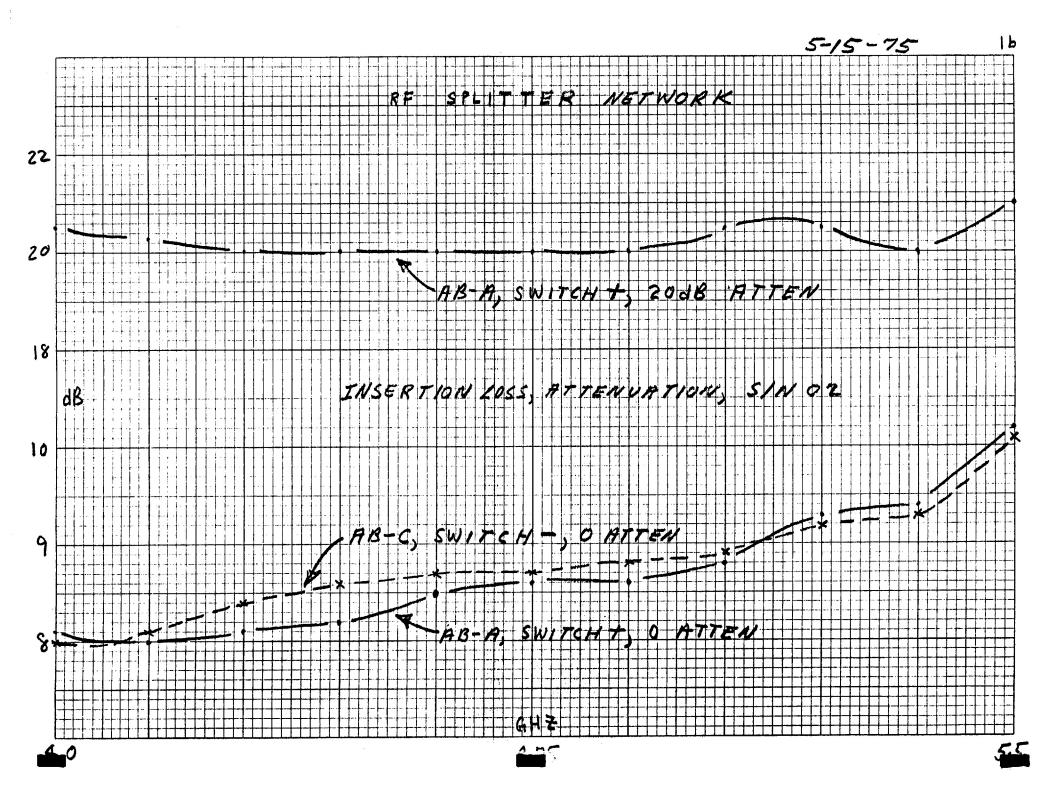

Tests of the RF Splitter Module are performed by connecting DC power and +3 or OV control signals for transfer and gain control. A 4.5 to 5.0 GHz generator is connected to AB or CD input and the appropriate otuputs are measured with a power meter as controls signals are switched and gain pots are varied. For initial adjustment the NORMAL GAIN and LOW GAIN pots are adjusted for 13 dB and 23 dB total insertion loss, respectively. The frontpanel indicator LED's should follow the applied control signal; improper initial operation is usually caused by a reversed LED or incorrect rear panel to circuit board wiring.

3-1

The only internal adjustment in the RF Splitter Module is the Log Amplifier zero, RlO. This should be adjusted to give a one volt output change as input level is changed from -30 dBm to -20 dBm; the absolute level need not be accurate but the 10 dB change should be accurate to  $\pm 1$  dB. If RF equipment is not available an approximate zero adjustment can be made by adjusting RlO to give -4.3 volts log output with no network input signal. The adjustment is accessible through a small hole in the side of the log amplifier module.

FIGURE 5 SPLITTER NETWORK INTERIOR VIEW

3-4

FIGURE 7 R.= SPLITTER - ATTENUATOR DRIVER S. WEINREB MORIL 1, 1975

FIGURE 9 - Detector output as function of load resistance, R for Aertech zero-bias Schottky-diode.

IV. BILL OF MATERIALS, SPECIFICATIONS, AND MANUFACTURERS' DATA

| ELECTRICAL            | MECHANICAL            | BOM # | REV        | DATE        | PAGE 1     | OF |

|-----------------------|-----------------------|-------|------------|-------------|------------|----|

| MODULE # <u>FG</u> NA | ME <u>RF</u> SPLITTER | DWG # | ŧ Sub .    | ASMB MAIN   | DWG #      |    |

| SCHEMATIC DWG #       | LOCATION              |       | QUA/SYSTEM | PREPARED BY | APPROVED _ |    |

\_\_\_\_\_

| ITEM<br># | REF<br>DESIG | MANUFACTURER | MFG PART #   | DESCRIPTION            | TOTAL<br>QUA |   |

|-----------|--------------|--------------|--------------|------------------------|--------------|---|

|           | -            | VECTRONICS   | A13170N3     | RF SPLITTER NErwork    | 1            |   |

|           | -            | ANV          | B13170 AB3   | ORIVER PC BOARD        | 1            |   |

|           | -            | ANY          | A13170 A84   | LOG AMP PC BOARD       | 2            |   |

|           | -            | Моорак       | 708-100-0000 | Box                    | 2            |   |

|           |              | AMPHENOL     | 74868        | UG-625/U BNG VACK      | γ            |   |

|           |              | OMNI SPECTRA | 209          | OSM FEEDTHRU           | 2            |   |

|           |              | OMNI SPECTRA | 20020 P/C    | TERMINATION WITH CHAIN | 2            | 5 |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

|           |              |              |              |                        |              |   |

| ELECTRICAL              | MECHANICAL BOM | # REV        | DATE         | PAGE OF  |

|-------------------------|----------------|--------------|--------------|----------|

| MODULE # <u>F6</u> NAME | RF SPLITTER    | DWG # SUE    | ASMB. ORIUER | DWG #    |

| SCHEMATIC DWG #         | LOCATION       | QUA/SYSTEM / | PREPARED BY  | APPROVED |

| ITEM<br># | REF<br>DESIG     | MANUFACTURER      | MFG PART #   | DESCRIPTION            | TOTAL<br>QUA |            |

|-----------|------------------|-------------------|--------------|------------------------|--------------|------------|

| 1         | AI               | ANY               | 7404N        | 10                     | 1            | 7          |

| 2         | A2               | ANALOG DEVICES    | AD7512 KN    | 10                     | 1            | 7          |

| 3         | Q1               | Amy               | 2N2219       | TRANSISTOR             | 1            | 7          |

| 4         | QZ               | ANY               | 2~2905       | TRANSISTOR             | 1            | 7          |

| 5         | 03               | ANY               | 2N3906       | TRANSISTOR             | 1            | 7          |

| 4         | DI, 03<br>010    | HEW PAC           | 5082-4955    | GREEN LED              | З            | 18         |

| 7         | D2,04<br>09      | n                 | 5082-4555    | YELLOW LED             | 3            | 18         |

| 8         | 05,04            | ANY               | 1~936        | ZENER DIODE            | 2            |            |

| 9         | 07,08            | ANY               | 1~ 459       | 01000                  | ス            | 14         |

| 10        |                  | ROBINSON - NUGENT | ICN 143 - 53 | 14 PIN DIL SOCKET      | 2            | 14-        |

| 11        | C1, C2<br>C3     | Kemet             | CSRIJEIS6KL  | 15 ME/201 TANFALUM CAP | ૩            | PR<br>4+69 |

| 12        | -                | KEYSTONE          | 1562-2       | TERMINAL               | 10           |            |

| 13        | R1, R2<br>R3, R4 | BECKMAN           | 89PRIOK      | IOR POT                | 4            |            |

| 14        | R5, R6<br>R7, R8 | A-B               |              | 180 ohm, 1/4w, 5%      | 4            | STOCK      |

| 15        | K9, R10          | A-8               |              | 18K, 14W, 5%           | 2            | STACK      |

| <b>ELECTRICAL</b>  | MECHAN    | NICAL BOM # | REV        | DATE        | PAGE <u>2</u> OF <u>2</u> |

|--------------------|-----------|-------------|------------|-------------|---------------------------|

| MODULE # <u>Fø</u> | NAME AF S | DWG         | # SUB      | ASMB DRIVER | DWG #                     |

| SCHEMATIC DWG #    | IO        | OCATION     | QUA/SYSTEM | PREPARED BY | APPROVED                  |

| ITEM<br># | REF<br>DESIG         | MANUFACTURER | MFG PART # | DESCRIPTION        | TOTAL<br>QUA | -     |

|-----------|----------------------|--------------|------------|--------------------|--------------|-------|

| 16        | RII, RIZ<br>RI3, RI4 | A-0          |            | 910 oHm, 1/4W, 570 | 4            | STOCK |

| 17        | R15, R16             | A-B          |            | 560 OHM, 1/4W, 570 | 2            |       |

| 18        | RIT                  | A-8          |            | 2K, 1/4W, 570      | 1            |       |

| 19        | RIS                  | A-B          |            | 2.4K, 1/4W, 570    | 1            |       |

| 20        | RIG                  | A-B          |            | 10 OHM, 1/4W, 5%   | 1            |       |

| 21        | R20                  | A-B          |            | 110 OHM; ZW, 570   | 1            |       |

| 22        | R21                  | A-B          |            | 68 OHM, 1/4W, 570  | 1            |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    | •            |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    |              |       |

|           |                      |              |            |                    |              |       |

| ELECTRICAL         | MECHANICAL       | BOM #   | REV                | DATE       | PAGE <u>1</u> | OF |

|--------------------|------------------|---------|--------------------|------------|---------------|----|

| MODULE # <u>F6</u> | NAME RF SPLITTER | DWG #   | SUB ASMB           | LOG DEFECT | OR DWG #      |    |

| SCHEMATIC DWG #    | LOCATION         | QUA/SYS | stem <u>2</u> prep | ARED BY    | APPROVED      |    |

| ITEM<br># | REF.<br>DESIG    | MANUFACTURER      | MFG PART #        | DESCRIPTION                            | TOTAL<br>QUA |            |

|-----------|------------------|-------------------|-------------------|----------------------------------------|--------------|------------|

| 1         | AI               | ANALOG DEVICES    | ADSO4L            | op Amp                                 | 1            | 12         |

| 2         | AZ               | ANALOG DEVICES    | 756N              | OP AMP                                 | 1            | 13         |

| ૩         | AЭ               | ANALOG DEVICES    | HO741KN           | OP AMP                                 | 1            | 7          |

| 4         | -                | ROBINSON - NUCENT | DP-5178-F         | 8 PIN TO-5 SOCKET                      | 1            | 8          |

| 5         | -                | n 11              | 101083 - 53       | 8 PIN DIL SOCKET                       | 1            | 8          |

| 4         | -                | CAMBION           | ASO-3388-01-03    | Socket PINS                            | 9            |            |

| 7         | -                | OMNI - SPECERA    | osm 21/           | OSM BULKHEAD VACK                      | 1            |            |

| 8         | C1, C2<br>C3     | ERIE              | 8101-100-651-471  | 4 TO PE/1000 CAPACITOR                 | З            | 12.        |

| 9         | C#, CS           | ERIE              | 8101-050-651-102m | 1000 PF/SOV "                          | 2            | 20         |

| 10        | <4,<7<br>⊂8      | SPECTRUM CONTROL  | FB-38-102W        | 1000 PF FEED-THRU CAPACITOR            | 3            | 30         |

| 11        | C9, C10          | Kemer             | CSRIBE 156KL      | ISME/201 TANALUM                       | 2            |            |

| 12        | RI, RZ<br>RS, RG | ANY               | RNSTO             | 10K 170                                | 4            | PR<br>4469 |

| 13        | R3, R4<br>R9     | ANY               | RNSSD             | 100× 1%                                | 3            | "          |

| 14        | R7, R8           | ANY               | RN550             | 150K 170                               | 2            | "          |

| 15        | R10              | BEGRMAN           | 63WRIOK           | lok 22 TURN POT                        | 1            |            |

| 16<br>47  | RII              | ANY               | RNSSO             | 1K 170<br>/ 1415 - 170 13 13 16 K 1910 | <br>4        | 25         |

## NATIONAL RADIO ASTRONOMY OBSERVATORY Charlottesville, Virginia VERY LARGE ARRAY PROJECT

## SPECIFICATION NO: A13170N1, Rev. B

NAME: 4.4 - 5.1 GHz Transistor Amplifier

DATE: March 4, 1975 PREPARED BY: MU APPROVED BY: XIU

### 1. FREQUENCY RANGE AND GAIN

Within the 4.4 to 5.1 GHz range the gain must be  $35 \pm 1$  dB. The gain must be less than 37 dB at any frequency outside of this band.

2. NOISE FIGURE

Less than 7 dB.

3. POWER OUTPUT

+10 dBm at 1 dB compression.

4. INPUT AND OUTPUT VSWR

Less than 2:1.

5. DC POWER

+15 volts.

6. TEMPERATURE

15°C to 35°C

7. CONNECTORS

Type SMA female.

### 8. MOUNTING PROVISION

Tapped holes on one surface.

## 9. GAIN TEMPERATURE COEFFICIENT

The temperature coefficient of gain shall be less than 0.1 dB/°C from  $20^{\circ}$ C to  $35^{\circ}$ C.

# MEASURED DATA LOCUS Model RF-623A

| Frequency                             | Gain<br>(dB) | Noise Figure<br>(dB) | Input  | Output | Output Power at 1.0dB  |

|---------------------------------------|--------------|----------------------|--------|--------|------------------------|

| (G,Hz)                                | (ub)         | (ub)                 | VSWR   | VSWR   | Gain Compression (dBm) |

|                                       |              | _                    |        |        |                        |

| 4,4                                   | 35,1         | 5.8                  | <1.5:1 | <1,48  | + 12.9                 |

| 4.5                                   | 35.3         | 5:8                  |        |        | + 13.4                 |

| 4.6                                   | 35.6         | 5,9                  |        |        | + 12.8                 |

| 4,7                                   | 35,6         | 6.0                  |        |        | + 12.3                 |

| 4.8                                   | 35,2         | 6.2                  |        |        | + 11.9                 |

| 4.9                                   | 34.9         | 6.4                  |        |        | +12.0                  |

| 5.0                                   | 35.3         | 6:8                  |        |        | +//./                  |

| 5,1                                   | 34.9         | le.9                 | ł      | L L    | +10.3                  |

|                                       |              |                      |        |        |                        |

| 1                                     |              |                      |        |        |                        |

|                                       |              |                      |        |        |                        |

|                                       | Í            |                      |        |        |                        |

|                                       | 1            |                      |        |        |                        |

|                                       |              |                      |        |        |                        |

|                                       | i            |                      |        |        |                        |

| · · · · · · · · · · · · · · · · · · · | 1            |                      |        |        |                        |

|                                       |              | i                    |        | l      |                        |

Test Performed By: RM Sackman Approved By: R. L. Ounkle Date: Now 15-1975 -----

Serial #\_\_\_\_\_ +15 Vac @ 154 ma

## NATIONAL RADIO ASTRONOMY OBSERVATORY Charlottesville, Virginia VERY LARGE ARRAY PROJECT

SPECIFICATION NO: A13170N3, Rev. A

NAME: RF Splitter Network

DATE: July 14, 1975

PREPARED BY:

#### APPROVED BY:

### 1. General Description

A microwave integrated circuit containing four directional couplers, two PIN diode attenuators, two detectors, a diode transfer switch, and two power dividers is required; the desired configuration is shown in Figure 1. A deviation from this configuration in which monitor and detector couplers are exchanged in position is allowed. The unit will be used at power levels  $\leq$  +20 dBm, at a temperature of 25  $\pm$ 5°C, and must meet all specifications in the 4.3 to 5.2 GHz range.

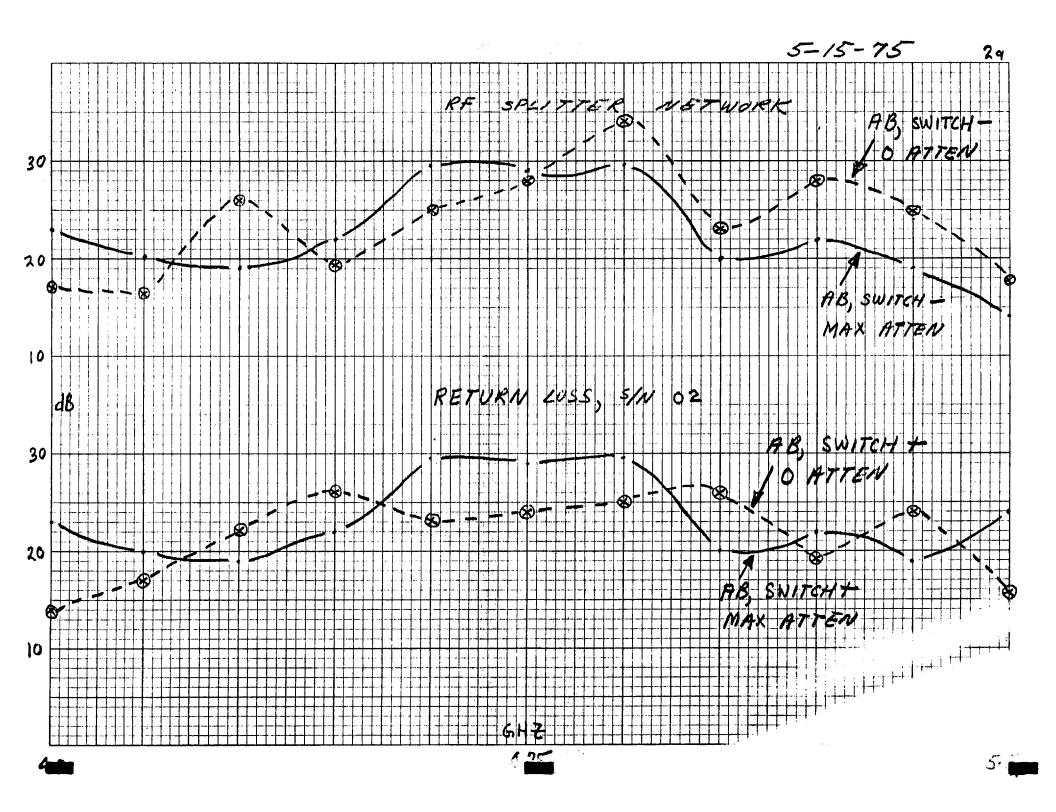

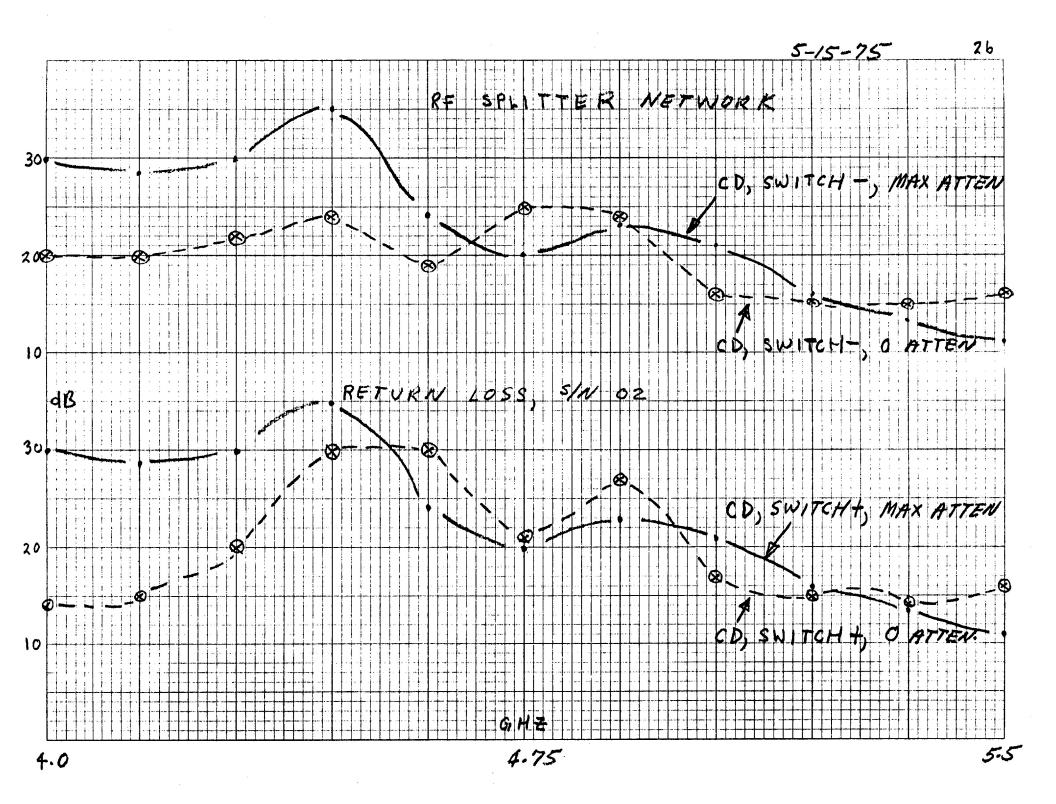

### 2. Attenuation and Return Loss

The maximum loss from either input to a desired output is 10 dB with PIN diode attenuators at minimum attenutation. The minimum return loss at any RF input or output shall be 15 dB.

### 3. Detectors

The detector sensitivity into a 1K load shall be 20 to 40  $\mu$ V per  $\mu$ w of network input power. The detector shall be unbiased, have negative output, and shall have a DC to 1 MHz frequency response. The detector shall be square-law within <u>+1</u> dB for network input powers of up to -3 dBm and for a detector load resistor of 1K.

### 4. PIN Attenuator

The PIN attenuator shall be controllable from a single control terminal and shall have a 20 dB attenuation range. The frequency variation of loss at any attenuator setting shall be  $\leq \pm 0.5$  dB and the return loss specification must be met at any attenuation. The switching speed shall be  $\leq 100 \ \mu$ s. An input current of 4 mA shall produce  $\geq 15$  dB of attenuation.

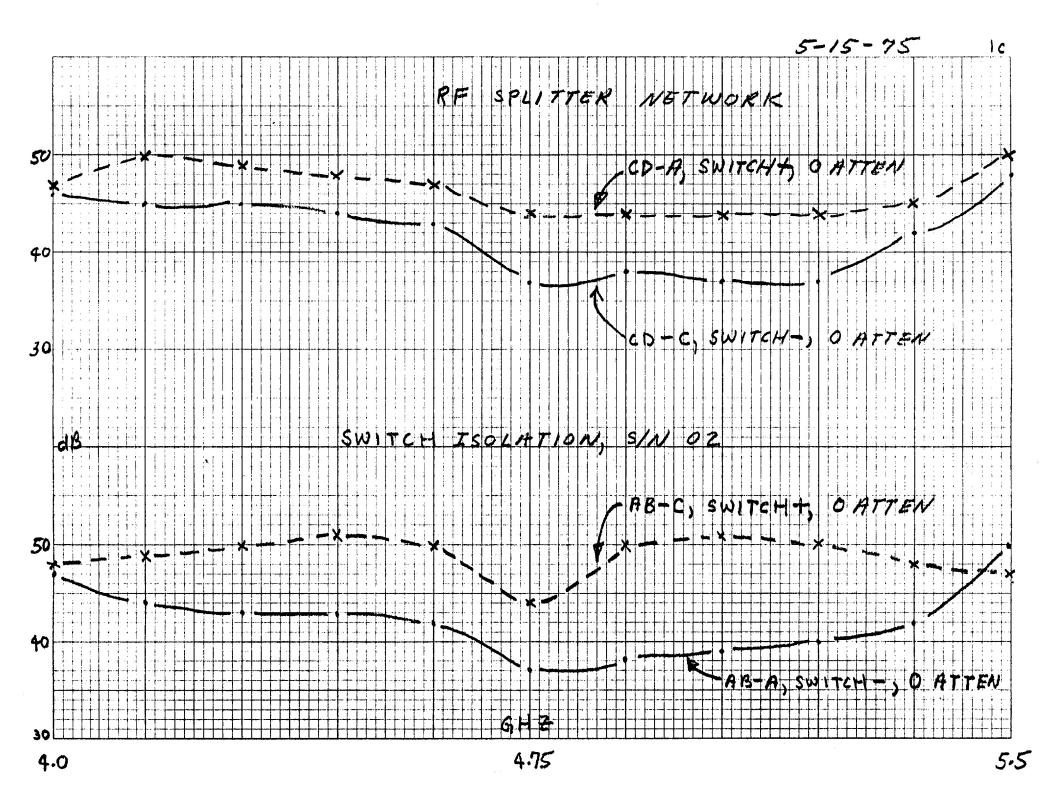

### 5. Transfer Switch

The diode transfer switch must provide a minimum of 35 dB isolation and a switching speed of  $\leq 100 \ \mu$ s. The control voltage shall be +3 volts for normal and -3 volts for transfer into a load resistance  $\geq 50$  ohms.

### 6. Monitor Couplers

The monitor couplers shall have coupling of 8  $\pm$ 2 dB referred to input and isolation  $\geq$ 15 dB.

### 7. Output Power Dividers

The output power dividers shall have an isolation  $\geq$ 20 dB and produce equal power within  $\pm$ 0.5 dB.

### 8. Construction

The unit must be housed in an RFI-tight aluminum case having dimensions 0.69"x2.5"x6.75" excluding connectors. The printed circuit must be of rigid construction with high quality solder joints.

## 9. Connectors

All RF connections and detector outputs shall be type SMA female. Control lines shall be feed-thru capacitor solder terminals.

### 10. Drawings

All artwork and reproducible copies of all drawings generated in manufacture shall be delivered with hardware.

### 11. Test Data

The following data must be provided for each unit in the 4.0 to 5.5 GHz range.

- AB and CD return loss in normal and transfer mode with 0 dB and 20 dB PIN attenuator settings (8 curves).

- AB to A and CD to C insertion loss in normal and transfer mode with 0 dB and 20 dB PIN attenuator settings (8 curves).

- AB and CD detector output voltage at input levels of -20 dBm (2 curves).

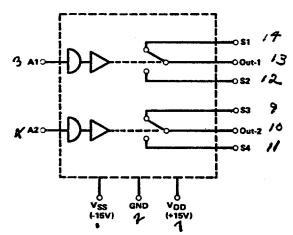

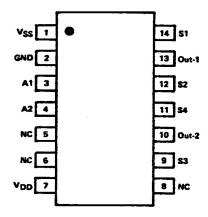

### CMOS Dual SPDT Analog Switch

#### PRELIMINARY DATA SHEET

# AD7512

#### **FUNCTIONAL DIAGRAM**

Two Independent SPDT Switches TTL/DTL/CMOS Direct Interface Power Dissipation: 30μW "ON" Resistance: 75Ω Silicon Nitride Passivation

#### **GENERAL DESCRIPTION**

**FEATURES**

The AD7512 consists of two independent analog SPDT switches switches on a monolithic CMOS chip. Packaging is a 14-pin ceramic or plastic DIP. All digital inputs are TTL/DTL and CMOS compatible with at least  $10^9\Omega$  input impedance. The extremely low power dissipation of  $30\mu$ W is achieved by combining unique circuit design with state-of-the-art CMOS technology.

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> (to GND)+17V             |

|------------------------------------------|

| V <sub>SS</sub> (to GND)17V              |

| Switch Voltage (to VSS) +27V             |

| Switch Voltage (to VDD)                  |

| Switch Current (ID-out, Continuous) 30mA |

| Switch Current (ID-out, Surge)           |

| 1ms duration, 10% duty cycle 150mA       |

| Digital Input Voltage Range VSS to VDD   |

| Power Dissipation (Package)              |

| 14-pin Plastic DIP                       |

| Up to +70°C 670mW                        |

| Derates above +70°C by 8.3mW/°C          |

| 14-pin Ceramic DIP                       |

| Up to +75°C 450mW                        |

| Up to +75°C                              |

| Operating Temperature                    |

| Storage Temperature                      |

|                                          |

CAUTION:

1. Do not apply voltages higher than  $V_{DD}$  and  $V_{SS}$  to any other terminal, especially when  $V_{SS} = V_{DD} = 0V$  all other pins should be at 0V.

The digital control inputs are zener protected; however, permanent damage may

occur on unconnected units under high energy electrostatic fields. Keep unused

units in conductive foam at all times.

Address "High" makes SZ to Out-1 and S3 to Out-2.

#### **ORDERING INFORMATION**

| AD7512J: | 0°C to +75°C    |

|----------|-----------------|

| AD7512K: | 0°C to +75°C    |

| AD7512S: | -55°C to +125°C |

| AD7512T: | -55°C to +125°C |

#### PACKAGE VERSIONS

| Suffix "N" | Plastic DIP                |

|------------|----------------------------|

| Suffix "D" | Ceramic DIP                |

| Suffix "F" | Flatpack (Special Request) |

#### **PIN CONFIGURATION (Top View)**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Tel:

617/329-4700

TWX:

710/394-6577

West Coast

Tel:

213/595-1783

Mid-West

Tel:

312/297-8710

# **SPECIFICATIONS** ( $V_{DD}$ = +15 V, $V_{SS}$ = -15 V, $T_A$ = +25° C unless otherwise noted)

| PARAMETER                                        | VERSION      | SWITCH   | 5        | <b>e</b> 25° ( |      |           | RANGE    |      | TEST CONDITIONS                                                                                  |  |

|--------------------------------------------------|--------------|----------|----------|----------------|------|-----------|----------|------|--------------------------------------------------------------------------------------------------|--|

|                                                  |              |          | MIN      | TYP            | MAX  | MIN       | MAX      |      |                                                                                                  |  |

| ANALOG SWITCH                                    |              |          |          |                |      |           |          |      |                                                                                                  |  |

| R <sub>ON</sub>                                  | Àll          | ON       |          | 70             | 100  |           |          | Ω    |                                                                                                  |  |

| RON VS. VS                                       | Ali          | ON       |          | 20             |      |           |          | %    | $-10 \text{ V} \le \text{V}_{\text{S}} \le +10 \text{ V}, \text{ I}_{\text{S}} = 1.0 \text{ mA}$ |  |

| ΔR <sub>ON</sub>                                 |              |          |          | <u> </u>       |      |           |          |      |                                                                                                  |  |

|                                                  | Ali          | ON       |          | +0.5           |      |           |          | %∕°C | V <sub>S</sub> = 0, I <sub>S</sub> = 1.0 mA                                                      |  |

| RON Mismatch Between Switches                    | All          | ON       |          | 1              |      |           |          | %    |                                                                                                  |  |

| RON Mismatch Between Switches<br>vs. Temperature |              | ON       |          | 0.01           |      |           |          | %/°C |                                                                                                  |  |

| _                                                | Ј, К         | OFF      |          | 0.5            | 5    |           | 500      | nA   |                                                                                                  |  |

| IS                                               | S, T         | OFF      |          | 0.2            | 3    |           | 200      | nA   | $-10 V \le V_{S} \le +10 V$                                                                      |  |

| _                                                | Ј, К         |          |          | 1.5            | 15   |           | 1500     | пA   | and                                                                                              |  |

| IOUT                                             | S, T         |          |          | 0.6            | 9    |           | 600      | nA   | $-10 V \le V_{OUT} \le +10 V$                                                                    |  |

| IOUT – IS                                        | All          |          |          |                | 20   |           |          | nA   | V <sub>D</sub> = 0                                                                               |  |

| DIGITAL CONTROL                                  |              |          |          |                |      |           |          |      |                                                                                                  |  |

|                                                  | Ali          | 1        | 1        |                |      |           | 0.8      | v    |                                                                                                  |  |

| V <sub>INL</sub>                                 | J, S         |          | <u> </u> |                |      | 3.0       |          | v    |                                                                                                  |  |

| VINH Note 1                                      | ,, 5<br>К, Т |          |          | 1              |      | 2.4       |          | v    |                                                                                                  |  |

| IINL or INH                                      | All          |          |          | 10             |      |           | <u> </u> | nA   |                                                                                                  |  |

| INL OF INH                                       | J, K         | ł        |          |                |      |           | 100 тур  | nA   |                                                                                                  |  |

|                                                  | 5, T         |          |          |                |      |           | 1 typ    | μA   |                                                                                                  |  |

| C <sub>IN</sub>                                  | All          | <u> </u> | $\vdash$ | 5              |      |           |          | pF   |                                                                                                  |  |

|                                                  |              |          | <u> </u> |                |      |           | <u> </u> |      |                                                                                                  |  |

| DYNAMIC                                          |              |          |          |                |      |           |          |      |                                                                                                  |  |

| CHARACTERISTICS                                  |              | 1        | ł        |                |      | 1         |          |      |                                                                                                  |  |

| <sup>t</sup> Transition                          | All          |          | <u> </u> | 1.2            |      |           | ļ        | μs   |                                                                                                  |  |

| C <sub>S</sub>                                   | All          | ON       |          | 28             |      |           |          | pF   |                                                                                                  |  |

| CS                                               | All          | OFF      |          | 8              |      |           | 1        | pF   |                                                                                                  |  |

| COUT                                             | All          | -        | 1        | 28             |      |           | 1        | pF   |                                                                                                  |  |

| C <sub>S</sub> -OUT                              | All          | OFF      | l .      | 0.5            |      |           |          | pF   |                                                                                                  |  |

| CSS Between Switches                             | All          | -        | ļ        | 0.5            |      |           |          | pF   |                                                                                                  |  |

| COUT-OUT                                         | All          | - 1      | ł        | 0.5            |      |           |          | pF   |                                                                                                  |  |

| Between Switches                                 |              |          | <u> </u> |                |      |           |          |      |                                                                                                  |  |

| POWER SUPPLY                                     |              |          |          |                |      |           |          |      |                                                                                                  |  |

| IDD                                              |              |          |          | 1              | 100  | }         | 1        | μA   | All Digital Inputs Low                                                                           |  |

| I <sub>SS</sub>                                  | · · · · ·    |          |          | 1              | 100  |           |          | μA   |                                                                                                  |  |

| I <sub>DD</sub>                                  |              |          |          | 0.15           | 0.5  |           | 1        | mA   | All Digital Inputs High                                                                          |  |

| ISS                                              |              |          | L        | 1              | 100  |           | <u> </u> | μA   |                                                                                                  |  |

| PRICE (1-49)                                     |              |          |          |                |      | 2010 2020 |          |      |                                                                                                  |  |

|                                                  | AD7512JN     |          |          | 8              | .00  |           |          | s    |                                                                                                  |  |

|                                                  | AD7512JD     |          |          | 13             | .00  |           |          | s    |                                                                                                  |  |

|                                                  | AD7512KN     |          |          | 9              | .00) |           |          | s    | ł                                                                                                |  |

|                                                  | AD7512KD     |          |          | 15             | .00  |           |          | s    |                                                                                                  |  |

|                                                  | AD7512SD     | 2        |          | 22             | .00  |           |          | s    | · · ·                                                                                            |  |

|                                                  | AD7512TD     |          |          | 24             | .00  |           |          | s    |                                                                                                  |  |

NOTES:

A pullup resistor, typically 1-2 kΩ, is required to make the AD7512J and AD7512S compatible with TTL/DTL levels. The maximum value is determined by the output leakage current of the driver gate when in the high state.

Specifications subject to change without notice.

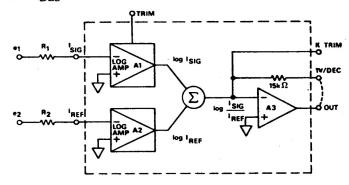

# Complete Log Ratio Module

#### PRELIMINARY TECHNICAL DATA

#### **FEATURES**

Complete Log Ratio Module Provides Log Ratio of Current Provides Log Ratio of Voltage Dynamic Range of 7 Decades of Ratio

#### **APPLICATIONS**

Log Ratio or Antilog Ratio of Voltages Log Ratio or Antilog Ratio of Currents Absorbance Measurements (see Figure 2)

$$R \approx \left(\frac{15k\Omega}{V}\right) \ K_{DES}$$

where R represents the total feedback resistance of  $A_3$ , and  $K_{DES}$  is the desired scale factor.

#### Figure 1. Functional Block Diagram of Model 756

#### **VOLTAGE LOG RATIO**

The principle of operation for voltage log ratio is identical to that of current log ratio after the voltage signal has been converted to a current. To accomplish this conversion, an external resistor is attached from the voltage signal to the appropriate input current terminal of the 756. Input currents are then determined by:

$$I_{sig} = \frac{e_1}{R_1}$$

,  $I_{ref} = \frac{e_2}{R_2}$

rate

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062

vices

Tel: 617/329-4700

TWX: 710/394-6577

hird

West Coast

Tel: 213/595-1783

ices.

Mid-West

Tel: 312/297-8710

#### **GENERAL DESCRIPTION**

Model 756 is a complete temperature compensated DC log ratio module, containing two channels for processing input variables. Channel 1 features a high quality FET amplifier with bias current of only 10pA. Using this input, signals spanning 4 decades can be processed with less than 1% error. By applying signals spanning up to 3 decades to channel 2, overall performance of 1% can be achieved for ratios covering a dynamic range of 10 million to 1 (7 decades).

Designed primarily for photometer applications, model 756 replaces two log modules, a subtractor, and associated circuitry. The signal sources for these applications are usually photo diodes which should be operated in the zero-volt mode (short circuit current). When connected as shown in Figure 2, the summing junctions provide virtual grounds, thereby forcing the input currents to be the short circuit current of the photo diodes.

#### PRINCIPLES OF OPERATION CURRENT LOG RATIO

Current log ratio is accomplished by model 756 when two currents,  $I_{sig}$  and  $I_{ref}$ , are applied directly to the input terminals (see Figure 1). The two log amps process these signals providing voltages which are proportional to the log of their respective inputs. These voltages are then subtracted and applied to an output amplifier. The scale factor, when connected as shown, is 1V/dec. However, other scale factors may be achieved by using an external/feedback resistor for A<sub>3</sub> instead of the internal  $15k\Omega$ . The governing equation for this optional adjustment is:

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# SPECIFICATIONS (typical at +25°C and ±15V unless otherwise noted)

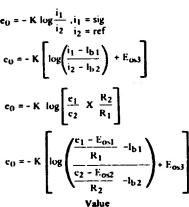

Current Log Ratio  $e_0 = -K \log \frac{i_1}{i_2}$ ,  $i_1 = sig$  $i_2 = i_2 = ref$ Transfer Equation Transfer Equation including Error Terms Voltage Log Ratio Transfer Equation  $\frac{R_1}{c_2 - E_{os2}}$ c<sub>0</sub> = - K log Transfer Equation including Error Terms Value Parameter Signal Current, i1 Reference Current, i2 Log Conformity<sup>2</sup> Scale Factor, K1,3 Bias Current, Ib1 Bias Current, 1b2 Offset Voltage, Eos1 3 Offset Voltage, Eos2 Output Offset, Eos3 Small Signal Response ft im 1kHz 1nA 1µA 8kHz 25kHz 100µA Slew Rate iin (decreasing) time im (increasing) time 10nA to 1nA 200µs InA to 10nA 70µs 50µs 100nA to 10nA 10nA to 100nA 25µs 1µA to 100nA 25µs 100nA to 1µA 25µs 1µA to 100µA 100µA to 1µA 20µs 20µs Noise in 10kHz B.W. V<sub>n</sub>, INPUT 1 3µV rms Vn, INPUT 2 3µV rms In, INPUT 1 0.1pA rms In, INPUT 2 20pA rms Rated Output ±10V at 5mA Log Mode Antilog Mode ±10V at 4mA Power Quiescent Current 3mA at ±15V Recommended Supply Model 915<sup>4</sup> 54dB PSRR 1.5" x 1.5" x 0.4" Package Size Price (1-9) \$75 (10-24) \$65 \* Positive for positive inputs (N type), negative for negative inputs (P type).

<sup>2</sup> The log conformity specification is referred to input (R.T.I.). Note: 1% error R.T.I. is equivalent to 4.3mV of error at output for K = 1V. <sup>3</sup>Externally trimmable.

<sup>6</sup>Model 915 is a 0.1% regulated dual 15V supply at 25mA. 1-9 price is \$23. For higher current capability consider models 904 (50mA), 902 (100mA) or 920 at 200mA.

Specifications subject to change without notice.

Figure 2. Photometry Application of Model 756

10nA to 100µA (4 decades) 100nA to 100µA (3 decades) ±0.5% (2 decades, is constant) ±1.0% (4 decades, i2 constant) 1V ±1% ±0.04%/°C 10pA, doubles/10°C 10nA, max, ±1%/°C ±1mV, max, 25µV/°C 0.5 mV, max,  $30 \mu \text{V/}^{\circ}\text{C}$  max ±10mV, max, 85µV/°C

**TRANSFER CURVES**

Plot of output voltage vs. input current for Model 756 connected in log mode and I ref =  $10\mu$ A. To use the same curve for input voltage, calculate in as e1/R1 (see Figure 1).

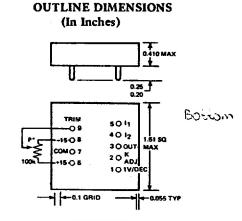

#### **PIN VIEW**

Pins: 0.040 +0.002 dia. spherical radius on ends, half-hard brass, gold plated per QQ-B-626.

Mating Socket AC1039 @ \$3.00 \*Ext 100k pot available from ADI Model #79PR100K at \$3.00

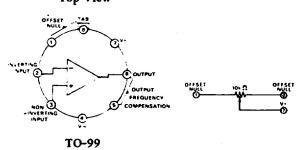

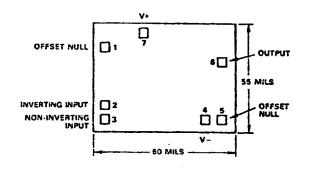

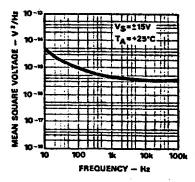

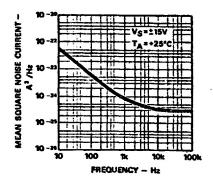

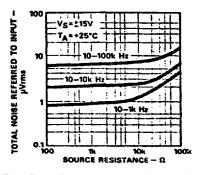

### LOW DRIFT, LOW NOISE OP AMP PIN CONFIGURATION AD504

### **ENERAL DESCRIPTION**

⇒ AD504J, AD504K, AD504L, and AD504M are moderately d operational amplifiers which combine ultra-low drift and noise and extremely high gain with the frequency response and slew rate of general purpose I.C. op amps. A new double integrator circuit concept combined with a precise thermallybalanced layout achieves maximum nulled offset drift below  $.5\mu V/^{\circ}C$ , max input noise voltage of  $0.6\mu V$  (p-p), and mininum gain of  $10^{6}$ . Unity gain small signal bandwidth is 300kHz and the slew rate is  $1.2V/\mu$ sec at a gain of 10. The amplifier is externally compensated for unity gain with a single 390pF caacitor; no compensation is required for gains above 500. The AD504 has fully protected inputs, which permit differential input voltages of up to  $\pm V_S$  without voltage gain or bias current degradation due to reverse breakdown. The output is also proPIN CONFIGURATION Top View

tected from short circuits to ground and/or either supply voltage, and is capable of driving 1000pF of load capacitance. All models are specified for operation over the 0 to +70°C temperature range, and are supplied in the TO-99 can package.

| MODEL                                                                   | AD504J                             | AD504K                     | AD504L                             | AD504M                                     |

|-------------------------------------------------------------------------|------------------------------------|----------------------------|------------------------------------|--------------------------------------------|

| OPEN LOOP GAIN                                                          |                                    |                            |                                    |                                            |

| $V_{os} = \pm 10V, R_L \ge 2k\Omega$<br>@ T <sub>A</sub> = 0°C to +70°C | 250,000 min<br>125,000 min         | 500,000 min<br>250,000 min | 10 <sup>6</sup> min<br>500,000 min | 10 <sup>6</sup> min<br>500,000 min         |

|                                                                         | 123,000 min                        | 230,000 min                | 500,000 min                        | 300,000 min                                |

| OUTPUT CHARACTERISTICS                                                  |                                    |                            | -                                  | -                                          |

| Voltage (a) $R_L \ge 2k\Omega$ , $T_A = 0^{\circ}C$ to $+70^{\circ}C$   | 1000pF                             |                            |                                    |                                            |

| Load Capacitance<br>Output Current                                      | 10mA min                           | •                          | •                                  |                                            |

| Short Circuit Current                                                   | 25mA                               | •                          | •                                  | •                                          |

| FREQUENCY RESPONSE                                                      |                                    |                            | »                                  |                                            |

| Unity Gain, Small Signal, C <sub>c</sub> = 390pF                        | 300kHz                             | •                          | •                                  | •                                          |

| Full Power Response, C <sub>c</sub> = 390pF                             | 1.5kHz                             | •                          | •                                  | •                                          |

| Slew Rate, Unity Gain, $C_c = 390 pF$                                   | 0.12V/µsec                         | ٠                          | •                                  | •                                          |

| INPUT OFFSET VOLTAGE                                                    |                                    |                            |                                    |                                            |

| Initial Offset, $R_S \le 10k\Omega$                                     | 2.5mV max                          | 1.5mV max                  | 0.5mV max                          | 0.5mV max                                  |

| vs. Temp., $T_A = 0^\circ C$ to +70°C, $V_{os}$ nulled                  | 5.0µV/°C max                       | 3.0µV/°C max               | 1.0µV/°C max                       | 0.5µV/°C max                               |

| $T_{\rm A} = 0^{\circ} {\rm C} \text{ to } +70^{\circ} {\rm C},$        |                                    |                            |                                    |                                            |

| Vos unnulled (Note 1)                                                   | 10µV/°C max                        | 5.0µV/°C max               | 2.0µV/°C max                       | 1.0µV/°C max                               |

| vs. Supply                                                              | 25µV/V max                         | 15µV/V max                 | 10µV/V max                         | 10µV/V max                                 |

| P T <sub>A</sub> = 0°C to +70°C                                         | 40µ√/V                             | 25µV/V max                 | $15\mu V/V max$                    | 15µV/V max                                 |

| vs. Time                                                                | 20µ√/mo                            | 15µV/mo                    | 10µV/mo                            | 10µV/mo                                    |

| INPUT OFFSET CURRENT                                                    |                                    |                            |                                    |                                            |

| @ T <sub>A</sub> = +25°C                                                | 40nA max                           | 15nA max                   | 10nA max                           | 10nA max                                   |

| INPUT BIAS CURRENT                                                      |                                    |                            |                                    |                                            |

| Initial                                                                 | 200nA max                          | 100nA max                  | 80nA max                           | 80nA max                                   |

| $\mathbf{P} \mathbf{T}_{\mathbf{A}} = 0^{\circ} \mathbf{C}$ to +70°C    | 300nA max                          | 150nA max                  | 100nA max                          | 100nA max                                  |

| vs. Temp., $T_A = 0^{\circ}C$ to +70°C                                  | 300pA/ <sup>*</sup> C              | 250pA/°C                   | 200pA/°C                           | 200pA/°C                                   |

| INPUT IMPEDANCE                                                         |                                    |                            |                                    |                                            |

| Differential                                                            | 0.5MΩ                              | 1.0MΩ                      | 1.3MΩ                              | 1.3ΜΩ                                      |

| Common Mode                                                             | 100MΩ  4pF                         | •                          | •                                  | 6                                          |

| INPUT NOISE                                                             |                                    |                            |                                    |                                            |

| Voltage, 0.1Hz to 10Hz                                                  | 1.0μV (p-p)                        | •                          | •                                  | 0.6µV (p-p) max                            |

| f = 100Hz                                                               | $10nV/\sqrt{Hz}$ (rms)             |                            |                                    | 10nV/VHz (rms) max                         |

| f = 1kHz                                                                | 8nV/VHz (rms)                      |                            | •                                  | 9nV/VHz (rms) max                          |

| Current, $f = 10Hz$                                                     | $1.0pA/\sqrt{Hz}$ (rms)            | •                          |                                    | 1.3pA/VHz (rms) max<br>0.6pA/VHz (rms) max |

| f = 100Hz<br>f = 1kHz                                                   | 0.6pA/√Hz (rms)<br>0.5pA/√Hz (rms) |                            |                                    | $0.3pA/\sqrt{Hz}$ (rms) max                |

|                                                                         | 0.5pA/\ n2 (ms)                    |                            |                                    | 0.5pA/V nz (ms) max                        |

| INPUT VOLTAGE RANGE<br>Differential or Common Mode, max safe            | ±Vs                                | •                          | •                                  | •                                          |

| Common Mode Rejection, $V_{in} = \pm 10V$                               | 94dB min                           | 100dB min                  | 110dB min                          | 110dB min                                  |

| POWER SUPPLY                                                            |                                    |                            |                                    | ······································     |

| Rated Performance                                                       | ±15V-                              | •                          | •                                  | •                                          |

| Operating                                                               | ±(5 to 18)V                        |                            | ٠                                  | •                                          |

| Current, Quiescent                                                      | ±4.0mA max                         | ±3.0mA max                 | ±3.0mA max                         | ±3.0mA max                                 |

| TEMPERATURE RANGE                                                       |                                    |                            |                                    |                                            |

| Operating, Rated Performance                                            | 0 to +70°C                         | •                          | •                                  | •                                          |

| Storage                                                                 | -65°C to +150°C                    | •                          | •                                  | •                                          |

| PRICE                                                                   |                                    |                            |                                    |                                            |

| (1-24)                                                                  | \$11.20                            | \$19.80                    | \$28.00                            | \$30.00                                    |

| (25-99)                                                                 | 9.55                               | 16.80                      | 21.80                              | 23.80                                      |

| (100–999)<br>NOTES:                                                     | 8.40                               | 15.30                      | 20.40                              | 22.00                                      |

# Lowest Cost High Accuracy IC Op Amps

#### FEATURES

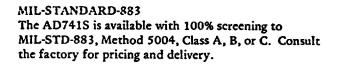

Precision Input Characteristics Low Vos: 0.5mV max (L) Low  $V_{os}$  Drift:  $5\mu V/^{\circ}C$  max (L) Low Ib: 50nA max (L) Low Ios: 5nA max (L) High CMRR: 90dB min (K, L) **High Output Capability**  $A_{ol} = 25,000 \text{ min}, 1k\Omega \text{ load } (J, S)$ T<sub>min</sub> to T<sub>max</sub>  $V_0 = \pm 10V \text{ min}, 1k\Omega \text{ load } (J, S)$ Low Cost (100 pieces) AD741J \$1.25 \$2.25 AD741K AD741L \$6.00 AD741S \$3.30

#### **GENERAL DESCRIPTION**

The Analog Devices AD741J, AD741K, AD741L and AD741S are specially tested and selected versions of the popular AD741 operational amplifier. Improved processing and additional electrical testing guarantee the user precision performance at a very low cost. The AD741J, K and L substantially increase overall accuracy over the standard AD741C by providing maximum limits on offset voltage drift. and significantly reducing the errors due to offset voltage, bias current, offset current, voltage gain, power supply rejection, and common mode rejection (see Error Analysis). For example, the AD741L features maximum offset voltage drift of  $5\mu V/^{\circ}C$ , offset voltage of 0.5mV max, offset current of 5nA max, bias current of 50nA max, and a CMRR of 90dB min. The AD741S offers guaranteed performance over the extended temperature range of -55°C to +125°C, with max offset voltage drift of  $15\mu V/^{\circ}C$ , max offset voltage of 4mV, max offset current of 25nA, and a minimum CMRR of 80dB.

#### HIGH OUTPUT CAPABILITY

Both the AD741J and AD741S offer the user the additional advantages of high guaranteed output current and gain at low values of load impedance. The AD741J guarantees a minimum gain of 25,000, swinging  $\pm 10V$  into a  $1k\Omega$  load from 0°C to +70°C. The AD741S guarantees a minimum gain of 25,000, swinging  $\pm 10V$  into a  $1k\Omega$  load from -55°Cto +125°C.

All devices feature full short circuit protection, high gain, high common mode range, and internal compensation. The AD741J, K and L are specified for operation from 0°C to +70°C, and are available in both the TO-99 and mini-DIP packages. The AD741S is specified for operation from -55°C to +125°C, and is available in the TO-99 package.

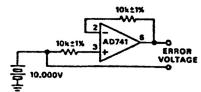

#### **GUARANTEED ACCURACY**

The vastly improved performance of the AD741J, AD741K, AD741L and AD741S provides the user with an ideal choice when precision is needed and economy is a necessity. An error budget is calculated for all versions of the AD741 (see page 3); it is obvious that these selected versions offer substantial improvements over the industry-standard AD741C and AD741. A typical circuit configuration (see Figure 1) is assumed, and the various errors are computed using maximum values over the full operating temperature range of the devices. The results indicate a factor of 8 improvement in accuracy of the AD741L over the AD741C, a factor of 5 improvement using the AD741K, and a factor of 2.5 improvement using the AD741J. The AD741S. similarly, achieves a factor of 3.5 improvement over the standard AD741. Note that the total error has been determined as a sum of component errors, while in actuality, the total error will be much less. Also, while the circuit used for the error analysis is only one of a multitude of possible applications, it effectively demonstrates the great improvement in overall 741 accuracy achievable at relatively low cost with the AD741J, K, L or S.

Figure 1. Error Budget Analysis Circuit

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062 Tel: 617/329-4700 TWX: 710/394-6577

# SPECIFICATIONS (typical @ +25°C and ±15VDC, unless otherwise specified)

| MODEL                                                             | AD741J                                 | AD741K                                              | AD741L                                        | AD741S                                    |

|-------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------|-----------------------------------------------|-------------------------------------------|

| OPEN LOOP GAIN                                                    | ······································ |                                                     |                                               |                                           |

| $R_L = 1k\Omega, V_0 = \pm 10V$                                   | 50,000 min (200,000 typ)               |                                                     | · .                                           | •                                         |

| $R_L = 2k\Omega, V_0 = \pm 10V$                                   |                                        | 50,000 min (200,000 typ)                            | 50,000 min (200,000 typ)                      |                                           |

| Over Temp Range, Tmin to Tmax,                                    |                                        |                                                     |                                               |                                           |

| same loads as above                                               | 25,000 min                             | •                                                   | •                                             | •                                         |

| OUTPUT CHARACTERISTICS                                            |                                        | ,                                                   |                                               |                                           |

| Voltage <b>@</b> $R_L = 1k\Omega$ , $T_{min}$ to $T_{max}$        | ±10V min (±13V typ)                    |                                                     |                                               | •                                         |

| Voltage @ $R_L = 2k\Omega$ , $T_{min}$ to $T_{max}$               |                                        | ±10V min (±13V typ)                                 | ±10V min (±13V typ)                           |                                           |