VLA TECHNICAL REPORT #28

MODULE T1 MODEM

W. E. DUMKE

OCTOBER 1976

# TABLE OF CONTENTS

| 1.0  | General Description                                   |

|------|-------------------------------------------------------|

| 2.0  | Theory of Operation                                   |

|      | A. R. F. Subassembly                                  |

|      | B. Phase Locked Local Oscillator                      |

| 3.0  | Module Specifications and Power Levels                |

| 4.0  | Circuit Details                                       |

|      | A. Voltage Regulator                                  |

|      | B. Synchronous Debounce Circuit                       |

|      | C. Pin Diode Driver                                   |

|      | D. Phase Locked Loop                                  |

|      | 1. IF Video Amplifier                                 |

|      | 2. Comparator/Level Shifters                          |

|      | 3. Phase Detector                                     |

|      | 4. Integrator                                         |

|      | 5. Sweep Circuit                                      |

|      | 6. Varactor Clamp and Free Run Bias Set 4-12          |

|      | 7. Lock Indication Circuit                            |

|      | 8. Logic                                              |

|      | 9. Monitor Buffers                                    |

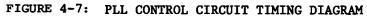

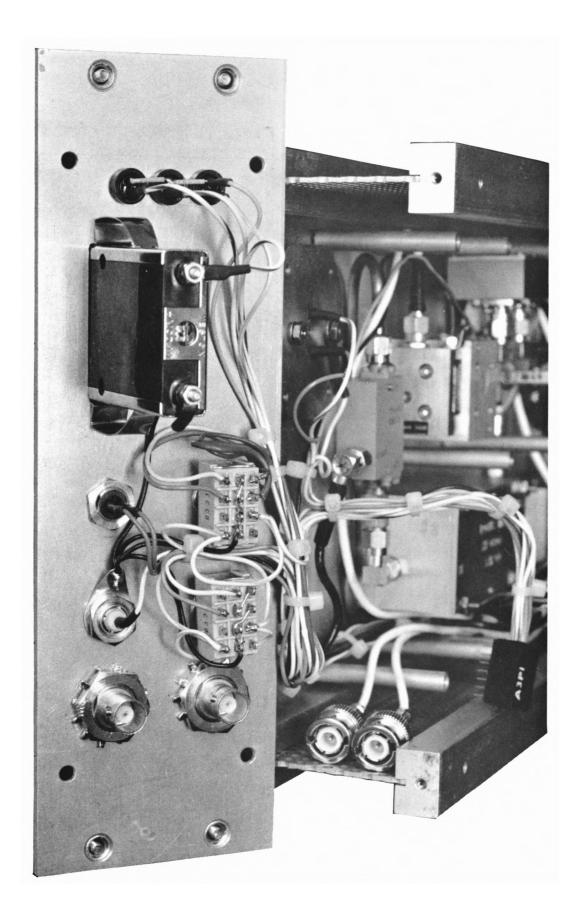

|      | E. Modem Wire Harness                                 |

| 5.0  | Front Panel Indicators and Controls                   |

| 6.0  | Preliminary Module Adjustments                        |

| 7.0  | Test Procedure, Monitor and Control Functions (Tl and |

|      | T2), RF Calibration (T1)                              |

|      | A. Connection of Tl and T2 to TEST SET                |

|      | B. Control Function Checkout                          |

|      | C. Monitor Function Checkout                          |

|      | D. RF Calibration Procedure (T1)                      |

| 8.0  | Modem Measurements                                    |

| 9.0  | Digital Communications System Address Assignments 9-1 |

| 10.0 | Modem Module (T1) Drawing List                        |

| 11.0 | Specifications                                        |

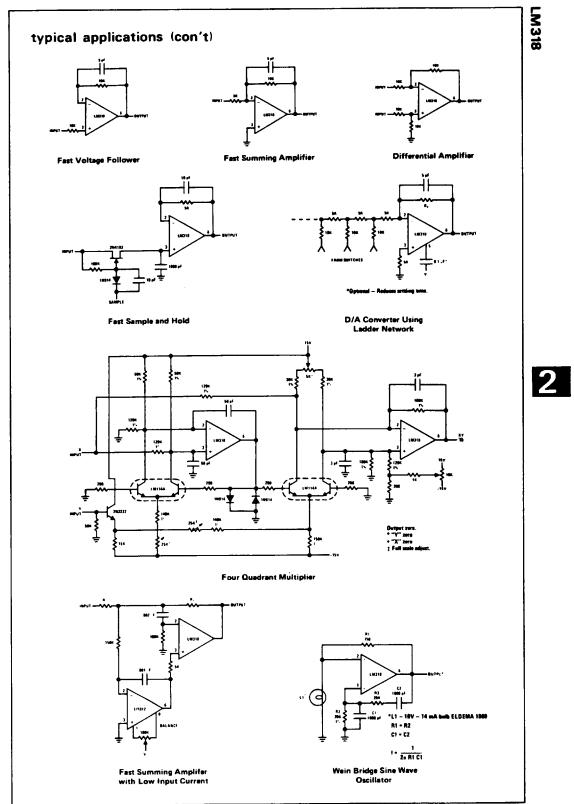

| 12.0 | Data Sheets                                           |

|      |                                                       |

#### FIGURES

- Figure 1-1. Modem Waveguide Channel Allocations

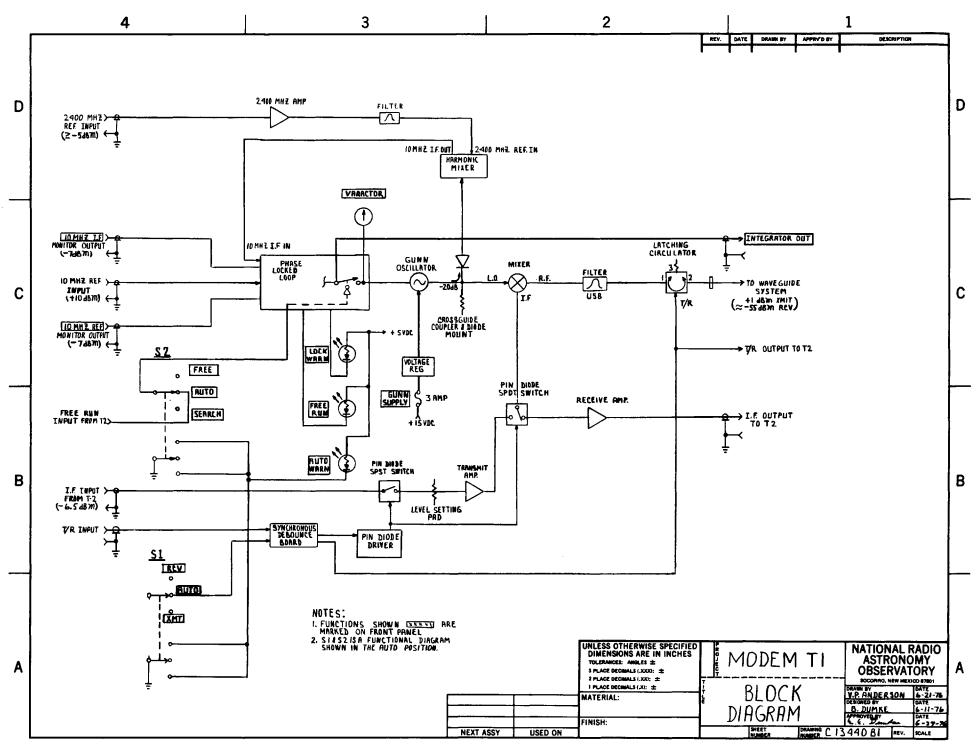

- Figure 2-1. Modem Tl Block Diagram

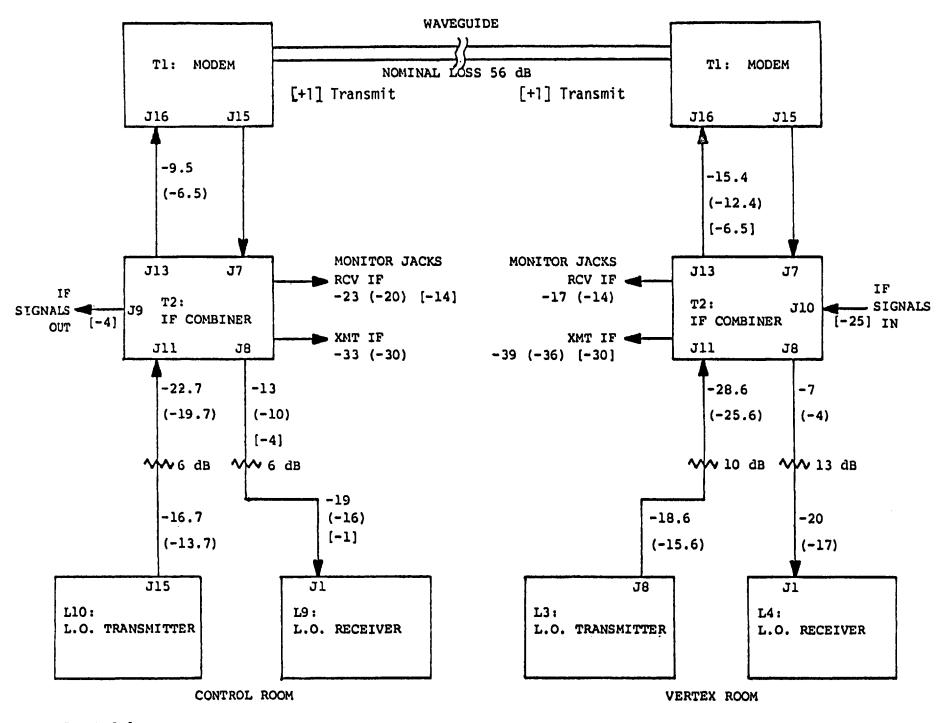

- Figure 3-1. System Levels and Pads

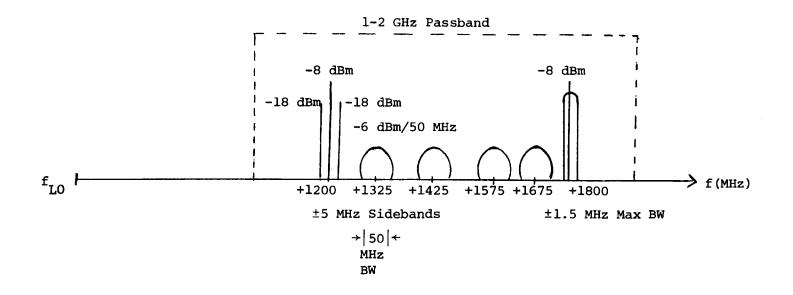

- Figure 3-2. Tl RF Transmit Passband at Waveguide

- Figure 3-3. T1 IF Transmit Passband at J16 Input

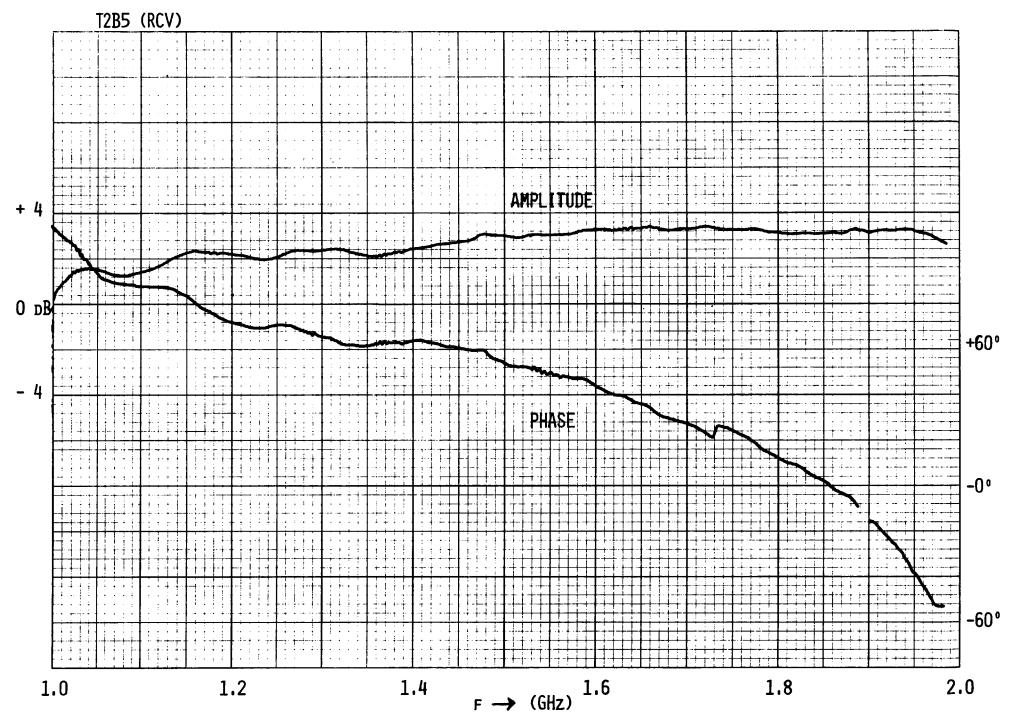

- Figure 3-4. Tl IF Receive Passband at J15 Output

- Figure 3-5. Tl Passband Variations

- Figure 3-6. Tl Noise Figure Budget

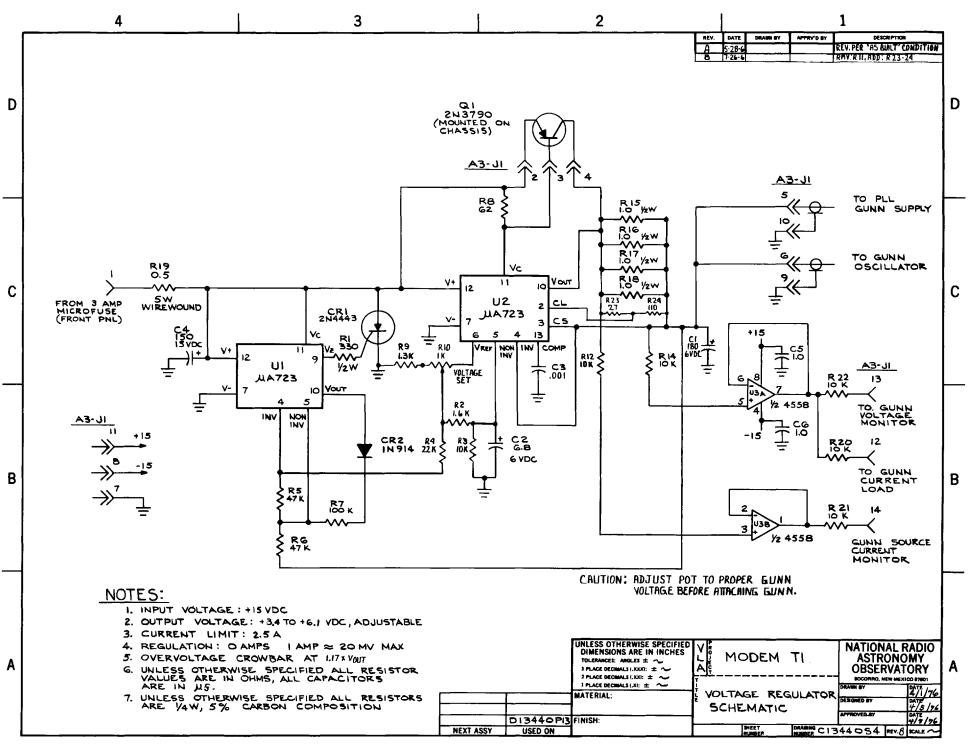

- Figure 4-1. Voltage Regulator Schematic

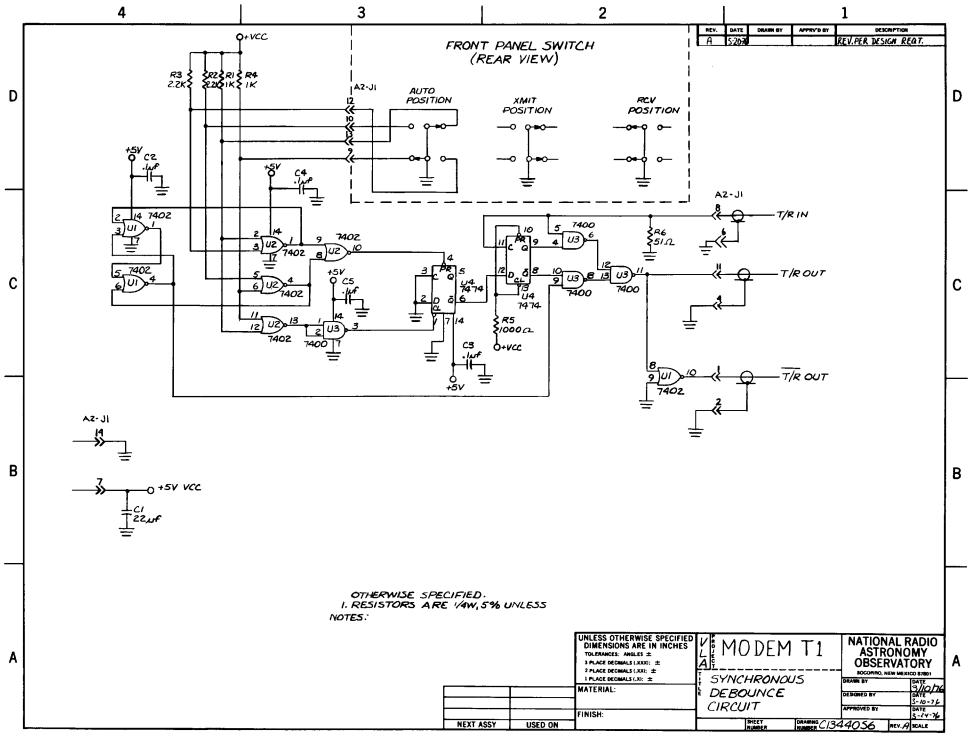

- Figure 4-2. Synchronous Debounce Circuit

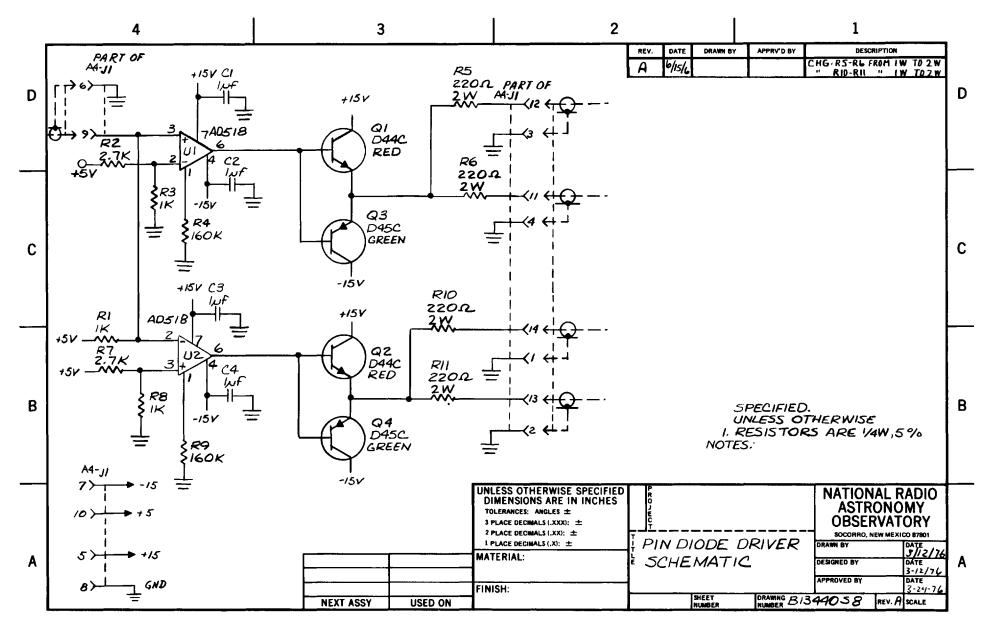

- Figure 4-3. Pin Diode Driver Schematic

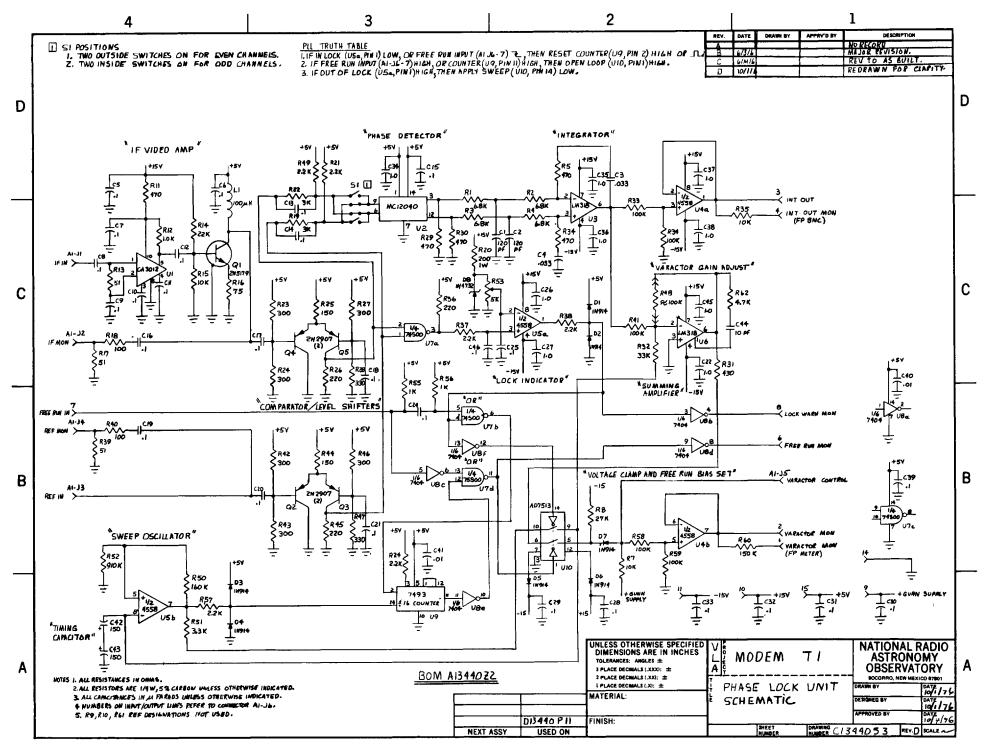

- Figure 4-4. Phase Lock Unit Schematic

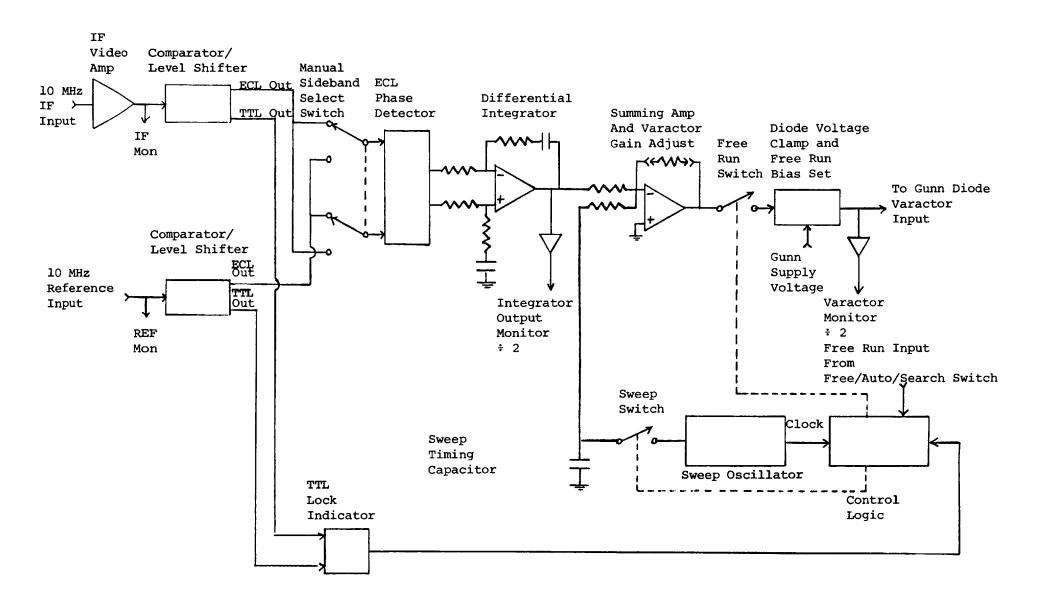

- Figure 4-5. Phase Lock Unit Block Diagram

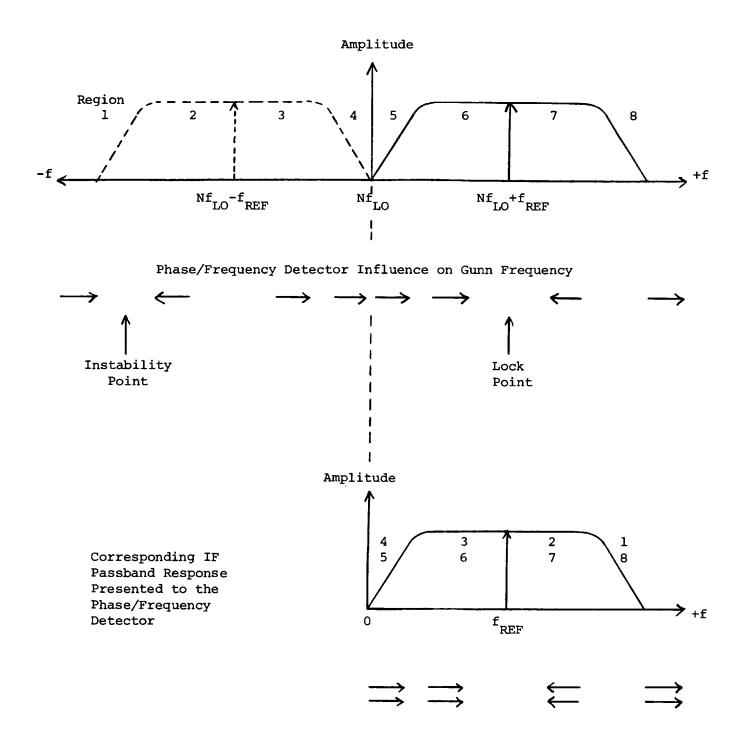

- Figure 4-6. Phase-Frequency Detector Influence on Gunn Frequency

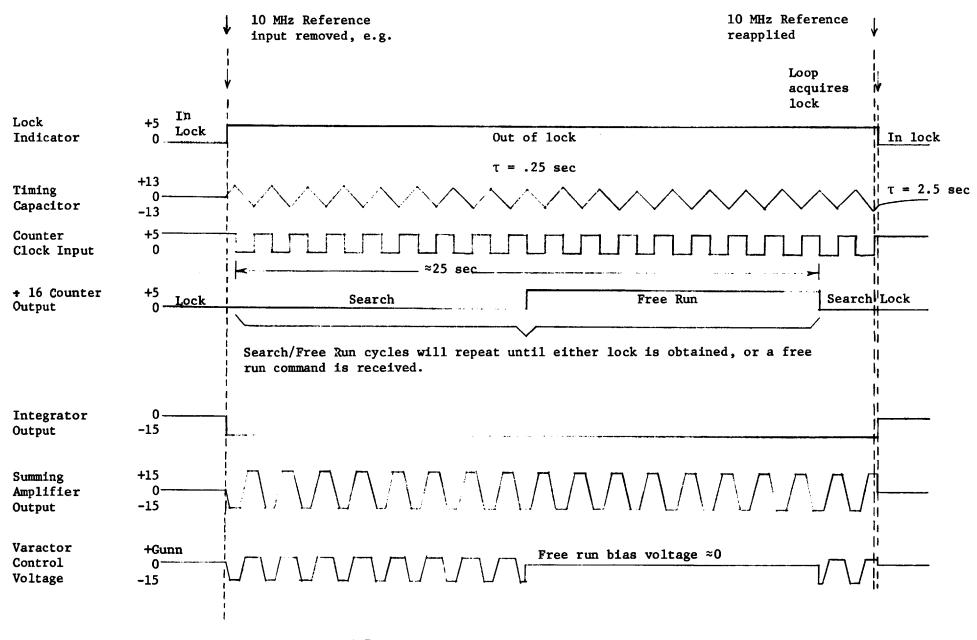

- Figure 4-7. PLL Control Circuit Timing Diagram

- Figure 4-8. Modem Wire Harness

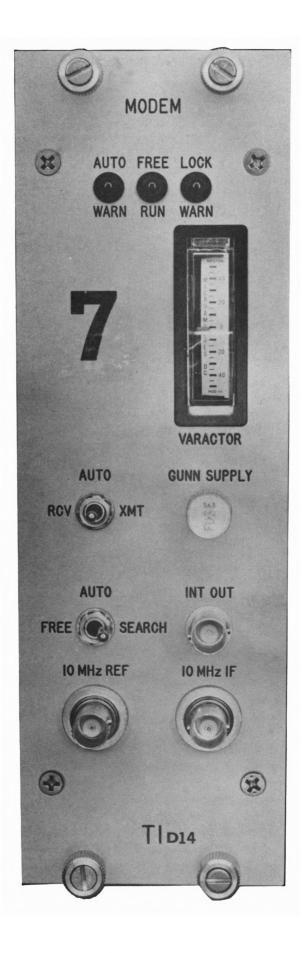

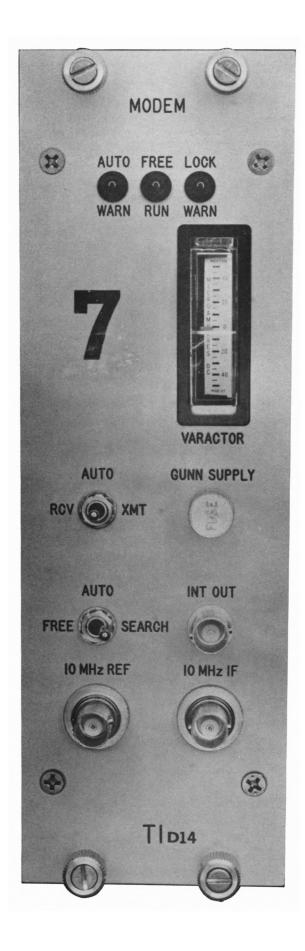

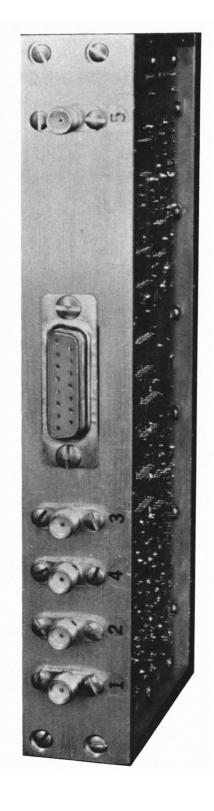

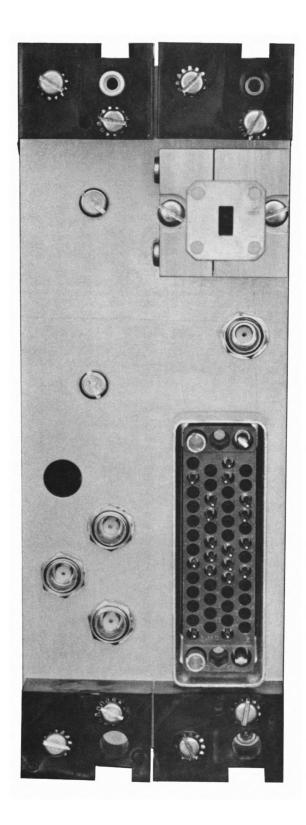

- Figure 5-1. Modem Tl Front Panel

- Figure 8-1. Spectrum Analyzer Response at 10 MHz IF Front Panel Connector

- Figure 8-2. IF Combiner T2 Modem T1 Transmit Switching Time

- Figure 8-3. Modem T1-IF Combiner T2 Receive Switching Time

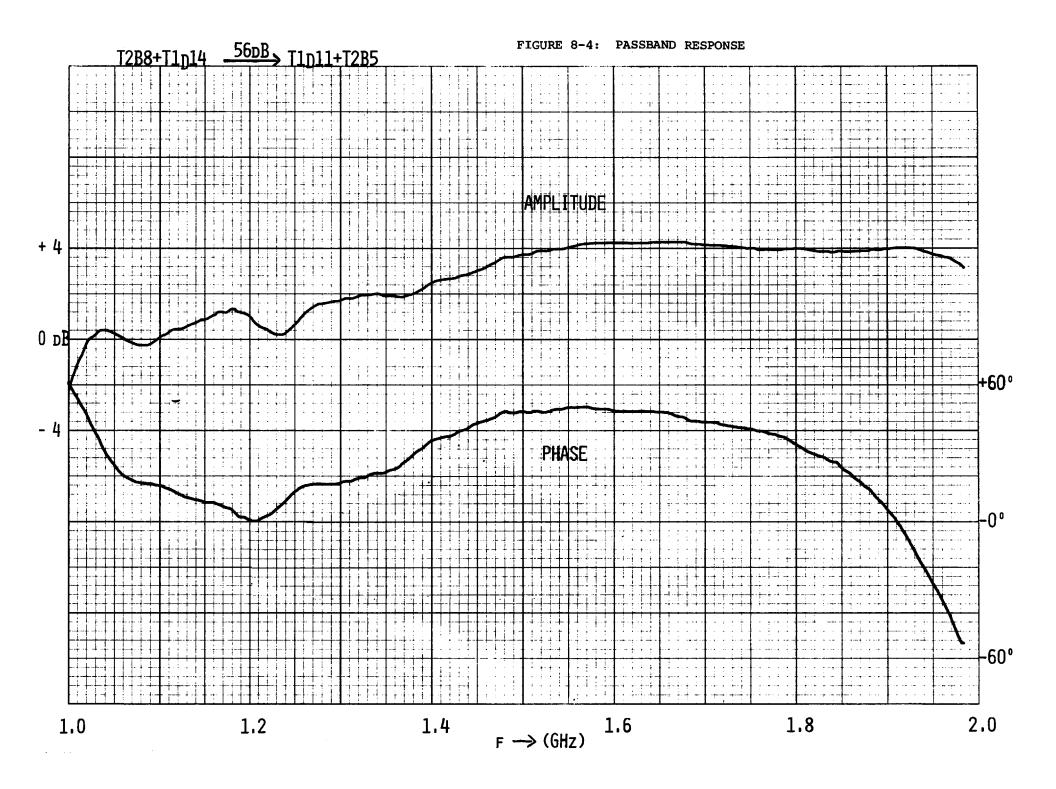

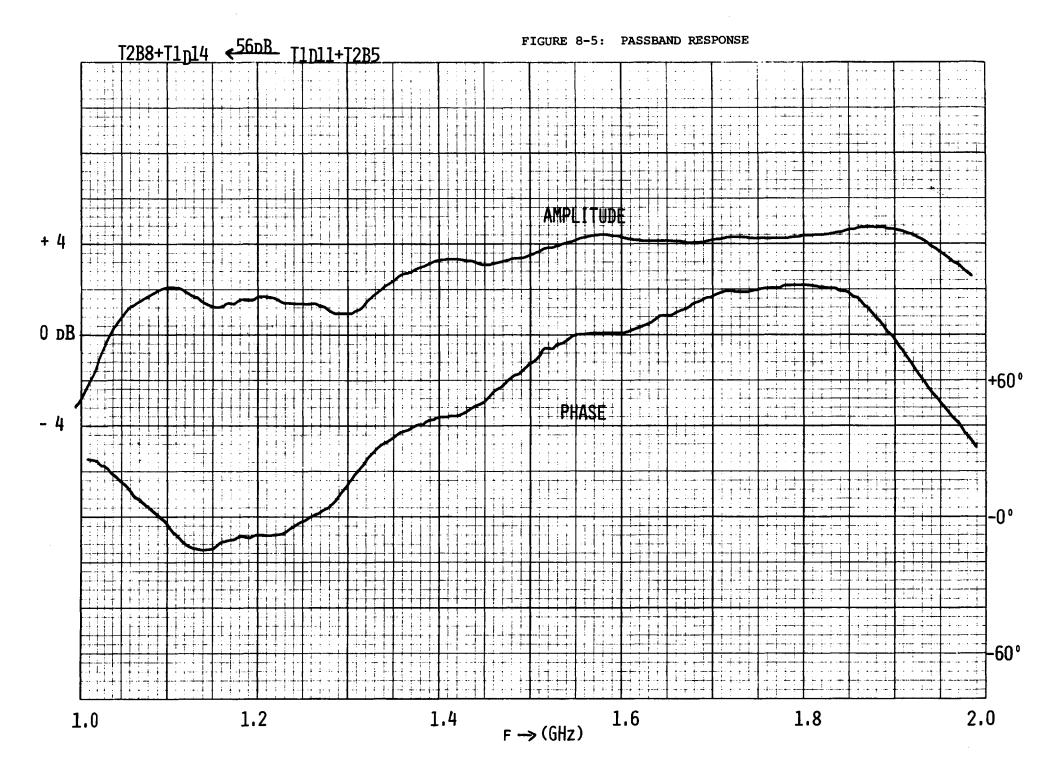

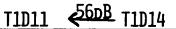

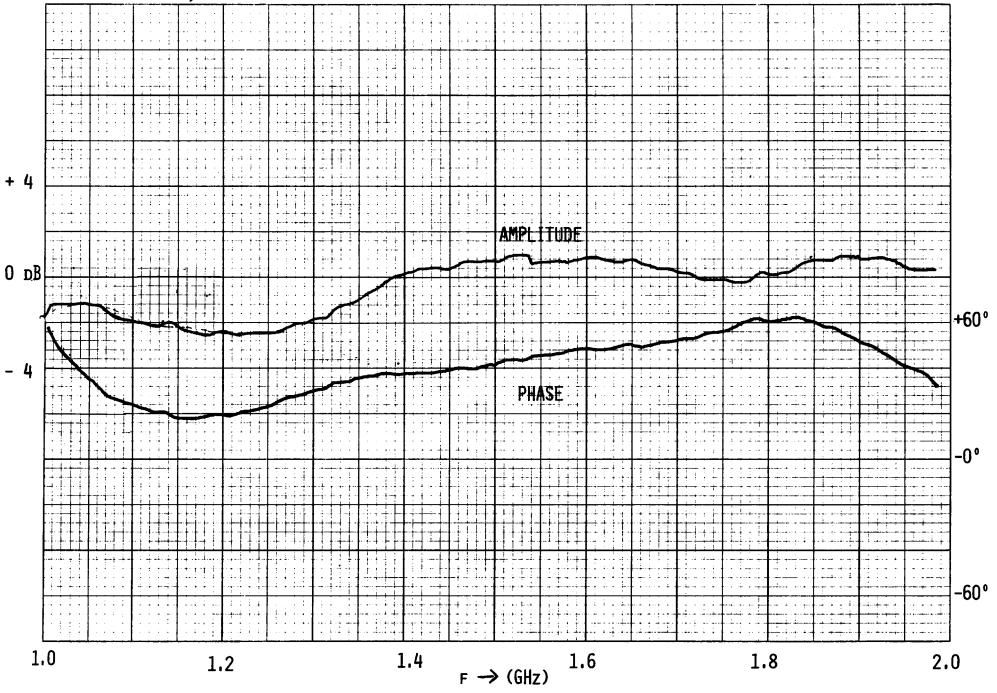

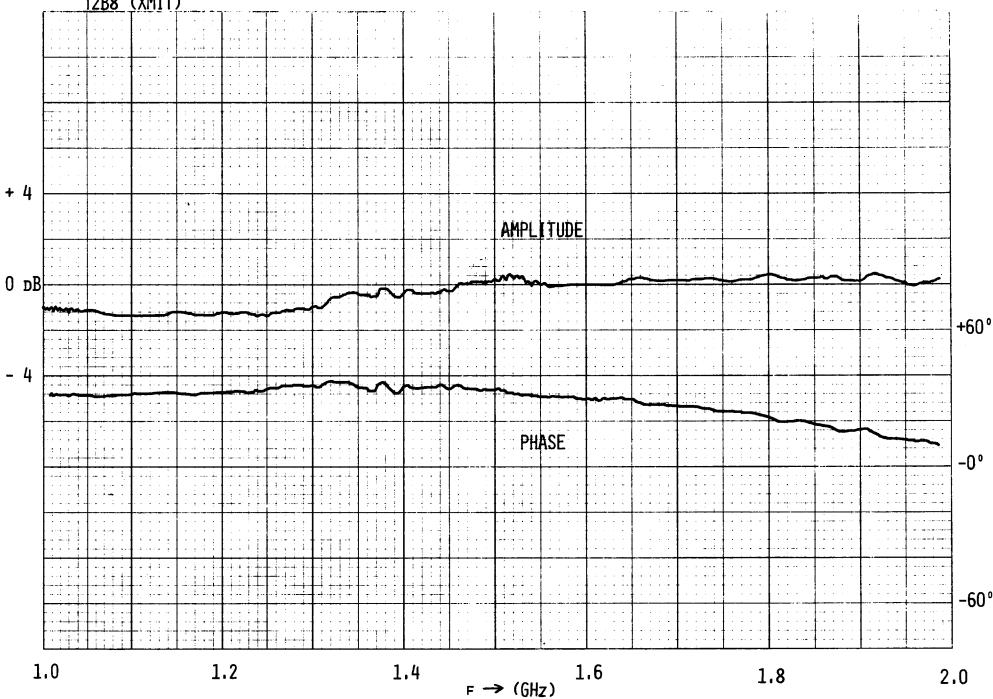

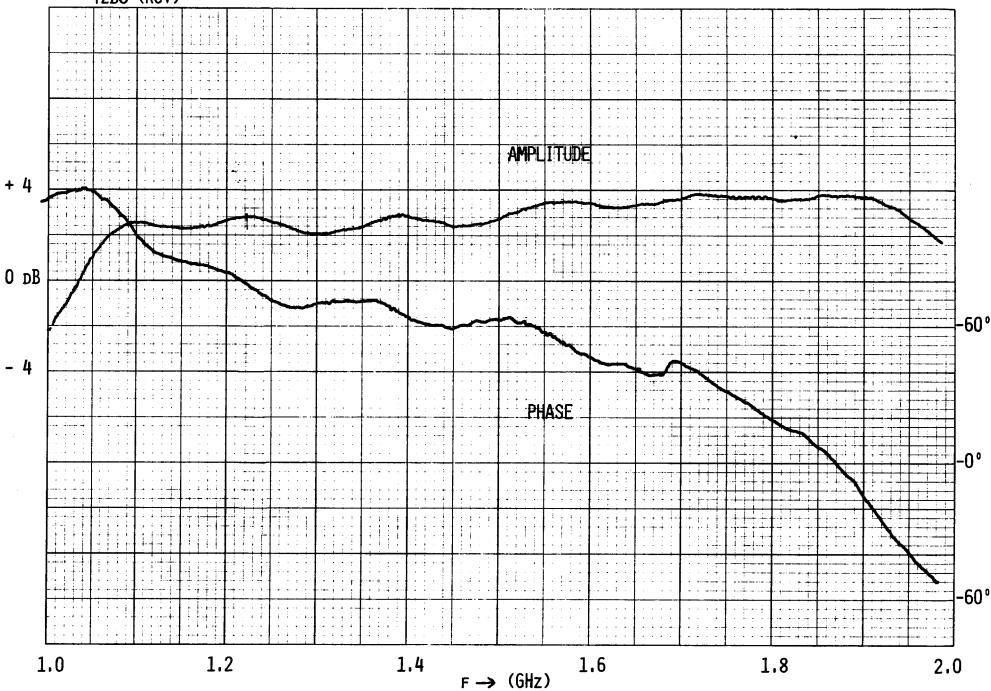

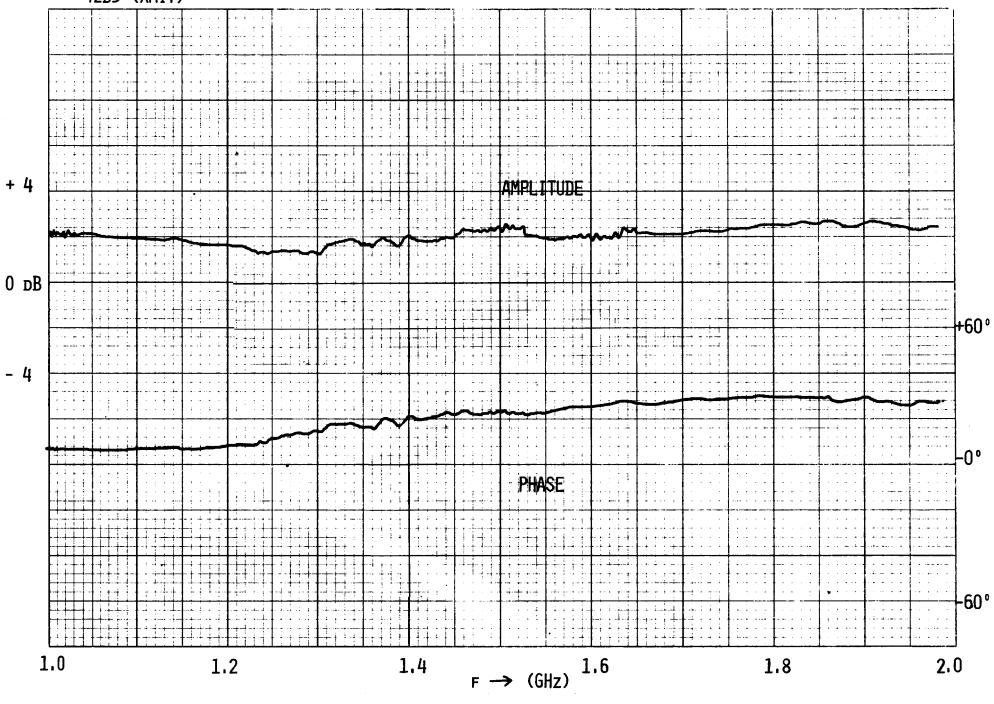

- Figure 8-4 8-11. Passband Responses

- Figure 9-1. DCS Addresses Vertex Room

- Figure 9-2. DCS Addresses Control Building

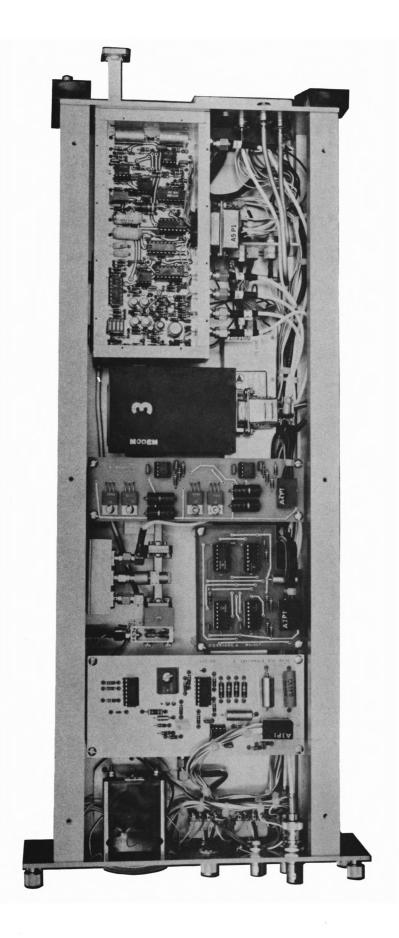

# 1.0 GENERAL DESCRIPTION

The "Modem" Tl with its support module, the "IF Combiner" T2 provide a two-way communications system between the control building and each antenna.

The Modem along with the waveguide comprise a closed single sideband millimeter wave system which operates on various channels from 27.4 to 52.4 GHz.

The Modem is basically a millimeter wave/1-2 GHz up/down mixer with a phase locked local oscillator.

The signals to be transmitted are combined from other modules in the accompanying "IF Combiner" T2 module. This unit also distributes the 1 GHz to 2 GHz received Modem IF passband to various other modules, besides interfacing itself and the Modem to the local Digital Communications System system.

The Modem system transmits "LO signals", used for electrical measurement of the waveguide length, and digital commands to each antenna. In turn, it receives "LO signals", digital and analog monitor data, and the front end IF signals from each antenna. All are contained in a Modem IF passband from 1 to 2 GHz. Typical Modem IF passbands are shown in Figure 3-2, 3, 4.

Since there is one common waveguide run between all antennas on a given arm and the control building, the signals are frequency division as well as time division multiplexed. Each antenna position in a given array has a specific channel allocated to it. The channels are given in Figure 1-1. Each antenna modem transmits for 49 msec and receives for 1 msec. Each control building modem transmits for 1 msec and receives for 49 msec.

Because of the broad frequency range covered in the waveguide system, modems are built for specific channels only. Thus only modems of a specific channel are compatible. The modems used at the vertex rooms of the antennas are identical to those used at the control building and may be substituted upon proper adjustment of the receive level on the T2 Module.

Since the T2 Module only operates with the 1-2 GHz Modem IF passband, which is not influenced by a specific channel, all IF Combiner T2 Modules are interchangeable upon proper adjustment of the receive level.

|         | LOCAL OSCILLATOR     | SIGNAL BAND |       |

|---------|----------------------|-------------|-------|

| CHANNEL | FREQUENCY            | LOW         | HIGH  |

|         | f <sub>o</sub> , GHz |             |       |

|         |                      |             |       |

| 1       | 26.41                | 27.41       | 28.41 |

| 2       | 28.79                | 29.79       | 30.79 |

| 3       | 31.21                | 32.21       | 33.21 |

| 4       | 33.59                | 34.59       | 35.59 |

| 5       | 36.01                | 37.01       | 38.01 |

| 6       | 38.39                | 39.39       | 40.39 |

| 7       | 40.81                | 41.81       | 42.81 |

| 8       | 43.19                | 44.19       | 45.19 |

| 9       | 45.61                | 46.61       | 47.61 |

| 10      | 47.99                | 48.99       | 49.99 |

| 11      | 50.41                | 51.41       | 52.41 |

|         |                      |             |       |

| L       | I                    |             |       |

#### 2.0 THEORY OF OPERATION

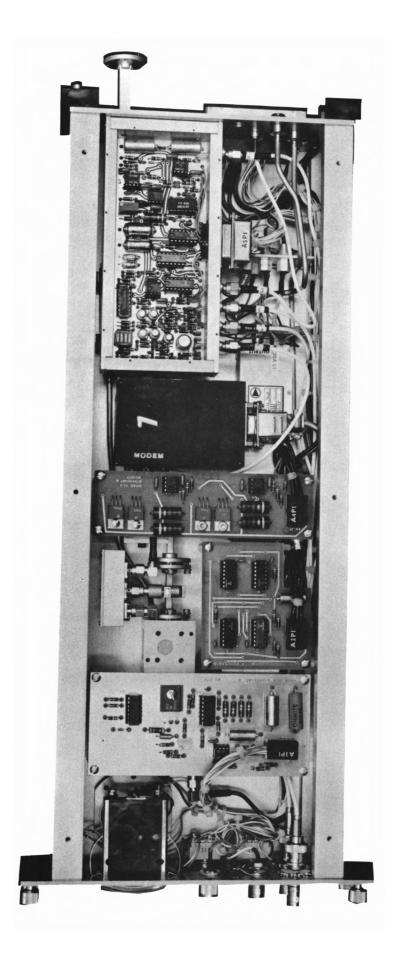

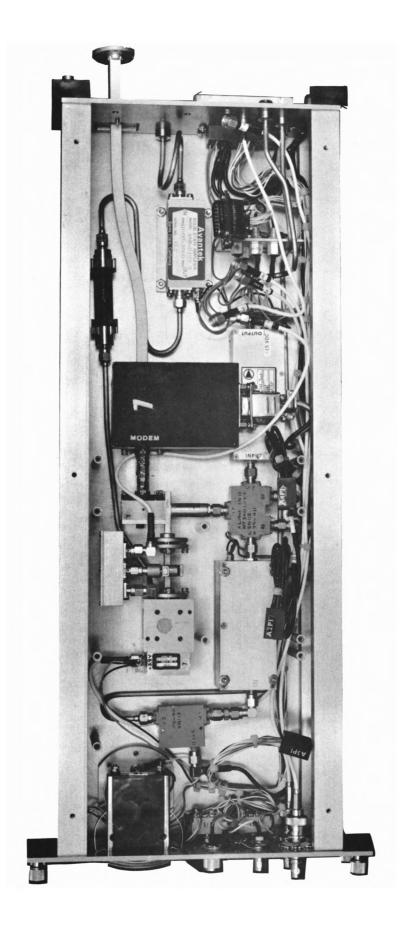

Refer to the modem block diagram of Figure 2-1.

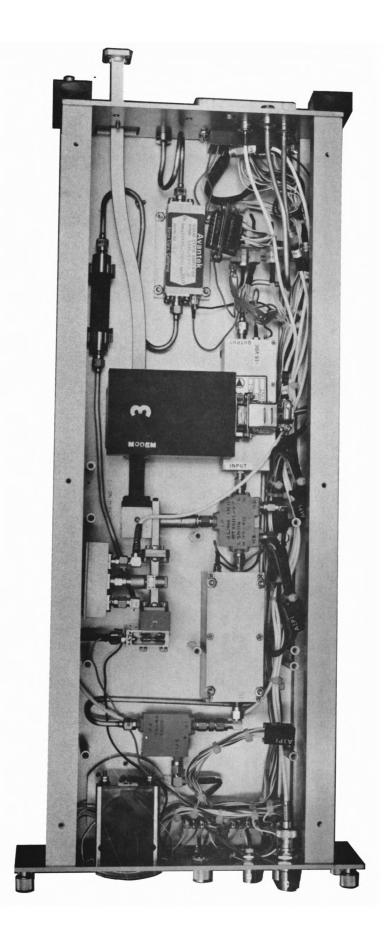

#### A. R. F. SUBASSEMBLY

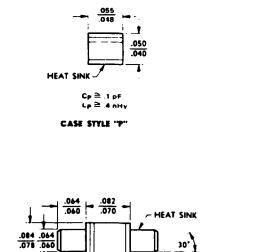

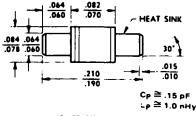

The Modem Mixer is used in both transmit and receive, without any switching of diode bias voltages to improve performance in either of the two modes. Thus while performance may not be optimum, reliability is increased because of more mechanically stable diode mounts and because of the elimination of noise pickup on the bias line. Also since the diodes in the "Spacekom" mixers are in a standard sealed pill package, they are more rugged, easier to change, multi-sourced and may be easily replaced later by better devices as the state of the art improves. Two diodes are used in each mixer to provide a better 1 dB compression point in the transmit mode.

The mixers are purchased for individual waveguide channels with the upper sideband RF passband filter attached, since the electrical distance from the mixer to the filter is critical for image enhancement, and thus optimum performance.

Because of the requirements for a low VSWR to be presented to the waveguide system in both transmit and receive, a latching three port circulator with port 3 terminated is used as a two port isolator, and is placed between the mixer/filter combination and the waveguide system to isolate the mixer from the waveguide. This unidirectional device switches direction of propagation on the edges of the transmit/ receive pulse. Because it switches on the edges of the T/R pulse, the T/R pulse must be free of "bounce" or "transients" for reliable operation. A "synchronous debounce circuit" removes any transient noise or bounce from S1, the front panel transmit/receive/auto switch and prevents the switch from interrupting the circulator T/R pulse train until a complete cycle of transmit or receive has been obtained. This insures a long enough duration of T/R pulse to enable the circulator to fully switch states, when Sl is thrown into either manual transmit or manual receive. However, this requires the T/R pulse train to be present for operation of the switch.

The latching circulator changes states by applying a short duration current pulse to an internal hard iron core electro-magnet. Thus when power is removed to the circulator it will remain in whatever

FIGURE 2-1

state it was switched to prior to power removal. Because of the need to switch this inductive load, transients are induced into the wiring of the modem module. But since the modem system is allowed 100 microseconds to acquire a stable state after the T/R pulse, system operation is not affected.

The output of the circulator is coupled to the waveguide system through a waveguide extension (WR-28, 26.5-40 GHz, for Channels 1-6 and WR-22, 33-50 GHz, for Channels 7-10). It should be noted that WR-19, 40-60 GHz, is used for all internal microwave components on Channels 7-10 except for the output side of the circulator and the waveguide extension. WR-22 was chosen for external waveguide runs because of its lower losses. The decision to use WR-19 for the Modem microwave components was arrived at before the decision on external rectangular waveguide runs.

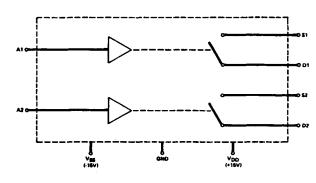

A bidirectional IF port on the modem mixer is gated with the T/R signal between a high 1 dB compression point transmit amplifier and a low noise receive amplifier. (A pin diode driver board interfaces the high current - high voltage requirements of both pin diode switches with the TTL T/R signal.) This single pole double throw pin diode switch has high isolation,  $\leq -60$  dB, between ports to minimize feed-through of the transmit signal into the receive system. The high 1 dB compression point on the transmit amplifier of +17 dBm minimum permits the maximum modem output transmit power with minimal intermodulation to be dependent on the limiting factor of mixer diode capability ( $\geq$  + 5 dBm at 1 dB compression) rather than on the transmit amplifier.

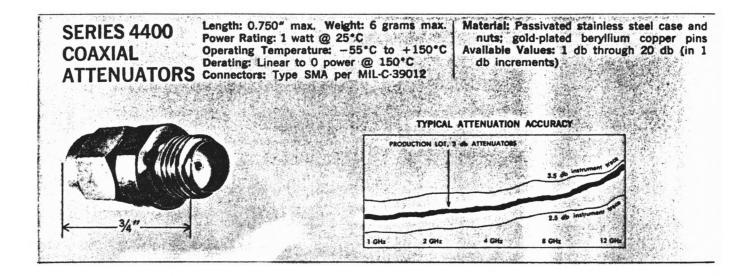

A level setting pad on the input to the transmit amplifier is custom selected for each modem to provide z + 1 dBm output at the waveguide port for -6.5 dBm input at the transmit IF input port, J16. Thus the + 5 dBm minimum compression point of each modem mixer may be taken advantage of even though the amplifier gain and mixer conversion loss may vary.

A single pole single throw pin diode switch with -40 dB isolation and gated by the T/R pulse is placed before the level setting pad to aid in preventing feedthrough of transmit signals into the receive system during receive. If the pad was placed before the pin diode switch, better passband ripple due to input VSWR and the long line of coaxial cable from T2 to T1 would be obtained. However, the transmit amplifier was found to oscillate when the

SPST switch on the input and the SPDT switch at the output were gated off. This problem, probably caused by higher input-output feedback due to the reactances presented to the amplifier with the switches off, could be prevented by placing the level setting pad between the SPST switch and the transmit amplifier's input, thus insuring a good match at the input under any condition and thus stable operation due to less feedback.

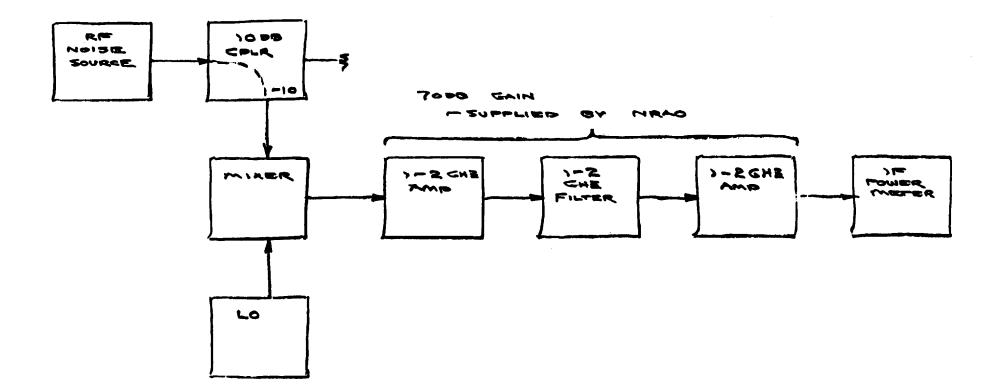

A low noise (3 dB maximum noise figure) 1-2 GHz receive amplifier is placed at the other port of the SPDT pin diode switch. A noise figure budget is given in Figure 3-6.

#### B. PHASE LOCKED LOCAL OSCILLATOR

A "Gunn" oscillator is used as the local oscillator for the modem mixer. No adjustment is provided for setting the power output (+17 dBm  $\pm$  1 dB) of the Gunn oscillator. A voltage regulator for the Gunn oscillator includes current limiting and overvoltage crowbar circuits to protect the oscillator from damage in the event of accidental transients. The crowbar is used in conjunction with a 3 amp fuse mounted on the front panel of the module.

In order to maintain frequency stability the Gunn oscillator is voltage tuned and phase locked to signals derived from the external crystal controlled "LO" System. A 2400 MHz reference signal from the LO system is amplified by a 1-2 GHz Avantek broadband amplifier (Avantek ASD-8199M) operated in saturation. The Avantek 1-2 GHz amplifier was chosen for this application rather than another amplifier built for 2.4 GHz because of several reasons. The amplifier still has good performance at 2400 MHz and as a general purpose 1-2 GHz amplifier it is utilized in many other places in the VLA electronics system. Thus replacement is easier. And since the quantity purchased each year is greater it is also cost effective.

A 2400 MHz filter with a -3 dB bandwidth of 200 MHz is placed after the 2400 MHz filter for rejection of spurious frequencies.

Approximately +15 dBm of 2400 MHz carrier at the output of the filter drives a harmonic mixer diode to provide harmonics of 2400 MHz for mixing with the Gunn oscillator output to provide a 10 MHz difference signal for comparison with a 10 MHz reference signal in the modem phase locked loop circuit. The silicon Schottky

barrier diode (Aertech #A2S123) is mounted in a combination waveguide coupler and diode mount providing 20 dB isolation from the output of the Gunn oscillator and a waveguide backshort tuning adjustment to provide some matching to the diode at the Gunn oscillator frequency in use. Some matching to the 10 MHz IF output and to the 2400 MHz reference input is provided by the harmonic mixer box attached to the SMA connector on the diode mount. No bias adjustment is used. Diodes may have to be hand selected for particular channels and diodes may have to be inserted in the mount in each of the two possible directions to optimize performance. The 10 MHz IF output, > -50 dBm, is amplified by a video amplifier in the phase locked loop and is compared against a 10 MHz reference signal from the LO system by a modulo  $4\pi$  phasefrequency detector. A high gain integrator following the phase detector insures a high gain loop. Thus under all legitimate lock conditions the IF and reference signals will be at  $0^0$  phase difference. Therefore, a simple lock indication circuit can be utilized which is used to turn off the sweep voltage once phase lock is achieved and to indicate proper operation of the phase locked loop system.

Because the Gunn oscillator tuning range ( $\geq$  200 MHz) and temperature drift are much larger than the IF reference frequency (10 MHz) it is necessary to implement a sweep system in the phase locked loop circuit to insure that the loop can acquire lock under worst case Gunn oscillator frequency drift conditions.

A sweep voltage from the timing capacitor of an internal astable multivibrator is added to the phase locked loop integrator output by use of a summing amplifier. Once the loop acquires lock the sweep voltage is removed from the summing amplifier and the loop remains in lock.

Control logic in the phase locked loop box permits a maximum of 8 two-way sweeps to acquire lock. If for some reason the loop cannot acquire lock the control circuitry will open the loop to the varactor and place a bias voltage on the varactor corresponding to the normal lock point for a time period corresponding to another 8 two-way sweeps (z 10 seconds).

This "free run" condition serves as a back-up system to the phase locked loop and will permit momentary operation of the

digital control system through the waveguide as long as both modem's Gunn oscillators are within 25 MHz of each other. If during this period a "free run command" (open loop command) is received in the T2 module's free run - search flip-flop, the modem phase locked loop will remain open and digital communications to the antenna can be utilized to diagnose the problem. Note that since a 53 second timer in the T2 module will reset this free run - search flip-flop to the normal search condition, a continuous chain of free run commands, at least one every 53 seconds must be issued.

If no free run command is received by the T2 module, the "search" condition will cause the module to continuously alternate between sweep cycles and free run periods until lock is obtained. A free run - auto - search switch on the front panel of T1 may be used to manually set the loop into either mode for test purposes. This switch has priority over the incoming command from T2.

Because the free run function permits digital communications only if the two modem's Gunn oscillators are within 25 MHz of each other's frequencies, the Gunn oscillators must be manually set to frequency after the modem has reached operating temperature in the rack. This can be done with a screwdriver adjustment on the Gunn oscillator itself, and should be checked periodically for drift.

#### 3.0 MODULE SPECIFICATIONS AND POWER LEVELS

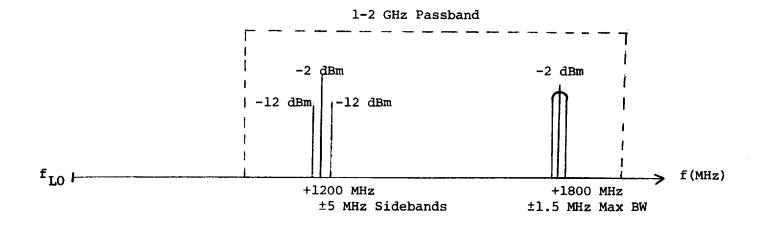

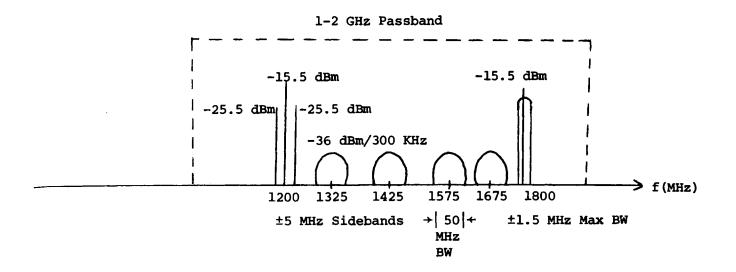

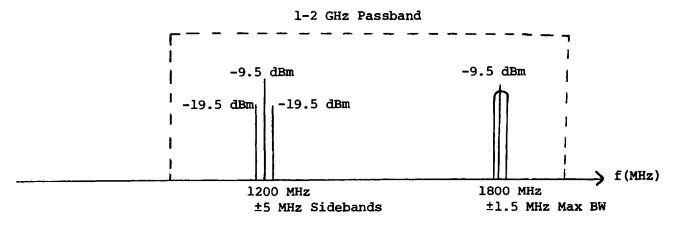

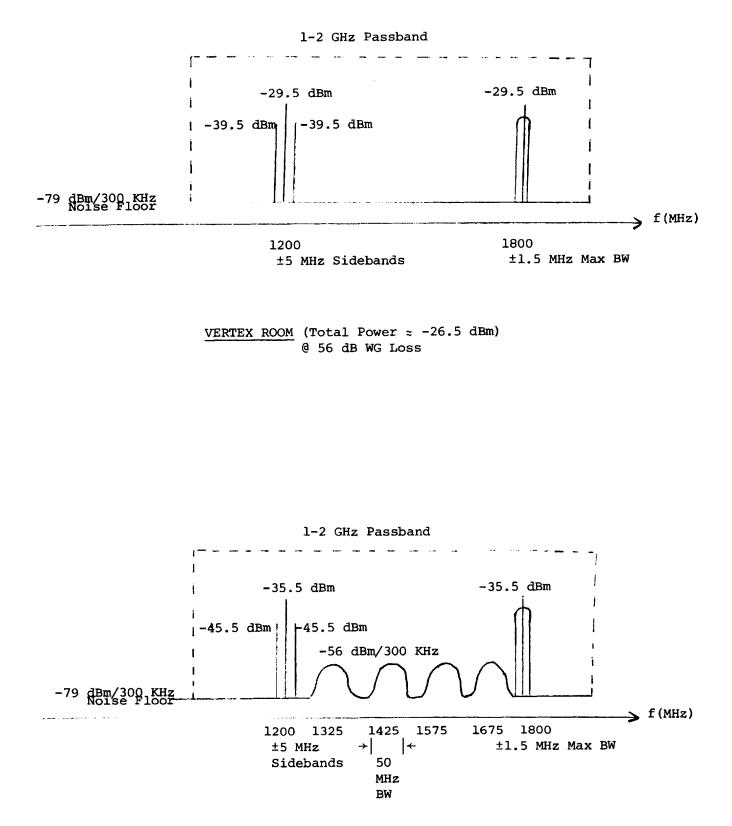

Refer to Figure 3-1 for modem system levels. Note that even though the front end "IF" signals are not transmitted by the control room modem, the total power output in full transmit is the same as that from the vertex room modem, +1 dBm. This is accomplished by an increase in the LO signal levels arriving at the T2 transmit input port. Thus full advantage is taken of the modem mixer's 1 dB compression point. Modem RF passbands at the waveguide, and 1-2 GHz Modem IF passbands at the transmit input port and receiver output port, are given in Figures 3-2, 3, and 4 respectively. Note that in the case of a 1-2 GHz spectrum, front end IF powers are given in a 300 KHz bandwidth to be convenient for use with a spectrum analyzer. In the case of a waveguide passband, front end IF powers are given in a 50 MHz total individual IF bandwidth, for ease of use with a power meter.

Worst case passband amplitude variations are given in Figure 3-5, and a noise figure budget is given in Figure 3-6. The noise figure budget does not include effects of intermodulation on the 50 MHz noise passbands. Third order intermod on all four IF signals will produce in band products which will raise the level of the noise floor.

FIGURE 3-1: System levels and pads. All power levels in dBm and apply to carrier if no parenthesis, total LO carriers if in parenthesis, and total IF and LO power if in brackets. All signal levels are when the signal is ON; they are not average levels.

CONTROL ROOM (Total Power z +1 dBm)

FIGURE 3-2: T1 RF TRANSMIT PASSBAND AT WAVEGUIDE (Discounting Passband Ripple)

VERTEX ROOM (Total Power = -6.5 dBm)

CONTROL ROOM (Total Power z -6.5 dBm)

FIGURE 3-3: T1 IF TRANSMIT PASSBAND AT J16 INPUT (Discounting Passband Ripple)

CONTROL ROOM (Total Power  $\approx$  -26.5 dBm) @ 56 dB WG Loss

FIGURE 3-4: T1 IF RECEIVE PASSBAND AT J15 OUTPUT (Discounting Intermodulation and Passband Ripple)

| Tl Passband Amplitude Variation in Receive |          |                   |   |  |

|--------------------------------------------|----------|-------------------|---|--|

| Component                                  | Worst Ca | ase Variation Spe | C |  |

| Latching Circulato                         | r        | ±0.3 dB           |   |  |

| Mixer/Filter                               |          | ±0.5              |   |  |

| SPDT Switch                                |          | ±0.4              |   |  |

| Receive Amplifier                          |          | <u>±0.5</u>       |   |  |

|                                            | Total    | ±1.7 dB *         |   |  |

| Tl Passband Amplitude Variation in Transmit |          |                    |  |  |

|---------------------------------------------|----------|--------------------|--|--|

| Component                                   | Worst Ca | ase Variation Spec |  |  |

| SPST Switch                                 |          | ±0.3 dB            |  |  |

| Fixed Attenuator                            |          | ±0.4               |  |  |

| Transmit Amplifier                          |          | ±0.5               |  |  |

| SPDT Switch                                 |          | ±0.4               |  |  |

| Mixer/Filter                                |          | ±0.5               |  |  |

| Latching Circulato                          | r        | <u>±0.2</u>        |  |  |

|                                             | Total    | ±2.3 dB *          |  |  |

\*NOTE: Total worst case passband variations do not include variations due to connections or reflection coefficients of individual components.

#### COMPONENT

```

Waveguide Extension<-.5 dB Loss</th>Latching Circulator<-.6 dB Loss</td>Mixer/Filter<11.8 dB N.F. with <4.0 dB IF N.F.</td>SPDT Switch<-.8 dB Loss</td>Receive Amplifier<3 dB N.F.</td>... IF noise figure = 3.8 dB maximum which

```

- is less than 4.0 dB.

- . Total noise figure = noise figure of mixer/filter plus losses.

- ... Total noise figure <12.1 dB

# SIGNAL/NOISE CALCULATIONS

| IF                                    | Transmit Level/IF = -6 dBm/50 MHz                              |  |

|---------------------------------------|----------------------------------------------------------------|--|

|                                       | Waveguide Loss = 56 dB Maximum                                 |  |

|                                       | $\therefore$ Received signal = -62 dBm/50 MHz                  |  |

|                                       | Noise power in 50 MHz = KTB = $-97 \text{ dBm}/50 \text{ MHz}$ |  |

|                                       | Noise figure = 12 dB                                           |  |

|                                       | . Total noise power = NKTB = -85 dBm/50MHz                     |  |

|                                       | . Signal/noise ratio = 23 dB less any intermodulation          |  |

| LO Transmit Level/LO Carrier = -8 dBm |                                                                |  |

|                                       | Waveguide Loss = 56 dB Maximum                                 |  |

| (Control                              | . Received signal = -64 dBm/Carrier                            |  |

| Room                                  | Noise power in 300 KHz = KTB = $-119$ dBm                      |  |

| Receive)                              | Noise figure = 12 dB                                           |  |

|                                       | . Total noise power = NKTB = -107 dBm/300 KHz                  |  |

|                                       | . Signal/Noise ratio = 43 dB/300 KHz less any intermodulation  |  |

| LO                                    | Transmit Level/LO Carrier = -2 dBm                             |  |

| (Vertex                               | . Signal/noise ratio = 49 dB/300 KHz less any intermodulation  |  |

| Room                                  |                                                                |  |

| Receive)                              |                                                                |  |

#### A. VOLTAGE REGULATOR

Refer to the voltage regulator schematic of Figure 4-1.

An input voltage of +15 VDC is applied to the regulator through the front panel "Gunn supply" crowbar fuse. To prevent the crowbar circuit from firing when power is first applied, resistor R19 and capacitor C4 slow the input power-on transient with a time constant of 75  $\mu$ s.

The crowbar circuit uses a 723 precision voltage regulator chip, Ul to perform a voltage comparison function between the regulator output voltage, sampled through R6, and the voltage set pot, R10. If the output voltage should happen to rise 17% above the normal regulated voltage value, then the comparator output at  $V_Z$  will go high and provide gate current to silicon controlled rectifier, CR1. CR1 will then conduct, shorting the input of the regulator and blowing the front panel "Gunn supply" fuse, thus preventing damage to the Gunn oscillator.

The  $V_Z$  output (series zener diode from the output of the 723 comparator) is used to insure that no SCR gate current flows when the comparator output is low. Resistor  $R_1$  is used to limit the current flowing into the SCR gate when the comparator goes high.

Diode CR2 and R7 in the positive feedback loop of the 723's fast comparator latches the comparator into the switched high state, insuring that the SCR will fire even on very short transients.

Voltage regulation is provided by another 723 regulator chip, U2, in conjunction with a series pass transistor Q1, adequately heat sunk to the module left side plate. Connections to the series pass transistor as well as all other voltage regulator board connections are made through a 14 pin IC socket - platform assembly. One might question the use of such a socket at the high current levels of the pass transistor. However, a test run with a +15 VDC supply, current limited to 1 amp, through a single pin resulted in a contact resistance degradation from 4.2 milliohms to only 5.0 milliohms with 500 power-on insertions.

The reference voltage for the voltage regulator is derived from its own internal zener reference. At approximately 7.15 VDC the voltage set potentiometer provides a range of 4.0 to 7.15 VDC

to the crowbar circuit and a range of + 3.4 to + 6.1 VDC to the reference input of the voltage regulator comparator.

This 17% tracking of voltages is performed by providing a voltage divider with R2 and R3 to reduce the voltage regulator reference by 17% relative to the crowbar reference. This is important to protection of the Gunn oscillator since required unit to unit supply voltages vary over a wide range depending on the Gunn waveguide channel in use.

<u>Caution</u>: Because of this wide range of Gunn supply voltages, leave the Gunn oscillator power supply lead unsoldered until the voltage set pot has been adjusted for the particular Gunn in use. Similarly, disconnect the Gunn supply wire from the Gunn before changing voltage regulator boards, and reapply power to the Gunn oscillator only after this adjustment has been made.

The current limit function is also handled by the voltage regulator chip, U2, in conjunction with resistors R15 through R18, R23 and R24. R15 through R18 form a 0.25  $\Omega$  1 watt resistor to provide a voltage =  $\frac{1}{4}$  x output current. This voltage is supplied to the crowbar current sense transistor's base to emitter junction by resistive divider R23 and R24. When this voltage rises to V<sub>BESAT</sub> (z.7VDC) the current will be held to a constant level. With the resistor values shown on the schematic, this will occur at z 2.5 amperes which is greater than the maximum turn-on current required for the Gunn oscillator.

The voltage across R15 through R18 is also used as a DCS monitoring point for Gunn current. Unity gain buffer amplifiers U3A and U3B with isolating resistors R12, R14, R20, and R21 provide a differential output corresponding to .25 volts/amp to the T2 interface logic board. Thence, another buffer amp with a gain of 4 normalizes the Gunn current monitor voltage to 1 volt/amp single ended before transmission to the DCS analog mux system. The T2 buffer amp utilizes resistors R20 and R21 on the T1 voltage regulator board to provide the proper gain ratio.

Buffer amplifier U3A also provides a Gunn voltage monitor point through R22 to the T2 interface board.

The voltage output of the regulator is shunted by a 180  $\mu$ Fd 6VDC tantalum capacitor to prevent the output from overshooting the normal operating voltage when the load is instantaneously removed. This overshoot is due to the slow response time of the voltage regulator.

One output of the regulator is connected directly to the Gunn oscillator supply input. However, another output is applied to the phase locked loop Gunn supply varactor voltage clamp to prevent the varactor voltage (referenced to the Gunn supply voltage in the Gunn oscillator) from biasing the varactor into conduction and possibly destroying it. A fixed voltage in the phase locked loop box can not be used for the clamp voltage because of the wide range of Gunn supply voltages used.

#### B. SYNCHRONOUS DEBOUNCE CIRCUIT

Refer to the Synchronous Debounce Schematic of Figure 4-2.

The purpose of the synchronous debounce circuit is to interface the Xmit/Auto/RCV switch to the T/R line for both Tl and T2 in such a manner as to switch states synchronously with the normal T/R clock pulses. Thus the minimum width of the T/R pulses to the latching circulator is maintained in spite of the asynchronous timing of manually throwing the Xmit/Auto/RCV switch. Also any noise or bounce from the switch is removed.

This action is necessary from the standpoint of the latching circulator which is an edge triggered device and could easily end up in a random state in the manual mode if the Xmit/Auto/RCV switch were connected directly to the T/R input.

A dual three position on-on-on toggle switch is used for the front panel Xmit/Auto/RCV function. One half of the switch is wired to indicate whether the switch is in a manual state. When the switch is in either manual Xmit or RCV, the "auto warn" LED lights, indicating an abnormal condition. This auto warn signal from the LED also triggers a set-reset flip flop in the T2 module sending a high TTL "auto warn" signal to the DCS analog multiplex monitor system. Thus any tampering of either of the two modem T1 switches can be indicated to the telescope operator.

The other half of the Xmit/Auto/RCV switch interfaces to the synchronous debounce circuit. An on-on-on toggle switch can be wired as a single pole - three position switch. However, because some of the states overlap as the switch is changed in position, it is difficult to debounce. Therefore, the three states of the toggle switch shown on the top of Figure 4-2 are decoded first into three "break before make" outputs by nor gates U2a, U2b and U2d. These

# FIGURE 4-2

gates are used as "and" gates.

In order to debounce the switch, two flipflop storage elements are required. Ula and Ulb are used as a set-reset flip-flop to debounce the  $(X.M.T) \leftrightarrow (RCV)$  information. And U4a is also wired as a set-reset flip-flop to debounce the  $(XMT \text{ or } RCV) \leftrightarrow (Auto)$  information. The "or" function in the latter case is performed by "nor" gate, U2c.

Now that the switch is debounced the interruption of the T/R pulse train can be made synchronous with the pulse train by use of D-type flip-flop U4b and a "and-or" select gate consisting of U3b, U3c and U3d. The and-or select gate is used to select either the T/R input pulse train or the switch XMT-RCV information to the T/R output line. The selection of either input is made synchronous with the T/R pulses by applying the T/R pulse train to the clock input on D-type flip-flop, U4b.

The T/R input (from a line driver in L8) is terminated in 50  $\Omega$  on the synchronous debounce card by R6 to prevent glitches caused by pulse reflection at the T/R input.

An inverted T/R output is provided by Ulc for easier interfacing to the rest of the Tl sub-assemblies.

# C. PIN DIODE DRIVER

Refer to the pin diode driver schematic of Figure 4-3.

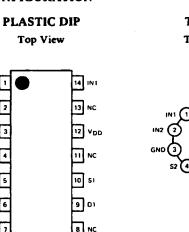

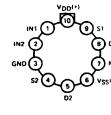

The purpose of the pin diode driver board is to interface the TTL transmit/receive signal from the synchronous debounce board to both pin diode RF switches in the modem Tl module. The pin diode switches require a  $\pm$  50 mA at 1 volt constant current source in conduction as well as in cut-off, depending on the polarity of the individual switch. Therefore the pin diode driver actually consists of two independent drivers of opposite polarity relative to the incoming T/R signal.

An AD518 high slew rate operational amplifier is used as a comparator to convert the TTL input signal to a voltage swing to approximately each 15 VDC supply rail. The reference input of the comparator is biased to a voltage (1.4 VDC) near the median voltage of worst case TTL input levels (.8 VDC maximum low and 2.0 VDC minimum high). R4 and R9 are used to stabilize the comparator.

Because of the high current requirements (50 mA) of the pin diode switches, the outputs of the comparators are buffered by complimentary symmetry amplifiers Q1, Q3 and Q2, Q4. Resistors R5, R6, R10 and R11

FIGURE 4-3

limit the output current to the pin diode switches to 50 mA.

The emitter follower complimentary amplifier was chosen for its stability. The output voltage swing of this system is adequate at the RF power levels used in the pin diode switches.

# D. PHASE LOCKED LOOP

Refer to the schematic of Figure 4-4 and block diagram of Figure 4-5.

# 1. IF VIDEO AMPLIFIER

The signal from the harmonic mixer at  $\geq$ -50 dBm must be amplified to a level compatible with that of the digital phase detector. A video amplifier is required to prevent erroneous lock points on subharmonics of the 10 MHz reference signal.

The beat note produced by the nth harmonic of 2400 MHz mixing with the Gunn diode output in the harmonic mixer is not a pure sinusoid. Because the harmonic mixer diode is not a perfectly square law device harmonics of the beat note will also appear in the output. If the beat note happens to be at a subharmonic of the 10 MHz reference frequency (say 5 MHz, for example) then a component at 10 MHz will exist at the input of the IF amplifier. If a narrow band filter at the 10 MHz reference frequency were placed at the input of the IF amplifier, then a 10 MHz signal would appear at the output and the phase detector could treat it as a proper 10 MHz signal and the loop could lock onto it, even though the beat note occurred at 5 MHz.

In order to prevent this ambiguity from occurring, one would think that the IF amplifier low frequency cutoff must occur at less than one half the reference frequency. This would permit at least some component of all possible subharmonics ( $f_{ref} \div 2, \div 3, \div 4, etc.$ ) to be passed on to the phase-frequency detector. A low frequency component would then offset the output of the detector and prevent any erroneous lock point.

However, the low frequency cutoff given above assumes that the harmonics of the beat note gradually decrease in amplitude with frequency. This is usually not true, and certainly would be difficult to control. Since many low order harmonics of the beat note may be lacking in amplitude, a video amplifier with a very low frequency cutoff is required.

FIGURE 4-4

FIGURE 4-5: PHASE LOCK UNIT BLOCK DIAGRAM

In the actual video amplifier used, a coupling capacitance of .1  $\mu$ Fd and a load resistance of 51  $\Omega$  leads to a low frequency -3 dB point of z 30 KHz. This is given by,

$$f_{-3dB} = \frac{1}{2\pi RC}$$

Therefore, the probability of false locking on a subharmonic is negligible.

Another requirement placed on the IF amplifier is that the output waveform be of constant amplitude over the input signal dynamic range to interface properly to the phase detector. Either a limiting amplifier or an AGC controlled amplifier is required.

A limiting amplifier was chosen in this application because of the dependence on waveform duty cycle of the lock indicator, which is not an edge-triggered device like the phase detector. A differential amplifier chip such as the CA3012 (U1) can provide symmetrical limiting because the transistors never swing into saturation. And with symmetrical limiting the output duty cycle will remain at 50% over a wide dynamic range on the input.

Because the limiting action will provide harmonics of the harmonic mixer beat note, the output of the limiting amplifier must also have a video passband response as explained earlier.

The video amplifier ideally should have a high frequency -3 dB point of twice the reference frequency. If the noise power is assymetric with the reference frequency, the edge-triggered phase-frequency detector will interpret the noise power as a frequency error and lock will be more difficult to acquire under weak signal conditions.

The CA3012 has a high frequency -3 dB point of about 8 MHz with a 1000  $\Omega$  load resistance, much too low for optimum performance. However, the signal to noise ratio at the input to the IF amplifier is high enough to permit satisfactory operation. A single CA3012 also does not have enough gain to limit on its own input noise power, a requirement for an optimum phase locked loop threshold. But again, the signal level presented to the input of the IF amplifier is adequate for this application.

An extra unity voltage gain 2N5179 power amplifier stage, Q1, was added to the output of the CA3012 to permit driving a

75  $\Omega$  load composed of the IF monitor isolation resistors, R17 and R18, and the IF comparator bias resistors, R23 and R24. The voltage gain of unity is obtained by the ratio of the collector load resistance to the emitter resistance. A common emitter amplifier with emitter degeneration was chosen instead of an emitter follower to maintain an output waveform duty cycle of 50%. The 2N5179 collector voltage is obtained from the +5 volt supply to minimize power dissipation. However, this places a restriction on peak to peak output voltage swing of about 1 VPP for maintenance of the duty cycle.

# 2. COMPARATOR/LEVEL SHIFTERS

Two identical comparator circuits consisting of Q4, Q5 and Q2, Q3, interface the IF video amp and 10 MHz reference input AC signals of 1 VPP to the TTL inputs of the lock indicator "nand" gate. The comparators are high gain wide bandwidth differential amplifier pairs which produce  $\approx$  0 to 2.5 VDC output swing TTL signals. These output signals are interfaced to the ECL inputs (1 VPP @ 3.75 VDC) of the phase/frequency detector by level shifting networks consisting of R49, R22, C13 and R21, R19, C14.

An offset voltage of approximately .1 VDC is introduced on the inputs of each comparator by bias resistors R28 and R47. This bias voltage insures that the comparator outputs are low in absence of input signals. Thus the lock indicator gate is forced to indicate an out of lock condition in case of absence of signal in the IF amplifier or at the 10 MHz reference source. The duty cycle of the input signals will be modified slightly by this offset.

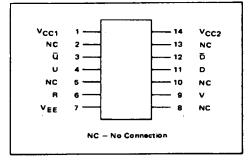

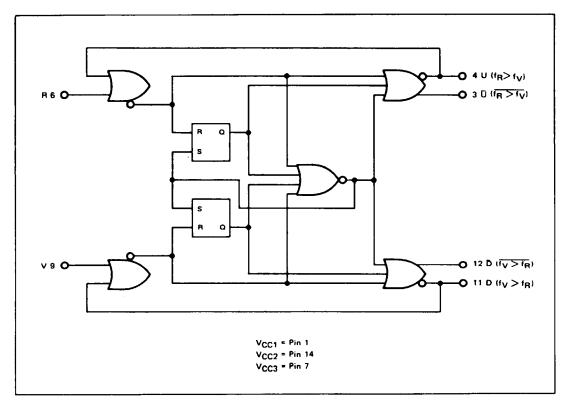

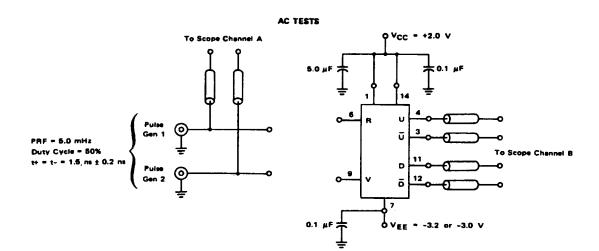

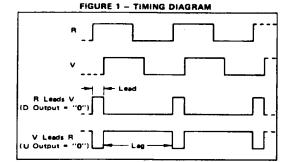

#### 3. PHASE DETECTOR

The Motorola MC12040 modulo  $4\pi$  ECL phase/frequency detector was chosen because of its ability in a swept phase locked loop to permit lock at only one IF sideband, as well as being immune to locking to IF frequencies that are harmonics or subharmonics of the reference frequency. This eliminates the additional circuitry needed to require a unique lock point for the Gunn oscillator when a quadrature phase detector is used. The effect of the phase-frequency detector on the Gunn frequency in the harmonic mixing scheme actually used in the modem phase locked loop is diagrammed in Figure 4-6.

- $\frac{\text{WHERE}}{\text{REF}} \qquad \begin{array}{c} \text{f} \\ \text{REF} \end{array} \Rightarrow 10 \text{ MHz Reference Frequency} \\ \text{to Phase Detector} \end{array}$

- Nf<sub>LO</sub> ⇒ nth Harmonic of 2400 MHz Local Oscillator Frequency at Harmonic Mixer

- Gunn Frequency ⇒ Output Frequency of Gunn Oscillator at Harmonic Mixer

- Region ⇒ One of 8 Unique Initial Conditions That the Gunn Oscillator Frequency Can Occupy Relative to the nth Harmonic of the 2400 MHz Local Oscillator Frequency

- Lock Point⇒ Frequency at Which the Gunn Oscillator Will Phase Lock to the nth Harmonic of the 2400 MHz LO Frequency Plus or Minus the 10 MHz Reference Frequency, Depending on the Position of the Sideband Select Switch. In This Example, an Upper Sideband, (Odd Channel), Has Been Selected

# Instability

Point ⇒ Frequency at Which the Gunn Frequency Will Remain in an Unstable Condition, If The Gunn Frequency Previously Occupied Either Region 1 or 2

FIGURE 4-6: Page 2

The horizontal arrows show the directions in which the Gunn oscillator's frequency is forced, for given initial conditions. This action may be readily derived from the IF passband response (what is actually presented to the detector) for the mixing scheme used. The passband response is critical to this analysis, since an out of band signal (no signal present) will appear to the phase detector as an IF signal that is lower in frequency than the reference signal. Therefore the phase detector will force the Gunn oscillator higher in frequency, resulting in the response of the top diagram.

Note that an instability point occurs at the edge of the lower sideband passband response in the top diagram. Because of this instability and the directions of Gunn oscillator frequency pull for the various initial conditions, a sweep system in which the Gunn oscillator is forced to be pulled into regions 3, 4 or 5 (the only initial conditions in which a stable lock point can occur) is required. Since the bandwidth of operation of the IF amplifier and phase detector is less than the worst case frequency drift of the Gunn oscillator, the sweep system described later operates over the full tuning range of the Gunn oscillator.

The gain of the MCl2040 phase detector is approximately .16 volts/radian.

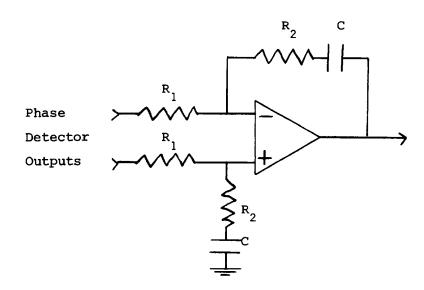

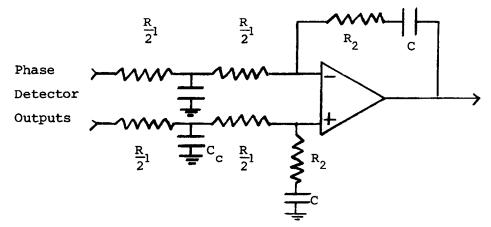

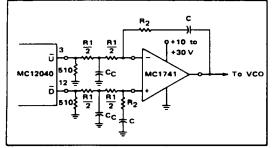

4. INTEGRATOR

For a discussion of phase locked loops, refer to <u>Phase Lock</u> <u>Techniques</u> by F.M. Gardner (John Wiley and Sons, Inc., New York, 1966).

A second order high gain integrator was chosen for the loop filter to insure a  $0^0$  phase difference between the 10 MHz IF and reference frequencies at lock. Thus a simple lock indicator can be designed using this principle to control the sweep logic.

Because a forced sweep is required for this system the loop parameters were chosen for best lock acquisition rather than low noise.

Measurements on a number of Gunn oscillators indicated an average varactor gain of 27.3 MHz/volt at the operating frequency.

:

$$K_0 = (27.3 \text{ MHz/volt}) \cdot (2\pi \text{ radians/Hz}) = 172 \times 10^6 \text{ radians/volt}$$

where  $K_0 =$  the VCO gain constant for the MC12040.

$K_d = .16 \text{ volt/radian where } K_d =$  the phase detector gain constant.

For best lock acquisition it is desirable to have as large a loop natural frequency ( $\omega_n$ ) as possible. However, practical considerations of loop stability permit a nominal loop bandwidth of 40 KHz.

$\therefore \omega_n = (40 \text{ KHz}) \cdot (2\pi \text{ radians/sec} \cdot \text{Hz})$  $\omega_n = 2.51 \times 10^3 \text{ radians/sec}$

Also for best lock acquisition a damping factor ( $\zeta$ ) of 2 was chosen. (Gardner, p. 48)

A differential integrator of the form shown below is required for compatibility with the phase detector.

Where  $\tau_1 = R_1C$  and  $\tau_2 = R_2C$  from eqn (2-10) (Gardner, p. 9),

$$\omega_{n} = \left(\frac{K K}{\sigma d}\right)^{\frac{1}{2}}$$

$$\zeta = \frac{\tau_{2}}{2} \left(\frac{K K}{\sigma d}\right)^{\frac{1}{2}}$$

or,

$$\tau_{1} = \frac{\kappa_{0}\kappa_{d}}{\omega_{n}^{2}} = 4.35 \times 10^{-4} \text{ sec}$$

$$\tau_{2} = \frac{2\zeta}{\omega_{n}} = 1.59 \times 10^{-5} \text{ sec}$$

Let C = .033 x  $10^{-6} \mu Fd$   $\therefore R_1 = 13.2 K\Omega$  $R_2 = 482 \Omega$

Because the very narrow correction pulses of the MCl2040 phase detector may not be integrated by the amplifier, an RC filter is imbedded in the integrator input resistor network as shown below.

The time constant of this network as recommended by the Motorola MC4044 (similar to the MC12040) data sheet (p.9) should be given as below.

$$\omega_c \approx 5 \omega_{nmax}$$

Where  $\omega_{nmax}$  = the maximum loop natural frequency encountered over the varactor control voltage range.

Measurements on a number of Gunn oscillators indicated a maximum varactor gain of  $\omega_{nmax} = 4.8 \times 10^5$  radians/sec. Therefore  $\omega_c = 24 \times 10^5$  radians/sec. From the Motorola MC4044 data sheet (p. 9),

$$\omega_{c} = \frac{4}{R_{1}C_{c}}$$

$$C_{c} = \frac{4}{R_{1}\omega c}$$

$$\therefore C_{c} = 126 \text{ pF}$$

Therefore, in choosing practical component values,

$\frac{R_1}{2} \approx 6.8 \text{ k}\Omega$   $R_2 \approx 470 \Omega$   $C \approx .033 \mu\text{Fd}$   $C_2 \approx 120 \text{ pF}$

These values are shown on the schematic of Figure 4-4. 5. SWEEP CIRCUIT

A sweep oscillator consisting of an op amp comparator circuit (U5b), and timing capacitor (C42 in conjunction with C43) is used to provide both a ramp voltage for addition to the integrator output voltage, and a clock for the logic circuit timing.

The comparator functions as an astable oscillator by charging the timing capacitor to the comparator's switching point determined by resistors R50 and R52. When the capacitor's voltage reaches this point the comparator switches state and begins charging the capacitor in the opposite direction. Thus a ramp voltage is produced on the timing capacitor, and a clock signal can be derived from the comparator's output by utilizing a voltage clamp circuit (R57, D3, and D4) to interface to the TTL input of counter U9.

The ramp voltage from the timing capacitor is applied directly to the summing amplifier U6 through resistor R32. The ratio of this resistor value to the input resistor from the integrator output, R41, insures that the sweep will be able to swing the varactor voltage over its entire range independent of the integrator output voltage.

The ramp voltage can not be removed instantaneously from the summing amplifier input, when the loop achieves lock, since the magnitude of this change, depending on lock point, could produce enough of a frequency change to throw the loop out of lock.

However, it is also desirable to have the sweep input decay to zero after lock to take advantage of the entire varactor tuning voltage range. Therefore, the sweep is removed by opening the timing capacitor charging resistor, R51, with FET switch UlO. The timing capacitor then discharges slowly through R32 to zero since pin 2 of U6 is at virtual ground. Since this time constant, is 10 times longer than the normal sweep time constant, the loop

can follow the discharge.

One disadvantage to this sweep system is the additional noise voltage introduced into the loop by R32.

For any resistor,

$P_{n} = KTB$   $Where P_{n} = Noise Power$  K = Boltzmann's constant T = Temperature B = Bandwidth  $V_{n} = \sqrt{P_{n}} R$   $Where V_{n} = Noise voltage$  R = Resistance

Therefore, the resistor values on the summing amplifier should be minimized to the point where the input noise power of the amplifier dominates.

Unfortunately the sweep system requires a larger resistance to maintain the sweep time constant, since the summing amplifier input resistance is always placed across the timing capacitor, and limits its voltage swing. Therefore, the schematic component values represent a compromise between these two requirements.

Since individual Gunn oscillators vary considerably in varactor gain constants, the gain of the summing amplifier can be varied by selecting the value of the feedback resistor R48 for stable operation. The overcompensation network of R62 and C44 insure op amp stability over a wide range of gain values. 6. VARACTOR CLAMP AND FREE RUN BIAS SET

The Gunn oscillators are built with the varactor diode referenced to the positive Gunn supply voltage. In order to take advantage of the full tuning range available, the varactor voltage must be permitted to swing from the positive Gunn supply voltage to the negative 15 volt supply rail of the integrator.

Since the Gunn supply voltage varies over a 3 to 6 VDC range and the varactor must not be forced into hard conduction, a diode voltage clamp consisting of D7 and R7 prohibit the varactor voltage from exceeding the Gunn supply voltage.

A bias voltage near 0 VDC must be applied to the varactor

input when the loop is opened by FET switch UlO in the free run backup mode. This is accomplished by adding R8 to the varactor clamp circuit. In the free run mode,

+V<sub>Gunn</sub>

I =

$$\frac{V_{Gunn} + 15 - .7}{10K + 27K}$$

V<sub>VAR</sub> = -15 + I · 27K

$\therefore$  V<sub>VAR</sub> = .73 V<sub>Gunn</sub> - 4.6

$D7$

$\downarrow$  .7 VDC

$\downarrow$  V<sub>VAR</sub>

$V_{VAR}$

$V_{VAR}$  Where,

$V_{VAR}$  = Varactor Voltage in Free Run

$V_{Gunn}$  = Gunn Power Supply Voltage

## 7. LOCK INDICATION CIRCUIT

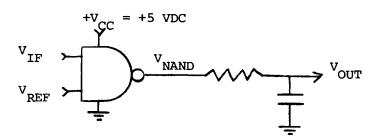

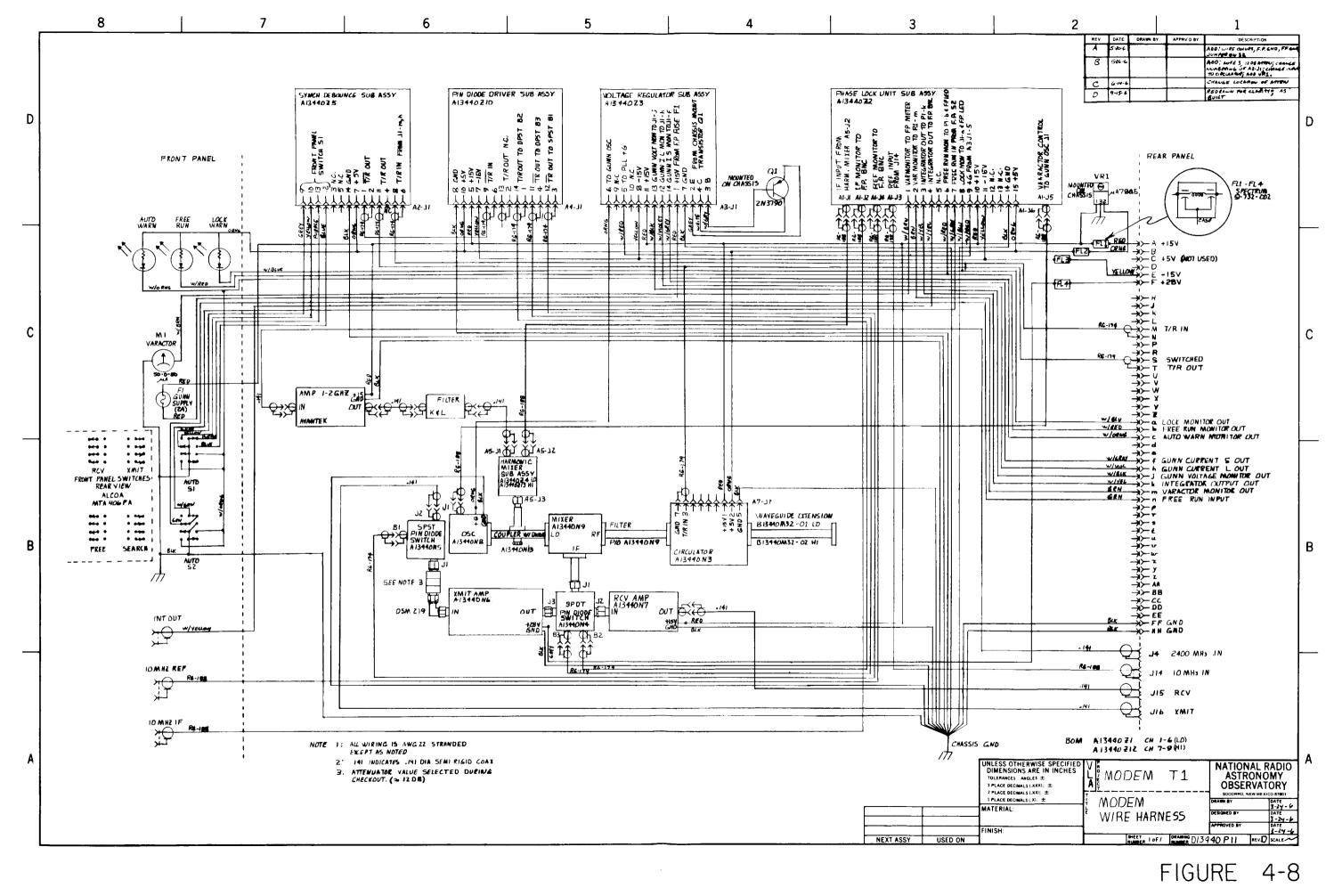

A simple lock indication circuit can be formed using a nand gate and comparator, when the phase difference between the IF and reference signals is zero.

|                 | TRUTH TA         | BLE               | $\therefore$ V <sub>OUT</sub> (out of lock) | $=\frac{3}{4}$ V <sub>CC</sub> |

|-----------------|------------------|-------------------|---------------------------------------------|--------------------------------|

| V <sub>IF</sub> | V <sub>REF</sub> | V <sub>NAND</sub> |                                             | = 3.75 VDC                     |

| 0               | 0                | 1                 | V <sub>OUT</sub> (in lock)                  | $=\frac{1}{2}$ V <sub>CC</sub> |

| 0               | 1                | 1                 | 001                                         | 2 00                           |

| 1               | 0                | 1                 |                                             | = 2.5 VDC                      |

| 1               | 1                | 0                 |                                             |                                |

|                 |                  | 1                 |                                             |                                |

In the actual circuit, however, the IF and reference comparators introduce an assymmetry in the input waveforms due to the comparator input offset voltage that is provided to pull each TTL nand gate input low in the absence of signal. (If either input is low, then the nand gate output is high, insuring an out of lock indication.) This assymmetry along with the limited output swing of the TTL nand gate change the actual circuit in-lock voltage to about 2.8 VDC and the out of lock voltage to about 3.7 VDC.

A schottky TTL nand gate, U7a, is used as the lock indicator. A 220  $\Omega$  pull up resistor (R36) is necessary on the output to minimize temperature drift of the output voltage swing, to maximize the output voltage swing, and to provide a low resistance to the RC low pass filter to produce equal decay and rise times.

The RC low pass filter of R37 and C46 accomplishes two functions. One is to average the output pulse waveform of the TTL gate to obtain a DC level which can be used as a lock indication. For this function the time constant would have to be long enough to filter out 10 MHz but short enough to indicate a locked condition before the sweep voltage pulled the loop out of lock.

However, the time constant must also be long enough to prevent the lock indicator from indicating a locked condition, when a low frequency beat note is produced between the signal and a harmonic or subharmonic of the reference frequency. This beat note will produce a waveform on the output of the nand gate, indicating a false lock with each low going pulse. Therefore, the -3 dB rolloff should be less than the free running short term drift of the Gunn oscillator. The components selected are a compromise between these three factors.

A comparator (U5a) is used to convert the lock indication voltage swing into a TTL level by comparison with a reference voltage provided by R53. This reference voltage should be set midway between the in-band out-of-lock voltage and the in-lock voltage,  $\approx$  3.25 VDC.

A voltage clamp circuit consisting of R38, D1, and D2 provide a TTL compatible output signal to the control logic system. LOGIC

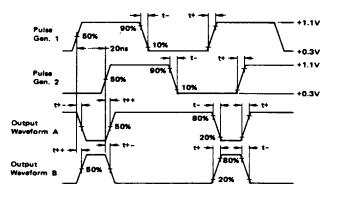

8. LOGI

Refer to the PLL control circuit timing diagram of Figure 4-7. When the loop drops out of lock for any reason, the logic circuit applies a charging current through R51 to the timing capacitor, thus starting the sweep oscillator. The sweep voltage from the timing capacitor is simultaneously applied to the summing amplifier input and the loop remains closed.

The sweep oscillator also applies a clock pulse to a ÷ 16

binary counter, U9. If the loop can not achieve lock in 8 counts of the sweep oscillator, the "search" period, then the loop is opened for another 8 counts, the "free-run" period. During the free-run period a bias voltage is applied to the Gunn oscillator varactor input which is equal to the normal operating voltage when the loop is closed. If each modem's Gunn oscillator is within 25 MHz of its normal operating frequency, then it is possible to exchange digital information with the remote antenna. If a free fun command is received once every 53 seconds at the T2 module, the loop will remain open, and further diagnostic checks may be made. If no command is received, the logic will continue to cycle between search and free-run states until lock is obtained.

A phase locked loop truth table on Figure 4-4 explains more completely this operation of the control logic. Note that the logic will immediately go into the search mode upon a change of the free run input to the search state (low). Thus if the T2 module is plugged into the rack, or if the free run/auto/search switch is brought to the search position, or if a search command is received, the logic will immediately go into the search mode. This convenience function is performed by resistor R56 and capacitor C24 which form an edge-triggered pulse generator at the input to U7b.

9. MONITOR BUFFERS

Both the integrator output and the varactor control line are buffered from the monitoring system by U4a and U4b to prevent external noise from appearing on these two noise sensitive monitoring points. Note that a ÷ 2 resistive divider is required on each op amp input to prevent latch-up when the monitor voltage approaches either supply rail.

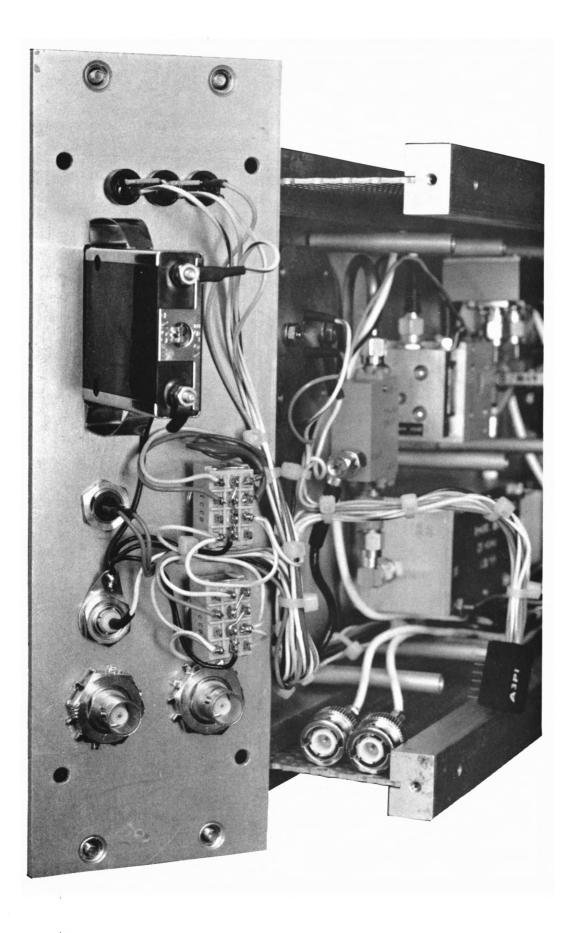

## E. MODEM WIRE HARNESS

The wire harness of Figure 4-8 shows the interconnections of the various subassemblies described previously. Note that all four incoming power supply lines are filtered and that the internal +5 VDC buss is generated by a voltage regulator on the +15 VDC incoming power supply line. This was necessary because of the wide voltage variations and noise on the rack +5 VDC buss.

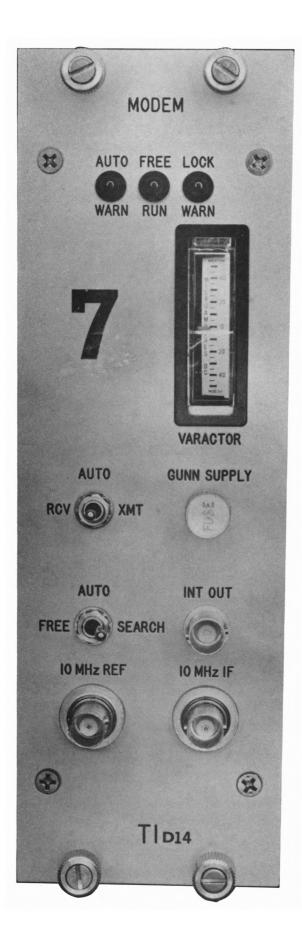

#### 5.0 FRONT PANEL INDICATORS AND CONTROLS

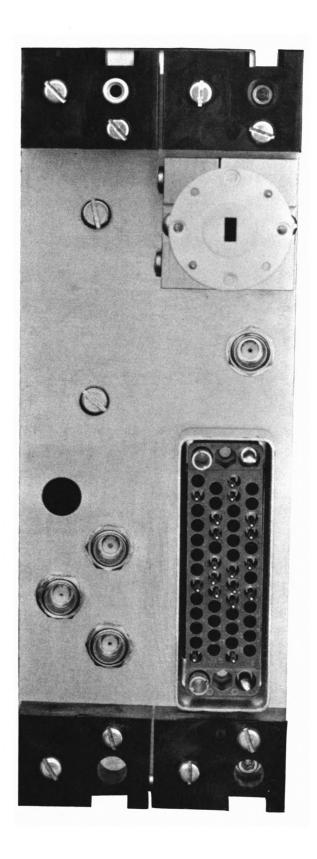

Refer to Figure 5-1.

## Auto Warn LED

Lights when either front panel switch is removed from the automatic position.

#### Free Run LED

Lights when either the phase locked loop cycles to the free run condition during a free run/search period, or when the free/auto search front panel switch is placed in the free-run position, or when a free-run command is received.

## Lock Warn LED

Lights when the Gunn oscillator phase locked loop has lost lock. Numeral

Indicates the waveguide channel number (1-11) of the particular modem. Only modems with the same channel number may be substituted. Varactor Meter

Indicates the voltage applied to the varactor input of the Gunn oscillator with a full scale reading of +15/0/-15 VDC. Under normal operation, or when the loop is in free-run, the meter should read approximately 0 VDC. If the loop is in search, and cannot find lock, the meter should sweep with a period of approximately 1<sup>1</sup>/<sub>2</sub> seconds between the Gunn supply voltage (+3 to +6 VDC) and approximately -15 VDC. RCV/Auto/XMT Switch

Permits the modem to be placed in full receive or transmit. Since this switch has priority over the transmit/receive timing from L8, it must be placed in the auto position for normal operation. Free/Auto/Search Switch

Permits the modem phase locked loop to be placed in free-run (loop open) or to be placed in search (loop closed) irrespective of the free-run command input from T2. If the modem has been in free-run and the switch is thrown to search, the phase locked loop should immediately start search/free-run cycles. Under normal conditions the loop should lock within one search period,  $\leq 1.5$  seconds. Since this switch has priority over the free-run command input from T2, it must be placed in the auto position for normal operation.

#### Gunn Supply Fuse

A 3 amp fuse supplying +15 VDC to the Gunn voltage regulator

board. This fuse will blow with the regulator over-voltage crowbar.

If the modem does not appear to transmit, nor receive, nor lock, check this fuse.

## INT OUT BNC Connection

Monitors the output of the phase locked loop integrator, before the summing amplifier and Gunn supply clamp, through a buffer amplifier with a voltage gain of  $\frac{1}{2}$ . If the loop is locked it should read \* 0 VDC. If the loop is unlocked it should read \* 7 VDC.

### 10 MHz REF BNC Connector

Monitors the external 10 MHz reference input to the phase locked loop board, and should be checked with a spectrum analyzer for power level (>-8 dBm) if the loop can not achieve lock.

#### 10 MHz IF BNC Connector

Monitors the IF passband at the output of the phase locked loop IF amplifier, and should be checked with a spectrum analyzer set for a high sweep rate of 5 MHz/div., if the loop can not achieve lock. This permits one to see the IF being swept in the search mode. In lock, this signal should read -8 dBm at 10 MHz.

#### 6.0 PRELIMINARY MODULE ADJUSTMENTS

- 1. Check power supply distribution wiring with ohmmeter. (Refer to drawing no. D13440P11.)

- With Gunn supply voltage wire and varactor coaxial cable disconnected from Gunn Oscillator, connect the test set to the module.

- 3. Apply proper power supply voltages to the test set.

- Set sideband select switch on the phase locked loop board to proper setting for modem channel in use. (Refer to drawing no. Cl3440S3.)

- 5. Set lock indicator reference voltage pot to 3.25 VDC at pin 2 of U5 on phase locked loop board. (Refer to drawing no. Cl3440P2.)

- Set the voltage set potentiometer (R10) on the voltage regulator board for the output voltage specified on the Gunn Oscillator case, using a digital voltmeter.

- 7. Disconnect module from test set and solder Gunn supply voltage wire onto the oscillator. <u>Caution</u>: Never connect this wire until the voltage has been set on the voltage regulator board for the particular Gunn Oscillator in use. Permanent damage can result if this voltage is too high.

- 8. Reconnect test set to the module, and throw free/auto/ search switch to search.

- Module should begin search/free-run cycles as indicated by the varactor meter sweeping for about 13 seconds and then resting near zero for approximately 13 seconds. The varactor meter should sweep from the Gunn supply voltage to about -14 VDC.

- b. Confirm that the voltage on the varactor output port,

J5, of the phase locked loop box does not swing above the Gunn supply voltage.

- c. The auto warn and lock warn LEDs should remain on.

- d. The free-run LED should light when the varactor meter rests near zero.

- 9. <u>Only</u> if the voltage on the varactor port has been confirmed to not swing above the Gunn supply voltage, connect the varactor coaxial cable to the varactor port, J5, on the

phase locked loop box.

- <u>Caution</u>: Never connect this cable until this has been checked out. Permanent damage can result to the oscillator if the varactor voltage rises above the Gunn supply voltage.

- 10. Apply reference signals to the Tl modules.

- a. 2400 MHz at -5 dBm to J4.

- b. 10 MHz at +10 dBm to J14.

- 11. Throw free/auto/search switch momentarily to free then back to search.

- a. Lock warn LED should extinguish within one complete sweep of the varactor meter.

- 12. Attach Spectrum Analyzer to 10 MHz IF port, and observe the wide band noise floor relative to the 10 MHz carrier with the video filter on.

- a. The signal to noise ratio should be a minimum of 50 dB in a 300 KHz analyzer bandwidth.

- b. Optimize the signal to noise ratio by varying the harmonic mixer backshort and by placing the harmonic mixer diode in each of the two possible directions in the harmonic mixer diode mount.

- c. In the case of a channel 7-10 modem also vary capacitor Cl in the harmonic mixer mount for best signal to noise ratio.

- d. Note that all of these adjustments interact.

- 13. Observe the close-in noise floor (<1 MHz from carrier) with an analyzer resolution of less than 10 KHz per division.

- a. If the noise floor peaks on each side of the carrier, change the varactor gain adjust resistor, R48, on the phase locked loop board until a flat frequency response is obtained.

- A. Connection of Tl and T2 to TEST SET

- 1. Proper power supply voltages must be connected to the TEST SET.

- 2. Reference signals, 2400 MHz and 10 MHz, must be connected to the T1.

- a) 2400 MHz at 5 dBm to J4.

- b) 10 MHz at +10 dBm to J14.

- 3. Place TEST SET switches in the following positions.

- a) ADDRESS SELECT switches up.

- b) Sl in LOCAL.

- c) S2 in CONTROL ROOM.

- d) S3 in AUTO.

- 4. Place both Tl switches in AUTO.

- a) All LED's on Tl should be out.

- 5. Momentarily close S9, RESET.

- a) All LED's on TEST SET should be out.

- B. Control Function Checkout

- Select "1" with ADDRESS SELECT switches (S4 down, free run command).

- 2. Momentarily close S8, STROBE.

- a) FREE RUN and LOCK WARN LED's on TEST SET and Tl should light.

- Select "0" with ADDRESS SELECT switches (all switches up, search command).

- 4. Momentarily close S8, STROBE.

- a) All LED's on Tl should go out.

- 5. Momentarily close S9, RESET.

- a) All LED's on the TEST SET should go out.

- Select "1" with ADDRESS SELECT switches (S4 down, free run command).

- 7. Momentarily close S8, STROBE.

- a) FREE RUN and LOCK WARN LED's on TEST SET and Tl should light.

- After approximately 53 seconds, FREE RUN and LOCK WARN LED's on T1 should go out.

- 9. Momentarily close S9, RESET.

- a) FREE RUN and LOCK WARN LED's on TEST SET should go out.

- 10. Place XMIT/RCV switch (S1) on Tl to either XMIT or RCV.

a) AUTO WARN LED's on TEST SET and Tl should come on.

- 11. Place XMIT/RCV switch on Tl to AUTO.

- a) AUTO WARN LED on Tl should go out.

- 12. Momentarily close S9, RESET.

- a) AUTO WARN LED on TEST SET should go out.

- C. Monitor Function Checkout

- Starting with test set SUB MUX ADDRESS SELECT switches at "0" (all switches up), select each address, "0" through "15", and compare TEST SET Meter, M1, reading with the following table.

| SUB MUX ADDRESS SELECT | TEST SET METER READING (100 = 10 VDC)         |

|------------------------|-----------------------------------------------|

| "0"                    | 0                                             |

| 1                      | <b>z+100</b>                                  |

| 2                      | <b>z+100</b>                                  |

| 3                      | 0                                             |

| 4                      | 0                                             |

| 5                      | ο                                             |

| 6                      | 0                                             |

| 7                      | z0 (should = 1.5 x Tl varactor meter reading) |

| 8                      | <b>20</b>                                     |

| 9                      | +30 to +60 (should = Tl Gunn Volt)            |

| 10                     | z+10 (should = T1 Gunn Current)               |

| 11                     | 0                                             |

| 12                     | 0                                             |

| 13                     | +40 (TTL High)                                |

| 14                     | +40 (TTL High)                                |

| 15                     | +40 (TTL High)                                |

|                        |                                               |

- Select "7" with ADDRESS SELECT switches (S7 down). Remove

MHz reference signal from J14, T1.

- a) TEST SET Meter, M1, should alternate from z + 25 to z 75.

- b) LOCK WARN LED's on TEST SET and Tl should light.

- c) After z 15 seconds, FREE RUN LED should light.

- 3. Reconnect 10 MHz reference signal to J14, T1.

- a) Momentarily throw FREE RUN/SEARCH switch to FREE RUN, then back to SEARCH.

- b) LOCK WARN LED on TI should go out within one complete sweep of the meter voltage.

- c) TEST SET Meter, M1, should read  $\approx$  0.

- 4. TI FREE RUN/SEARCH switch to AUTO, momentarily close S9, RESET.

- a) All LED's on TEST SET should go out.

- 5. Select "2" with ADDRESS SELECT switches (S5 down, monitor reset command).

- 6. Momentarily close S9, STROBE.

- Select addresses "13", "14" and "15" in turn. TEST SET Meter, M1, should indicate 2 0 (TTL Low) for these three steps.

- D. RF Calibration Procedure (T1)

- NOTE: This procedure can be accomplished in conjunction with the above or as a separate check using a Tl only.

- 1. TEST SET switches are set according to step A3.

- a) If T2 is not connected, S3 must be set to LOCKED.

- 2. Set up Test Oscillator for -6.5 dBm at 1.5 GHz and connect to J16 on rear panel.

- 3. Connect Waveguide Power Meter to waveguide.

- a) Power Meter should be set for +5 dBm full scale.

- 4. Set front panel switch, Sl, to XMIT.

- a) Power Meter should read +1 dBm. (This level can be adjusted as required by changing attenuator pad in transmit input line.)

- 5. Connect Spectrum Analyzer to J15 on rear panel.

- 6. Connect Noise Tube to waveguide.

- 7. Set front panel switch, S1, to RCV.

- 8. Two traces should be stored on the Spectrum Analyzer. One with Noise Tube off and one with Noise Tube on. The difference should be z 8 dB and should not vary over displayed spectrum.

| NOTE : | The Spectrum Analyzer | should | be set up as follows: |

|--------|-----------------------|--------|-----------------------|

|        | Center Freq           | =      | 1.5 GHz               |

|        | Bandwidth             | =      | 300 KHz               |

| Scan Width                    | =          | 100 MHz/Div.   |

|-------------------------------|------------|----------------|

| Input Atten                   | =          | 0 dB (.1 mw)   |

| Scan Time                     | =          | 2 sec.         |

| Log Ref Level                 | =          | -30 dB         |

| Lin Sensitivity               | -          | 0 dB           |

| Video Filter                  | =          | 100 Hz         |

| Scan Mode                     | =          | Single         |

| Switch                        | =          | 10 dB Log      |

| Scan Trigger                  | =          | Auto           |

| Storage                       | =          | Std.           |

| • • • • • • • • • • • • • • • | <b>a</b> 1 | - Crem Made Co |

Scan is produced by depressing Single Scan Mode Switch.

٠

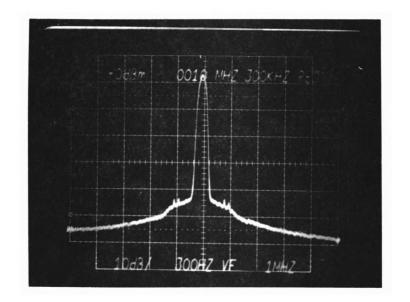

### 8.0 MODEM MEASUREMENTS

An example of the output signal at the 10 MHz IF port is given in Figure 8.1. Note the close-in noise floor ( $\leq$ 1 MHz from carrier) created by the summing amplifier in the phase-locked loop. Several small noise spikes from the transmit-receive pulses appear in this passband.

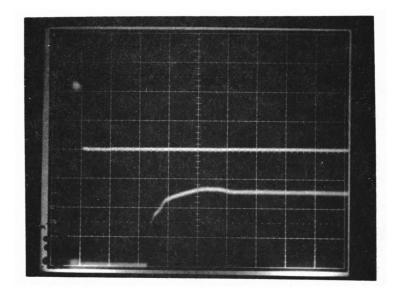

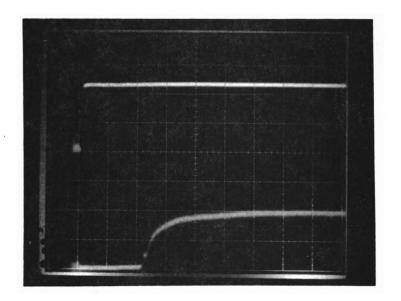

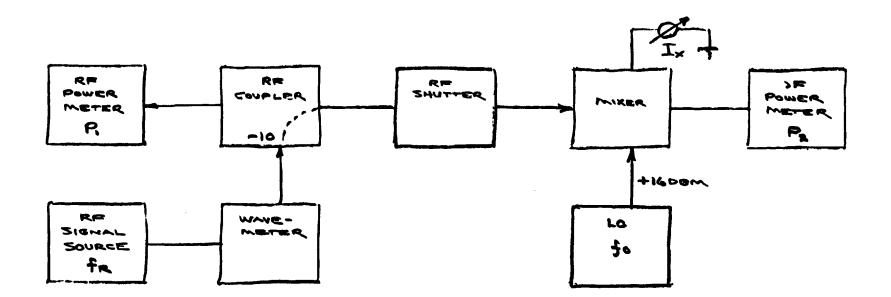

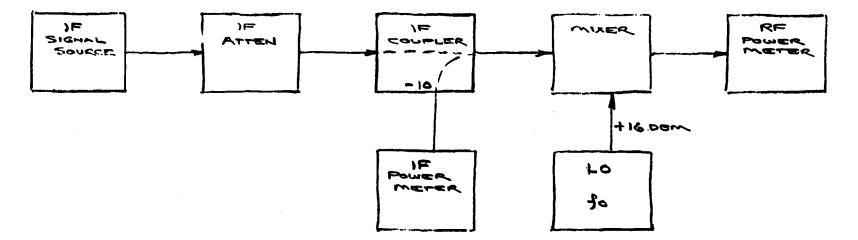

Transmit and receive switching times for T2-T1 combinations appear in Figures 8-2 and 8-3. Note that the transitions occur well within the maximum 100 µsec switching time specification, and yet do not bounce.

Complete RF amplitude and phase passband measurements for a system of IF combiners and modems are given in Figures 8-4 through 8-11.

- 0 dBm @ top line with 10 dB/Division

- 10 MHz center frequency with 1 MHz/Division

- 300 KHz bandwidth with 300 Hz video filter

- Module TlD10 in lock

FIGURE 8-1: SPECTRUM ANALYZER RESPONSE AT 10 MHz IF FRONT PANEL CONNECTOR

TOP TRACE - T/R Input Pulse (Vertical 2 Volts/Div) (Horizontal 0.5 µS/Div)

BOTTOM TRACE - Detected Transmit Output Level at Waveguide (Vertical 2mV/Div) (Horizontal 0.5 µS/Div) MODULES USED - T2B5 and T1D12 (phase locked)

FIGURE 8-2: IF COMBINER T2 - MODEM T1 TRANSMIT SWITCHING TIME

TOP TRACE - T/R Pulse (Vertical l Volt/Div) (Horizontal 0.5 µS/Div) BOTTOM TRACE - Detected Receive Output At T2-J8 (Vertical 50mV/Div) (Horizontal 0.5 µS/Div) MODULES USED - T1D14 (phase locked) and T2B5

FIGURE 8-3: MODEM T1-IF COMBINER T2 RECEIVE SWITCHING TIME

# T2B8 (XMIT)

FIGURE 8-8: PASSBAND RESPONSE

# T2B5 (XMIT)

FIGURE 8-11: PASSBAND RESPONSE

## 9.0 DIGITAL COMMUNICATIONS SYSTEM ADDRESS ASSIGNMENTS

Address assignments for the modem Tl - IF Combiner T2 system are given in Figures 9-1 and 9-2. Note that the monitor addresses are different for the vertex room and control room, and that the interface to the DCS system for both modules occurs in the T2 module.

## MODEM T1 - IF COMBINER T2 MONITOR POINTS

## VERTEX ROOM DATA SET NO. 2

| Octal Address | Monitor Point             | Voltage                              |

|---------------|---------------------------|--------------------------------------|

| 40            | Ground                    | 0 VDC                                |

| 41            | Temperature Monitor No. 1 | 0.1 VDC/°C, 0 VDC $\rightarrow$ 0°C* |

| 42            | Temperature Monitor No. 2 | 0.1 VDC/°C, 0 VDC $\rightarrow$ 0°C* |

| 43            | Ground                    | 0 VDC                                |

| 44            | Ground                    | 0 VDC                                |

| 45            | Transmit IF Power         | 5 VDC Nominal                        |

| 46            | Received IF Power         | 5 VDC                                |

| 47            | Varactor                  | ~0 VDC, 1 VDC ⇒ 2 VDC                |

| 50            | Integrator Output         | ~0 VDC, 1 VDC => 2 VDC               |

| 51            | Gunn Oscillator Voltage   | 3 to 6 VDC                           |

| 52            | Gunn Oscillator Current   | ~1 VDC, 1 VDC $\Rightarrow$ 1 Amp    |

| 53            | Ground                    | 0 VDC                                |

| 54            | Mixer Voltage             | 0 VDC                                |

| 55            | Auto Warn                 | ≈0 VDC TTL High ⇒ ON                 |

| 56            | Free Run Warn             | 20 VDC TTL High ⇒ ON                 |

| 57            | Lock Warn                 | ≈0 VDC TTL High ⇒ ON                 |

|               |                           |                                      |

\*when connected.

MODEM T1 - IF COMBINER T2 COMMANDS VERTEX ROOM DATA SET NO. 2

| Octal Address | Command       |

|---------------|---------------|

| 360           | Search        |

| 361           | Free Run      |

| 362           | Monitor Reset |

## MODEM T1 - IF COMBINER T2 MONITOR POINTS

CONTROL BUILDING DATA SET NO. 5

| Octal Address | Monitor Point             | Voltage                                     |

|---------------|---------------------------|---------------------------------------------|

| 120           | Ground                    | 0 VDC                                       |

| 121           | Temperature Monitor No. 1 | 0.1 VDC/°C, 0 VDC $\rightarrow$ 0°C*        |

| 122           | Temperature Monitor No. 2 | 1 VDC/°C, 0 VDC $\rightarrow$ 0°C*          |

| 123           | Ground                    | 0 VDC                                       |

| 124           | Ground                    | 0 VDC                                       |

| 125           | Transmit IF Power         | 5 VDC Nominal                               |

| 126           | Received IF Power         | 5 VDC                                       |

| 127           | Varactor                  | ~0 VDC, 1 VDC => 2 VDC                      |

| 130           | Integrator Output         | ~0 VDC, 1 VDC -> 2 VDC                      |

| 131           | Gunn Oscillator Voltage   | 3 to 6 VDC                                  |

| 132           | Gunn Oscillator Current   | ~1 VDC, 1 VDC $\Rightarrow$ 1 Amp           |

| 133           | Ground                    | 0 VDC                                       |

| 134           | Mixer Voltage             | 0 VDC                                       |

| 135           | Auto Warn                 | z.1 VDC, TTL High $\Rightarrow$ ON          |

| 136           | Free Run Warn             | $\approx$ .1 VDC, TTL High $\Rightarrow$ ON |

| 137           | Lock Warn                 | z.1 VDC, TTL High $\Rightarrow$ ON          |

\*when connected.

MODEM T1 - IF COMBINER T2 COMMANDS CONTROL BUILDING DATA SET NO. 5

| Octal Address | Command       |

|---------------|---------------|

| 360           | Search        |

| 361           | Free Run      |

| 362           | Monitor Reset |

| Title                                 | Number       |

|---------------------------------------|--------------|

| Schematic & Logic Diagrams            |              |

| Phase Lock Loop Unit Schematic        | C13440S3     |

| Voltage Regulator Schematic           | C13440S4     |

| Synchronous Debounce Schematic        | C13440S6     |

| Harmonic Mixer Schematic              | B13440S7     |

| Pin Diode Driver Schematic            | B13440S8     |

| Bill of Materials                     |              |

| Modem (Top B.O.M.), Ch 1-6            | A13440Z1     |

| Phase Lock Unit Subassembly           | A13440Z2     |

| Voltage Regulator Subassembly         | A13440Z3     |

| Harmonic Mixer Subassembly, Ch 1-6    | A13440Z4     |

| Synchronous Debounce Subassembly      | A13440Z5     |

| Pin Diode Driver Subassembly          | A13440Z10    |

| Modem (Top B.O.M.), Ch 7-10           | A13440Z12    |

| Harmonic Mixer Subassembly, Ch 7-10   | A13440Z13    |

| Assembly Drawings                     |              |

| Modem Top Assembly Drawing            | D13440P13    |

| Phase Lock Loop Assembly Drawing      | C13440P2     |

| Voltage Regulator Assembly Drawing    | B13440P4     |

| Harmonic Mixer Assembly Drawing       | C13440P7     |

| Synchronous Debounce Assembly Drawing | C13440P8     |

| Pin Diode Driver Subassembly          | B13440P10    |

| Modem Wire Harness                    | D13440P11    |

| Latching Circulator                   | C13440P16    |

| Single Pole Double Throw Pin Switch   | C13440P17    |

| Single Pole Single Throw Pin Switch   | C13440P18    |

| Transmit Amplifier                    | C13440P19    |

| Receive Amplifier                     | C13440P20    |

| Gunn Diode Oscillator                 | C13440P21    |

| 26.5-50 GHz Mixers, Ch 1-6            | C13440P22-01 |

| Ch 7-10                               | C13440P22-02 |

| Harmonic Mixer Mount                  | C13440P23    |

| Wire Lists                            |              |

| Rear Module Connector Wire List       | A13440W2     |

| Block Diagrams                        |              |

| Modem Block Diagram                   | C13440B1     |

|                                       |              |

| Printed Circuit Board Art Work       |              |

|--------------------------------------|--------------|

| Phase Lock Loop Unit                 | B13440AB2    |

| Voltage Regulator Board              | B13440AB3    |

| Harmonic Mixer PC Board              | B13440AD5    |

| Synchronous Debounce                 | B13440AB6    |

| Pin Diode Driver Board               | B13440AB7    |

| Printed Circuit Board Silk Screen    |              |

| Phase Lock Loop Unit                 | None         |

| Voltage Regulator Board              | None         |

| Harmonic Mixer PC Board              | None         |

| Synchronous Debounce                 | None         |

| Pin Diode Driver Board               | None         |

| Printed Circuit Board Drill Drawings |              |

| Phase Lock Loop Unit                 | C13440M21    |

| Voltage Regulator Board              | B13440M28    |

| Harmonic Mixer PC Board              | B13440M13    |

| Synchronous Debounce                 | B13440M12    |

| Pin Diode Driver Board               | B13440M29    |

| Mechanical Drawings                  |              |

| Phase Lock Unit Enclosure Plate      | C13440M36    |

| (Front and Rear)                     |              |

| Phase Lock Unit Enclosure Plate      | B13440M37    |

| (Left and Right Side)                |              |

| Mounting Plate for Power Transistor  | C13440M6     |

| Front Panel                          | C13440M2     |

| Rear Panel                           | C13440M4     |

| Left Side Plate, Ch 1-6              | B13440M5-01  |

| Ch 7-10                              | B13440M5-02  |

| Enclosure Cover, Top and Bottom      | B13440M10    |