VLA Technical Report No. 30

THE HANDYMAN'S GUIDE TO THE DATA SET, MODULE TYPE ML

D. W. Weber

September 1977

# TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                                                  |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------|--|--|--|--|--|

| 2.0 | GENERAL FUNCTIONAL DESCRIPTION                                                |  |  |  |  |  |

| 3.0 | DETAILED FUNCTIONAL DESCRIPTION                                               |  |  |  |  |  |

|     | 3.1 5 MHz Clock Detection and Doubling Logic $3-2$                            |  |  |  |  |  |

|     | 3.2 Input Signal Synchronization Logic                                        |  |  |  |  |  |

|     | 3.3 Message Detection/Loading Logic                                           |  |  |  |  |  |

|     | 3.4 Command Output Logic                                                      |  |  |  |  |  |

|     | 3.5 Word 1/Word 2 and Mux Load Sequence Logic 3-5                             |  |  |  |  |  |

|     | 3.6 Monitor Data Multiplex Address Formulation 3-6                            |  |  |  |  |  |

|     | 3.7 Analog Data Gathering Sequence                                            |  |  |  |  |  |

|     | 3.8 Output Data Sequencing Logic                                              |  |  |  |  |  |

| 4.0 | ANALOG SUBSYSTEM ALIGNMENT AND TESTS                                          |  |  |  |  |  |

|     | 4.1 Alignment Procedure for Revision C A/D Board 4-1                          |  |  |  |  |  |

|     | 4.2 DC Common Mode                                                            |  |  |  |  |  |

|     | 4.3 AC Common Mode                                                            |  |  |  |  |  |

|     | 4.4 A/D Adjustment and Test                                                   |  |  |  |  |  |

|     | 4.5 CMR Test                                                                  |  |  |  |  |  |

| 5.0 | DIAGNOSTIC/TROUBLESHOOTING OBSERVATION<br>POINTS AND DEPENDENCY RELATIONSHIPS |  |  |  |  |  |

| 6.0 | TYPICAL COMMAND/DATA CHANNEL LOGIC 6-1                                        |  |  |  |  |  |

| 7.0 | DATA SET DOCUMENTATION                                                        |  |  |  |  |  |

| 8.0 | I/O SIGNAL PIN ASSIGNMENTS                                                    |  |  |  |  |  |

| 9.0 | SPECIAL MODULE DATA SHEETS                                                    |  |  |  |  |  |

# TABLE OF TIMING DIAGRAMS

## SECTION

| 1.  | INPUT SIGNAL SYNCHRONIZATION TIMING                   |

|-----|-------------------------------------------------------|

| 2.  | MESSAGE DETECTION - LOADING TIMING                    |

| 3.  | COMMAND OUTPUT TIMING                                 |

| 4.  | MONITOR DATA MULTIPLEX ADDRESS CLOCK PHASE GENERATOR3 |

| 5.  | MONITOR DATA OUTPUT CLOCK GENERATOR                   |

| 6.  | MONITOR DATA OUTPUT CLOCKING, START OF DATA OUTPUT 3  |

| 7.  | MONITOR DATA OUTPUT TIMING, PARITY DATA OUTPUT        |

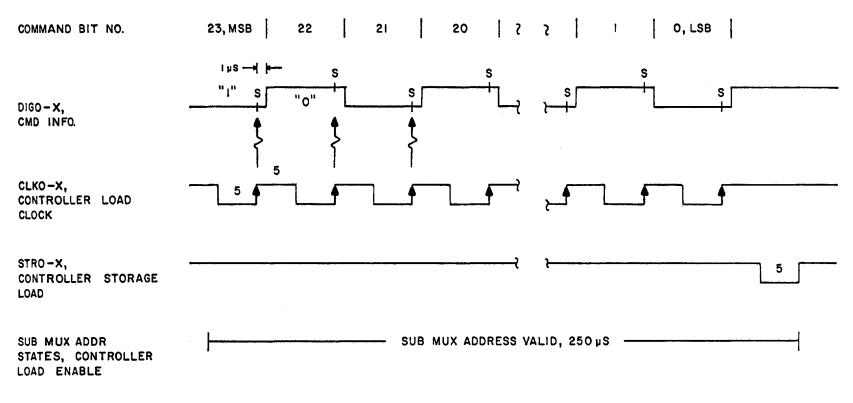

| 8.  | CONTROLLER COMMAND LOAD TIMING                        |

| 9.  | CONTROLLER BINARY MONITOR DATA UNLOAD TIMING          |

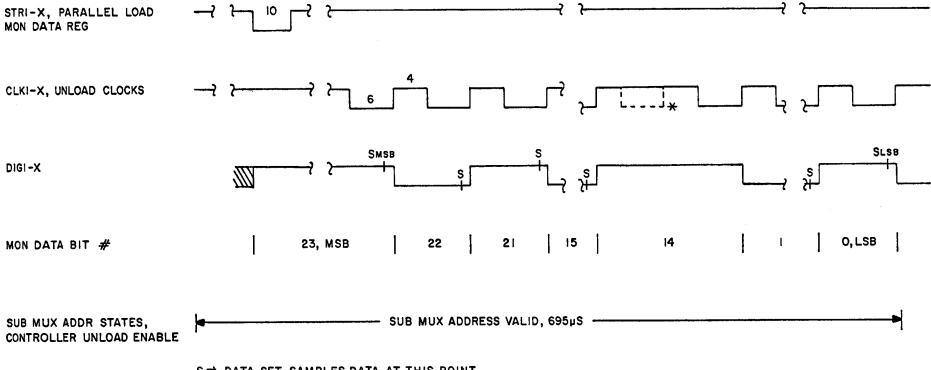

| 10. | CONTROLLER ANALOG DATA TIMING                         |

### TABLE OF FIGURES

| 1.  | DATA SET COMMAND AND MONITOR DATA AND DATA              |   | -  |

|-----|---------------------------------------------------------|---|----|

|     | REQUEST MESSAGE FORMATS                                 | • | .2 |

| 2.  | DATA SET INPUTS, OUTPUTS, AND VITAL SIGNALS             | • | .2 |

| 3.  | TYPICAL MODULE CONTROLLER LOGIC DIAGRAM                 | • | .6 |

| 4.  | DETAILED FUNCTIONAL BLOCK DIAGRAM                       | • | .3 |

| 5.  | DATA SET VITAL, ADDRESS AND SIGNAL I/O PIN ASSIGNMENTS. | • | .8 |

| 6.  | COMMAND/DATA CHANNEL I/O PIN ASSIGNMENTS                | • | .8 |

| 7.  | DATA SET LOGIC FLOW DIAGRAM                             | • | .5 |

| 8.  | DATA SET TESTPOINT (J1) WAVEFORMS                       | • | .5 |

| 9.  | REV. "D" DATA SET DOCUMENTATION TREE                    | • | .7 |

| 10. | MULTIPLEXER - A/D CONVERTER CARD TEST DATA SHEET        | • | .4 |

|     |                                                         |   |    |

## TABLES

1. DATA SET MULTIPLEX ADDRESSES AND ASSOCIATED FUNCTIONS . . .2

#### 1.0 INTRODUCTION

This manual describes the DCS Data Set (module type Ml) functions, operation and specifications and is primarily intended to serve as the principle maintenance, repair and alignment guide. In addition, interfacing information and guidelines are included which may be useful for those who design command or data channels which interact with the Data Set.

The functional descriptions contained in this manual are treated in two levels of detail:

- A brief functional description which provides a general understanding of Data Set functions and operation and is intended to serve as conceptual base for the detailed description which follows. This description also may be useful to the reader who is interested in a general knowledge of the Data Set properties but who has no interest in the circuitry details.

- 2) A detailed functional description keyed to a block diagram and augmented by logic timing diagrams which graphically illustrate important circuit timing relationships. This detailed description is oriented toward the reader who has a well-developed knowledge of digital machinery and is familiar with the TTL logic families. The reader is referred to commercial logic data books for detailed characteristics of the logic elements used in the Data Set.

The Data Set is the prime focus of interest in this manual but functions of the Antenna and Central Buffers are developed where it is necessary to explain aspects of the Data Set operation. For an understanding of these Buffer units, the reader is referred to the appropriate module or DCS System Manual.

The DCS System Manual describes the usage of the Data Set in the VLA system. The reader is urged to consult this manual for details on the command and data flow timing.

#### 2.0 GENERAL FUNCTIONAL DESCRIPTION

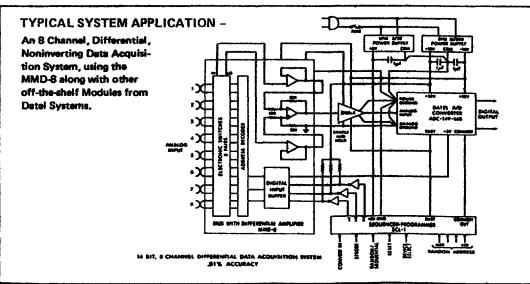

The Data Set physical package is fabricated from a one-unit wide, standard VLA module and contains wire-wrapped logic connector boards for the digital logic chips and a removable (for alignment and test) analog multiplexer and A/D converter PC board assembly.

A front panel numeric LED indicates the Data Set address (discussed later) and flashing green and red LEDs respectively indicate monitor data output activity and malfunctioning signal conditions. Front panel test points permit direct oscilloscope observation of the Data Set operation in place. For a general understanding of the Data Set physique see the Data Set Top Assembly Drawing in the pocket in the back cover of this manual.

The Data Set is a synchronous digital machine which detects, error tests and distributes time-serial digital command messages to commanded devices. The Data Set also gathers, converts, formats and emits time-serial digital monitor data messages. Both time and space division multiplexing is utilized by the Data Set in interacting with commanded devices and data sources.

The command messages originate in the central control computers and are routed to the Data Set via the Serial Line Controller, Central Buffer, L.O. System, WCC and Antenna Buffer, (see the DCS and VLA system manual for details). The monitor data messages are routed to the Buffers for storage and transmission to the control computers via the units cited above.

The Data Set is a passive machine in that it performs a command or data operation only when stimulated by a Buffer. The Buffer emits a time-ordered serial stream of command, monitor data and data request messages and depending upon the character of the messages the Data Set performs the command and monitor data operations.

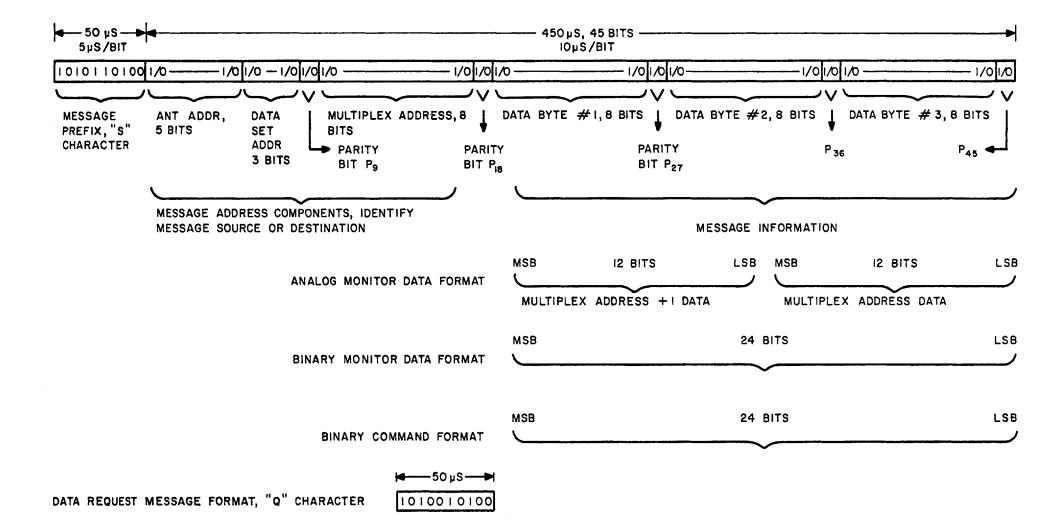

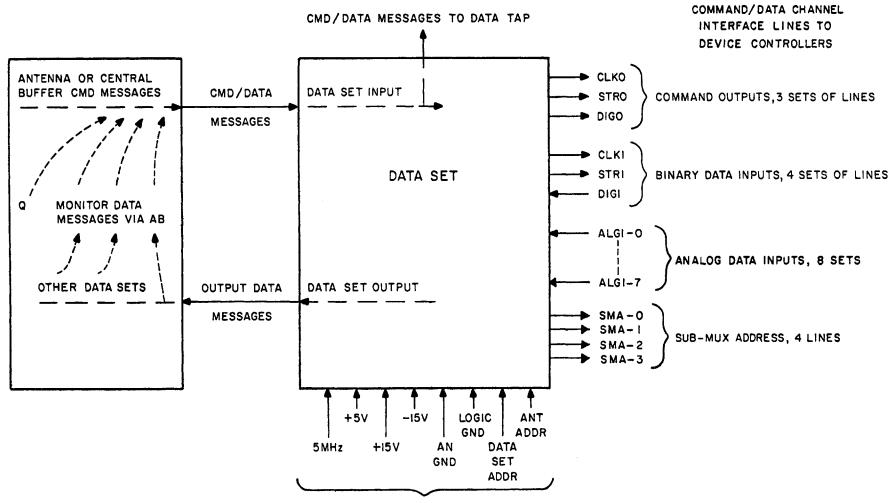

The reader should refer to Figure 1 which depicts the formats of the command, monitor data and data request messages. Figure 2 illustrates the relationships of the Data Set inputs and outputs to the other VLA units. Table I relates the multiplex address ranges and Data Set command/data functions.

In performing a command operation the Data Set detects, loads and tests the command message for parity errors. If the command message

contents satisfy the error detection logic, the data set address components of the message are compared with the data set address to determine if the command is directed to the Data Set in question. If so, then the command information and multiplex address are stored for execution of the command. In executing the command the multiplex address is decoded to activate output information, clock and strobe lines causing the command to be serially loaded and stored in the multiplex address-designated device. The antenna address component of the command is not tested by the Data Set other than for parity purposes. The Buffers store only the commands which pertain to their associated antenna so that the Data Sets need not test for antenna address relevance.

The Data Set is caused to perform a monitor data operation when it detects a Data Request Message emitted by a Buffer. The Data Set then gathers both digital and analog data which is formatted into a monitor data message along with multiplex address data set address, antenna address and message parity data components. In the case of monitor data messages which contain analog data there are <u>two</u> analog data values and only one multiplex address. The multiplex address for the second analog value is implied and is the message multiplex address +1. The monitor data message is then serially output to the Buffer. The Data Set monitor data control logic has a 200 microsecond delay for analog data settling and A/D conversion delay.

The Data Set monitor data sampling operations are time and multiplex address ordered in the VLA cycle. The Buffer evokes two monitor data messages from each Data Set in one VLA cycle. The multiplex addresses for the first monitor data message are derived from an address program stored in a programmable read-only-memory (PROM) which may be programmed to produce any arbitrary sequence of multiplex addresses within a 192 message sequence. The multiplex addresses for the second monitor message are derived in either of

two ways:

- Sequential mode in which 128 analog channels are sequentially sampled twice and 64 digital channels are sequentially sampled once over a ten second period.

- Selected mode in which the multiplex address is set to a fixed channel specified by the Control Computers.

Commands directed to the Data Set designate the selected address and control Select/Sequential mode states. In addition the PROM address may be initialized to a base value so that all Data Sets with identical PROMs sample the same data in any given cycle.

The monitor data messages emitted by the Data Set are rebroadcast by the Antenna Buffer as they are stored in the Buffer data memory. This rebroadcasting enables a data tap (see data tap manual for details) to be connected to any Data Set in the antenna for visual display of command or monitor data messages. The Data Set is inhibited from responding to its own monitor data messages to prevent positive feedback perturbations to the logic.

When the Data Set detects a distorted command or monitor data message, parity error detection logic inhibits the execution of the message (if it is a command) and the multiplex and Data Set address of the distorted message are stored for future monitor data readout as binary monitor data is read out by multiplex address 2008. An additional feature of the error data readout is a flag bit which is set if the error is detected in the multiplex address component of the message. A binary counter is included in the error data logic and is used to count the parity errors that occurred in the intervals between address 2008 data readout meassages. The counter is reset to zero as part of the readout process. Because the Data Set is unable to respond to its own monitor data messages, it cannot test or report its own malfunctioning output.

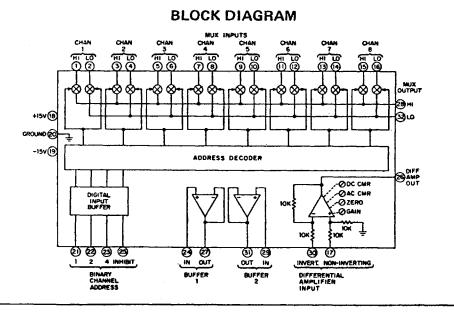

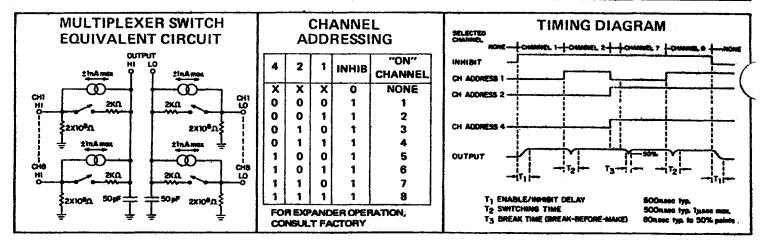

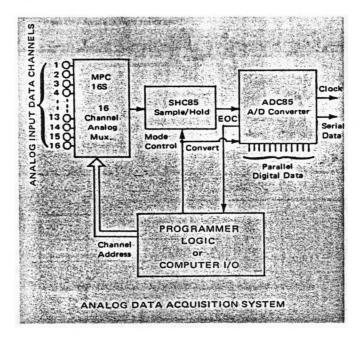

Analog data is multiplexed in the Data Set by an eight channel differential input multiplexer-buffer amplifier. Each of these inputs

is driven by an eight or sixteen channel single-ended or differential multiplexer located in the modules serviced by the Data Set. The lower four bits of the multiplex address drive the remote multiplexer and the next three bits drive the eight input Data Set multiplexer. The multiplex address is incremented after the first analog to digital conversion so that the second analog data channel can be selected and converted.

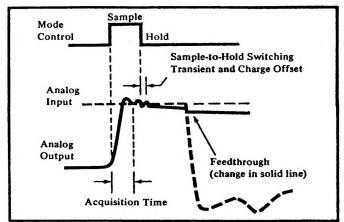

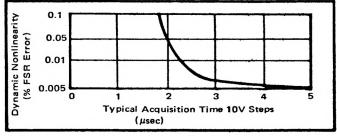

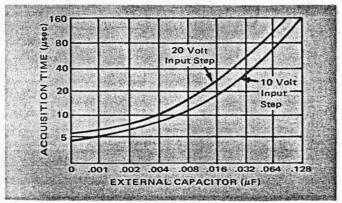

The output of the Data Set multiplexer-amplifier drives a sample and hold unit which "holds" the analog data level constant for the analog to digital converter. The Data Set conversion control logic provides a 30 microsecond settling delay for the analog data before the data is held by the sample and hold unit. Ten microseconds after the data is held, the A/D converter is triggered to start conversion. The end-of-conversion pulse from the A/D converter causes the data to be loaded into a storage register for subsequent readout when the monitor data message is output.

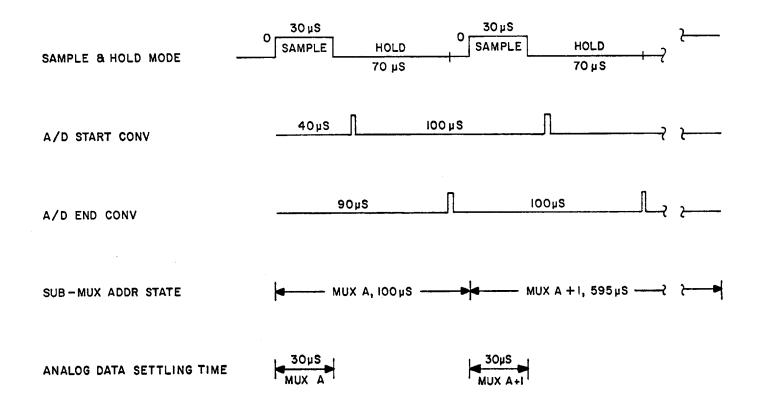

The dominant properties of the analog multiplexer - A/D converter are:

Analog signal range - +10.235 to -10.240 Multiplexer "on" input impedance - 100 megohms Analog Settling Delay - 30 microseconds Multiplexer "on" resistance - 2KΩ/line A/D Conversion Period - 50 microseconds Common Mode Rejection - >60 dB with a 1KΩ source unbalance Conversion Code - 12 bit offset binary code, 5mv/bit Settling Time - <4µsec to .01% of full scale Cross Talk - <1mv, P-P @ 10KHz Input Over Voltage Tolerance - 35 V, max

Each device serviced by a Data Set contains a small logic controller driven by the Data Set which decodes addresses and accepts and stores command information. Under address control from the Data Set, the controller loads binary data and serially

emits it to the Data Set. Analog data is routed to the Data Set A/D converter by either single-ended or differential analog multiplexers in the controller. Many different implementations of controllers are possible to service any combination of command or binary and analog monitor channels. The most general implementation utilizes all three and consists of about 13 chips which can decode and store a 24 bit command, load and output 24 bits of binary data and multiplex 8 channels of differential analog data. Figure 3 shows the logic diagram of a typical controller. The use of these controllers located in the various VLA functional modules permits the rack wiring to be minimized and enables the Data Set to service a great many command and. data channels. The full command/data capacity of a Data Set is:

- 128 analog channels, converted to 12 bit binary values, ±10 volt analog signal range.

- 2) 64 channels of 24 bit binary data (1536 binary bits).

- 3) 48 channels of 24 binary command (1172 binary bits).

FIGURE 1: DATA SET COMMAND AND MONITOR DATA AND DATA REQUEST MESSAGE FORMATS

DATA SET VITAL AND ADDRESS INPUTS

# FIGURE 2: DATA SET INPUTS, OUTPUTS, AND VITAL SIGNALS

| MULTIPLEX ADDRESS              | FUNCTION                        |

|--------------------------------|---------------------------------|

| 0 to 17 <sub>8</sub>           | Analog Data Input, ALGI-0       |

| 20 - 37 <sub>8</sub>           | Analog Data Input, ALGI-1       |

| 40 - 57 <sub>8</sub>           | Analog Data Input, ALGI-2       |

| 60 - 77 <sub>8</sub>           | Analog Data Input, ALGI-3       |

| 100 - 177 <sub>8</sub>         | Analog Data Input, ALGI-4       |

| 120 - 137 <sub>8</sub>         | Analog Data Input, ALGI-5       |

| 140 - 157                      | Analog Data Input, ALGI-6       |

| 160 - 177 <sub>8</sub>         | Analog Data Input, ALGI-7       |

| 200 <sub>8</sub>               | Parity Data Readout             |

| 201 - 217 <sub>8</sub>         | Binary Monitor Data, DIGI-0     |

| 220 - 237 <sub>8</sub>         | Binary Monitor Data, DIGI-1     |

| <b>24</b> 0 - 257 <sub>8</sub> | Binary Monitor Data, DIGI-2     |

| 260 - 277 <sub>8</sub>         | Binary Monitor Data, DIGI-3     |

| 300 <sub>8</sub>               | Set Data Set to Select Mode     |

| 301 <sub>8</sub>               | Set Data Set to Sequential Mode |

| 302 <sub>8</sub>               | Reset PROM Address Counter      |

| 320 - 337 <sub>8</sub>         | Binary Command, DIGO-0          |

| 340 - 357 <sub>8</sub>         | Binary Command, DIGO-1          |

| 360 - 377 <sub>8</sub>         | Binary Command, DIGO-2          |

TABLE I: DATA SET MULTIPLEX ADDRESSES AND ASSOCIATED FUNCTIONS

# 3.0 DETAILED FUNCTIONAL DESCRIPTION

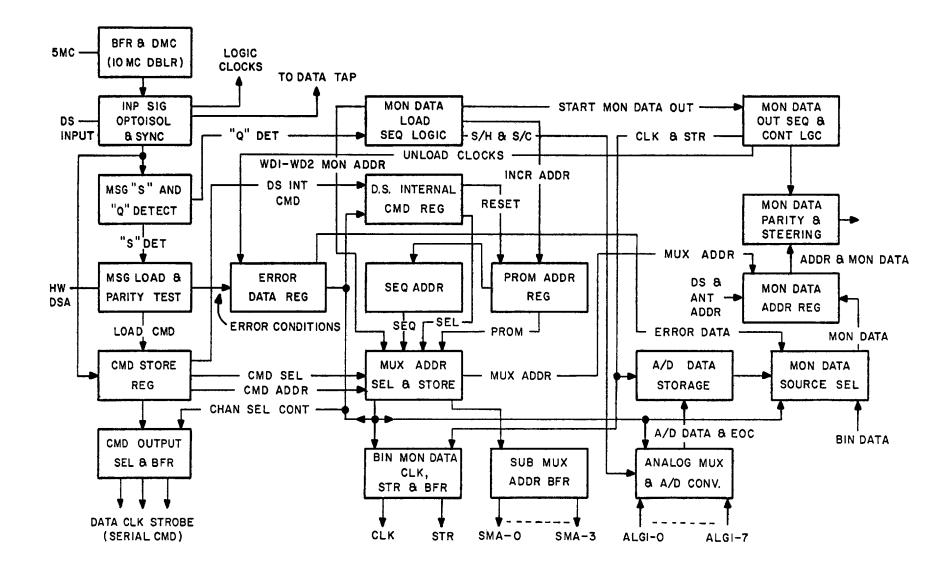

This section contains a detailed description of the theory of operation of the Data Set and is broken into sections which have a distinct natural structure, closely keyed to the Data Set Block Diagram, (Figure 4). The Data Set logic is straightforward and easily grasped by those with digital backgrounds, therefore the logic descriptions in the sections are brief and emphasize the most important aspects of the logic rather than exhaustive gate-bygate discussions of the functions of each and every logic element. The logic sections are discussed in the order of increasing functional dependency.

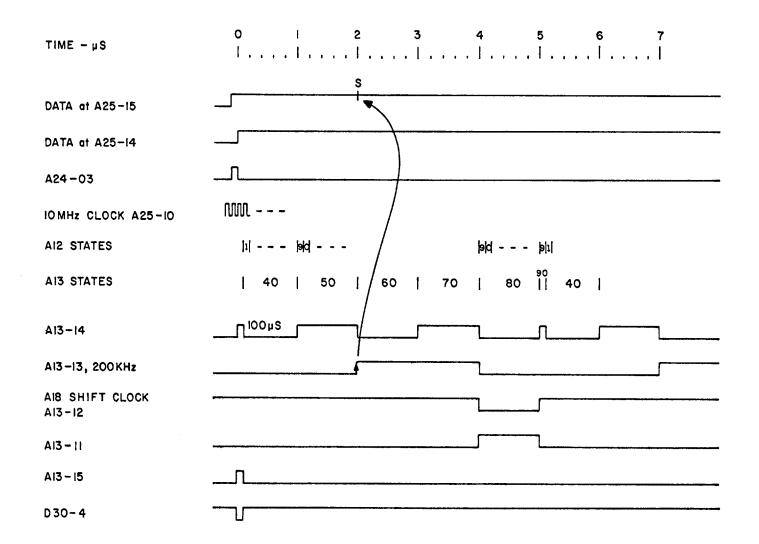

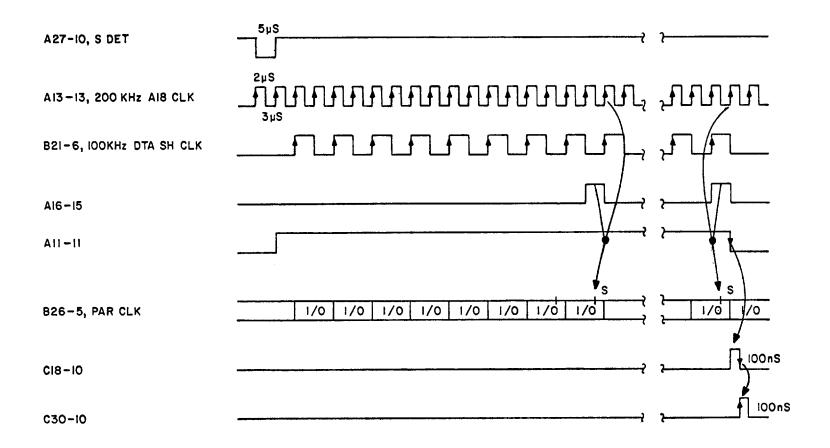

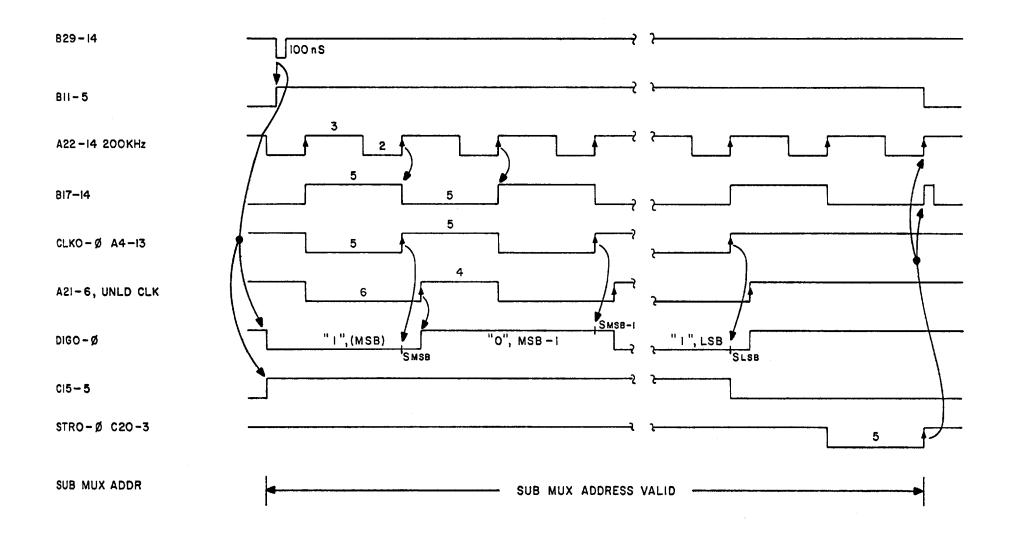

The reader should study the timing diagrams referenced by the description as they graphically illustrate logic operations and are a literal replica of the timing waveforms which may be observed with an oscilloscope. The timing diagrams are keyed to signal source points by the location designator and pin number. Important causative relationships are indicated by arrows from one waveform to others. Clocking relationships are implied by an up or down arrow which indicates the portion of the waveform which causes driven devices to be triggered. Where it is important to the discussion, logic states, time durations, delays or frequencies are marked on the diagrams. A linear time base is employed in all diagrams but delays may be exaggerated for emphasis of race or delay considerations. Waveform sampling is indicated by arrows, tick marks and the letter S to denote sampling.

Finally, logic elements are designated by the location designation and pin number of the driving source. This treatment is one of the conventions of the wire-listing programs which enables close correlation of the wiring documentation with the logic diagrams.

The discussions refer to the "Rev. C" and "D" versions of the Data Set. Earlier revision levels will be upgraded to the "D" level. Revision "C" and "D" are logically identical except for wiring details.

The Revision "D" Data Set logic diagrams are in the pocket in the back cover of this manual.

### 3.1 5 MHz Clock Detection and Doubling Logic

An externally provided, 5 MHz 1.5 volt peak (nominal) sine wave signal is the clock source for the Data Set. A 72710 differential analog comparator A30B "squares" up the 5 MHz signal to drive the Al4 harmonic generator which doubles the 5 MHz clock. The Al4 tank circuit rings at 10 MHz and is "kicked" by the positive-going edge of the drive from inverter Al002. Al0 is a 74SO4 because of its high switching speed which produces sharp edged drive pulses for the harmonic generator. The drive edges are differentiated by the 10 pf/l KΩ circuit in the MPS 918 base circuit and the positive-going edge provides a narrow current impulse to the transistor base. Inverter Al004 is caused to operate in a quasi-linear region by the 2K resistor in Al4. The output of Al006 is the highest frequency clock source in the Data Set and all clock rates are derived from it.

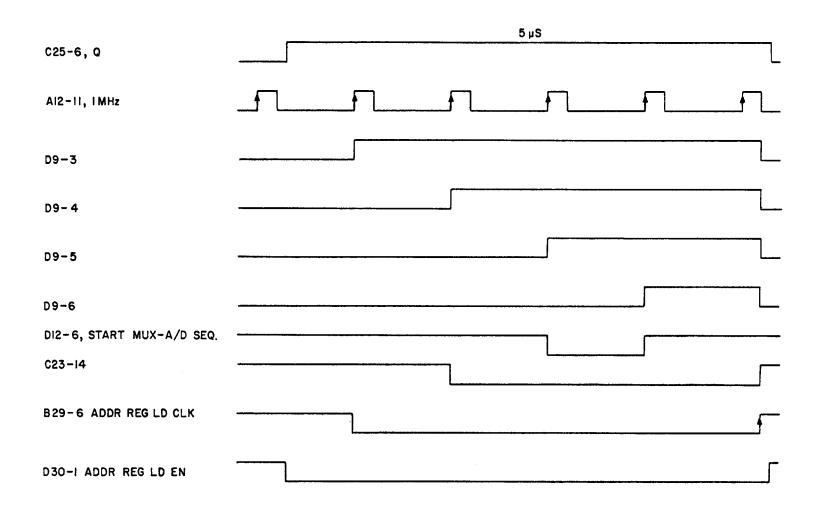

# 3.2 Input Signal Synchronization Logic

The optically-coupled isolator A30A detects the Data Set input signals and provides ground isolation between the Data Set and Buffers. The data is clocked into shift register A25 by the 10 MHz clock. 1/0 or 0/1 data edges are detected by exclusive or gate A2403 which presets counters A12 and A13 to a count state of 41. This counter is incremented by the 10 MHz clock to a count of 90 which then causes the counter to be reset to the 41 state via the 7402 D3004. Timing Diagram 1 depicts the timing relationships. Output A1313 is a 200 kHz waveform whose positive-going edge is delayed 2 microseconds from the 1/0 or 0/1 input signal edges. This 200 kHz signal is the clock for counters Al6 and All and also the sample clock for shift register Al8. The purpose of the delay is to sample the input signal at the approximate center of the "S" character bits. A 1 MHz clock is tapped off counter A1211. The use of this clock is discussed later.

## 3.3 Message Detection/Loading Logic

Shift register A18 is serially loaded with the input data stream by the phase adjusted 200 kHz clock from A1313 described above. Two gates A2610 and A2710 serve as matched filters to detect the presence of a data request message (Q)or start of a command or monitor data message (S) in shift register Al8. When the last eight bits of the Q message are loaded into A18, gate A2610 goes true for 5 µsec. This Q detection initiates the monitor data gathering sequence described later. Similarly gate A2710 goes true for 5 µsec when the last eight bits of the start (S character) portion of a command or monitor data message are loaded into A18. This S detection activates the message loading sequencing counter consisting of flip-flops B2106 and synchronous counters Al6 and All. This counter generates 45 shift clocks to serially load the message into the loading registers B30, B25, B20, B15 and B10. See Timing Diagram 2 for waveform details. Counter Al6 operates with a radix of 9 to program a parity test of the message data on a byte by byte basis. The parallel contents of register B30 are presented to B26, a parallel parity checker/generator, and at the count of 9 the output of B26 will enable the J input of flip-flop B2110. If there is a parity error, B2110 will be clocked true. At the completion of the loading sequence, the counter is shut off by the fall of Allll which also triggers one-shot Cl810. The strobe output of C1810 causes parity error data to be stored in the error data register (discussed later) if an error occurred in the message. If the message passes the parity test, the C1810 strobe is enabled onto comparator B8 which compares the hardwired data set address with the data set address standing in register BlO. If the addresses agree, B8 A=B output passes the B2110 strobe to gate B2914 which further tests the message to determine if it

is a command by anding mux address bits 128 and 64 (both true only for commands). If the message is a command addressed to the Data Set in discussion then the 24 information bits of the message are parallel loaded into registers B24, B19 and B14. The Cmd Busy flip-flop Bllll is also set by B2914. The command multiplex address is caused to be stored in the multiplex register Al5 and A2 via multiplexers D21, D22, D26 and D27. The multiplexers are pointed to the portions of the message loading registers which contain the command multiplex address by gates D506/10 and D2406/10 and the Cmd Busy flip-flop Bllll. The mux address is strobed into registers A15 and A2 by the leading edge of one shot C3009. C3009 is triggered by the trailing edge of one shot C1810 and provides 100 ns of delay to enable the mux address to propagate through the multiplexers and stabilize at the Al5 and A2 inputs before being clocked by C3009. If a parity error should occur, one shot C1807 is triggered on to provide a stretched illumination of the front panel red parity error LED.

Note that the parity test logic operates on <u>both</u> command and monitor data messages and causes error data to be stored for both classes of messages. Thus a parity error in a monitor data message is heard by all Data Sets in the antenna and is multiply reported. Also note that the antenna address is not tested or used in the loading process other than in the parity error tests.

#### 3.4 Command Output Logic

In the previous section we saw how the command messages were loaded, error tested and parallel stored. The storage process is completed by about 200 ns after the last load shift clock. The 24 command information bits are immediately unloaded to the command destination which leaves the message loading circuitry free to accept the next message which may immediately follow. The unload

operation is initiated by gate B2914 (mentioned above) which sets control flip-flops Bll05 and Cl511. Bll05 enables counters Bl7 and B22 to count out 24 100 kHz shift clocks and one clock pulse time later a strobe pulse. The 24 command data bits, checks and strobe are enabled to one of three pairs of digital outputs by address decoder Bl2 which is driven by the four high order bits of the multiplex address. The four lower order bits of the multiplex address are decoded by the commanded devices and enable the information output on the three sets of outputs to be loaded and stored. Note that both time and space division multiplexing are used in this command distribution logic. For more details on the utilization of these signals see Section 6 of this manual which contains a typical command channel logic diagram.

The trailing edge of the strobe pulse resets the command busy flip-flop Bllll. Bllll forces the multiplex address registers A2 and A15 to be cleared via the DS busy gate B0613. Thus the multiplex address storage registers are cleared to address 0 between command operations.

Timing Diagram 3 shows the time relationships of the command output logic.

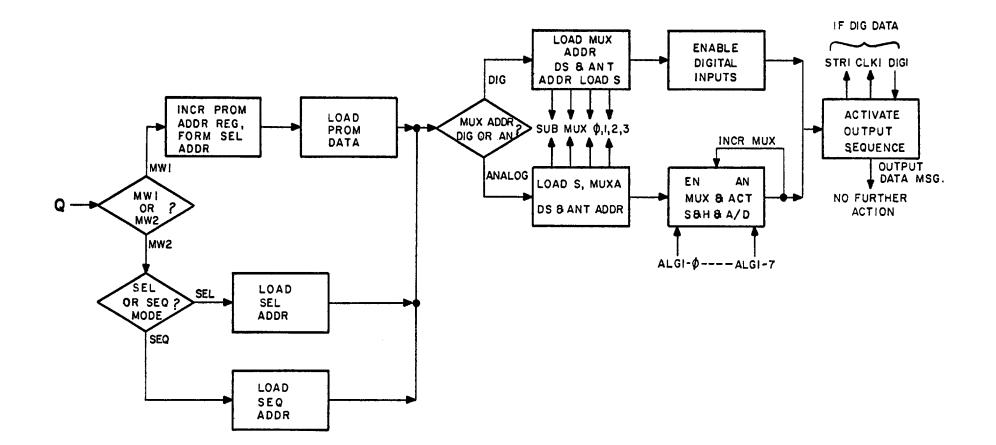

## 3.5 Word 1/Word 2 and Mux Load Sequence Logic

When a data request message (Q) is detected (see Section 3.3), it toggles D2305 which controls the word 1/ word 2 steering of the multiplex address multiplexers D21, D22, D26 and D27. D2305 also increments the PROM address counters D17 and D18. The reader will remember that word 1 (i.e., the first monitor data message evoked by the Buffer in a VLA machine cycle) contains data selected by the program residing in the PROM. Word 2 data is associated with either a computer-specified (i.e., selected address) or a sequentially

scanned address. The word l/word 2 ordering is accomplished by the two one shots D0405 and D0409, which are triggered by the Q pulses from A2610. The Q pulses occur in pairs (1 pair/ VLA machine cycle) and are separated by either 800 microseconds or 4.5 milliseconds depending upon which Buffer drives the Data Set. One shot D0406 is retriggerable with a period of 5 Ms which is greater than the Q pulses separation. This delay causes flip-flop D2305 to be left in the proper state to steer the PROM addresses to the address register when the Buffer requests the first monitor word in the VLA cycle. Shift register D9 is a clock phase generator which generates a time delayed clock to allow the multiplex address enough time to propagate through the address multiplexer to the address register. Other functions of the clock phase generator are initialization of the 200 kHz divider A0705, triggering of the output data sequencing logic, loading of the multiplex address, data set address and antenna addresses in C22 and C27, and the "S" character bits in registers C24 and C26. Timing Diagram 4 shows the clock terms generated by the clock phase generator D9.

The PROM is physically located on the analog multiplexer - A/D board for packaging convenience because of its 24 pin physique.

#### 3.6 Monitor Data Multiplex Address Formulation

Counters D17 and D18 are incremented by the leading edge of the Q detector and have a radix of 192, thus the PROM address recycle rate is 192 VLA machine cycles in 10 seconds. Since counters D17 and D18 are incremented by the leading edge of the Q detector, the address program contents of the PROM have about five microseconds to settle through the multiplexer before they are loaded into the multiplex address registers A2 and A15 by the logic described in the section above. This same settling time also applies to the select address and sequential address data.

The select address data is stored in shift register C21 which is loaded by a command addressed to multiplex address  $300_8$ .

When this command is detected, the lower eight bits of the command are shifted into C21 and the select/sequential flip-flop is set to the select state. This flip-flop then causes the multiplex address multiplexer to route the selected address stored in C21 to the address registers A2 and A15.

The sequential address is formed algorithmically by 2 to 1 multiplexers D19 and D20 and full adder D13 under the control of gates D2903, D2906, D1203, C1213, C0510, C0514 and C0506. The sequential addresses scan all 128 analog addresses twice in ten seconds and the 64 digital addresses once in ten seconds. The digital address scan is broken into two scans of 32 channels each between analog data scans. The base for the sequential address counter is the PROM address counter which sequences from 0 to 191 and is incremented once per cycle.

The sequential address algorithm is very simple and involves using the PROM address counter directly, doubling the counter value and/or adding 64 to the count. Briefly the algorithm is as follows:

| PROM Address<br>Counter Range | Sequential Address<br>Counter Range | Algorithm<br><u>Rule</u> |

|-------------------------------|-------------------------------------|--------------------------|

| 0 <u>&lt; Np &lt;</u> 63      | 0 <u>&lt;</u> Ns <u>&lt;</u> 126    | Ns = 2 Np                |

| 64 <u>&lt; Np &lt;</u> 95     | $128 \leq Ns \leq 159$              | Ns = Np + 64             |

| 96 <u>&lt; Np &lt;</u> 159    | $0 \leq Ns \leq 126$                | Ns = 2 Np                |

| $160 \le Np \le 191$          | $160 \le Ns \le 191$                | Ns = Np                  |

The control gates enable or inhibit the add 64 and left or no shift logic operations in the adder and multiplexers on the basis of the PROM address register states. The contents of the multiplex address register are used extensively in the Data Set to control the distribution of monitor data and command output clocks, strobes and data. The lower four bits of the

address register are buffered out of the Data Set as low true lines by power Buffer A8. After the completion of a command or monitor data operation, the D5 busy logic A17 and B6 force the multiplex address register to a zero state. This then makes the sub-mux address assume the zero state so that all external devices will sense this state. The external analog multiplexers will all select this channel and will route it to the Data Set. This forced channel selection is not a problem condition as the Data Set is not perturbed by the presence of this signal.

#### 3.7 Analog Data Gathering Sequence

Counter C17 and C1605 are enabled by control flip-flop C1611 which is set by the clock phase generator discussed in Section 3.5. The multiplex address had been loaded 1 microsecond earlier in multiplex address registers A2 and A15. The counter is incremented by 100 kHz clocks from A705 to generate sequential control terms for the sample and hold unit and A/D converter. At 30 microseconds, the sample and hold is set to the hold mode; at 40 microseconds, the A/D start conversion input is triggered by one shot D1006. After a 50 microsecond conversion, the A/D end of conversion line drops and triggers one shot D1010 which resets flip-flop A0710 to reset the sample and hold unit to the sample state. Gate C1913 steers the 500 ns one shot to load the A/D data into shift registers Cl and C2. At 100 microseconds, counter C17 increments the multiplex address registers (if the mux address is in the analog data address range) which then causes the next sequential analog channel to be selected by the external analog multiplexer. With the new analog data the sample and hold unit, start conversion, end of conversion and data storage operations occur at 130, 140 and 190 microseconds respectively. At 200 microseconds, flip-flop C1610 is reset and the output data shift operation is initiated by setting flip-flop Cl505.

Gate C1913 generates a binary data strobe which is used to cause binary data sources to load the registers for an impending unload shift.

#### 3.8 Output Data Sequencing Logic

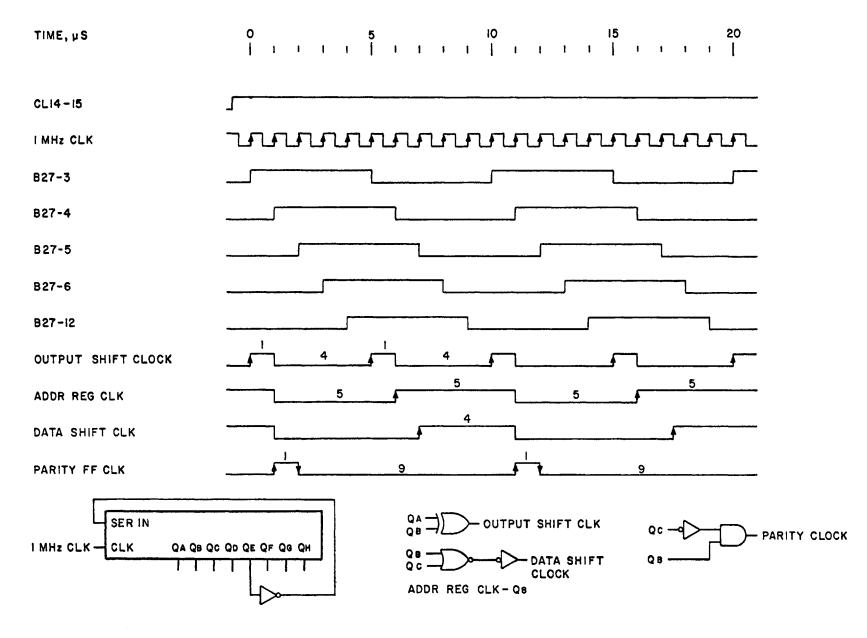

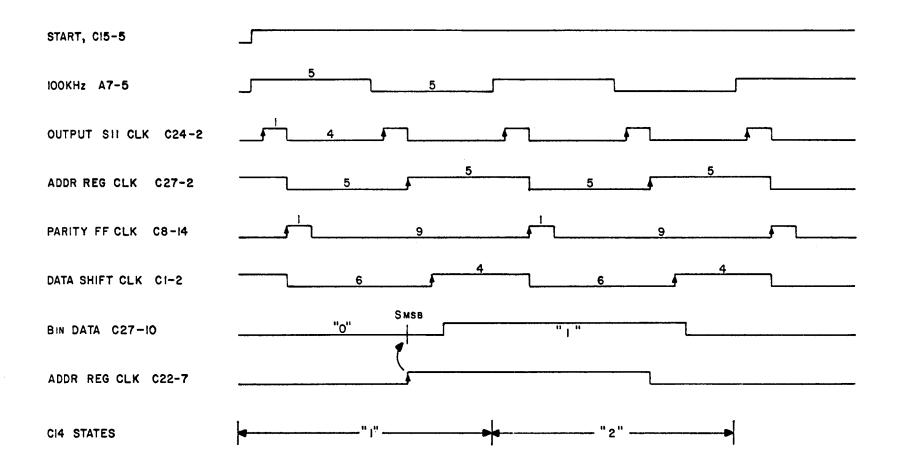

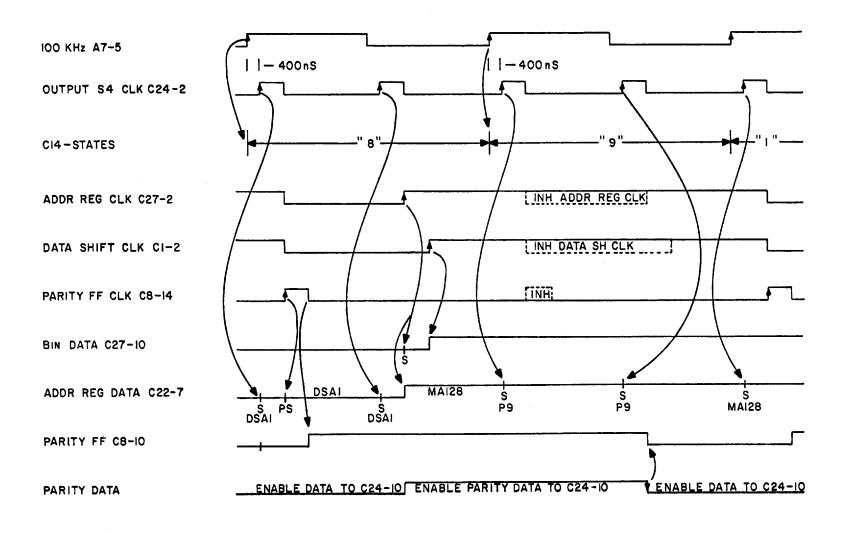

The data output operation essentially consists of serially shifting out the address and A/D data stored in the registers described above. Counters C14 and D16 are incremented by 100 kHz clock pulses from A705 and generate sequencing and control terms which program the output of the monitor data message. Counter Cl4 operates with a radix of nine to cause parity data to be output at the appropriate points in the output message. Shift register B27 is a Johnson counter with a radix of 10 and is incremented by 1 MHz clock pulses from Al211. The counter is initialized to an all zero state by flip-flop C1505. When C1505 goes high at the start of the output sequencing operation, a wave of five "1"s followed by a wave of five "0"s circulate around the register. The gates driven by B27 generate time-phased clocking terms to clock all the monitor data registers. Timing Diagram 5 shows these waveforms and the basic logic. The logic driven by these terms are: parity counter C8, output register C29 and C26, data set/ ant/multiplex address registers C22 and C27, data registers C1, C2, C6 and Cll, parity error registers B5 and C9 and the binary data registers in external binary data channels. These sample clocks are time-phased to avoid race conditions in clocking the long string of concatenated shift registers and also to enable the Data Set to be very tolerant of logic delays in external binary data channels. Timing Diagrams 6 and 7 show the generation and usage of these clock terms. Under multiplex address control multiplexer C7 selects either the A/D converted data or binary data from a binary data channel in some module serviced by the Data Set. And-or-invert gate D0210 selects either the C7 data mentioned above or the parity error data from parity data registers C9 and B5. Every ninth count state of

counter Cl4, the parity readout control logic (consisting of gates Bl310, inverters C2514 and C2502 and flip-flop Al705) causes and-or-invert gate D0206 to steer the parity data from flip-flop C8 into the output data stream.

Gate BOILO causes the clock inhibit flip-flop D1412 to be set at a count of 24 so that the three data registers (i.e., converted analog data, parity error data and external binary data register) see only 24 unload clock pulses which is enough to unload them completely. An additional 16 clock pulses are required to bring these data to the output register C24. This 24 clock pulse count is chosen to permit command channels to operate in a 24 bit circular shift mode so that the contents of command channels may be read out non-destructively as binary data. Module L7 uses this feature. Counter D16 is preset to a count of 3 which provides sufficient time for all data to propagate completely through registers C24 and C26 with an additional 45 microseconds of shift time after the last data has shifted through C24 and C26.

The DS busy flip-flop A1710 is reset at the completion of the output data shift operation.

An output of flip-flop C1506 is used to inhibit the ability of the Data Set to "hear" its own output when used with an antenna Buffer. The inhibit disables the phase adjust term from exclusive or gate A2403 and clears shift register A18 so that the 200 kHz clocks are not phase perturbed by the Data Set's own output (a positive feedback) and it does not detect the S in its output message.

Parity counter C8 is initialized to the "l" state by the multiplex address clock phase generator and is reinitialized after the parity data for each byte is read out.

Buffers A0411 and A0409 drive the data to the Buffer and the data out LED respectively.

## 3.9 Parity Error Data Readout Logic

In the event that a distorted command or monitor data message is detected by the Data Set, gate Bl606 causes the message multiplex and Data Set address components and the error count to be stored in registers B5 and C9. In addition if the error occurred in byte 2 of the message, gate B0106 sets flip-flop D2311 which is also stored with the data above. In the event that the parity rate is high, counter B4 counts the number of errors (up to 16) between the error data readouts on multiplex address 2008. Gate D0610 goes true when multiplex address 2008 occurs and enables the parity data in registers C9 and B5 to be routed to the output logic via and-or-invert gate D0210. The data is clocked and sampled in the same manner as analog or digital data.

FIGURE 4: DETAILED FUNCTIONAL BLOCK DIAGRAM

TIMING DIAGRAM 1: INPUT SIGNAL SYNCHRONIZATION TIMING

# TIMING DIAGRAM 2: MESSAGE DETECTION - LOADING TIMING

TIMING DIAGRAM 3: COMMAND OUTPUT TIMING

# TIMING DIAGRAM 4: MONITOR DATA MULTIPLEX ADDRESS CLOCK PHASE GENERATOR

TIMING DIAGRAM 5: MONITOR DATA OUTPUT CLOCK GENERATOR

TIMING DIAGRAM 6: MONITOR DATA OUTPUT CLOCKING, START OF DATA OUTPUT

TIMING DIAGRAM 7: MONITOR DATA OUTPUT TIMING, PARITY DATA OUTPUT

# 4.0 ANALOG SUBSYSTEM ALIGNMENT AND TESTS

The analog multiplexer - A/D converter board is removable from the Data Set for alignment and test in a controllable analog and logic environment. This environment is provided by an A/D-mux test fixture, (dwg. D13720L45) a high precision adjustable DC source (Fluke 343A), a digital multimeter and an oscilloscope.

The A/D-mux test fixture has a dual bus switching structure and several analog signal sources. Control and conversion logic sequences the multiplex address, triggers the sample/hold unit and A/D converter and displays the converted digital value and mux channel. The timing of these terms is identical to those in the Data Set. Control switches permit the multiplex address to sequence or be set at any channel. These switches also permit the selection of continuous or manually triggered conversions and the use of various alignment and perturbation sources.

## 4.1 Alignment Procedure for Revision C A/D Board

| 1. | Set the | front panel | switches | of | the | mux-A/D | test | fixture |

|----|---------|-------------|----------|----|-----|---------|------|---------|

|    | unit as | follows:    |          |    |     |         |      |         |

CMP/LC - LC SCAN/SEL - SEL MANUAL/OFF - OFF BUS A 0-JO - 0 BUS A DIFF/CM - DIFF BUS A +/-- + BUS B 0-50 - 0 BUS B DIFF/CM - DIFF CHANNEL SELECT - CH 0 BUS A SOURCE - GND BUS B SOURCE - GND

Set all channel switches to BUS A.

Plug a Revision C A/D board (component side up) into the top socket and turn power switch on.

2. Connect a 4 digit Data Precision DVM between the S/H out

and the analog ground test points, and adjust the S/H offset pot for a reading of 0.0000V.

- Move the DVM to the analog out and analog ground test points and set the zero adjust pot on the MMD-8 multiplexer for 0.000V out.

- Remove the DVM and adjust the ADC offset pot for a tester display of 0.000V.

- 4.2 DC Common Mode

- Set the BUS A DIFF/CM switch to CM. Set the BUS A source to 100 Hz square wave. Switch the desired channel to BUS A and all others to BUS B (GND). With a scope of at least 5 MV/cm sensitivity connected between the analog out and analog gnd terminals, adjust the DC CMR pot on the MMD-8 for the absolute minimum signal.

- 4.3 AC Common Mode

- Using the procedure outlined above, set the BUS A source to a 1 kHz sine wave and adjust the AC CMR pot on the MMD-8.

- Repeat the DC CMR adjustment of step 4.2.1 to insure proper AC and DC CMR alignment.

- 4.4 A/D Adjustment and Test

- Set the BUS A DIFF/CM switch to DIFF and the BUS A source to external. Apply a precision DC reference between the BUS A Hi and Low terminals.

- Set the reference for +10.000V and adjust the ADC gain pot for a panel reading of 10.000V.

- Set the reference for +0.000V and adjust the ADC offset adj. pot for 0.000V. Return to step 2 and repeat until no further adjustment is necessary.

- 4. Using the test data sheet, Figure 10, vary the external reference from +10.000V to -10.000V in 1.0V increments and record the displayed converted values. It may be convenient to set in small offsets to the 1V increments to more effectively evaluate any error biases which may exist in the A/D converter.

#### 4.5 CMR Test

- 1. Install a 1 k $\Omega$  resistor between the BUS A Hi and Low terminals. Connect desired channel to BUS B.

- Set BUS A source to external. Set RSA and RSB switches to 0 resistance. Set A and B +/- switches to +. Set A and B CM/DIFF to CM.

- 3. Set BUS B source to 1 k, and note converted value.

- 4. Set BUS B source to 1V and record value.

- 5. Set BUS B source to 10V and note value.

- 6. Calculate and record following values:

$$CMR_1(dB) = 20 \log \frac{|(step 3 - step 4)|}{1.000V}$$

$CMR_2(dB) = 20 \log \frac{|(step 3 - step 5)|}{10.000V}$

In handling the A/D-mux board, it is very important to avoid touching the PC board contact fingers as human skin oil and salts may contaminate and corrode the edge connector contacts in the Data Set. This will cause unreliable contact in a few months time. If the contact fingers are touched, the edge connector contact area should be thoroughly cleaned before installing the A/D-mux board in the Data Set.

| DATA | A SET | MUX | - | A/D | TEST | DATA |

|------|-------|-----|---|-----|------|------|

| Board Type  | REVISION C      | _ Serial #       |              |

|-------------|-----------------|------------------|--------------|

| Date        | <u></u>         | _ Test/Set-up By |              |

| Input Volts | Conv'rtd. Value | Error, MV        | A/D SN       |

| +10.000     |                 |                  | MUX SN       |

| + 9.000     |                 |                  | Installed in |

| + 8.000     | <u></u>         |                  | DS           |

| + 7.000     |                 | <del></del>      | DATE         |

| + 6.000     |                 |                  |              |

| + 5.000     |                 | <u> </u>         |              |

| + 4.000     |                 | ••••••           |              |

| + 3.000     |                 |                  |              |

| + 2.000     | ·····           |                  |              |

| + 1.000     | · · ·           |                  |              |

| ± 0.000     |                 |                  |              |

| - 1.000     |                 |                  |              |

| - 2.000     |                 |                  |              |

| - 3.000     |                 |                  |              |

| - 4.000     |                 |                  |              |

| - 5.000     |                 |                  |              |

| - 6.000     |                 |                  |              |

| - 7.000     |                 |                  |              |

| - 8.000     |                 |                  |              |

| - 9.000     |                 |                  |              |

| -10.000     |                 |                  |              |

| CMR, dB     | CM              | 1R-2             |              |

FIGURE 10: MULTIPLEXER - A/D CONVERTER CARD TEST DATA SHEET

#### 5.0 DIAGNOSTIC/TROUBLESHOOTING OBSERVATION POINTS AND DEPENDENCY RELATIONSHIPS

Figure 8 shows the timing waveforms which may be observed on the front panel test connector (Jl). These test points are connected to important points in the logic and are a valuable diagnostic aid in evaluating the Data Set logic operations.

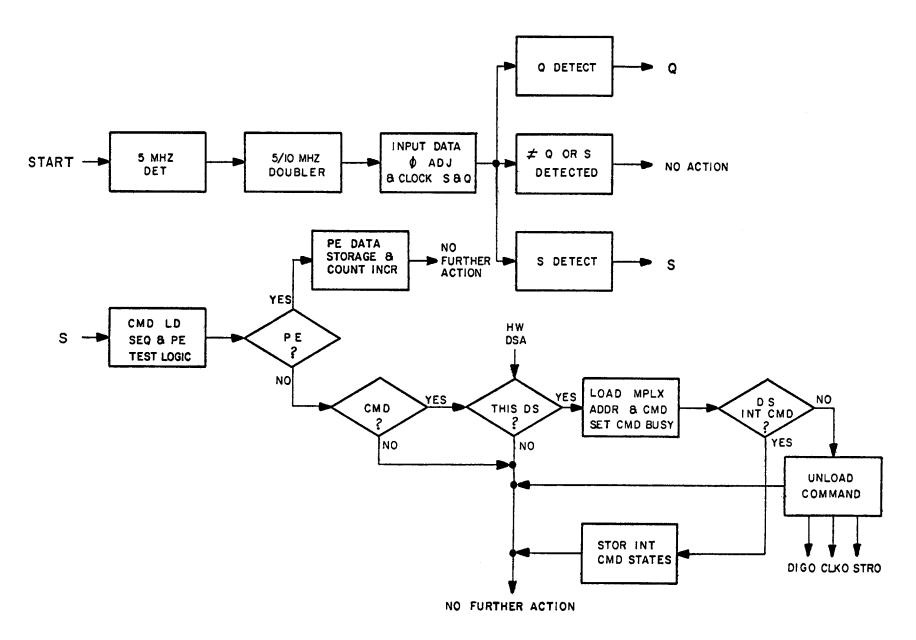

Figure 7 shows the Data Set logic flow diagram. This schema illustrates the logic and dependency relationships of the Data Set inputs, stimulus and outputs.

FIG. 7: DATA SET LOGIC FLOW DIAGRAM

FIG.7: CONT. DATA SET LOGIC FLOW DIAGRAM

FIGURE 8: DATA SET TESTPOINT (J1) WAVEFORMS

| Jl Pin | Signal  | Comment                          | $\frac{\text{Waveform}}{\text{Gnd}} = \text{LO}$ |

|--------|---------|----------------------------------|--------------------------------------------------|

| 1      | +5SYNC  | +5 VDC                           | DC, +5                                           |

| 2      | GNDSYNC | Logic Conn                       | DC, Gnd<br>MUX MUX+1 - +10V MAX                  |

| 3      | ANMON   | Multiplexed<br>Analog Data       | 100<br>µS 595µS                                  |

| 4      | PARERR  | Parity Error<br>Detected         | 5µS                                              |

| 5      | DTAOUT  | Monitor Data<br>to Buffer        | Monitor Data<br>Message, Hi-True                 |

| 6      | DSINP   | Data Set                         | Cmd/Monitor<br>Messages, Lo-True                 |

| 7      | CLKDIN  | Clocked Input<br>Message         | Cmd/Monitor<br>Messages, Hi-True                 |

| 8      | SHFTCLK | Input Message<br>Load Clock      | μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ<br>μ        |

| 9      | SHFTEN  | Input Message<br>Shift Enable    | 450 y S                                          |

| 10     | SDET    | Cmd/Mon Message<br>Detected      | 5μS                                              |

| 11     | QDET    | Data Request<br>Message Detected | 5μS                                              |

| 12     | SERCMD  | Output Cmd<br>Information        | 10 µs/Bit, Lo-True                               |

| 13     | ADEOC   | A/D Conv End<br>of Conversion    | 500 nS                                           |

| 14  | 192EN   | DS Int Cmd En                               | 250 µ S                         |

|-----|---------|---------------------------------------------|---------------------------------|

| 15  | DSSEL   | Message Directed<br>to Data Set             | 100 n S                         |

| 16  | SER/SEL | Sequential/Select<br>Mode Control           | Hi = Sequential Mode<br>Control |

| 17  | CMDCLK  | Command Output<br>Shift Clock,<br>24 Pulses | 6 μS 4 μS                       |

| 18  | RSPPOM  | Reset Prom Address<br>Register              | 250 y S                         |

| 19  | A/DSC   | A/D Converted Start<br>Conversion           | 500 nS                          |

| 20  | DSCLK   | Binary Monitor Data<br>Shift Clock          | 6 µS 4 µS                       |

| 21  | BINSTR  | Binary Monitor Data<br>Load Store           | 10 #S                           |

| 22  | DINDTA  | Binary Monitor Data<br>Input to Data Set    | Low True Serial<br>Waveform     |

| 23  | CMDSTR  | Cmd Chan Load<br>Strobe                     | 5yS                             |

| .24 | 5mHZ    | 5 MHz detector<br>Output                    |                                 |

| 25  | 10MHZ   | Doubled 5 MHz                               |                                 |

| 26  | SMA-4   | Mux Address - 4,<br>"16", Hi True           | OR                              |

|     |         | 2                                           | 250µS CMDS<br>700µS MON DATA    |

| 27 | Sma-5   | Mux Address - 5<br>"32", Hi True                         | OR<br>250 ps CMDS<br>700 ps MON DATA   |

|----|---------|----------------------------------------------------------|----------------------------------------|

| 28 | SMA-6   | Mux Address - 6<br>"64", Hi True                         | SAME AS ABOVE                          |

| 29 | SMA-7   | Mux Address - 7<br>"128", Hi True                        | SAME AS ABOVE                          |

| 30 | SMA-0   | Sub-Mux Address - 0<br>"l", Low-True                     | MONITOR<br>DATA 100 µS<br>OR<br>595 µS |

| 31 | SMA-1   | Sub-Mux Address - l<br>"2", Low-True                     | SAME AS ABOVE                          |

| 32 | SMA-2   | Sub-Mux Address - 2<br>"4", Low-True                     | SAME AS ABOVE                          |

| 33 | SMA-3   | Sub-Mux Address - 3<br>"8", Low-True                     | SAME AS ABOVE                          |

| 34 | A/DDATA | Converter Analog<br>Data Storage Reg                     | 24 Bits, Low True                      |

| 35 | DSBUSY  | Data Set Busy,<br>Executing CMD or<br>Gathering New Data | CMD 250 µS<br>MONITOR 695 µS<br>DATA   |

| 36 | WD1/WD2 | Monitor Word 1/2<br>Control Flip-Flop                    | 4.5mS<br>OR 1mS<br>WD2 MON WD1 WD2     |

| 37 | PEDATA  | Parity Error Data<br>Storage Reg Output                  | PE Message Data,<br>Hi-True            |

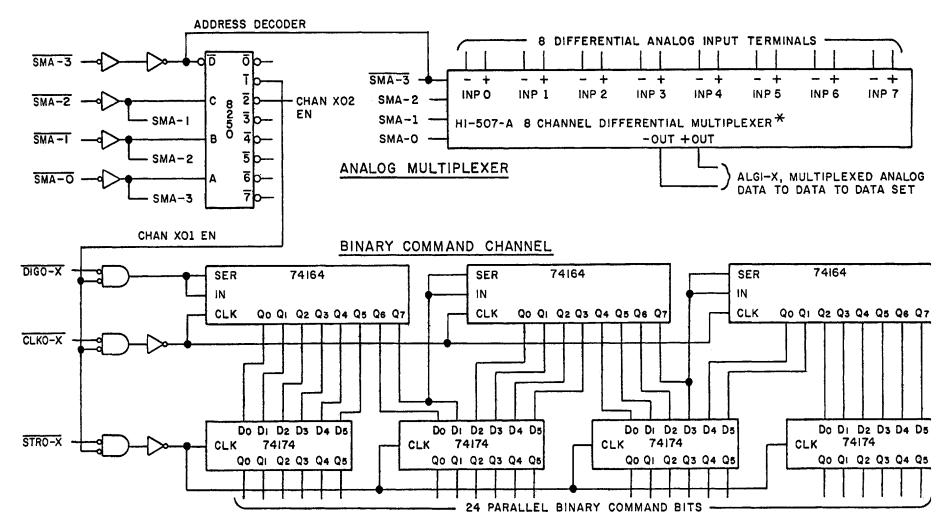

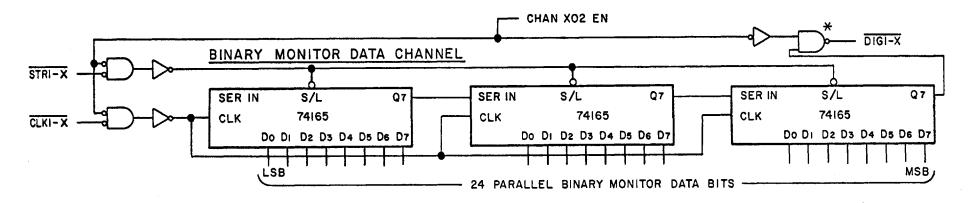

#### 6.0 TYPICAL COMMAND/DATA CHANNEL LOGIC

In this section, we consider the logic circuitry and functions of a generalized controller which may be used for module control and monitoring. The controller can accept and store a 24 bit binary command, read out a 24 bit binary data word and multiplex 16 channels of analog data. Figure 3 depicts the logic diagram of this generalized controller. The logic description in this section is a simplistic treatment. The interested reader may refer to the earlier section for a more detailed discussion of the generation and use of the clocking and strobe signals.

A fundamental requirement for a command or data channel is multiplex address enabling or activation. Each channel serviced by the Data Set has a unique 8 bit multiplex address assignment which when decoded enables a command to be stored or data gathered. The four high order bits of the multiplex address are decoded internally in the Data Set and cause the Data Set internal analog multiplexer, binary data and command lines to be activated to interact with a module controller. Each decode state of these higher order bits is associated with a group of 16 multiplex addresses; therefore, up to 16 channels of analog data, command or binary data may be serviced by the analog, command and binary data lines. Referring to Table I we see that the Data Set analog multiplexer can service eight controllers having up to 16 analog channels for a total of 128 analog channels. Combinations of eight and sixteen channel controllers may also be implemented. Four sets of binary monitor lines can service up to 64 channels of 24 bit binary monitor data or 1536 binary bits. Three sets of command lines can service up to 48 channels of 24 bit binary commands or 1172 bits.

The four lower order bits of the multiplex address are bussed to each module controller in a daisy chain. The controllers then decode these lines to generate enabling terms which permit the controller to load commands and output binary and analog data. These low true multiplex address terms are called sub-mux address

6-1

and are labeled SMA-0 ("1"), SMA-1 ("2"), SMA-3 ("4") and SMA-3 ("8") on the wire lists and logic diagrams.

All logic lines to a device controller are low true and should not burden the Data Set with more than one standard TTL load. The binary monitor data output gate should be an open collector gate as the binary monitor data lines (DIGI-X) are a daisy chain with the pull-up resistor in the Data Set.

The command portion of the controller consists of a serially loaded shift register, enabled by the decoded multiplex address. At the completion of the serial load, the 24 command information bits are parallel loaded into static storage by the command strobe pulse (STRO-X). Note that the command loading samples (shifts) the command information line (DIGO-X) on the trailing (rising) edge of the clock pulse (CLKO-X). The Data Set shifts out the command information on the leading edge of the clock thus providing a large margin of settling delay.

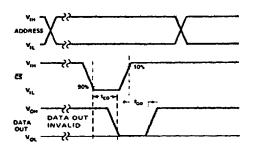

Binary monitor channels operate in a similar manner but the information flow is reversed. Again the decoded multiplex address enables the logic operations. A strobe (STRI-X) pulse causes the data loading register to parallel load 24 discrete logic level lines. Then a 24 pulse shift clock from the Data Set causes the information to be serially loaded into the Data Set. The data loading, register shifts on the trailing edge of the clock (CLKI-X) pulses while the Data Set samples the data on the leading edges.

The analog multiplexer is driven by the sub-mux lines and may operate in either single-ended or differential mode. The differential mode is preferred in cases where there is more than a few millivolts of common mode signal impressed upon the data. By tying the multiplexer low sides to the common mode sources (there may be more than one), the differential amplifier in the Data Set is able to "buck" out the common mode signal to provide a more accurate conversion of the analog signal.

6-2

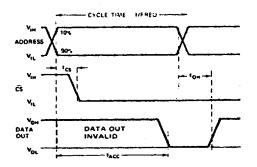

Timing Diagrams 8, 9 and 10 illustrate the time relationships of the sub-mux address, command, binary and analog signals.

The generalized controller logic schematics shown here are obviously not the only implementation possible (many other arrangements are possible) but they illustrate the interfacing techniques to be used with the Data Set.

\* ANOTHER 8 CHANNEL DIFFERENTIAL MULTIPLEXER MAY BE ADDED OR 16 CHANNEL SINGLED MULTIPLEXERS SUBSTITUTED IF COMMON MODE VOLTAGES ARE LOW.

FIGURE 3: TYPICAL MODULE CONTROLLER LOGIC DIAGRAM

★ - THIS GATE MUST HAVE AN OPEN COLLECTOR AS THE DIGI-X LINE IS A PARTY LINE WITH THE PULL-UP RESISTOR IN THE DATA SET.

S = CONTROLLER SAMPLES (ie. LOADS SHIFT REG.) CMD INFO. AT THIS POINT

TIMING DIAGRAM 8 - CONTROLLER COMMAND LOAD TIMING

S ⇒ DATA SET SAMPLES DATA AT THIS POINT

\* THERE ARE 3 PAUSES IN CLKI-X AT 9 BIT INTERVALS TO PERMIT DATA SET TO MERGE PARITY DATA INTO MONITOR DATA WAVEFORM.

TIMING DIAGRAM 9: CONTROLLER BINARY MONITOR DATA UNLOAD TIMING

#### 7.0 DATA SET DOCUMENTATION

Figure 9 is the Revision "D" Data Set documentation file and relates all the Data Set drawings in the assembly hierarchy.

TOP ASSEMBLY DRAWING - D13720P73 TOP BILL OF MATERIAL - A13720Z99

| LED DISPLAY<br>SUB ASS'Y. | A/D CONVERTER<br>SUB ASS'Y. | IC MODULE<br>PANEL     | MECHANICAL<br>PARTS           | MASTER W<br>LIST<br>A13720W | DIAGRAMS          |

|---------------------------|-----------------------------|------------------------|-------------------------------|-----------------------------|-------------------|

| Ass'y Dwg C13720P38       | Ass'd Dwg D13720P58         | Ass'y Dwg Cl3720P57    | Front Panel, Engrvd Bl3720M22 |                             |                   |

| BOM - A13720Z83           | BOM - A13720Z85             | Ass'y BOM - A13720Z84  | Filter, Red Pol B13720M18-1   |                             |                   |

| Drill Dwg Cl3720M33       | Drill Dwg D13720M45         |                        | Filter, Clr - B13720M18-2     |                             |                   |

| Artwork Dwg B13720AB36    | Artwork Dwg D13720AB11      |                        | Rail Modified - Cl3720Ml5-1   |                             |                   |

|                           |                             |                        | Rail Modified - Cl3720Ml5-2   |                             |                   |

|                           |                             |                        | Rear Panel - Bl3450M32        |                             |                   |

|                           |                             |                        | Guide Blocks - Bl3050M4       |                             |                   |

|                           |                             |                        | Perf Cover - Cl3050M7         |                             |                   |

|                           |                             |                        | Side Plate - Cl3720M50        |                             |                   |

|                           |                             |                        | Bracket, Conn B13720M46       |                             |                   |

|                           |                             |                        | Spacer - B13720M47            |                             |                   |

|                           |                             |                        | Side Plate Insul B13720M49    |                             |                   |

|                           |                             | DIP HEADER SUB ASS'YS. |                               |                             |                   |

|                           |                             | Ass'y Dwg Ass'y BOM    | F                             |                             | 1                 |

|                           |                             | A13720P62 - A13720Z89  | HAND WIRE MACHINE CO          | NNECTOR                     | POWER             |

|                           |                             | A13720P63 - A13720Z90  |                               | O LIST                      | WIRING<br>DIAGRAM |

|                           |                             | A13720P60 - A13720Z87  | A13720W62 A13720W63 A1        | .3720W64 D                  | 13720L44, SH7     |

|                           |                             | A13720P59 - A13720Z86  |                               |                             |                   |

|                           |                             | A13720P6 - A13720Z88   |                               |                             |                   |

|                           |                             | B13720P16 - A13720Z39  |                               |                             |                   |

|                           |                             | B13720P17 - A13720Z9   |                               |                             |                   |

|                           |                             | A13720P69 - A13720Z95  |                               |                             |                   |

|                           |                             | B13720P14 - A13720Z10  |                               |                             |                   |

### 8.0 I/O SIGNAL PIN ASSIGNMENTS

Figure 5 shows the Data Set vital, address and signal I/O pin assignments. Figure 6 shows the command/data channel I/O pin assignments.

| VITAL INPUTS         | ADDRESS INPU  | TS             | SIGNA     | L INPUTS | SIGNAL OUTPUTS             |

|----------------------|---------------|----------------|-----------|----------|----------------------------|

| +5 V Logic Pwr J4-10 | Anta-4 ("16") | J4-18          | CMD Inp-H | II J4-25 | CMD/Data to DT, HI - J4-8  |

| 5 V Common J4-34     | Anta-3 ("8")  | J4-24          | CMD Inp-R | et J4-26 | CMD/Data to DT,Ret - J4-9  |

| +15 V Pwr J4-16      | Anta-2 ("4")  | J <b>4-</b> 20 |           |          | Data to Buffer,HI - J4-15  |

| -15 V Pwr J4-17      | Anta-1 ("2")  | J4-13          |           |          | Data to Buffer,Ret - J4-27 |

| Analog Gnd J4-42     | Anta-0 ("1")  | J4-2           |           |          |                            |

| 5 MHz-HI J3-MM       | DSA-2 ("4")   | J4-29          |           |          |                            |

| 5 MHz-Ret J3-NN      | DSA-1 ("2")   | J4-28          |           |          |                            |

|                      | DSA-0 ("1")   | J4-11          |           |          |                            |

FIGURE 5: DATA SET VITAL, ADDRESS AND SIGNAL I/O PIN ASSIGNMENTS

|           |                                    |                                    |                                    |                                    |                 | ALGI-X  |             |     | SUB-MUX |                    |

|-----------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------|---------|-------------|-----|---------|--------------------|

| DIGI/O    | #O                                 | #1                                 | #2                                 | #3                                 | 008             | ALGI-0+ | J4-14       | "I" | SMA-0   | J 3-EE             |

| ADDR8     | 200 <sub>8</sub> -217 <sub>8</sub> | 220 <sub>8</sub> -237 <sub>8</sub> | 240 <sub>8</sub> -251              | 260 <sub>8</sub> -277 <sub>8</sub> |                 | ALGI-0- | J4-32       | ±   | SMA-02  | J3-CC              |

| Signal    | < J3-34                            | Pin ——>                            | <──J4-42                           | Pin>                               |                 | -       |             |     | •       |                    |

| DIGIX     | J3-B                               | J3-R                               | J4-01                              | J4-19                              | ſ               | ALGI-1+ | J4-33       |     | SMA-1   | <b>Ј3-</b> КК      |

| DIGIX RET | J3-D                               | J3-T                               | J4-04                              | J4-22                              | 208             |         |             | "2" |         |                    |

| CLKIX     | J3-F                               | J3-V                               | J4-03                              | J4-21                              | l               | ALGI-1- | J4-41       |     | SMA-1R  | J3-HH              |

| CLKIX RET | J3-J                               | J3-X                               |                                    |                                    |                 |         |             |     | Cours   | *1 00              |

| STRIX     | J3-L                               | J3-2                               | J4-12                              | J4-23                              | 40 <sub>8</sub> | ALGI-2  | J4-7        | "4" | SMA-2   | J3-DD              |

| STRIX RET | J3-N                               | J3-BB                              |                                    | ***                                |                 |         |             |     | SMA-2R  | J3-FF              |

| ADDR 8    | 320 <sub>8</sub> -337 <sub>8</sub> | 340 <sub>8</sub> -357 <sub>8</sub> | 360 <sub>8</sub> -377 <sub>8</sub> |                                    | 60 <sub>8</sub> | ALGI-3  | J4-40       |     |         |                    |

| DIGOX     | J3-C                               | J3-S                               | J4-35                              |                                    |                 |         | - · •       | "8" | SMA-3   | J3-JJ              |

| DIGOX RET | J3-A                               | J3-P                               | J4-36                              |                                    | 1008            | ALGI-4  | J4-6        | 8   | SMA- 3R | J3-LL              |

| CLKOX     | J3-H                               | J3-W                               | J4-37                              |                                    |                 |         | - 4 - 9 - 9 |     | •       | $\hat{\mathbf{T}}$ |

| CLKOX RET | J3-E                               | J3-U                               |                                    |                                    | 1208            | ALGI-5  | J4-39       |     |         | J3                 |

| STROX     | J3-M                               | J3-AA                              | J4-30                              |                                    |                 |         | - 4 - 5     |     |         | 50                 |

| STROX RET | J3-K                               | J3-Y,                              |                                    |                                    | 1408            | ALGI-6  | J4-5        |     |         |                    |

|           | J3                                 |                                    | J                                  | 4                                  | 160             | NF.07 7 | 74 20       |     |         |                    |

|           |                                    |                                    |                                    |                                    | 1008            | ALGI-7  | J4-38       |     |         |                    |

|           |                                    |                                    |                                    |                                    |                 |         | Î           |     |         |                    |

|           |                                    |                                    |                                    |                                    |                 |         | J4          |     |         |                    |

FIGURE 6: COMMAND/DATA CHANNEL I/O PIN ASSIGNMENTS

#### 9.0 SPECIAL MODULE DATA SHEETS

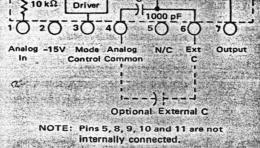

Four special purpose modules are used in the Data Set. These are:

- 1. A/D Converter Datel K12BE

- 2. Analog Multiplexer Datel MMD-8

- 3. Sample and Hold Burr-Brown SHC-85

- 4. PROM Intel 1702A

All four of these items are contained on the Analog Multiplexer -A/D Converter PC board and are removeable for replacement. The PROM is installed on the A/D board because of its 24 pin physique which would be awkward to mount anywhere else in the Data Set. The PROM address programs are particularized for the data sampling requirements of each application so be sure the appropriate PROM is installed before you leave for an antenna with a Data Set under your arm. Be sure to use a PROM carrier when installing a PROM as the chip leads are very delicate and PROM's are very expensive.

Data Sheets for these four modules are bound in the next few pages.

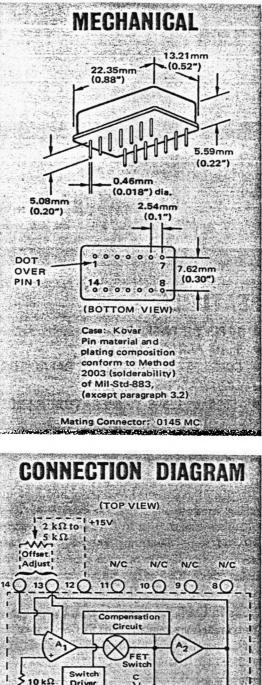

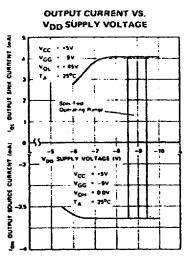

The A/D Converter data sheet shows only a  $\pm 5$  volt input signal range. The A/D Converter used by the Data Set is a specially ordered version which has an input signal range of  $\pm 10$  volts (actually  $\pm 10.235$  to -10.240 or 5 MV/bit).

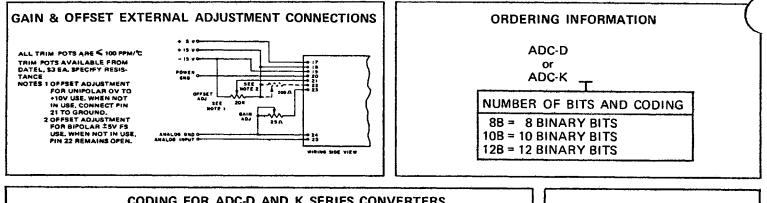

The A/D is configured for bipolar operation and uses the offset adjustment configuration of Note 2 on the data sheet.

The A/D converter output code for bipolar operation is Offset Binary as shown on the data sheet. Inverter D2512 on the MSB transforms the code to 2's complement format as shown below:

| Analog Input                           | 2's Complement Code     |

|----------------------------------------|-------------------------|

| +10.235, +FS                           | 011111111111            |

| +10.230, +FS-1 bit                     | 011111111110            |

| +5.000, + <sup>1</sup> <sub>2</sub> FS | 001111100111            |

| +0.005, CS+1 bit                       | 0 0 0 0 0 0 0 0 0 0 0 1 |

| 0.000, CS                              | 0 0 0 0 0 0 0 0 0 0 0 0 |

| -0.005, CS-1 bit                       | 11111111111             |

| $-5.000, -\frac{1}{2}FS$               | 101111100111            |

| -10.235, -FS+1 bit                     | 100000000001            |

| -10.240, -FS                           | 10000000000000          |

RAULESSENTLE SER H 1 Test Structures - A

H. J. 1997 (20) (20, 21 (20), 1123 (No. 1998) (20), Articratic National Values, 1763 (20), 2007 (20), 55

#### **GENERAL DESCRIPTION**

Modern accuracy, medium conversion speed and relatively low cost is the theme behind the ADC-D and K Series Both use the successive approximation conversion technique. This encoding method is the most popular of all the A/D conversion techniques because it offers a favorable combination of a full monotonic conversion with excellent linearity over the full scale input range.

ADC-D and K series have total conversion speeds of 10 KHz (100  $\mu$ sec) and 20 KHz (50  $\mu$ sec) respectively. Voltage input can be unipolar (0 to +10V) or bipolar (±5V) by external pin strapping. Output coding can be straight binary, offset binary or two's complement with word lengths of 8, 10 and 12 binary bits.

Specified accuracy is ±0.05% for ADC-D series and ±0.025% for ADC-K series. Model ADC-D and ADC-K feature 50 ppm/°C and 30 <code>>pm/°C</code> temperature coefficients respectively nd need not be adjusted over an operating tem-perature range of 0° to +70°C. Digital outputs include up to 12 parallel lines, serial output and an end of conversion status.

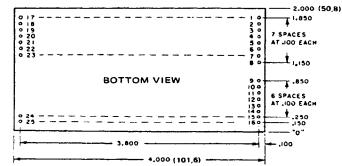

Overall dimensions are  $2''W \times 4''L \times 0.4''H$ . Input power requirements are  $\pm 15VDC$  and  $\pm 5VDC$  and all input control lines and digital outputs are DTL/TTL compatible.

Basic ingredients of each series is a temperature compensated voltage reference source, successive approximation logic, output storage register/programmer, a low noise voltage comparator and a precision digital to analog converter.

All models feature dual-in-line pinning compatibility on .100" grid pin spacing.

# ANALOG-TO-DIGITAL CONVERTERS ADC-D SERIES ADC-K SERIES

# MODERATE ACCURACY AND SPEED AT LOW COST PRICED FROM \$79.00

#### FEATURES

# MECHANICAL DIMENSIONS INCHES (MM)

### INPUT/OUTPUT CONNECTIONS

| PIN | FUNCTION         | PIN | FUNCTION          | ]            |

|-----|------------------|-----|-------------------|--------------|

| ſ   | E.O.C. (STATUS)  | 17  | + SY DC POWER IN  | 1            |

| 2   | MSB OUTPUT       | 18  | +ISVDC POWER IN   | 1            |

| 3   | START CONVERT    | 19  | - IS VOC POWER IN | 1            |

| 4   | SERIAL OUTPUT    | 20  | POWER GROUND      | 1            |

| 5   | BIT I OUT (MSB)  | 21  | OFFSET (NOTE 1)   | SEE NOTES    |

| 6   | 81T 2 OUT        | 22  | OFFSET (NOTE 2)   | ) ON REVERSE |

| 7   | BIT 3 OUT        | 23  | GAIN ADJUST       | SIDE         |

| 8   | BIT 4 OUT        | 24  | ANALOG GND        |              |

| 9   | BIT 5 OUT        | 25  | ANALOG INPUT      | 1            |

| 10  | BIT & OUT        |     |                   |              |

| "   | BIT 7 OUT        |     |                   |              |

| 12  | BIT 8 OUT        |     |                   |              |

| 13  | BIT 9 OUT        |     |                   |              |

| 14  | BIT IO OUT       |     |                   |              |

| 15  | BIT II OUT       |     |                   |              |

| 16  | BIT 12 OUT (LSB) |     |                   |              |

#### SPECIFICATIONS (typical @ 25°C unless otherwise noted)

|                              |                                                                                                                       | Performance:                   |                                                                                                                                                          |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ELECTRICAL<br>Inputs:        |                                                                                                                       | Resolution                     | One part in 2 <sup>n</sup> (max. resolution<br>12 binary bits or 3 digit BCD).<br>(n≈ number of binary bits).                                            |

| Analog input voltage range . | . Standard ranges of QV to +10V<br>FS, ±5V FS via ext. pin strapping.                                                 | Accuracy (@25°C)               | ADC-D Series                                                                                                                                             |

| Input Overvoltage            | ±15V DC without damage of unit.                                                                                       |                                | 8 Binary Bits - $\pm 0.05\%$ of FS $\pm \%$ LSB<br>10 Binary Bits - $\pm 0.05\%$ of FS $\pm \%$ LSB<br>12 Binary Bits - $\pm 0.025\%$ of FS $\pm \%$ LSB |

| input Impedance              | shunted with 10 pf single-ended                                                                                       |                                | ADC-K Series                                                                                                                                             |

| Start of Conversion          | to ground.<br>2V min. to 7V max, positive<br>pulse with duration of 100 nsec<br>min. 500 nsec max rise and fall times |                                | 8 Binary Bits<br>10 Binary Bits<br>12 Binary Bits                                                                                                        |

|                              | "1" resets the converter,<br>"0" initiates conversion.                                                                | Temperature Coefficient        | ±50 ppm/°C ADC-D Series<br>±30 ppm/°C ADC-K Series                                                                                                       |

|                              | Loading of one TTL load.                                                                                              | Total Conversion Time          | 50 μsec                                                                                                                                                  |

| Outputs:                     | -                                                                                                                     | Input Power Requirements       | ±15VDC, ±0.5VDC @ ±35 ma<br>+5VDC, ±0.5VDC @ 300 ma (3)                                                                                                  |

| Parallel output data         | Up to 12 parallel lines of data                                                                                       | PHYSICAL-ENVIRONMENT           | AL                                                                                                                                                       |

|                              | held until next conversion<br>command.                                                                                | Operating temperature          |                                                                                                                                                          |

|                              | Vout ("0") ≤ +0.4V                                                                                                    | range                          | 0°C to +70°C                                                                                                                                             |

|                              | V out ("1") ≥ +2.4V                                                                                                   | Storage temperature range      | -55°C to +85°C                                                                                                                                           |

|                              | Each output capable of driving                                                                                        | Relative Humidity              | Up to 100% Non-condensing                                                                                                                                |

|                              | up to 6 TTL loads.                                                                                                    | Size                           | 2''W x 4''L x 0.4''H                                                                                                                                     |

| Coding                       | Straight Binary (Unipolar Input)<br>Offset Binary (Bipolar Input)                                                     | Pins                           | 0.020" round gold plated<br>0.250" long min.                                                                                                             |

|                              | Two's Complement (Bipolar                                                                                             | Case Material                  | Black Diallyl Phthalate Per                                                                                                                              |

|                              | Input)                                                                                                                |                                | MIL-M-14.                                                                                                                                                |

| Serial Output                | NRZ successive decision pulse                                                                                         | Weight                         |                                                                                                                                                          |

|                              | output generated during con-<br>version, with MSB first.                                                              | Mating Socket                  | DILS-2, 2 req'd per module, \$4/pr.                                                                                                                      |

| End of Conversion            | Conversion Status Signal                                                                                              | Model ADC-D and K Series A     | VD converter modules are fully                                                                                                                           |