VLA Technical Report No 58 THE DATA SET, MODULE TYPE M1

> D. W. Weber 8/22/86

## TABLE OF CONTENTS

TABLE OF ILLUSTRATIONS AND MAJOR DRAWINGS

## 1.0 INTRODUCTION

## 2.0 DATA SET DESCRIPTION

- 2.1 Message Format Description

- 2.2 I/O Signal Decsription

- 2.3 Control/Data Interface Description

- 2.4 Data Set Capacity

## 3.0 DETAILED FUNCTIONAL DESCRIPTION

- 3.1 5 Mhz Clock Detection and Doubling logic

- 3.2 Input Signal Synchronization Logic

- 3.3 Message Detection/Loading Logic

- 3.4 Command Output Logic

- 3.5 Word 1/Word 2 Mux Load Sequence Logic 3.6 Monitor Data Mux Address Formulation

- 3.7 Analog Data Gathering Sequence

- 3.8 Output Data Sequencing Logic

- 3.9 Parity Error Data Readout Logic

- 4.0 ANALOG SUBSYSTEM ALIGNMENT AND TESTS

- 4.1 Alignment Procedures for A/D Board

- 4.2 DC Common Mode

- 4.3 AC Common Mode

- 4.4 A/D Adjustment and Test

- 4.5 CMR Test

- 5.0 DATA SET DRAWING LIST

- 6.0 I/O SIGNAL PIN ASSIGNMENTS

- 7.0 SPECIAL MODULE DATA SHEETS

## FIGURES

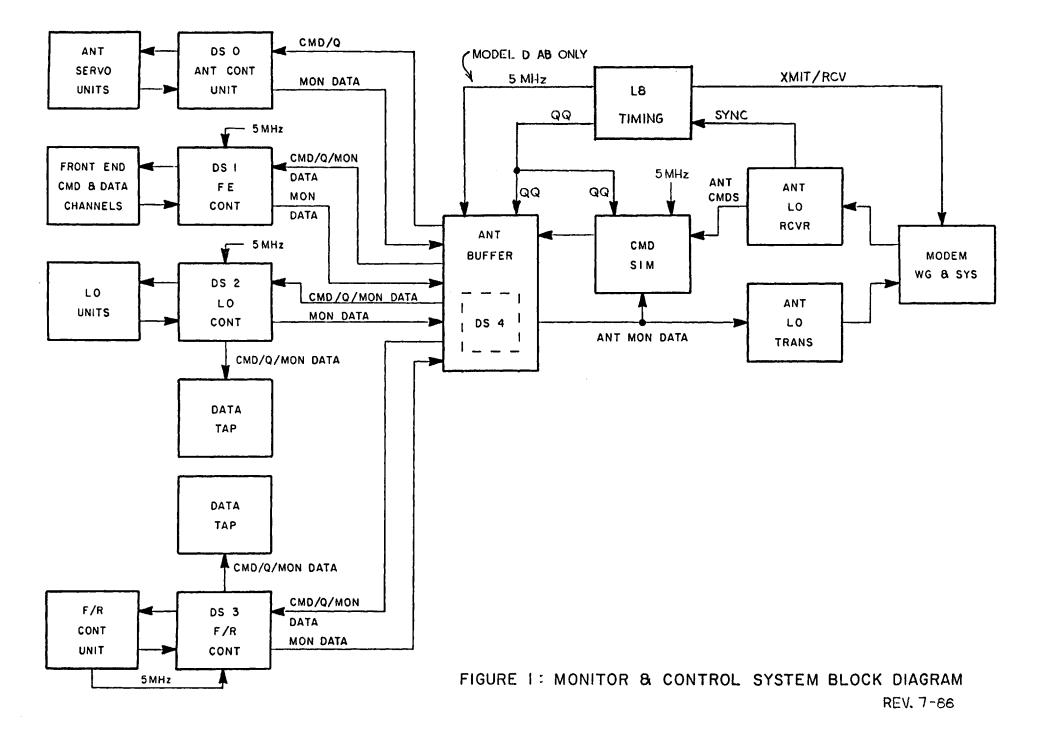

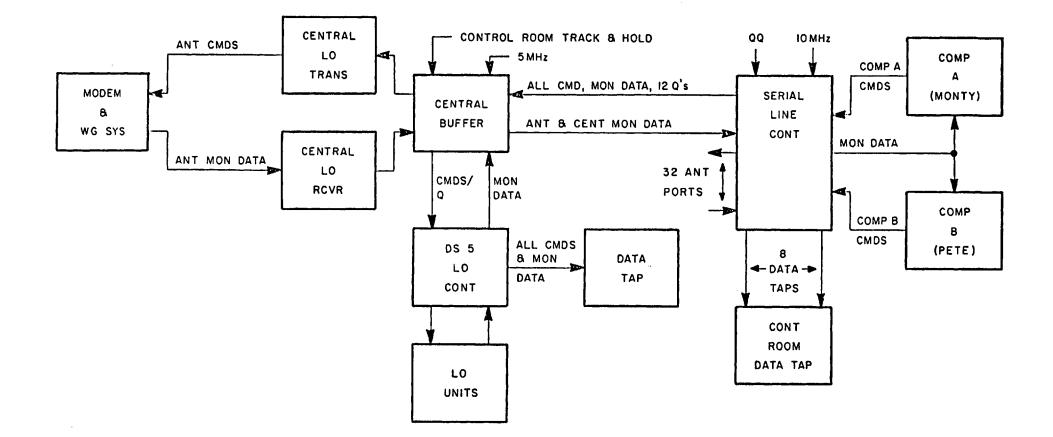

| Figure 1  | Block Diagram of the Monitor and Control System |

|-----------|-------------------------------------------------|

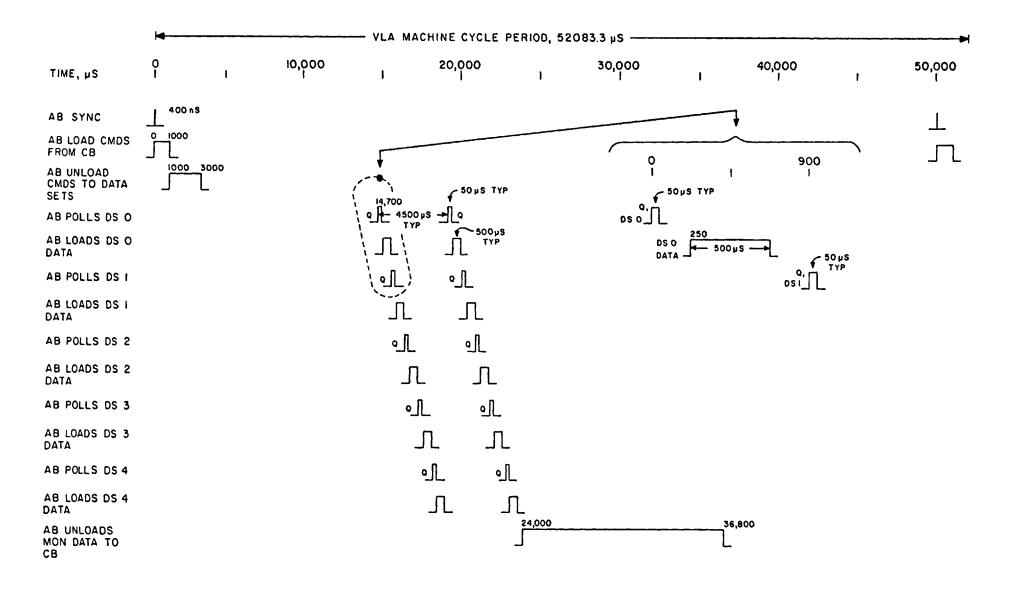

| Figure 2  | Antenna Timing Operations                       |

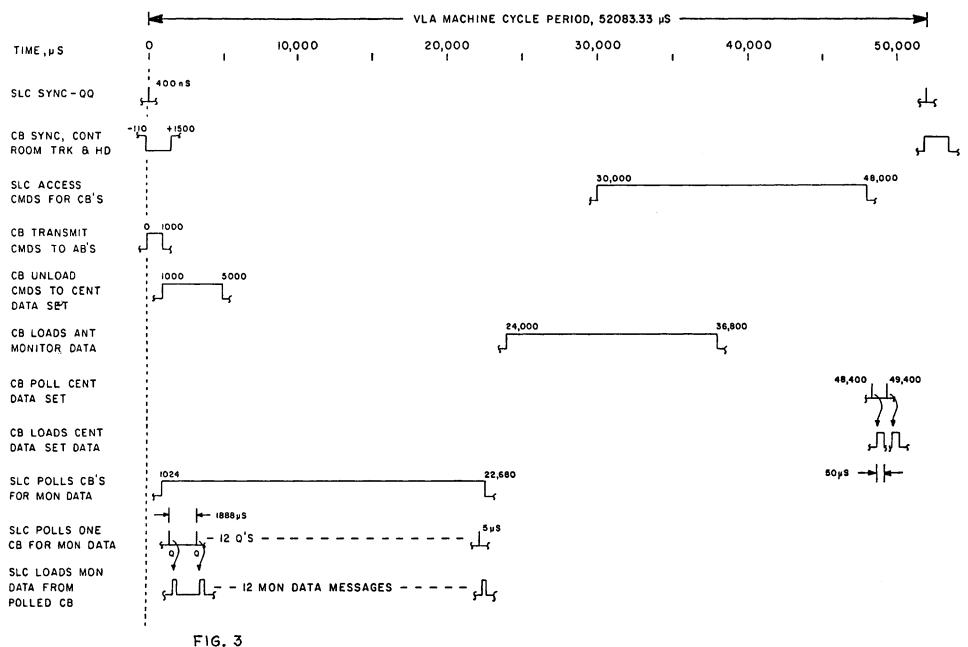

| Figure 3  | Central Timing Operations                       |

| Figure 4  | Message Format                                  |

| Figure 5  | Data Set Logic Flow Diagram                     |

| Figure 6  | Data Set Block Diagram                          |

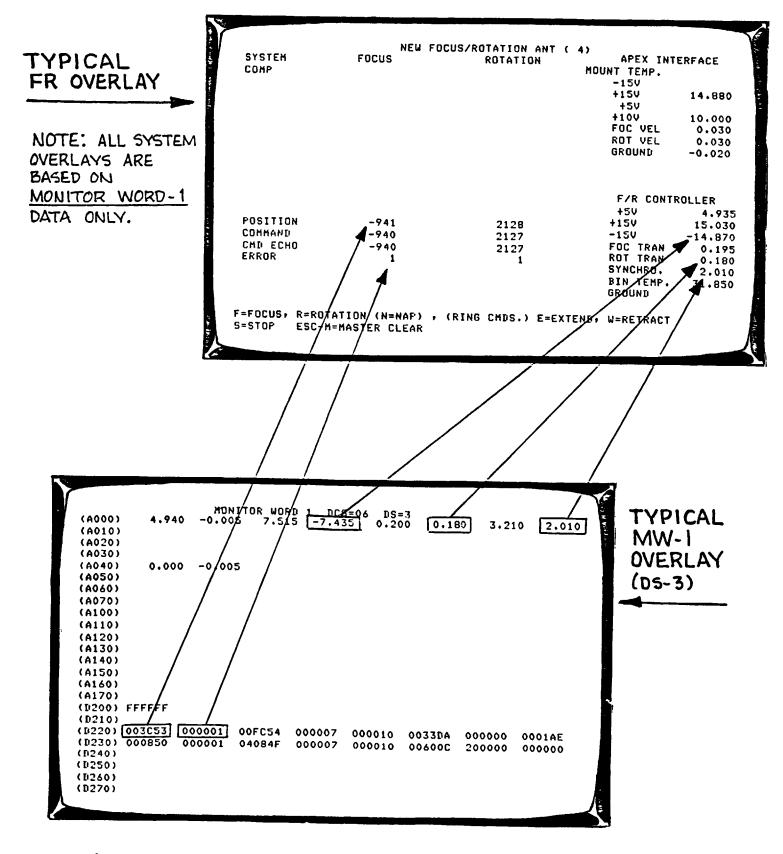

| Figure 7  | Typical MW1 – MW2 Overlay Examples              |

| Figure 8  | Data Set Testpoint (J1) Waveforms               |

| Figure 9  | Typical Control/Data Interface Logic            |

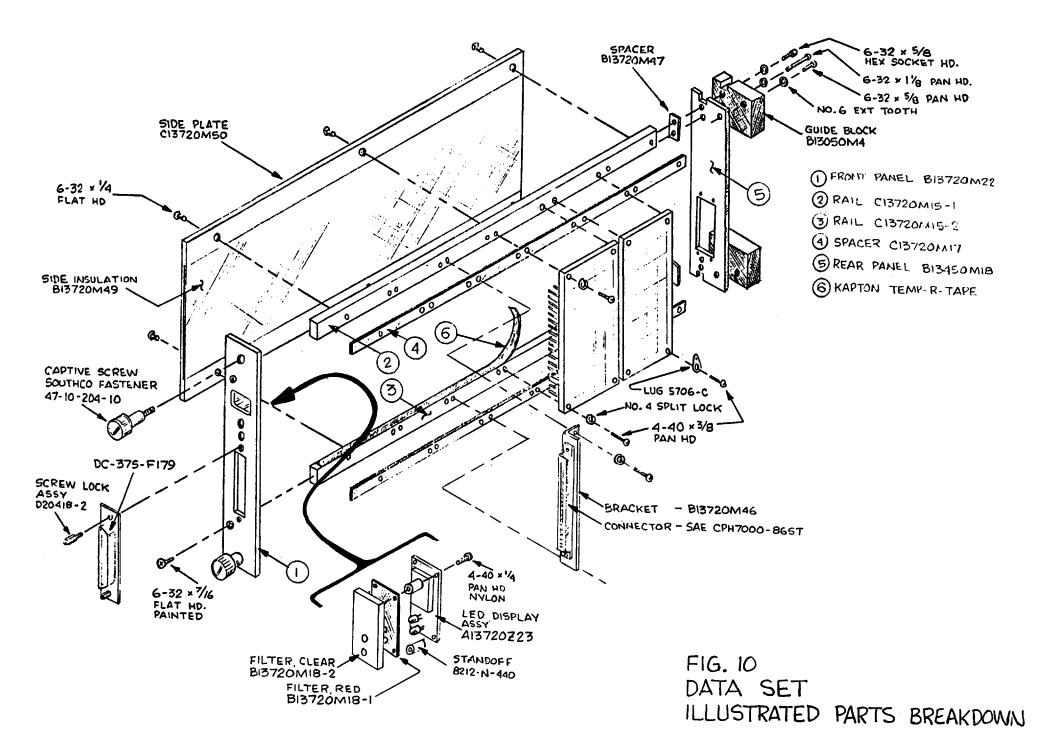

| Figure 10 | Illustrated Parts Breakdown                     |

| -         |                                                 |

## TIMING DIAGRAMS

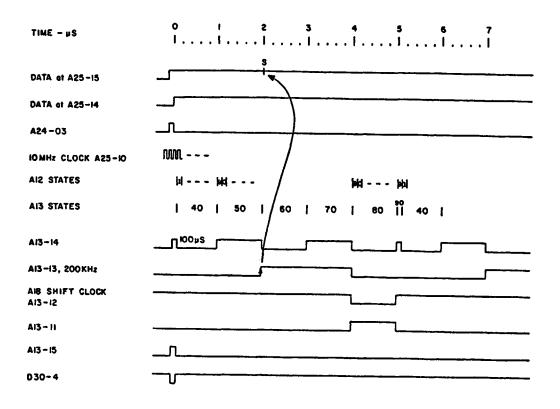

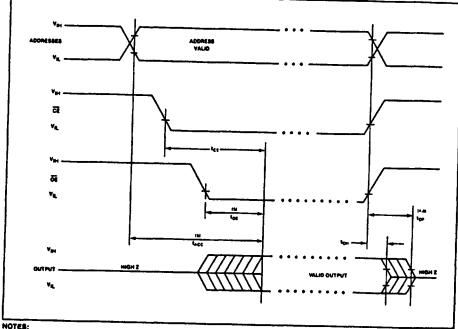

| TD | 1  | Input Signal Synchronization Timing                  |  |  |  |  |  |

|----|----|------------------------------------------------------|--|--|--|--|--|

| TD | 2  | Message Detection - Loading Timing                   |  |  |  |  |  |

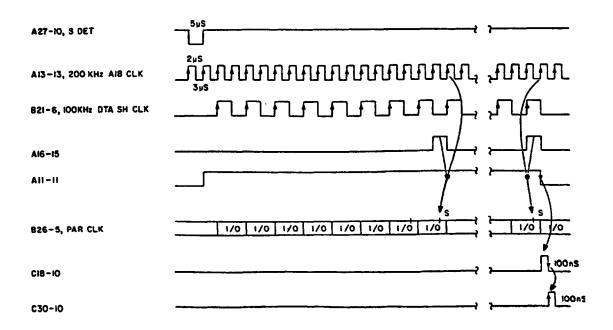

| TD | 3  | Command Output Timing                                |  |  |  |  |  |

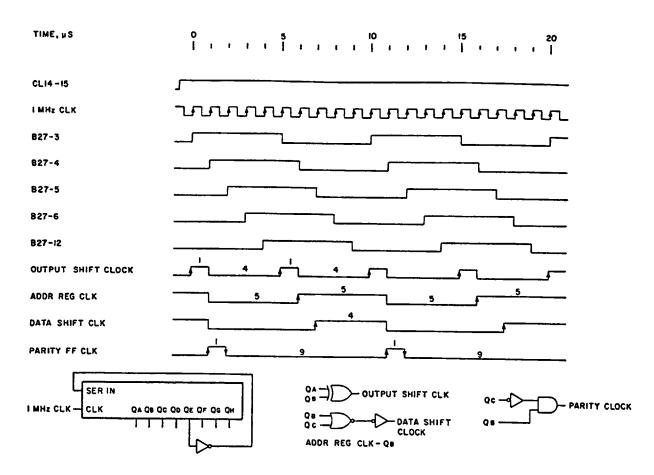

| TD | 4  | Monitor Data Multiplex Address Clock Phase Generator |  |  |  |  |  |

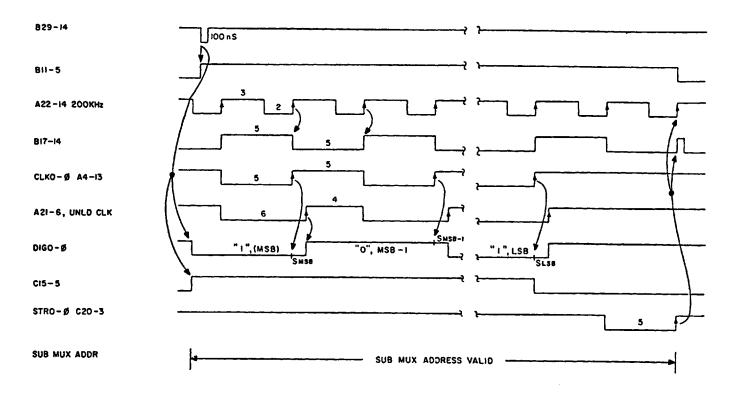

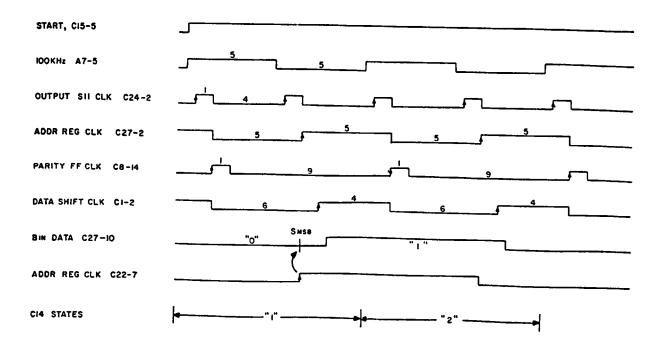

| TD | 5  | Monitor Data Output Clock Generator                  |  |  |  |  |  |

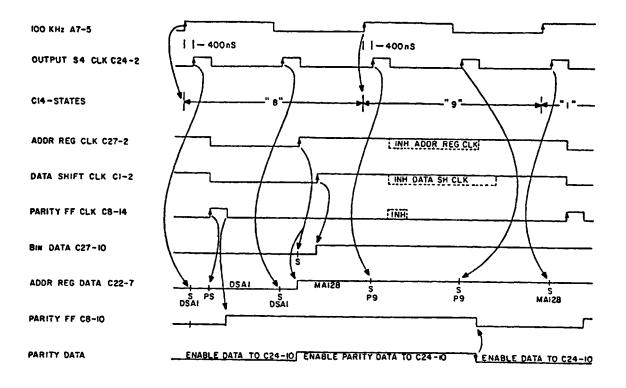

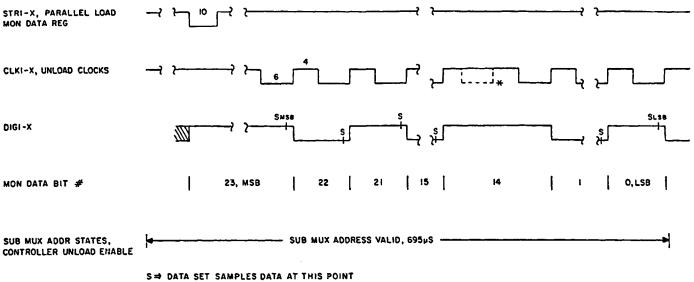

| TD | 6  | Monitor Data Output Clocking                         |  |  |  |  |  |

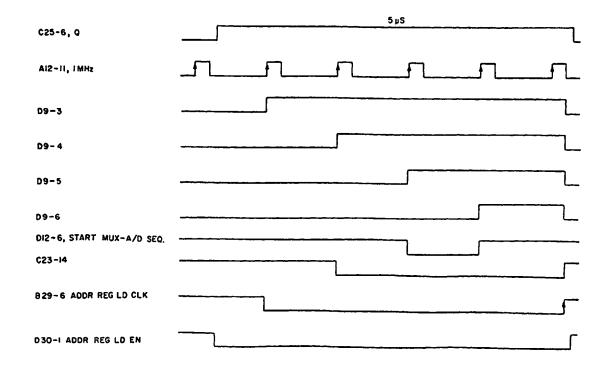

| TD | 7  | Monitor Data Output Timing, Parity Data Out          |  |  |  |  |  |

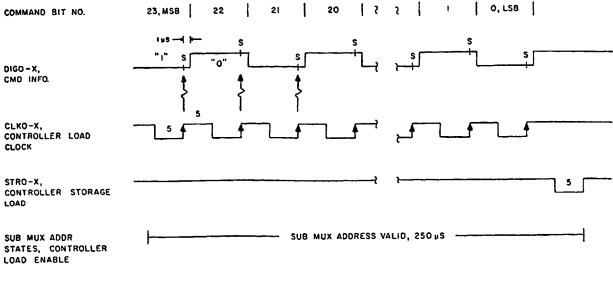

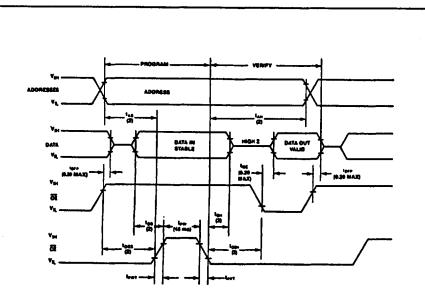

| TD | 8  | Device Interface Command Load Timing                 |  |  |  |  |  |

| TD | 9  | Device Interface Binary Monitor Data Unload Timing   |  |  |  |  |  |

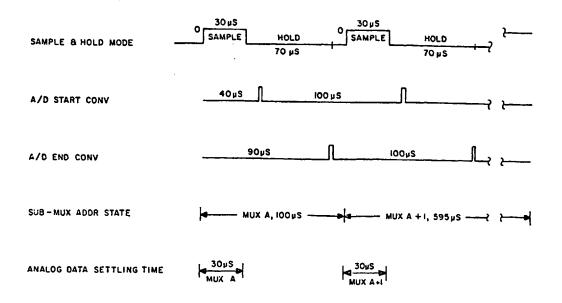

| TD | 10 | Device Interface Analog Data Timing                  |  |  |  |  |  |

MAJOR DRAWINGS

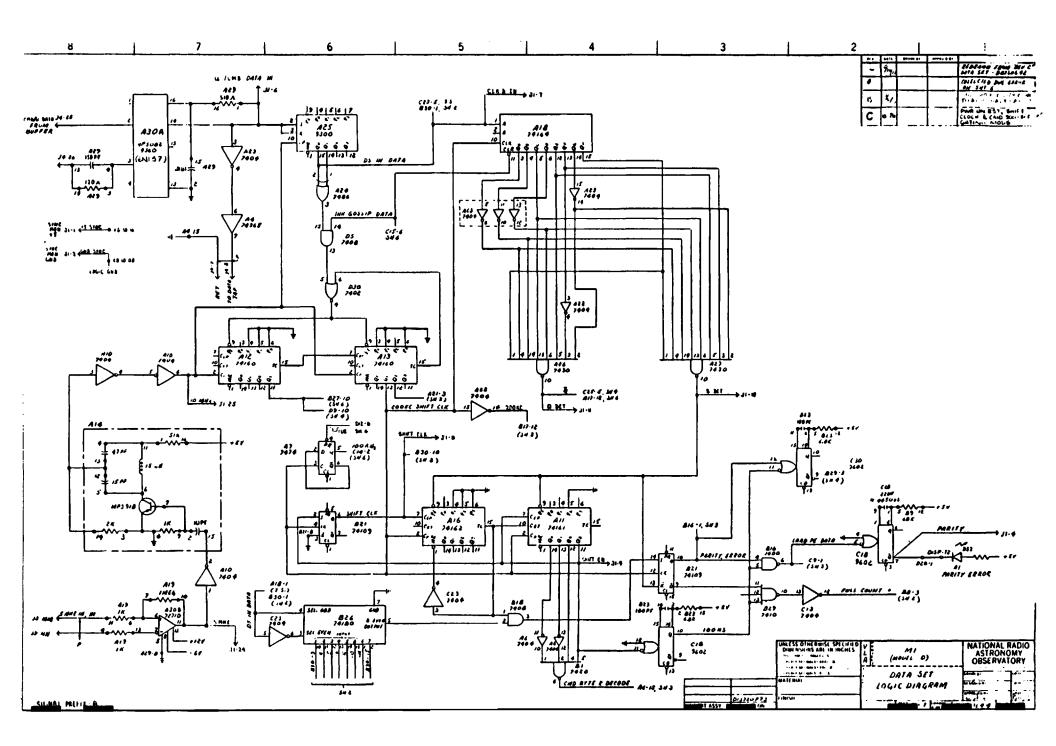

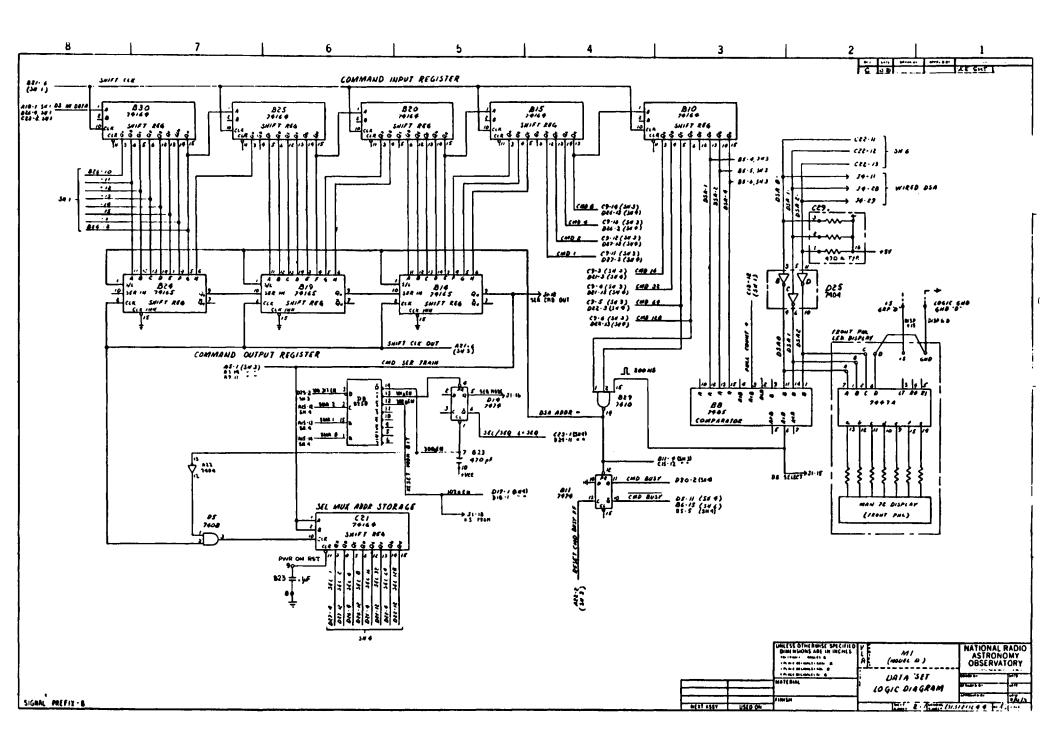

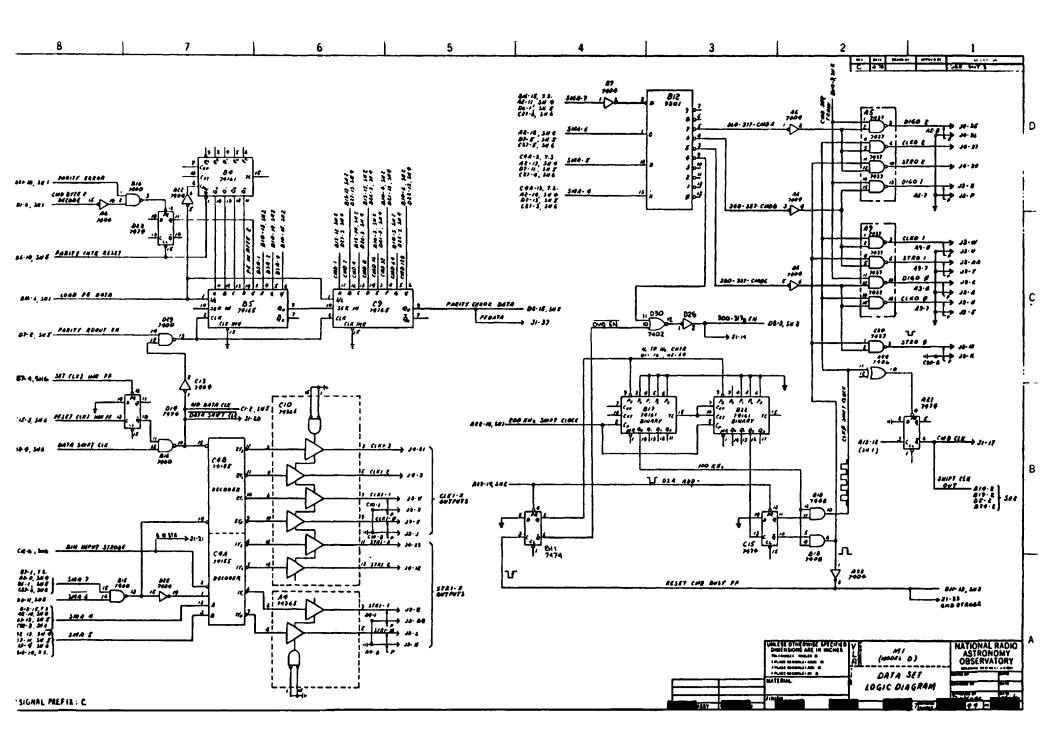

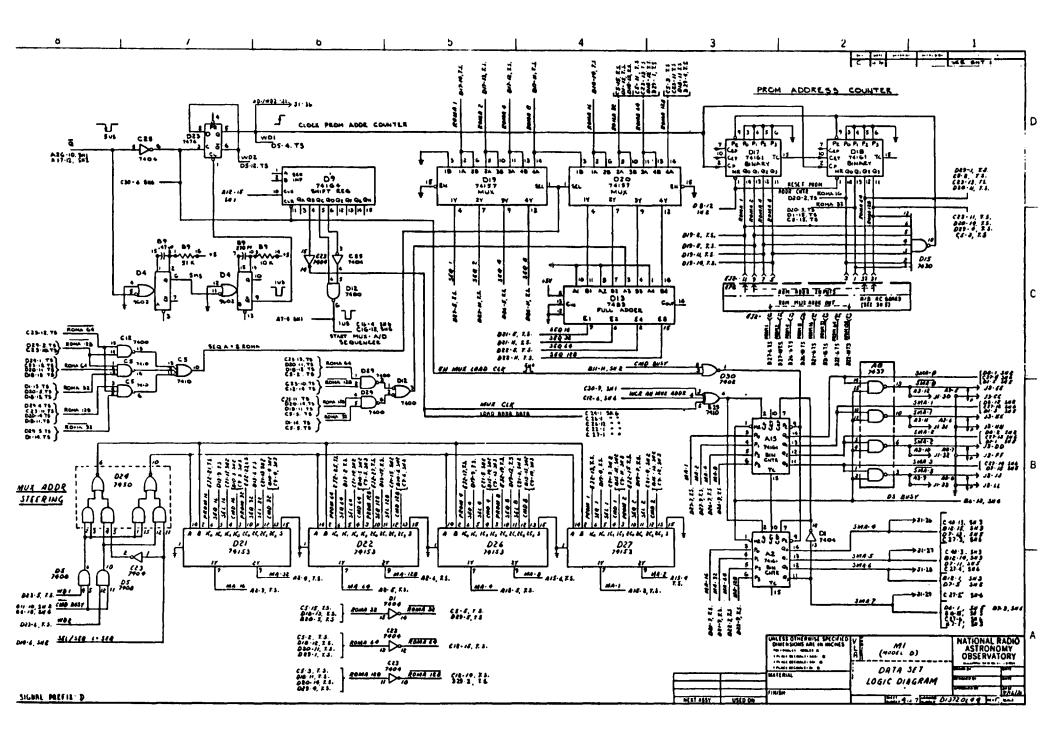

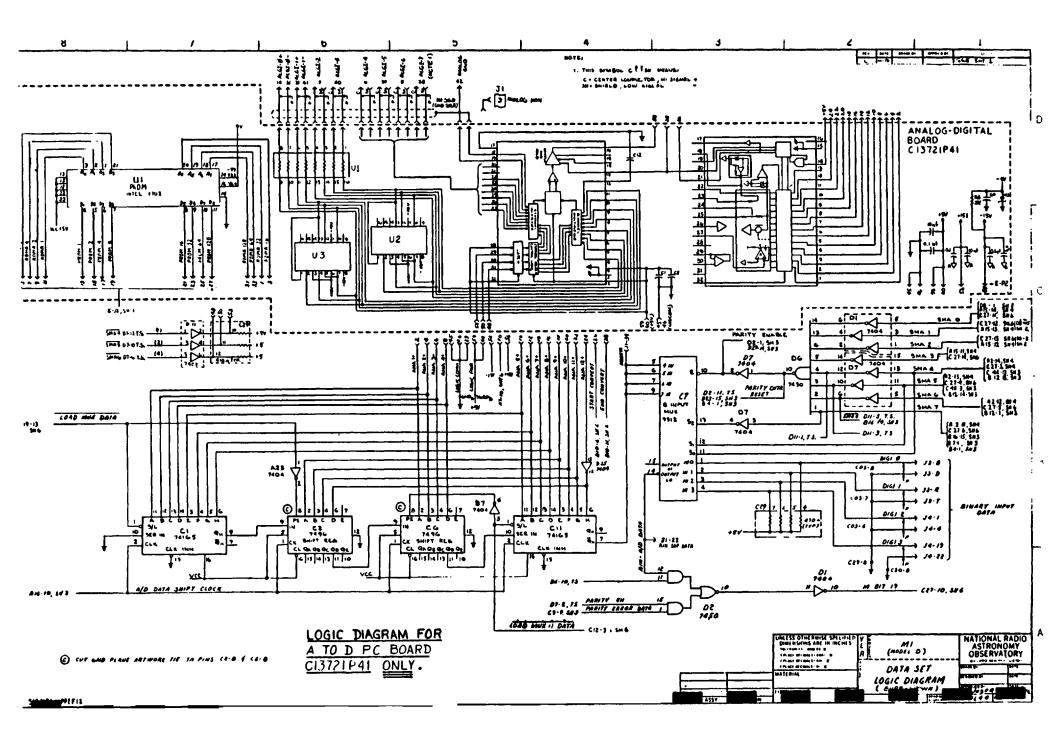

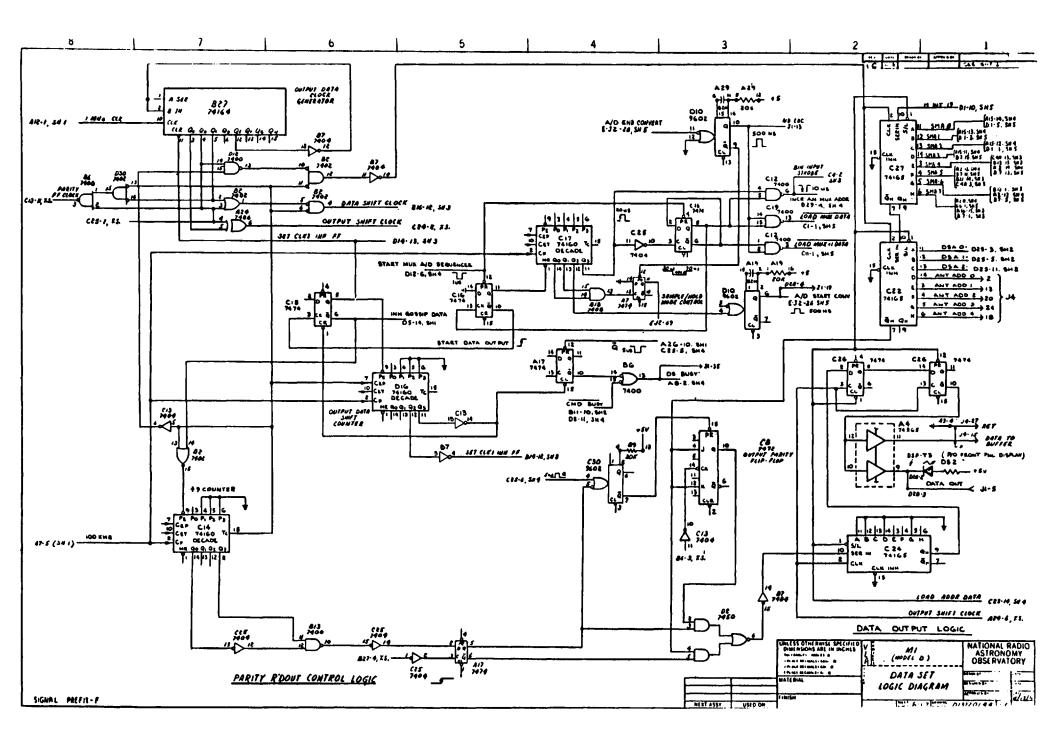

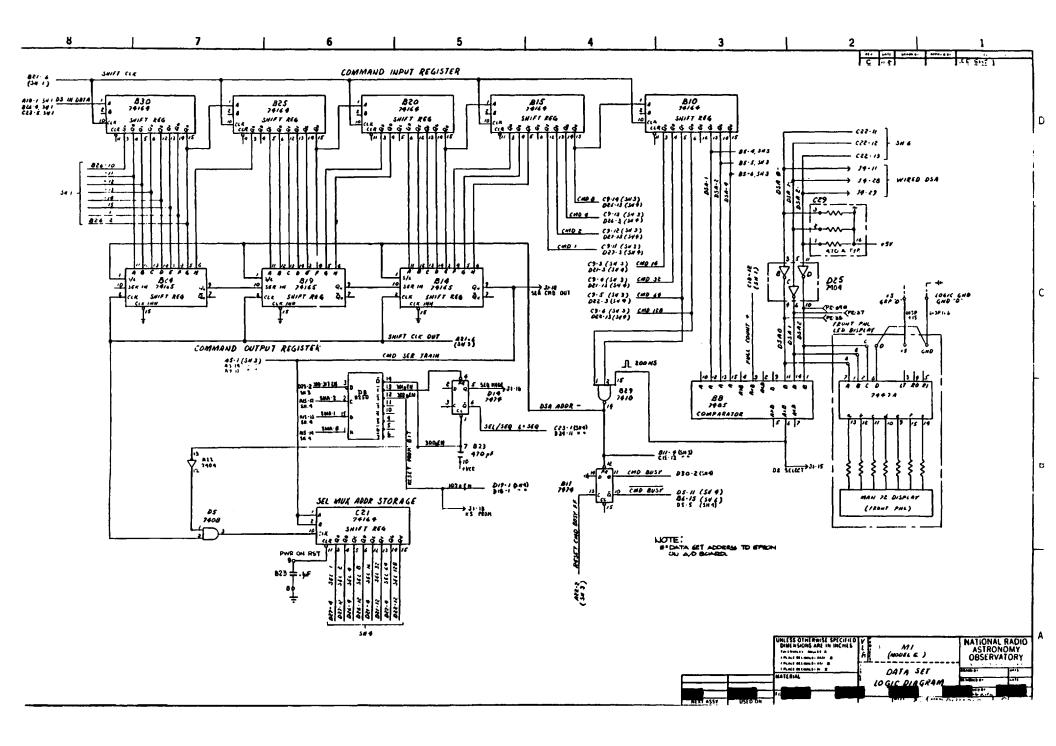

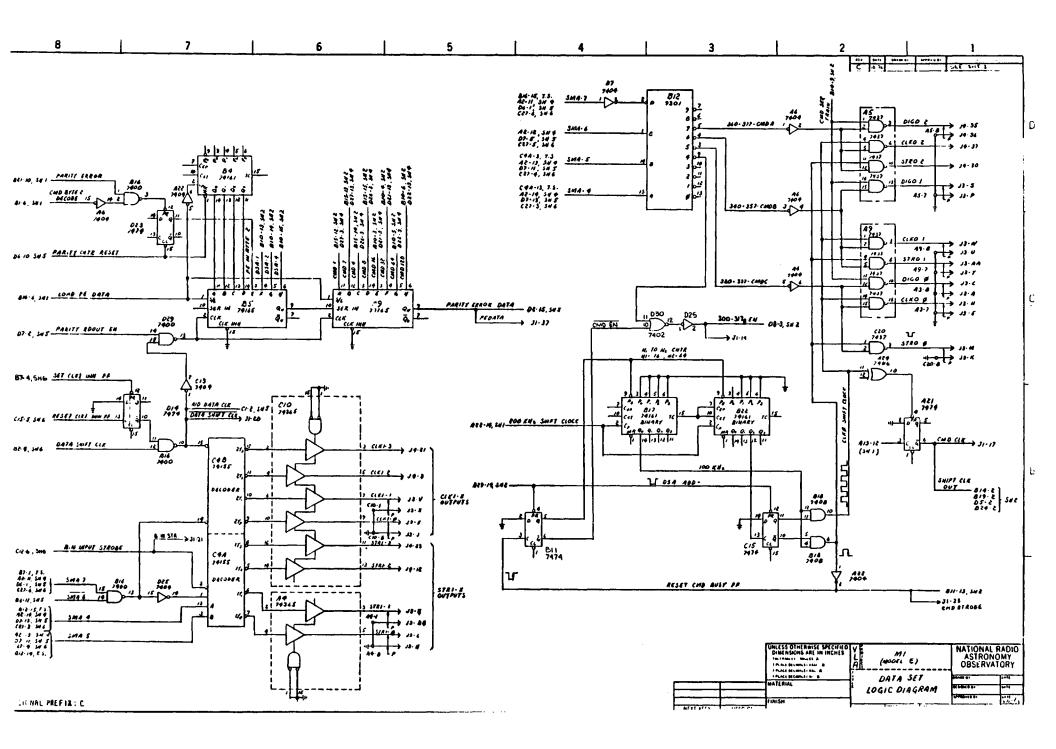

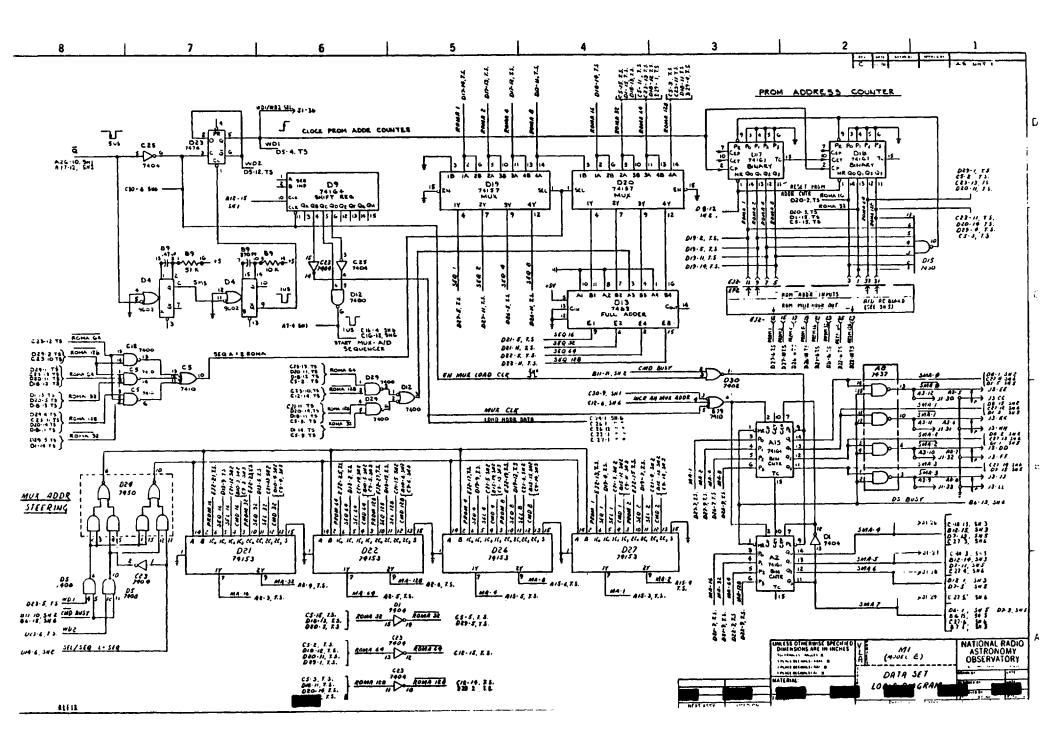

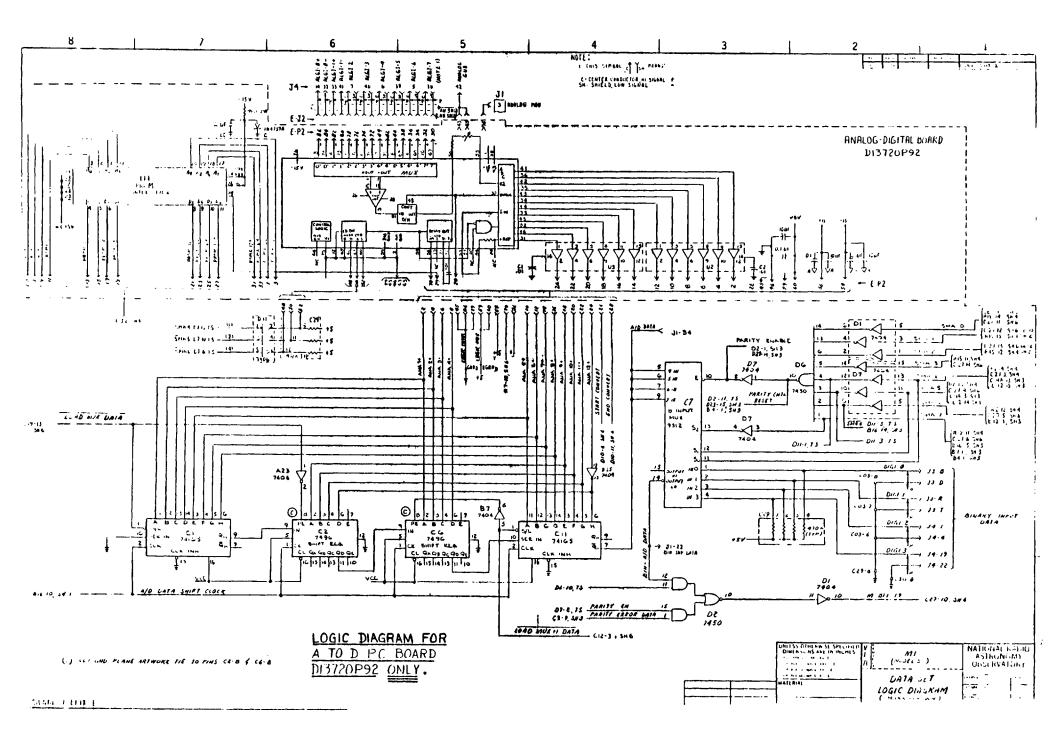

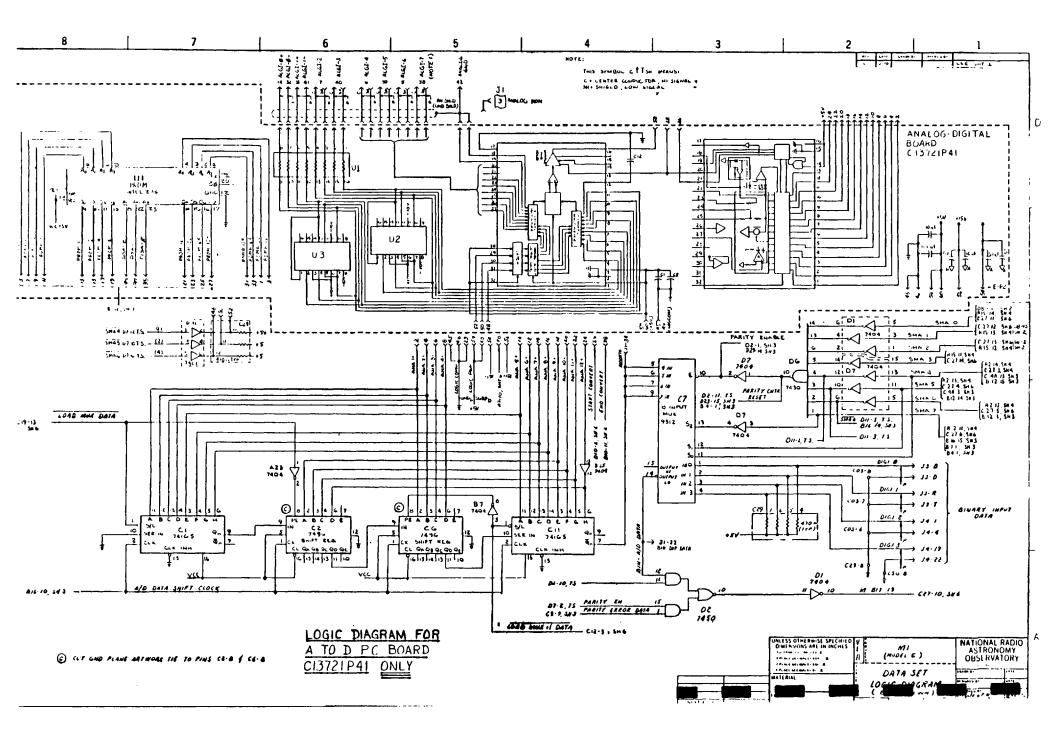

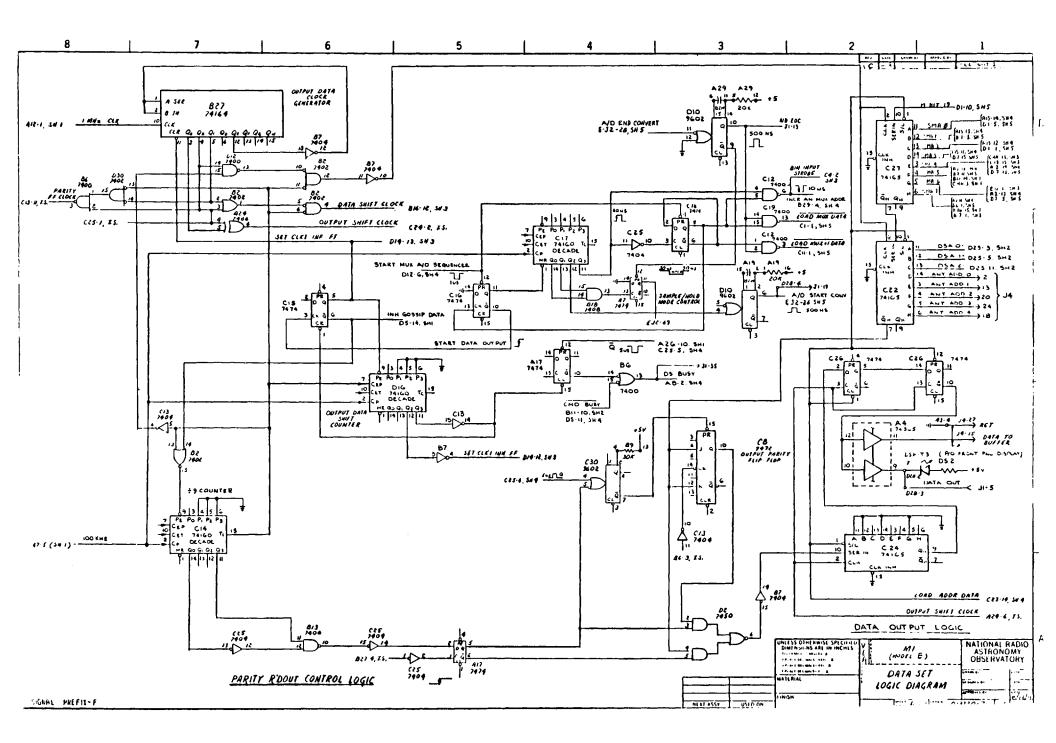

| D13720L44 | Model D Data Set Logic | Diagram |

|-----------|------------------------|---------|

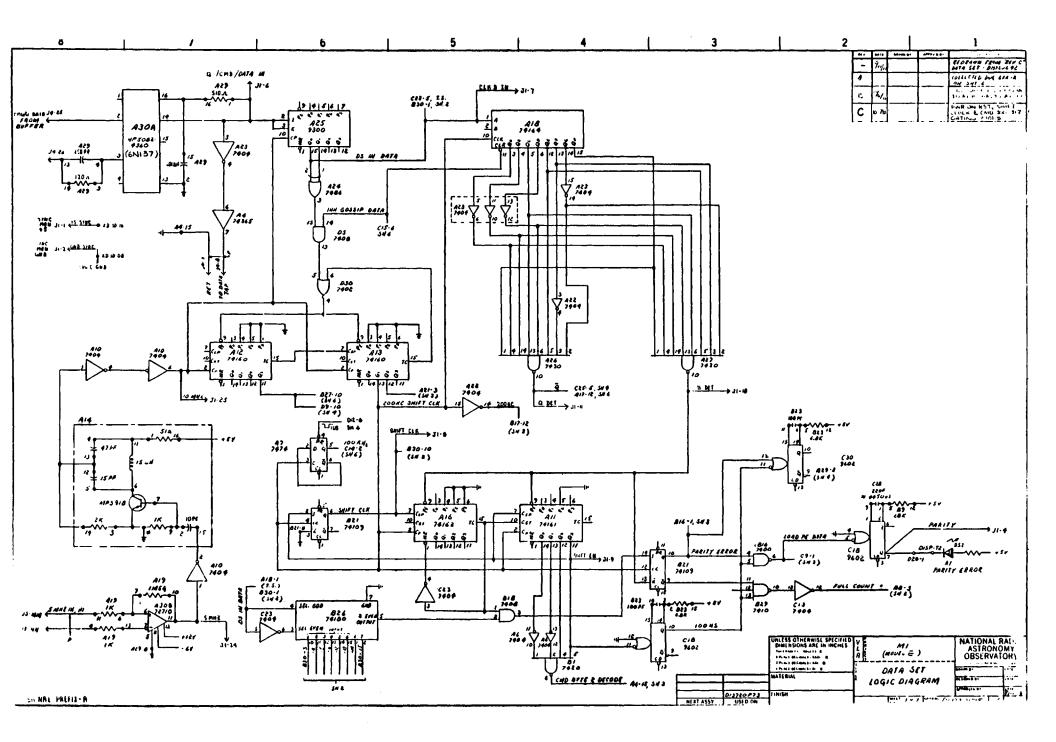

| D13720L75 | Model E Data Set Logic | Diagram |

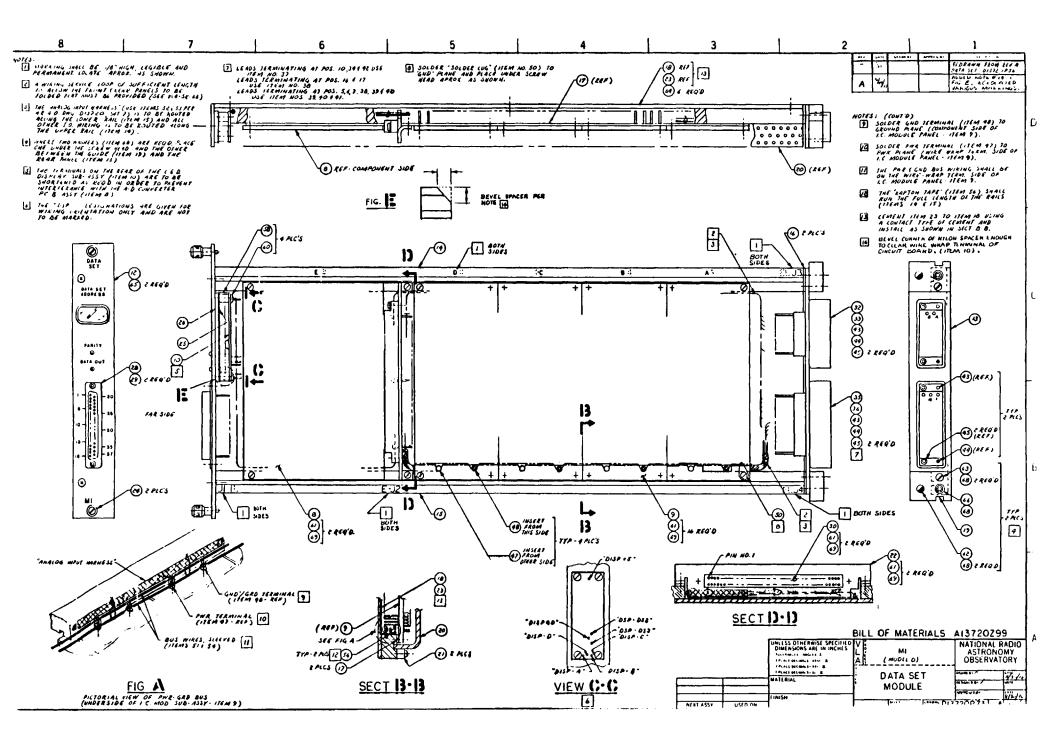

| D13720P73 | Model D and E Assembly | Drawing |

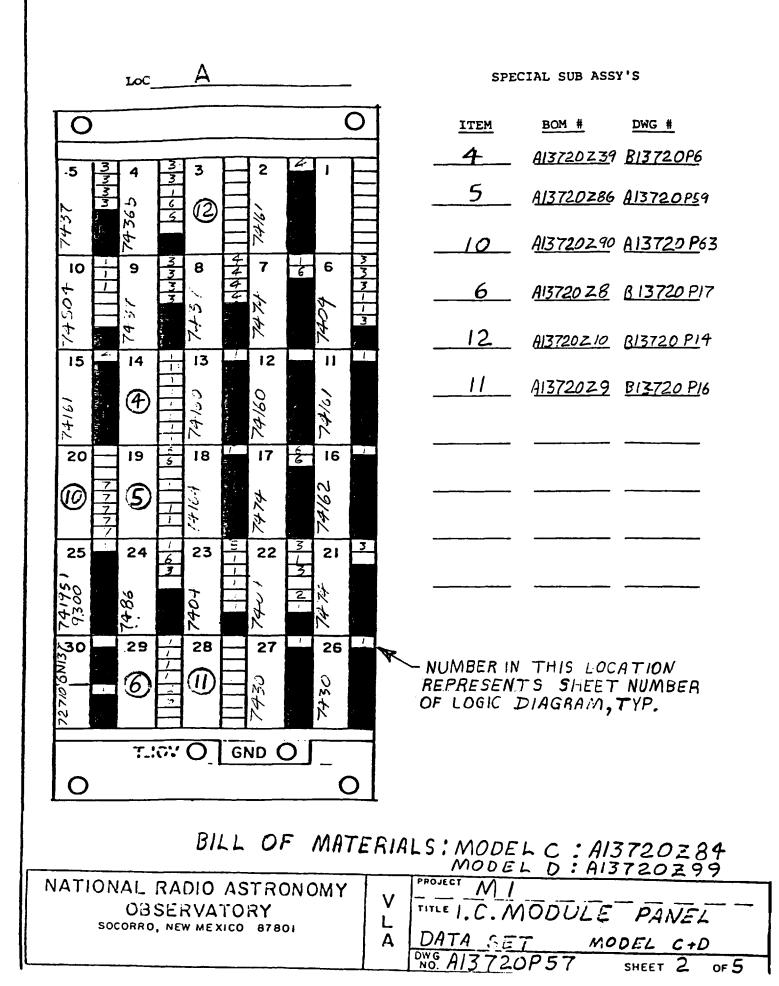

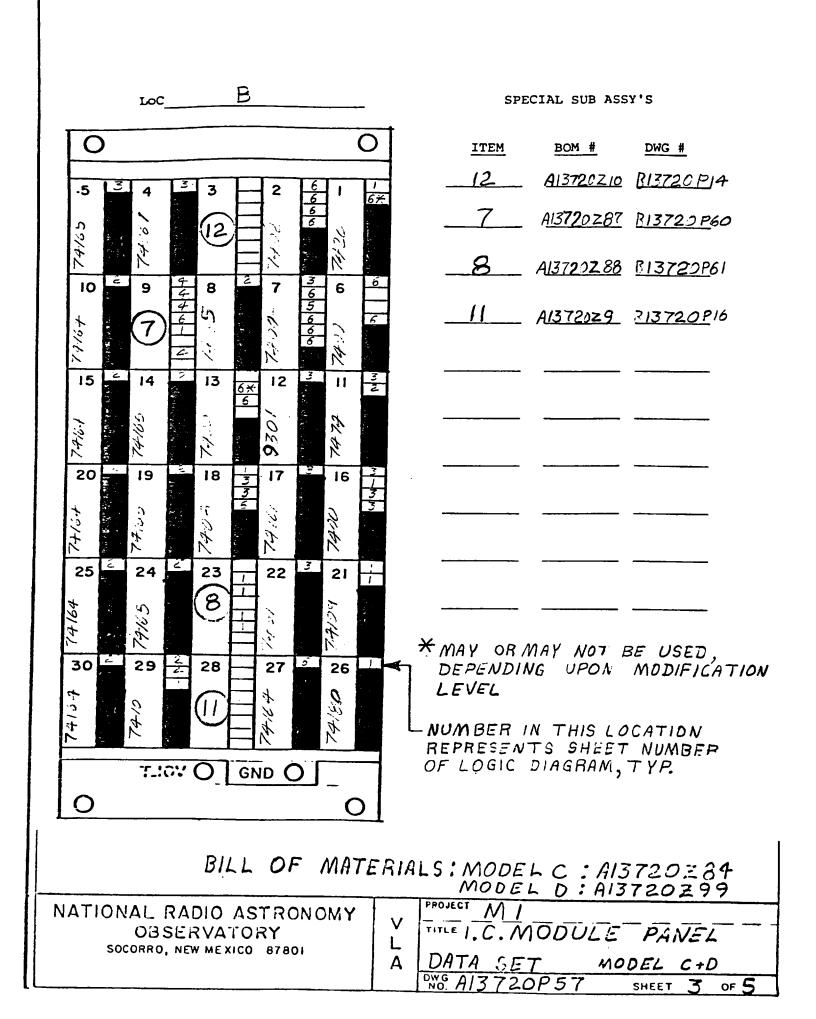

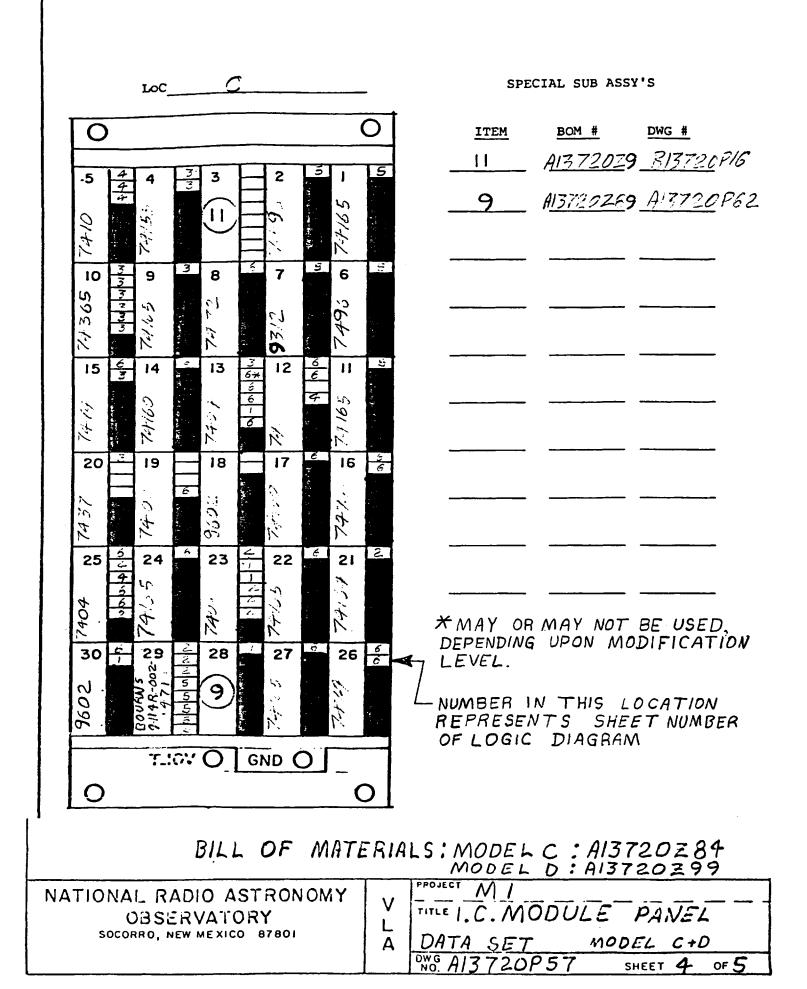

| A13720P57 | IC Panel Chip Location | Diagram |

#### **1.0 INTRODUCTION**

This manual describes the operation of the Data Set (DS), module type M1, and was written to serve as the trouble shooting and maintainance guide for this component of the Monitor and Control System (M&C). This manual is an updated version of an earlier Data Set manual; The Handyman's Guide to the Data Set, Module Type M1, VLA Technical Report No 30. Included is interfacing information which may be useful for those who design command or data channels which interact with the Data Set.

The function of the Data Set is to execute computer control command messages and to gather and format monitor data messages for the control computers. The Data Set is typically installed in a VLA electronics rack and services all the devices in the rack which require computer control or monitoring. The Data Set has a large command/data capacity; none of the VLA Data Sets have been used to capacity.

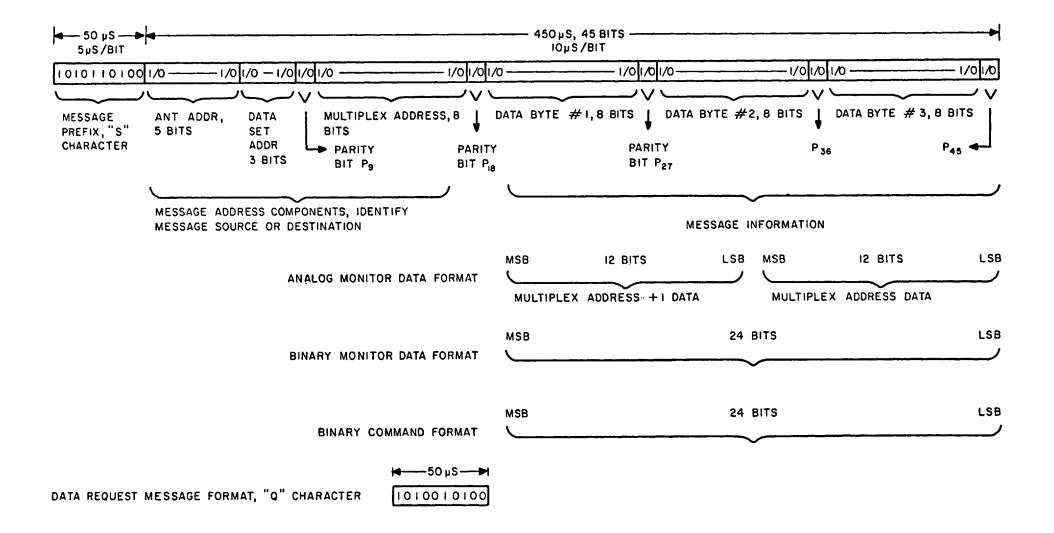

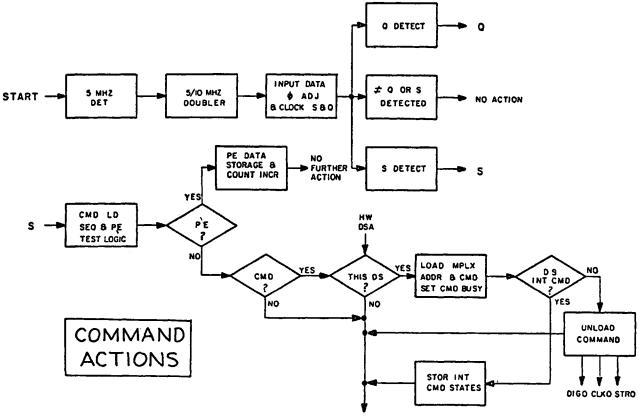

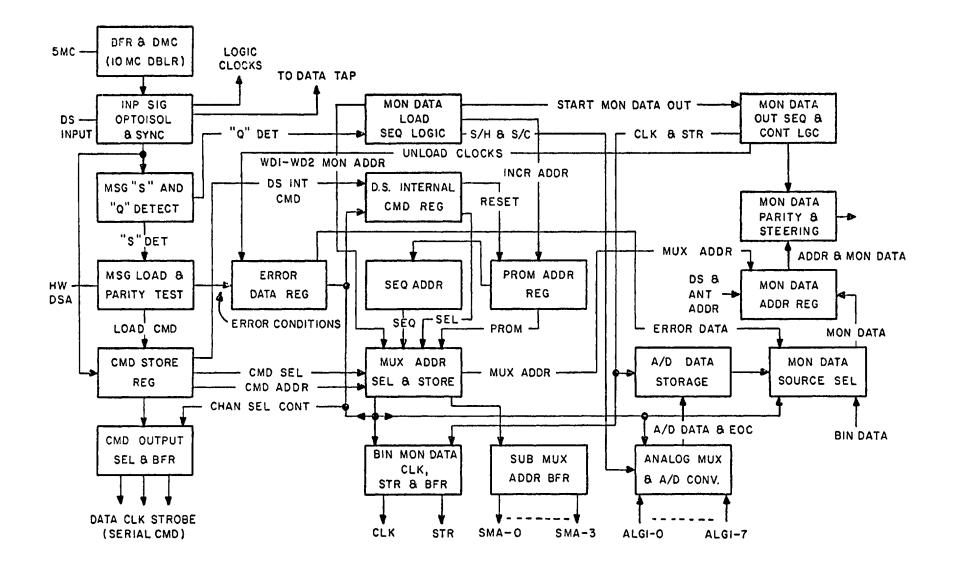

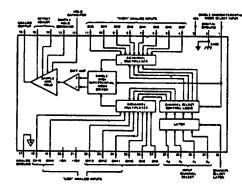

The Data Set is the prime focus of interest in this manual but functions of the Antenna Buffer and Central Buffer are described where it is necessary to explain aspects of the Data Set operation. For a description of these Buffer units, the reader is referred to "Overview of the Monitor and Control System", VLA Technical Report No 44. The Data Sets and devices serviced by them are depicted in Figure 1, the Monitor and Control System Block Diagram. The Antenna, Central and System Buffer manuals. (VLA Technical Reports Nos 59, 60 and 61 respectively) describe the interactions between these buffers and the Data Set. Figures depict the Monitor and Control 2 and 3 System timing relationships. Figure 4 depicts the message formats.

## 2.0 DATA SET DESCRIPTION

The Data Set is a digital machine which executes time-serial digital control command messages by controlling the states of controlled devices in accordance with the command message arguments. The Data Set also gathers analog and digital monitor data from these devices and formats the data into time-serial digital monitor data messages which are routed to the control computers for diagnostic purposes.

The Data Set is passive; it performs a command or data function only when stimulated by an Antenna, Central or System Buffer. The Buffer emits a stream of command, monitor data and data request messages and depending upon the character of the messages, the Data Set executes the command and monitor data operation.

The command messages originate in the central control computers and are routed to the Data Set via the Serial Line Controller, Central (or System) Buffer, Local Oscillator/Waveguide System (LO/WG), and Antenna Buffer. The monitor data messages are polled from the Data Sets by the Buffers, temporarily stored and then transmitted to the control computers via the Antenna Buffer, LO/WG transmission system, the Central (or System) Buffer and SLC.

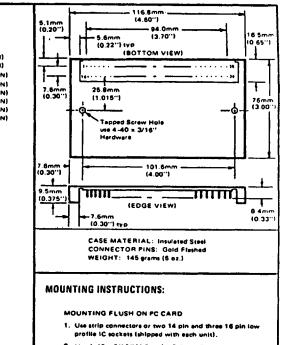

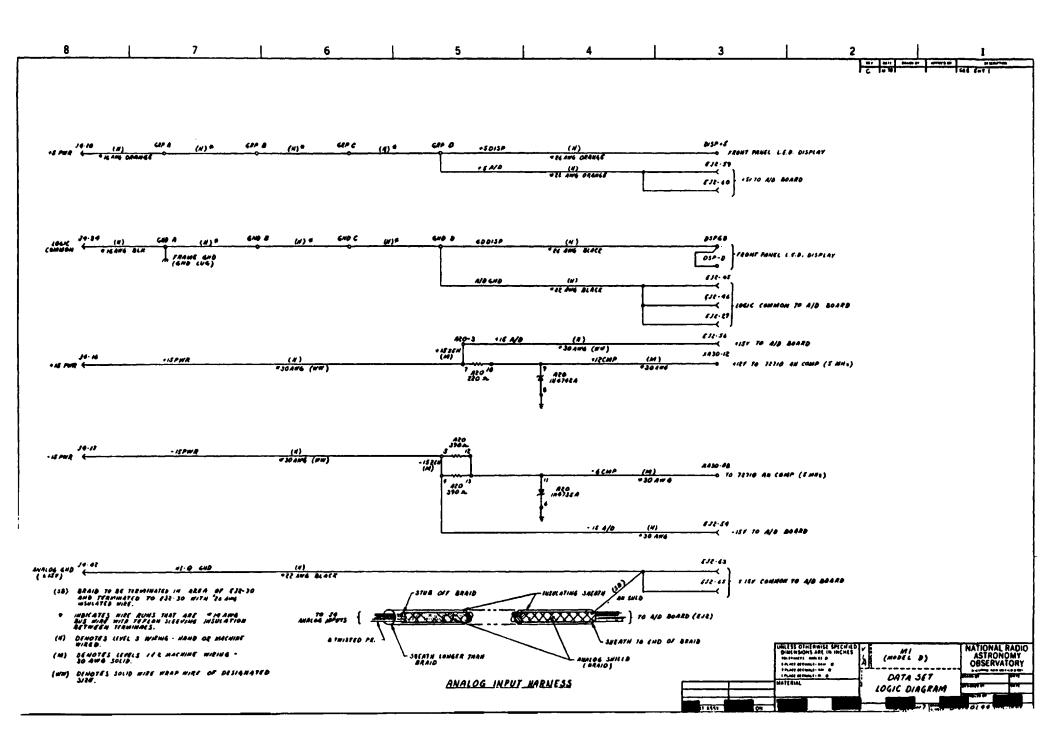

The Data Set is packaged in a 1-wide standard VLA module and contains wire-wrapped logic connector boards for the digital logic chips and a removeable (for alignment and test) analog multiplexer and A/D converter PC board. A front panel numeric LED indicates the Data Set address and flashing green and red output activity LEDs indicate monitor data message and malfunctioning signal conditions. Front panel test points permit important logic signals for diagnostic direct observation of purposes. The Data Set physique is depicted in the Data Set Top Assembly Drawing, D13720P73 and the Illustrated Parts Breakdown (Fig 10) in the rear of this manual.

#### 2.1 MESSAGE FORMAT DESCRIPTION

Figure 4 depicts the format of the M&C Command and Monitor Data messages and the "Q" character format. The Data Set accepts and outputs the NRZ form of these messages. All M&C messages are prefixed by an "S" (for start) character which signals that a message immediately follows. The bit rate of the S character is 5 usec/bit and the message bit rate is 10 usec/bit; thus the S character is unique and always distinguishable from message data The message consists of five 8-bit data bytes; the patterns. first byte contains a 5 bit DCS ddress (which can range from 0 to 31, 0 to 37, octal) and a 3 bit Data Set Address (DSA) which can range from 0 to 7. The second byte is the Multiplex Address which designates a particular command or data channel. The third, fourth and fifth bytes are components of a 24 bit command or monitor data argument. In the case of an analog data message, the 24 bit argument consists of two 12 bit values resulting from signals by the the conversion of two analog Data Set analog-to-digital converter. In all address and argument values. the first bit (in time) is the most significant bit.

The "Q" (for query) character is used by the CB, SB and AB to poll data from a Data Set and is sequentially directed to Data Sets via the Buffer's Data Set Command Ports. The bit rate of the Q character is 5 usec/bit.

## 2.2 DATA SET I/O SIGNALS

- Data Set Input Port, - an optically isolated (in the DS), TTL level input port which receives low-true command and monitor data messages and the data request (Q) character.

- Data Set Monitor Data Port, - a TTL level, low-true monitor data message output to the Buffer.

- Data Tap Port, - a TTL level, low-true output to the Data Tap which may be connected to the Data Set Input Port.

- 5 Mhz, - a 5 Mhz, 1 volt (nominal) clock which drives the Data Set logic. The clock may be either a 1 volt peak, (nominal) sine wave signal from the L8 distribution system or a TTL level clock from the Antenna Buffer.

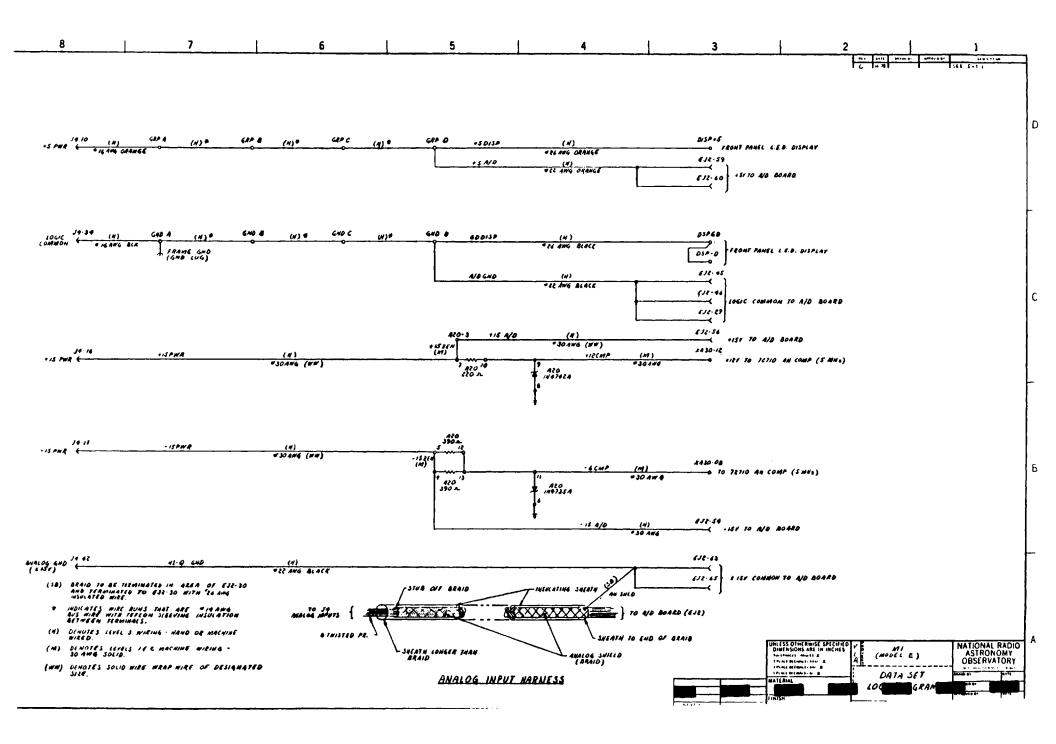

- Analog Inputs, ALGI-0 .. ALGI-7, - eight differential, +/- 10 volt level analog signal inputs to the A/D converter analog multiplexer from controlled devices.

- Digital Command Output Ports, - three TTL level, low-true command output ports consisting of clock, strobe and data lines and returns.

- Digital Monitor Input Ports, - four TTL level, low-true digital monitor input ports consisting of clock, strobe and data lines and returns.

- SMA-0 .. SMA-3, - four TTL level, low-true lines and returns which are used by devices to decode device select addresses. After the completion of a command or monitor operation, these lines are defaulted to the high (false) state.

- DSA address lines, - three low-true, TTL lines which define the Data Set address. These lines are hard-wired to logic common on the back of the bin to define the Data Set address.

- DCS address lines, - five low-true, TTL level lines to the monitor data output register which define the DCS address of the monitor data message output by the Data Set. These lines have no relevance in Data Sets connected to the Antenna Buffer because the AB dubs the DCS address into the monitor data messages in the process of polling antenna Data Sets. These lines must be hard-wired to ground when Data Sets are used with the System or Central Buffers.

In performing a command operation, the Data Set detects, loads and tests the command message for parity errors. If the message contents satisfy the error detection logic, the Data Set address (DSA) components of the message are compared with the hard-wired (in the bin) Data Set address to determine if the command is If so, then the command information and directed to it. multiplex address are stored for execution of the command. In executing the command the multiplex address is decoded to activate output data, clock and strobe lines causing the command be serially loaded into the multiplex address-designated to The DCS address component of the command message is not device. decoded by the Data Set; the Buffers store only the commands which pertain to their associated antenna so that the Data Sets

need not test for DCS address relevance.

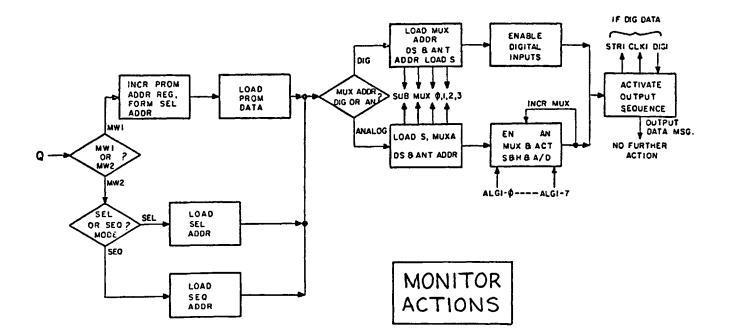

The Data Set is caused to perform a monitor data operation when it detects a Data Request character (Q) emitted by the associated Buffer. The Data Set then gathers digital and analog data which is formatted into a monitor data message along with multiplex address, Data Set address, DCS address, and message parity components. In the case of analog monitor data messages, there are two analog values and only one multiplex address. The multiplex address for the second analog value is implied and is the multiplex address + 1. The monitor data message is then serially output to the Buffer. The monitor data control logic has a 200 microsecond delay for analog data settling and A/D conversion.

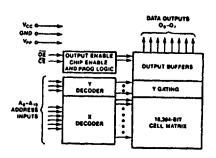

The Data Set monitor data sampling operations are time and multiplex address ordered. The Buffer evokes two monitor data messages (MW-1-MW-2) from each Data Set in one VLA machine cycle. The multiplex addresses for the first monitor data (MW-1) message are derived from an address program stored in a programmable read-only-memory (EPROM) which may be programmed to produce any sequence of multiplex addresses within a 192 message period. The EPROM may be programmed to sample channels at rates between 1 sample/10 seconds to 1 sample/VLA machine cycle. The multiplex addresses for the second monitor data (MW-2) message are derived in either of two ways:

1) Sequential mode in which 128 analog signals are sampled twice and 64 digital channels are sampled once over a ten second period.

2) Selected mode in which the multiplex address is set to a fixed channel specified by the control computers. This mode permits intensive (1 sample/VLA cycle) sampling of the designated channel for diagnostic purposes.

The reason that there are two different address-peculiar monitor data messages per VLA cycle is that the control computer operating system uses the EPROM address-designated (MW-1) data for diagnostic and control purposes which are fixed and constant. The second monitor word is provided for investigative and high sampling rate (in the Select mode) monitoring of device functions independent of the control computer programs. Figure 7 depicts typical MW1, MW2 and System overlay relationships.

Commands directed to the Data Set designate the selected address and control Select/Sequential modes. In addition, the EPROM address counter may be initialized to a base value by a Data Set Reset command so that all Data Sets with identical EPROMs sample the same data in any given machine cycle.

The monitor data messages emitted by the Data Set are

rebroadcast by the Antenna Buffer as they are stored in the AB monitor data memory. The rebroadcast data is sometimes called "gossip data". This rebroadcasting enables a Data Tap (see the Data Tap manual for details) to be connected to any Data Set in the antenna for visual display of command or monitor data messages. The Data Set is inhibited from responding to it's own monitor data messages to prevent positive feedback perturbations to the logic.

When the Data: Set detects an error-tainted (ie. parity error), command or monitor data message, parity error detection logic inhibits the execution of the message (if it is a command); the multiplex and Data Set address of the error-tainted message are stored for future monitor data readout by multiplex address 200 A flag bit is set if the error is detected in the (octal). multiplex address component of the message. A binary counter in error data logic counts the parity errors that occurred in the the intervals between address 200 data readout messages. The counter is reset to zero as part of the readout process. Because the Data Set is unable to respond to it's own monitor data messages, it cannot test or report it's own malfunctioning output.

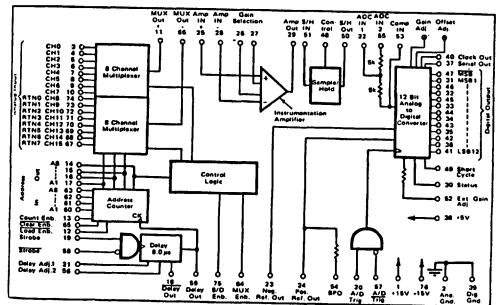

Analog data is multiplexed in the Data Set by an 8 channel differential input multiplexer-buffer amplifier. Each of these inputs is (typically) driven by an 8 or 16 channel single-ended or differential multiplexer located in the modules serviced by the Data Set. The lower four bits of the multiplex address drive the remote multiplexer and the next three bits drive the eight input Data Set multiplexer. The multiplex address is incremented after the first analog to digital conversion so that the second analog data channel can be selected and converted.

The output of the Data Set multiplexer/amplifier drives a sample and hold unit which "holds" the analog level constant for the analog to digital converter. The Data Set conversion control logic provides a 30 microsecond settling delay for the analog signal before it is held; the A/D converter causes the data to be loaded into a storage register for subsequent readout when the monitor data is output.

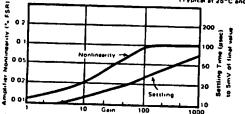

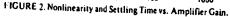

The major specifications of the analog multiplexer - A/D converter are:

Analog input range - +10.235 to - 10.240 Multiplexer "on" input impedance - 100 megohms Analog settling delay - 30 microseconds Multiplexer "on" resistance - 2 Kohms/line A/D conversion period - 50 microsaconds Common moderejection - > 60 db with a 1 Kohm source unbalance Conversion code - 12 bit 2's complement binary, 5 mv/bit Settling time - < 4 microseconds to .01% of full scale Cross talk - < 1mv, P-P @ 10 Khz Input over voltage tolerance - 35 V, max

## 2.3 MODULE CONTROL/DATA INTERFACE

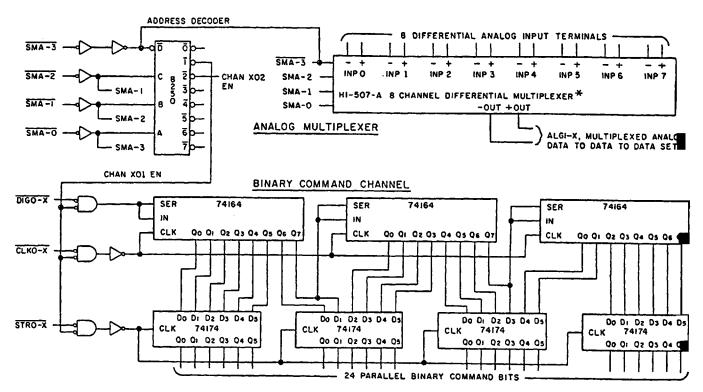

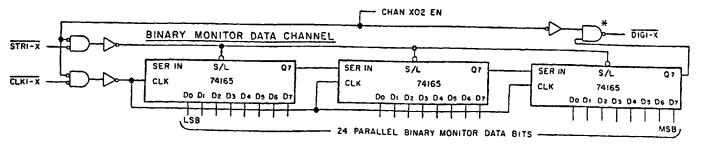

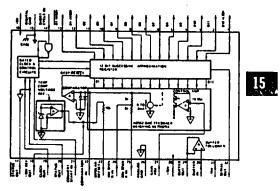

Each module serviced by a Data Set contains a small control/data interface driven by the Data Set which decodes addresses and accepts and stores command information. Under control of the Data Set, the control/data interface samples the device binary states and serially unloads it to the Data Set. Analog data is routed to the Data Set A/D converter by either single-ended differential analog multiplexers or in the interface. control/data Many different implementations of control/data interfaces are possible to service command, analog binary data channels. The most general or implementation incorporates all three functions and consists of about 13 chips which can decode and store a 24 bit command, load and output 24 bits of binary data and multiplex 8 channels of differential Figure 9 shows the logic diagram of a typical analog data. control/data interface. In effect these control/data interfaces are an extension of the Data Set logic. The use of these interfaces located in the various VLA functional modules enables the Data Set to service a great many command and data channels. Figure 9 depicts the analog and digital circuitry of a typical Control/Data Interface

#### 2.4 DATA SET CAPACITY

The full command/data capacity of the Data Set is:

- 1) 128 analog channels, converted to 12 bit 2's complement digital values.

- 2) 64 channels of 24 bit binary data (1536 bits).

- 3) 48 channels of 24 bit binary command (1172 bits).

The following table shows the Address/Function assignments:

#### MULTIPLEX ADDRESS\* FUNCTION

#### CAPACITY

| 0<br>20 | to<br>to | 17<br>37 | Analog data input, ALGI-0<br>Analog data input, ALGI-1 | 16 channels |

|---------|----------|----------|--------------------------------------------------------|-------------|

| 40      | to       | 57       | Analog data input, ALGI-2                              | 1           |

| 60      | to       | 77       | Analog data input, ALGI-3                              | Í           |

| 100     | to       | 117      | Analog data input, ALGI-4                              | i           |

| 120     | to       | 137      | Analog data input, ALGI-5                              | İ           |

| 140     | to       | 157      | Analog data input, ALGI-6                              | i           |

| 160     | to       | 177      | Analog data input, ALGI-7                              | 16 channels |

| 200     |          |          | Parity data readout                                    |             |

| 201     | to       | 217      | Binary monitor data, DIGI-0                            | 15 channels |

| 220     | to       | 237      | Binary monitor data, DIGI-1                            | 16 channels |

| 240 |    | 257 | Binary monitor data, DIGI-2      | l           |

|-----|----|-----|----------------------------------|-------------|

| 260 | to | 277 | Binary monitor data, DIGI-3      | ł           |

| 300 |    |     | Set MW 2 to select mode          |             |

| 301 |    |     | Set MW 2 to sequential mode      |             |

| 302 |    |     | Reset EPROM address counter      |             |

| 303 | to | 317 | Reserved for future Data Set use |             |

| 320 | to | 337 | Binary command, DIGO-0           | 16 channels |

| 340 | to | 357 | Binary command, DIGO-1           | 1           |

| 360 | to | 377 | Binary command, DIGO-2           | i           |

\* addresses in octal notation

#### 3.0 DETAILED FUNCTIONAL DESCRIPTION

This section contains a description of the theory of operation and is broken into sections which are keyed to the Data Set Block Diagram, (Figure 4). The Data Set logic is straightforward and easily grasped by those with digital backgrounds, therefore the logic descriptions in the sections are brief and emphasize the most important aspects of the logic rather than exhaustive discussions of the function performed by each logic element. The order of increasing logic discussed in the is functional dependency.

Figure 8 depicts the waveforms which may be observed on the front panel test point connector.

The reader should study the timing diagrams referenced by the description as they graphically illustrate logic operations; they are a replica of the timing waveforms which may be observed with an oscilloscope. The timing diagrams are keyed to the signal location designator and pin number. source points by the Important causitive relationships are indicated by arrows from Clocking relationships are implied by an one waveform to others. up or down arrow which indicates the portion of the waveform which causes driven devices to be triggered. Where it is important to the discussion, logic states, timing durations, delays or frequencies are marked on the diagrams. A linear time base is employed in all diagrams but delays may be exxagerated for emphasis of race or delay considerations. Waveform sampling is indicated by arrows, tick marks and the letter S to denote sampling.

The discussions refer to the Model D and E versions of the Data Set which differ in the type of EPROM which stores the data sampling program. The Model D units use an Intel 1702A, (8 bit x 256 byte) word EPROM which must be changed when relocating Data Sets between racks. The Model E units use an Intel 2716 (8 bit x 2 k byte) EPROM which contains all data sampling programs. The three DSA lines (hardwired on the rear panel) select the program appropriate for the rack location, (e.g racks A,B,C,D); this simplifies the logistics of swapping Data Sets. Earlier models of the Data Set were upgraded to levels D and no longer exist. Model E Data Set construction started in the spring of 1986. Logic diagrams for both models are found in the rear of this manual.

#### 3.1 5 Mhz CLOCK DETECTION AND DOUBLING LOGIC

An externally provided 5 Mhz, 1.0 volt peak (nominal) sine wave signal is the clock source for the Data Set. A 72710 analog comparator (A30B) and 7404 inverter square the 5 Mhz signal to drive the harmonic doubler A14 which doubles the 5Mhz clock. The A14 tank circuit rings at 10 Mhz and is "kicked" by the positive-going edge of the drive from inverter A1002. AlO is a 74S04 because of it's high switching speed which produces sharp edged pulses for the harmonic generator. The drive edges are differentiated by the 10 pf/1 Kohm circuit in the MPS 918 base circuit and the positive-going edge provides a narrow current pulse to the transistor base. Inverter A1004 is caused to operate in a quasi-linear region by the 2 Kohm resistor in A14. The output of A1006 is the highest frequency clock source in the Data Set and all clock rates are derived from it. All must be a 74S04; the high switching speed of the Schottky logic is important for the doubler circuit's operation.

#### 3.2 INPUT SIGNAL SYNCHRONIZATION LOGIC

Optically-coupled isolator A30A detects the Data Set command/Q signals from the Antenna or Central Buffers and provides ground isolation between the Data Set and the Buffers. The data is clocked into shift register A25 by the 10 Mhz clock. 1/0 or 0/1data edges are detected by exclusive or gate A2403 which presets counters Al2 and Al3 to a count state of 41. This counter is incremented by the 10 Mhz clock to a count of 90 which then causes the counter to be reset to the 41 state via the 7402 D3004. Timing Diagram 1 depicts the timing relationships. Output A1313 is a 200 Khz waveform whose positive-going edge is delayed 2 usec from the 1/0 or 0/1 signal edges. The 200 Khz signal is the clock for counters Al6 and Al1 and also the sample clock for shift register A18. The purpose of this delay is to sample the input signal at the approximate center of the S character bits. A 1 Mhz clock is tapped off counter A1211. The use of this clock is discussed later.

#### 3.3 MESSAGE DETECTION/LOADING LOGIC

Shift register A18 is serially loaded with the input data stream by the phase adjusted 200 Khz clock from A1313 described above. Gates A2610 and A2710 detect a data request message (Q) or a start of a command or monitor data message (S) in shift register A18. When the last 8 bits of the Q character are loaded into A18, gate A2610 goes true for 5 usec. This Q detection initiates the monitor data gathering sequence described later.

Similarly gate A2710 goes true for 5 usec when the last 8 bits of the start (S) character are loaded into A18. This S detection activates the message load counter consisting of flip-flops B2106 and synchronous counters A16 and A11. The counter generates 45 shift clocks to serially load the message into the message input registers B30, B25, B15, and B10. See timing diagram 2 for Counter A16 operates with a radix of 9 to program a details. parity test of the message data on a byte by byte basis. The parallel contents of register B30 are presented to B26, а parallel parity generator/checker, and at the count of 9 the output of B26 will enable the J input of flip-flop B2110. If there is a parity error, B2110 will be clocked true. At completion of the loading sequence, the counter is shut off At the by the fall of All11 which also triggers one-shot C1810. The strobe output of C1810 causes parity error data to be stored in the error data register (discussed later) if a parity error occurred in the message.

If the message passes the parity test, the C1810 strobe is enabled onto comparator B8 which compares the message Data Set address with the hard-wired (in the bin) DSA. If the addresses agree, B8 A-B output passes the B2110 strobe to gate B2914 which further tests the message to determine if it a command by anding mux address bits 128 and 64 which are both true for command messages. This test is necessary because the message could be a rebroadcast monitor data message which is of no consequence to the Data Set other than the parity test.

If the message is a command message addressed to the Data Set in discussion, then the 24 command argument bits are parallel loaded into registers B24, B19 and B14. The Cmd busy flip-flop B1111 is also set by B2914. The command multiplex address is caused to be stored in the multiplex address register A15 and A2 via multiplexers D21, D22, D26 and D27. The multiplexers are pointed to the portions of the message loading registers which the command multiplex address by gates contain D0506/10, and the Cmd Busy flip-flop B1111. D2406/10 The mux address is strobed into registers A15 and A2 by the trailing edge of one C3009 is triggered by the trailing edge of one shot shot C3009. C1810 and provides 100 ns of delay to enable the mux address to propagate through the multiplexers and stabilize at A15 and A2 before being clocked by C3009. If a parity error should occur, C1807 shot is triggered on to provide a stretched one illumination of the front panel red parity error LED.

Note that the parity test logic operates on <u>both</u> command and monitor data messages and causes error data to be stored for both types of messages. Thus a parity error in a monitor data message is heard by all Data Sets in the antenna and is multiply reported. Also note that the DCS address is not tested or used in the loading process other than in the parity error tests.

#### 3.4 COMMAND OUTPUT LOGIC

In the previous section we saw how the command messages were loaded, error tested and parallel stored. The storage process is completed by about 200 ns after the last load shift clock. The 24 command argument bits are immediately unloaded to the command destination which leaves the the message loading circuitry free to accept the next message which may immediately follow. The unload operation is initiated by gate B22914 (mentioned above) which sets control flip flops B1105 and C1511. B1105 enables counters B17 and B22 to count out 24 100 Khz shift clocks and one clock time later a strobe pulse. The 24 command argument bits, shift clocks and strobe are enabled to one of three sets of digital outputs by address decoder B12 which is driven by the four high order bits of the multiplex address. The four lower order bits of the multiplex address are decoded by the commanded devices and enable the information output on the three sets of outputs to be loaded and stored. For details on the usage of these signals in a controlled device see Section 6 for an example of a typical command channel logic diagram.

The trailing edge of the strobe pulse resets the Cmd Busy flip flop Bllll. Bllll forces the multiplex address registers A2 and A15 to be cleared via the DS busy gate B0613. Thus the multiplex address storage registers are cleared to address 0 between command operations. Timing Diagram 3 shows the time relationships of the command output logic.

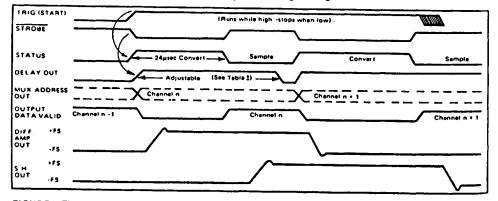

## 3.5 MW-1/MW-2 AND MUX LOAD SEQUENCE

When a data request character (Q) is detected (see Section 3.3), it toggles D2305 which controls the MW-1/MW-2 steering of the multiplex address multiplexers D21, D22, D26 and D27. D2305 also increments the EPROM address counters D17 and D18. The reader will remember that MW-1 (ie. the first monitor data message evoked by the Buffer in a VLA machine cycle) contains data selected by the program residing in the EPROM. MW-2 is either a computer-specified (ie. associated with selected or sequentially scanned address) а address. The MW-1/MW-2ordering is accomplished by the two one-shots D0405 and D0409, which are triggered by the Q detection gate A2610. The Q characters occur in pairs, (1 pair/VLA machine cycle) and are separated by either 1000 usec or 4.5 milliseconds depending upon drives Buffer the Data Set. One-shot which D0406 is retriggerable with a period of of 5 milliseconds; this is greater than the interval between the Buffer's Q character outputs. This delay causes flip-flop D2305 to be left in the proper state to steer the EPROM address to the address register when the

Buffer requests the first monitor word in the VLA cycle. Shift register D9 is a clock phase generator which generates a time delayed clock to allow the multiplex address enough time to propagate through the address multiplexer to the address storage register. Other functions of the clock phase generator are initialization of the 200 Khz divider A0705, triggering of the output data sequencing logic, loading of the multiplex address, Data Set address and DCS addresses in C22 and C27, and the "S" character bits in registers C24 and C26. Timing diagram 4 shows the clock terms generated by the clock phase generator D9.

Because of it's 24 pin package, the EPROM is physically located on the analog multiplexer - A/D board for packaging convenience.

#### 3.6 MONITOR DATA ADDRESS FORMULATION

Counters D17 and D18 are incremented by the leading edge of the Q detection gate A2610 and have a radix of 192; thus the EPROM address recycle rate is 192 addresses in 10 seconds. Since counters D17 and D18 are incremented by the leading edge of the Q detection gate, the address program contents of the EPROM have about 5 microseconds to settle through the multiplexer before they are loaded into the multiplex address registers A2 and A15 by the logic descsribed above. This same settling time also applies to the Select and Sequential address data.

The Select address data is stored in shift register C21 which is loaded by a command addressed to multiplex address 300 (octal). When this command is detected, the lower 8 bits of the command are shifted into C21 and the Select/Sequential flip-flop is set to the select state. This flip-flop then causes the multiplex address multiplexer to route the selected address stored in C21 to the address registers A2 and A15.

The sequential address is formed by 2-to-1 multiplexers D19 and D20 and full adder D13 under control of gates D2903, D2906, D1203, C1213,C0514 and C0506. The sequential addresses scan all 128 analog addresses twice in ten seconds and the 64 digital addresses once in ten seconds. The digital address scan is broken into two scans of 32 addresses each between analog address scan. The base for the sequential address counter is the EPROM address counter which sequences from 0 to 191 and is incremented once each VLA cycle by the Q detector logic.

The Sequential address algorithm is very simple and involves using the EPROM address counter directly, doubling the counter value and/or adding 64 to the count. The algorithm is depicted on the next page, (Np - Prom address, Ns - Sequential Address):

| EPROM address                   | Sequential address             | Rule         |

|---------------------------------|--------------------------------|--------------|

| counter range                   | counter range                  |              |

|                                 |                                |              |

| 0 <- Np <- 63                   | 0 < <b>-</b> Ns < <b>-</b> 126 | Ns - 2Np     |

| 64 < <b>-</b> Np < <b>-</b> 95  | 128 <- Ns <- 159               | Ns = Np + 64 |

| 96 < <b>-</b> Np < <b>-</b> 159 | 0 < <b>-</b> Ns < <b>-</b> 191 | Ns - 2Np     |

| 160 <= Np <=191                 | 160<- Ns <- 191                | Ns - Np      |

The control gates enable or inhibit the add 64 and left or no shift logic operations in the adder and multiplexers on the basis on the Prom address counter states. The contents of the multiplex address register are used extensively in the Data Set to control the distribution of monitor data and command output clocks, strobes and data. The lower four bits of the address register are buffered out of the Data Set as low-true lines by After the completion of a command or monitor data buffer A8. message output, the D5 busy logic A17 and B6 force the multiplex address register to the zero state. This makes the sub-mux address assume the zero state; • all control/data interfaces will sense this state. The external analog multiplexers will a11 select the zero address channel and route it to the Data Set ALGI-0 analog input. The Data Set is not perturbed by the presence of this signal since the multiplexer and A/D are inactive.

#### 3.7 ANALOG DATA GATHERING SEQUENCE

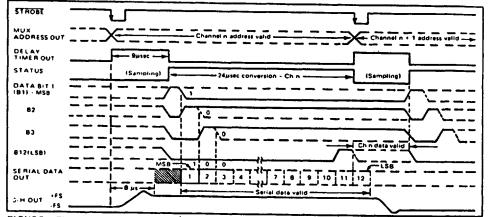

Counter C17 and C1605 are enabled by control flip-flop C1611 which is set by the clock pulse generator discussed in Section The multiplex address had been loaded 1 usec earlier in 3.5. multiplex address registers A2 and A15. The counter is incremented by 100 Khz clocks from A0705 to generate sequential control terms for the Sample and Hold unit and A/D Converter. At 30 usec, the Sample and Hold is set to the hold mode; at 40 usec. the A/D start conversion input is triggered by one-shot D1006. After the 50 usec duration conversion, the A/D end of conversion line drops and triggers one-shot D1010 which resets flip-flop A0710 to reset the Sample and Hold unit to the sample mode. Gate C1913 steers the 500 ns one-shot to load the A/D data into shift registers Cl and C2. At 100 usec, counter C17 increments the multiplex address registers (if the mux address is in the analog data address range) which then causes the next sequential analog channel to be selected by the external analog multiplexer. With analog signal, the new the Sample and Hold unit, start conversion, end of conversion and data storage operations occur at 130, 140, and 190 usec respectively. At 200 usec, flip-flop C1610 is reset and the output data shift operation is initiated by setting flip-flop C1505. Gate C1913 generates a binary data strobe which is used to cause binary data sources to paralell load output shift registers for an impending unload shift.

#### 3.8 OUTPUT DATA SEQUENCING LOGIC

The data output operation consists of serially shifting out the DCS, DSA & MUX addresses, A/D data, parity bits and the "S" When the message emerges at the output port it message prefix. will be in the M&C message format. Counters C14 and D16 are incremented by 100 Khz clock pulses from A0705 and generate sequencing and control terms which program the output of the monitor data message. Counter Cl4 operates with a radix of 9 to cause parity data to be output at the appropriate points in the output message. Shift register B27 is a Johnson counter with a radix of 10 and is incremented by 1 Mhz clock pulses from A1211. The counter is initialized to an all zero state by flip-flop When C1505 goes high at the start of the output C1505. sequencing operation, a wave of five "1"s followed by a wave of five "0"s circulate around the register. The gates driven by B27 generate time-phased clocking terms to clock all the monitor data Timing Diagram 5 shows these waveforms and the basic registers. logic. The logic driven by these terms are: parity counter C8, output register C29 and C26, data register C1, C2 C6 and C11, parity error registers B5 and C9 and the binary data channels from the external device controllers. These sample clocks are to avoid race conditions in clocking the long time-phased string of concatenated shift registers; this makes the Data Set very tolerant of logic delays in external binary data channels. Timing Diagram 6 and 7 show the generation and usage of these clock terms. Under multiplex address control, multiplexer C7 selects either the A/D converted data or binary data from a binary data channel in some module serviced by the Data Set. And-or-invert gate D0210 selects either the C7 data mentioned above or the parity eror data from parity data registers C9 and B5. Every ninth count state of counter Cl4, the parity readout control logic (consisting of gates B1310, inverters C2514 and C2502 and flip-flop A1705) causes and-or-invert gate D0206 to steer the parity data from flip-flop C8 into the output data stream.

Gate B0110 causes the clock inhibit flip-flop D1412 to be set at a count of 24 so that the three data registers (ie. converted analog data, parity error data and external binary data register) see only 24 unload clock pulses which is enough to unload them completely. An additional 16 clock pulses are required to bring these bits to the output register C24. This 24 clock pulse count is chosen to permit command channels to operate in a circular shift mode so that the contents of command channels may be read out non-destructively as binary data. Module L7 uses this feature. Counter D16 is preset to a count of 3 which provides sufficient time for all data to propagate through registers C24 and C26 with an additional 45 usec of shift time after the last data has shifted through C24 and C26.

The DS busy flip-flop A1710 is reset at the completion of the

output data shift operation.

An output of flip-flop C1506 is used to inhibit the ability of the Data Set to "hear" it's own output when used with an Antenna Buffer. This inhibit disables the phase adjust term from exclusive or gate A2403 and clears shift register A18 so that the 200 Khz clocks are not phase perturbed by the Data Set's own output (a positive feedback). In addition it inhibits the detection of the S in it's output message.

Buffers A0411 and A0409 drive the data to the Buffer and the Data Out LED respectively.

#### 3.9 PARITY ERROR DATA READOUT LOGIC

In the event that a distorted command or monitor data message is detected by the Data Set, gate B1606 causes the message multiplex and Data Set address components and the error count to be stored in registers B5 and C9. In addition, if the error occurred in byte 2 of the message, gate B0106 sets flip-flop D2311 which is also stored with the data above. In the event that the parity error rate is high, counter B4 counts the number of errors (up to 16) between the error data readouts on multiplex address 200 (octal). Gate D0610 goes true when multiplex address 200 occurs and enables the parity data in registers C9 and B5 to be routed to the output logic via and-or-invert gate C0210. The data is clocked and sampled in the same manner as A/D or digital data from a device interface.

## 4.0 ANALOG SUBSYSTEM ALIGNMENT AND TESTS

The analog multiplexer - A/D converter board is removeable from the Data Set for alignment and test in a controllable analog and logic environment. This environment is provided by an A/D-mux test fixture, (dwg D13720I45) a high precision adjustable DC source (Fluke 343A), a digital multimeter and an oscilloscope.

The A/D-mux test fixture has a dual bus switching structure and several analog signal sources. Control and conversion logic sequences the multiplex address, triggers the sample/hold unit and A/D converter and displays the converted digital value and mux channel. The timing of these terms is identical to those in the Data Set. Control switches permit the multiplex address to sequence or be set at any channel. These switches also permit the selection of continuous or manually triggered conversions and the use of the various alignment and perturbation sources. 4.1 ALIGNMENT PROCEDURE FOR A/D BOARD

1. Set the front panel switches of the test fixture as follows:

| CMP/LC          | - | LC   |

|-----------------|---|------|

| SCAN/SEL        | - | SEL  |

| MANUAL ON/OFF   | - | OFF  |

| BUS A O-JO      | - | 0    |

| BUS A DIFF/COMM | - | DIFF |

| BUS A +/-       | - | +    |

| BUS B 0-50      | - | 0    |

| BUS B DIFF/CM   | - | DIFF |

| CHANNEL SELECT  | - | CH 0 |

| BUS A SOURCE    | - | GND  |

| BUS B SOURCE    | - | GND  |

|                 |   |      |

Set all channel switches to BUS A.

Plug an A/D board (component side up) into the top socket and set the power switch to on.

2. Connect a 4 digit Data Precision DVM between the S/H out and the analog ground test points and adjust the S/H offset pot for a reading of 0.0000 volts.

3. Move the DVM to the analog out test point and adjust the zero adjust pot for 0.000 volts.

4. Remove the DVM and adjust the ADC offset pot for a tester display of 0.000 volts.

4.2 DC Common Mode

1. Set the BUS A DIFF/COM switch to CM. Set the BUS A source to 100 Hz square wave. Switch the desired channel to BUS A and all others to BUS B (GND). With a scope of at least 5 MV/cm sensitivity connected between the analog out and analog gnd terminals, adjust the DC CMR pot for the minimum signal.

4.3 AC Common Mode

1. Using the procedure outlined above, set the BUS A source to a 1 Khz sime wave and adjust the AC CMR pot.

2. Repeat the DC CMR adjustment of 6.2 to insure proper AC and DC CMR alignment.

4.4 A/D Adjustment and Test

1. Set the BUS A DIFF/CM switch to DIFF and the BUS A source to external. Apply a precision DC reference between the BUS A Hi and Low terminals.

2. Set the reference to +10.000 volts and adjust the ADC gain

pot for a panel reading of 10.000 volts.

3. Set the reference to 0.000 volts and adjust the ADC offset pot for a panel reading of 0.000 volts. Return to step 2 and repeat the 2/3 sequence until no further adjustment is necessary.

4. Using the test data sheet, Figure 10, vary the external reference from +10.000 to -10.000 in 1.0 volt increments and record the displayed values.

4.5 CMR Test

1. Install a 1 Kohm resistor between the BUS A Hi and Low terminals. Connect the selected channel to BUS B.

2. Set BUS A source to external. Set RSA and RSB switches to 0 resistance. Set A and B +/- switches to +. Set A and B CM/DIFF switches to CM.

3. Set BUS B source to 1 k, and note the converted value.

4. Set BUS B source to 1 volt and record the value.

5. Set BUS B source to 10 volts and note value.

6. Calculate and record the followint values:

CMMR(db) = 20 log <u>| (step 3 - step 4) |</u> 1 volt

CMMR(db) = 20 log <u>| (step 3 - step 4) |</u> 10 volts

In handling the A/D board, it is very important to avoid touching the PC board contact fingers as human skin oil and salts may contaminate and corrode the edge connector contacts on the board and in the Data Set. Board contact plating often is porous and skin oils and salts can form corrosion products which will cause unreliable electrical contact in a few months. If the contact fingers are touched, the contact area should be thourougly cleaned before installing the A/D-mux board in the Data Set.

16

# DATA SET MUX-A/D BOARD TEST DATA

|             | Serial #                         |      |

|-------------|----------------------------------|------|

| Date        | Test by                          |      |

| A/D Ser #   | Installed in Data Set Ser #      | Date |

| Input Volts | <u>Converted Value</u> Error, MV |      |

| +10.000     |                                  |      |

| +9.000      |                                  |      |

| +8.000      |                                  |      |

| +7.000      |                                  |      |

| +6.000      |                                  |      |

| +6.000      |                                  |      |

| +5.000      |                                  |      |

| +4,000      |                                  |      |

| +3.000      |                                  |      |

| +2.000      |                                  |      |

| +1.000      |                                  |      |

| 0.000       |                                  |      |

| -1.000      |                                  |      |

| -2.000      |                                  |      |

| -3.000      |                                  |      |

| -4.000      |                                  |      |

| -5.000      |                                  |      |

| -6.000      |                                  |      |

| -7.000      |                                  |      |

| -8.000      |                                  |      |

| -9.000      |                                  |      |

|             |                                  |      |

| -10.000     |                                  |      |

| CMD all     |                                  |      |

| CMR, db     |                                  |      |

5.0 Major Data Set Drawings Top Assembly Drawings Data Set, Model D Top Assembly Drawing D13720P73 A13720299 Data Set, Model D Top BOM Functional Drawings Data Set, Model E Logic Diagram D13720L75 Data Set, Model D Logic Diagram D13720L44 A13720P57 IC Panel Chip Location Map, Model D & E Wiring Drawings A13720W61 Data Set, Model D Master Wire List A13720W62 Data Set, Model D Hand Wire List A13720W63 Data Set, Model D Machine Wire List A13720W64 Data Set, Model D Connector Pin/Signal Wire List C13720P03 DCS Module Logic Wire-Wrap Field Dim & Notation D13720M97 Data Set Wiring Jig Configuration A13720W44 Data Set J1 I/O Signal Wire List A13720W45 Data Set J3 I/O Signal Wire List A13720W46 Data Set J4 I/O Signal Wire List Mechanical Components Drawings C13720M16 Data Set Front Panel Machining Drawing C13720M15-1, 2 Modification, Rail B13720M18-1 Front Panel Filter, Polarizing B13720M18-2 Front Panel Filter, Clear C13720M17 Insulated Spacer, Rail C13720P68 Insulated Side Panel Ass'y B13720M49 Side Panel Insulation C13720M50 Side Panel, Modified C13720M07 Perf Cover Ass'y B13050M17 Perf Cover Fastener B13050M32 1-Wide 42/34 Rear Panel B13720M46 A/D PCB Connector Support C13720AA51 Data Set Front Panel Silk Screen Artwork Front Panel LED Display Drawings C13720P38 Front Panel LED Display Ass'y A13720Z23 Front Panel LED Display Ass'y BOM D13720M33 Front Panel LED Display Detail B13720AB06 Front Panel LED Display PCB Artwork Burr-Brown Type Mux-A/D Converter Drawings, (Model D DS only) (uses Burr-Brown SDM 853 and Intel 1702 EPROM) D13720P92 A/D Converter Ass'y Drawing A13721Z19 A/D Converter Ass'y, BOM D13720AD20 PCB Artwork D13720AD22 PCB Silkscreen Artwork D13720M55 PCB Drill Drawing D13720AD23 PCB Solder Mask Artwork C13720P93 Prom Carrier PC Board Ass'y

B13720M57 Prom Socket Protector

Analog Devices Type Mux-A/D Converter Drawings, (Model D DS only) (uses Analog Devices AD 363 Analog Input System & Intel 1702 EPROM) C13721P41 A/D Converter Ass'y A13720Z61 A/D Converter Ass'y BOM D13720M91 PCB Drill Drawing C13720AB35 PCB Solder Mask Artwork C13720AB36 PCB Silkscreen Artwork A13720P93 Prom Carrier PC Board Ass'y B13720M57 Prom Socket Protector (note, the PCB artwork for this board was modified to the Model E Data Set version) Analog Devices Type Mux-A/D Converter Drawings, (Model E DS only) (uses Analog Devices AD 363 Analog Input System & Intel 2716 EPROM) D13720S23 Logic Schematic C13720AB48 PCB Artwork D13721M13 PCB Drill Drawing C13720AB49 PCB Silk Screen Artwork A13720P93 Prom Carrier PC Board Ass'y B13720M67 Prom Socket Protector

6.0 Input/Output Signal Pin Assignments J1 - 37 pin Front Panel test D connector J2 - 86 pin Mux - A/D board internal connector J3 - 34 pin Amp Rear Panel connector J4 - 42 pin Amp Rear Panel connector Power Inputs: + 5 Volt logic power - J4 - 10 Logic Common - J4 - 34 + 15 Volt power - J4 - 16 - 15 Volt power - J4 - 17 Analog Gnd - J4 - 42 Address Inputs: - J4 - 18 - J4 - 24 Anta-4 ("16") Anta-3 ("8") - J4 - 20 Anta-2 ("4") Anta-1 ("2") - J4 - 13 Anta-0 ("1") - J4 - 2 DSA-2 ("4") - J4 - 29 DSA-1 ("2") - J4 - 28 DSA-0 ("1") - J4 - 11 Command Message/Q Inputs: Cmd/Q Hi - J4 - 25 Cmd/Q Lo -J4 - 26 Monitor Data Message Outputs: Data to Buffer Hi - J4 - 15 Data to Buffer Lo - J4 - 27 Data Tap Output: Cmd/Data Messages Hi - J4 - 8 Cmd/Data Messages Lo - J4 - 9 Submultiplexer Address Outputs: Signal Pin SMA-0 ("1") J3 - EE SMA-0 Ret J3 - CC SMA-1 ("2") J3 - KK SMA-1 Ret J3 - HH SMA-2 ("4") J3 - DD SMA-2 Ret J3 - FF SMA-3 ("8") J3 - JJ SMA-3 Ret J3 - LL

Command/Data Channel I/O Pin Assignments

Digital Command Outputs

| DIGI/O     | #0        | #1       | #2        | #3        |

|------------|-----------|----------|-----------|-----------|

| Addr *     | 200 - 217 | 220 -237 | 240 - 257 | 260 - 277 |

| Signal     |           |          |           |           |

| DIGI-X     | J3 - B    | J3 - R   | J4 - 1    | J4 - 19   |

| DIGI-X Ret | J3 - D    | J3 - T   | J4 - 4    | J4 - 22   |

| CLKI-X     | J3 - F    | J3 - V   | J4 - 3    | J4 - 21   |

| CLKI-X Ret | J3 -\J    | J3 - X   |           |           |

| STRI-X     | J3 - L    | J3 - Z   | J4 - 12   | J4 - 23   |

| STRI-X Ret | J3 - N    | J3 - BB  |           |           |

\* Address in octal notation

Digital Monitor Data Inputs

| Addr *     | 320 - 337 | 340 -357 | 360 - 377 |

|------------|-----------|----------|-----------|

| Signal     |           |          |           |

| DIGO-X     | J3 - C    | J3 - S   | J4 - 35   |

| DIGO-X Ret | J3 - A    | J3 - P   | J4 - 36   |

| CLKO-X     | J3 - H    | J3 - W   | J4 - 37   |

| CLKO-X Ret | J3 - E    | J3 - U   |           |

| STRO-X     | J3 - M    | J3 - AA  | J4 - 30   |

| STRO-X Ret | J3 - K    | J3 - Y   |           |

Analog Monitor Data Inputs:

| Signal  |            |      | Address * |

|---------|------------|------|-----------|

| ALGI-0+ | J4         | - 14 | 00        |

| ALGI-0- | J4         | - 32 |           |

| ALGI-1+ | J4         | - 33 | 20        |

| ALGI-1- | J4         | - 41 |           |

| ALGI-2  | <b>J</b> 4 | - 7  | 40        |

| ALGI-3  | J4         | - 40 | 60        |

| ALGI-4  | J4         | - 6  | 100       |

| ALGI-5  | J4         | - 39 | 120       |

| ALGI-6  | J4         | - 5  | 140       |

| ALGI-7  | J4         | - 38 | 160       |

\* address is in octal notation

.

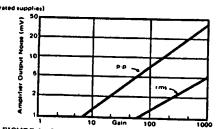

7.0 SPECIAL MODULE DATA SHEETS

Three different versions of analog multiplexer - A/D Converter

PC board sub-assemblies are used:

1) Burr-Brown - SDM853, used in Model D Data Sets only

2) Analog Devices - AD363KD AIS, with Intel 1702A EPROM; used in Model D Data Sets only.

2) Analog Devices - AD363KD AIS with Intel 2716 EPROM; used in Model E Data Sets only.

Two EPROMs are used for MW1 address programs: the Intel 1702 and 2716 (data acces speed is not a problem, just about any 1702 or 2716 will work). The EPROMs are located on the A/D board because of the chip 24 pin package. When Model D Data Sets are installed in a rack, be sure that the EPROM program is appropriate for the rack location. This consideration does not apply to the Model E Data Sets because the 2716 EPROM contains programs for all racks.

Data Sheets for these devices follow.

# FIGURE 1: CONTINUED

FIG. 2 ANTENNA TIMING OPERATIONS

CENTRAL TIMING OPERATIONS

FIGURE 4: DATA SET COMMAND AND MONITOR DATA AND DATA REQUEST MESSAGE FORMATS

NO FURTHER ACTION

FIG. 5 DATA SET LOGIC FLOW DIAGRAM

| (D210)<br>(D220)<br>(D230)                                                                                                                                                                                                                                                           | 0.000<br>-0.885<br>-4.630<br>5.145<br>3.615  | 1.095<br>-0.455<br>4.490<br>-4.275<br>0.000<br>3.450                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DR WORD<br>0.000<br>1.545<br>7.470<br>3.535                                                                                                                                                                                                               | 1 DCS=12<br>3.485<br>0.000<br>0.000<br>-7.510<br>4.240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -7.520<br>0.990<br>0.095<br>6.295                       | -0.985<br>0.005<br>4.640<br>0.100<br>5.815<br>0.005 | -0.895<br>7.465<br>1.065<br>4.130<br>6.150<br>0.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MW-1                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|