VLA Technical Report No. 64 Synthesizer Control Module, Type L16

Paul Harden 12/15/86

"The untold story of the FLUKES in the VLA System."

- 1.0 Introduction

- 1.1 Purpose

- 1.2 MLO/Synthesizer System Overview

- 2.0 Brief Functional Description

- 2.1 Module DCS Addressing

- 2.2 Command Processing

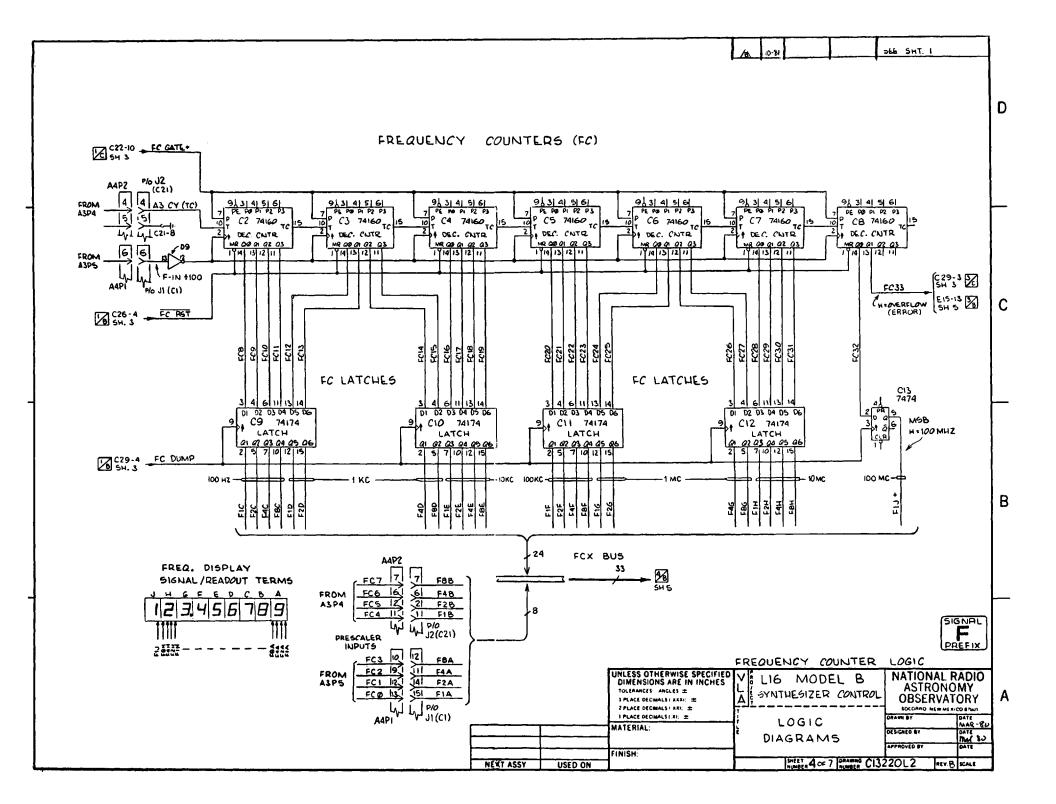

- 2.3 Frequency Counter

- 2.4 1-Second Gating and Time Base

- 2.5 Update Sequencing

- 2.6 Monitor Data Actions

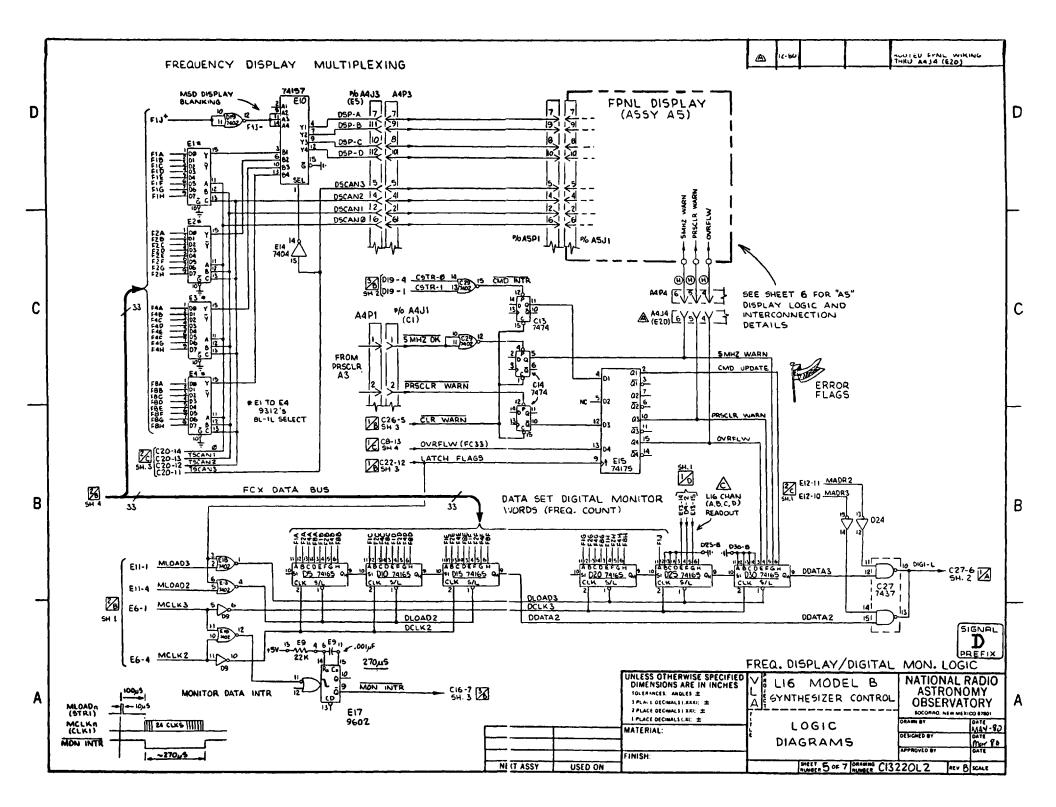

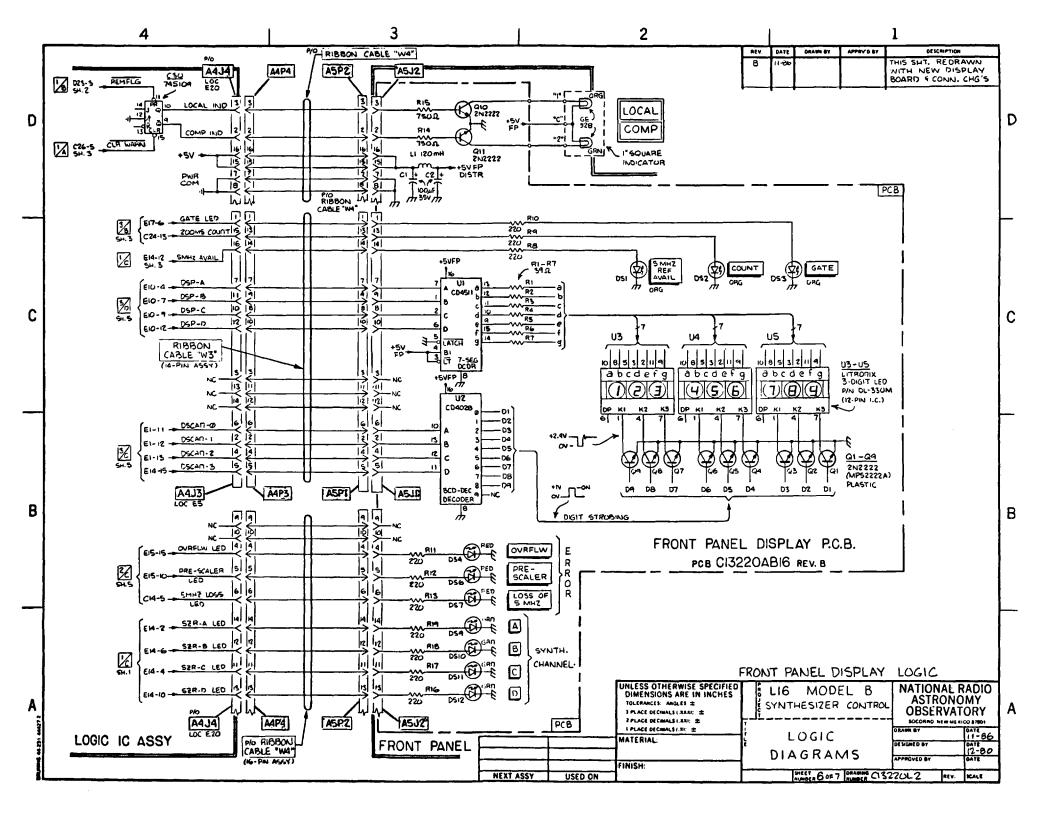

- 2.7 Frequency Display

- 2.8 Error/Status Flags

- 3.0 Detailed Circuit Analysis

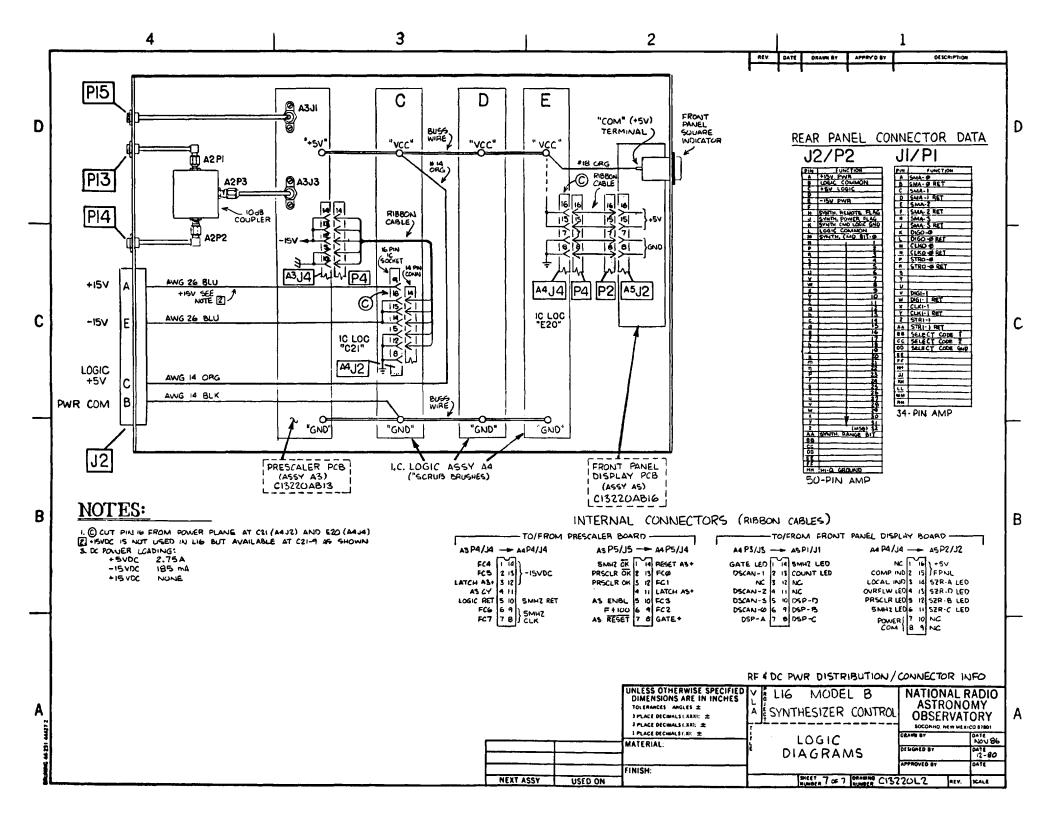

- 3.1 Module Interconnections and Specifications

- 3.2 Module Selection/Addressing

- 3.3 5 Mhz Time Base

- 3.4 Command Loading

- 3.5 Frequency Counter

- 3.6 Update Sequencing & Control Logic

- 3.7 Monitor Data Processing

- 3.7.1 Command Echo Logic

- 3.7.2 Frequency Count Monitor Logic

- 3.8 Frequency Display Logic

- 3.9 Error Flags and Status

4.0 List of L16 Drawings

5.0 List of MLO Drawings

## LIST OF ILLUSTRATIONS

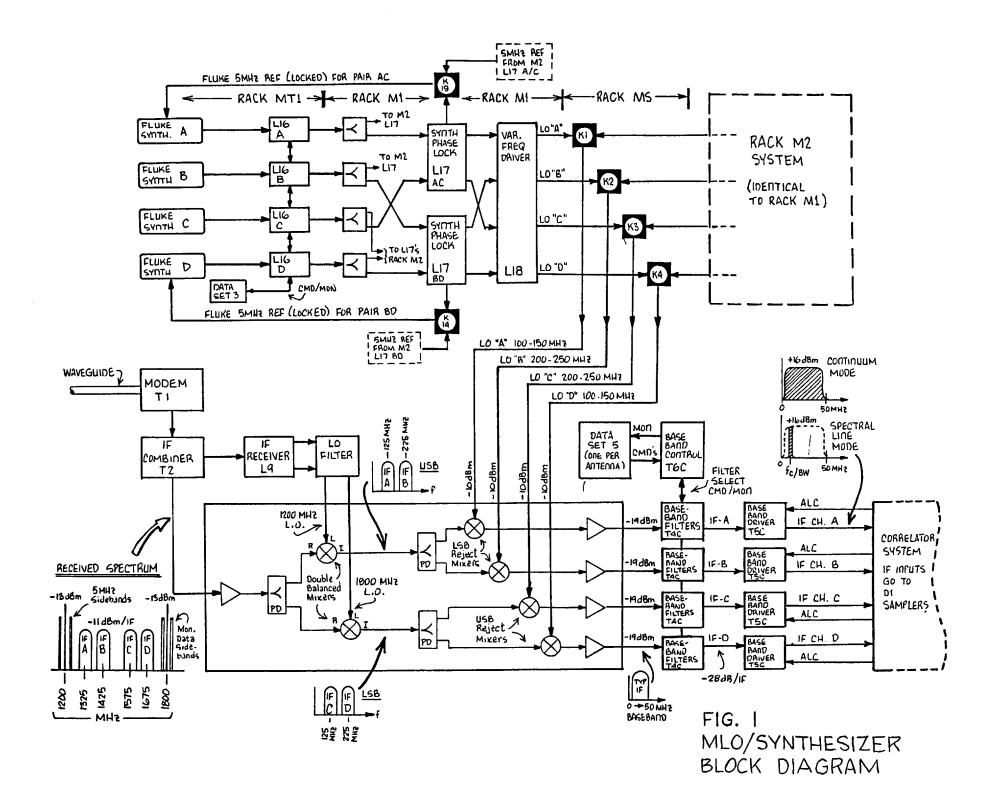

| Figure 1 -   | MLO/Synthesizer Block Diagram                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

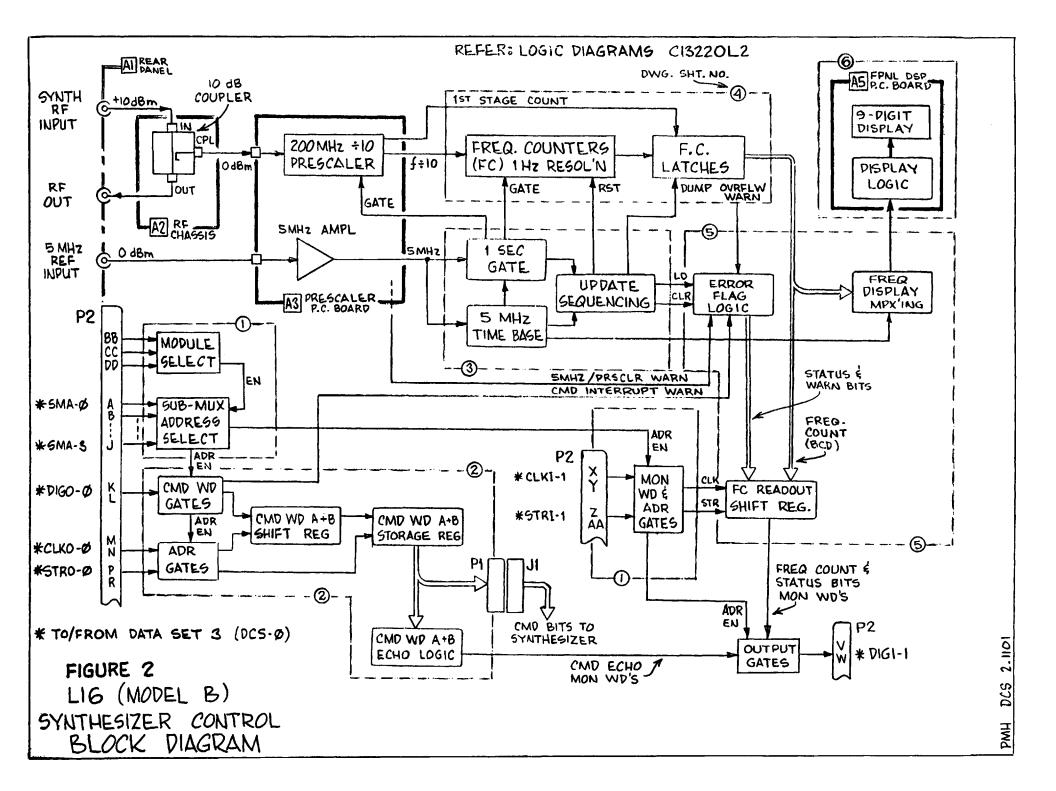

| Figure 2 -   | L16 Block Diagram                                                                                                                                                                      |

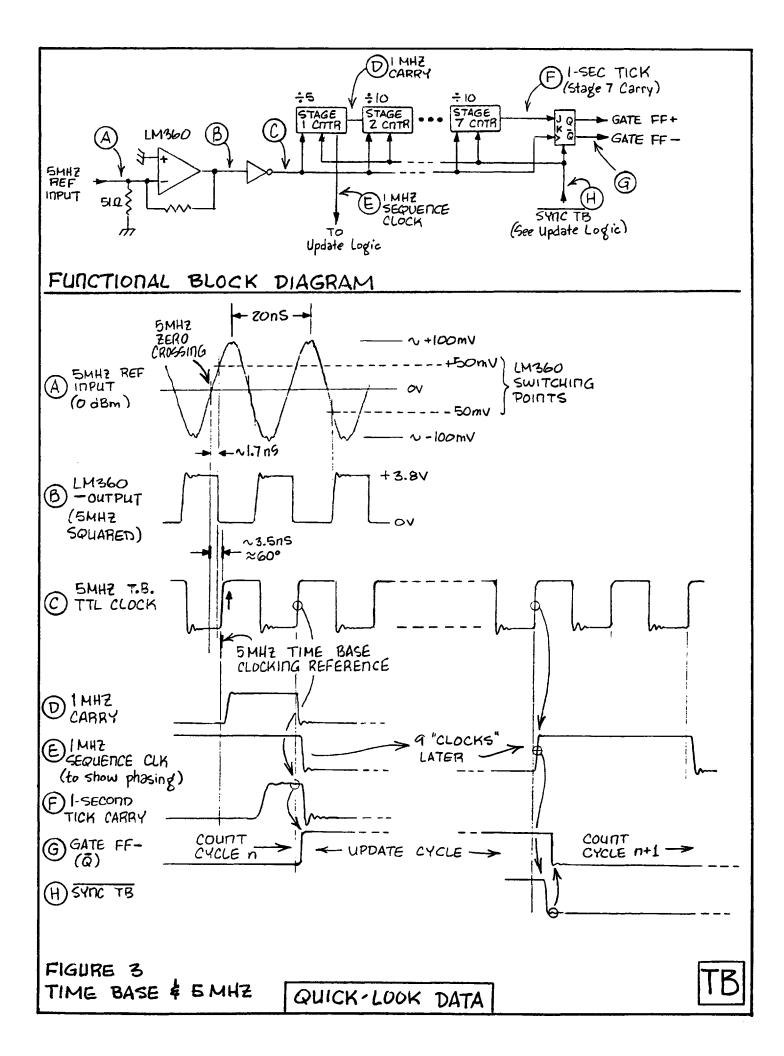

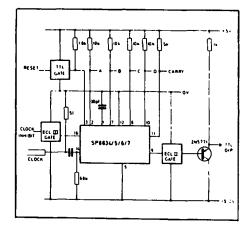

| Figure 3 -   | Time Base Logic & Waveforms                                                                                                                                                            |

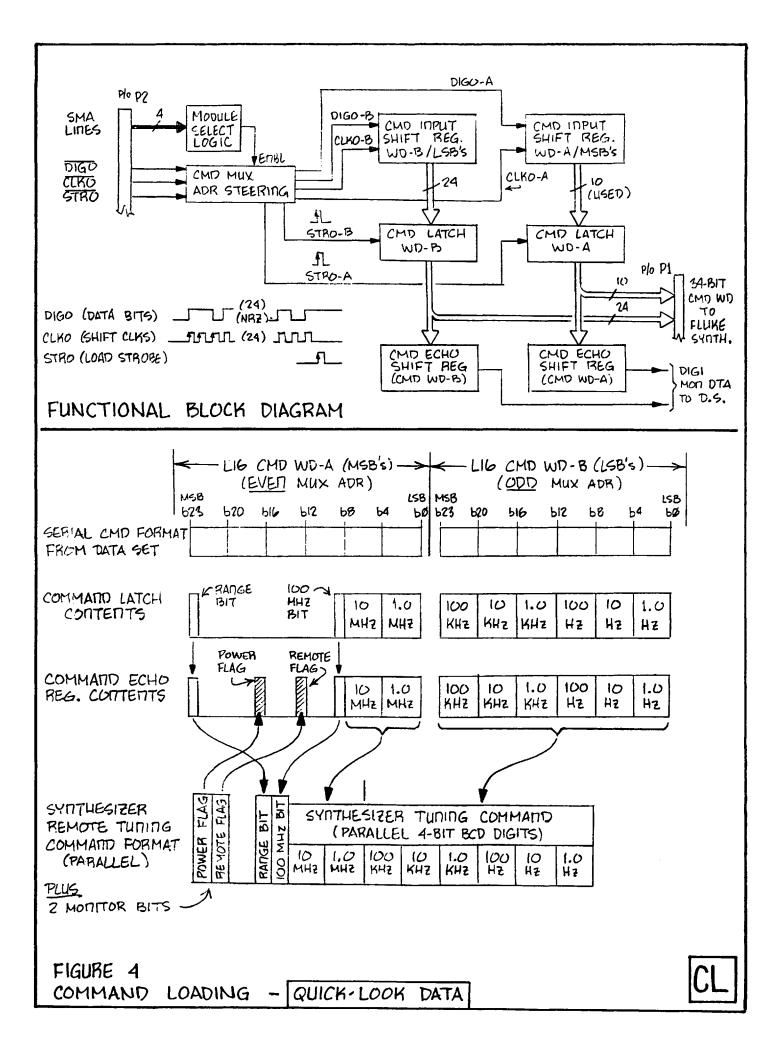

| Figure 4 -   | Command Loading                                                                                                                                                                        |

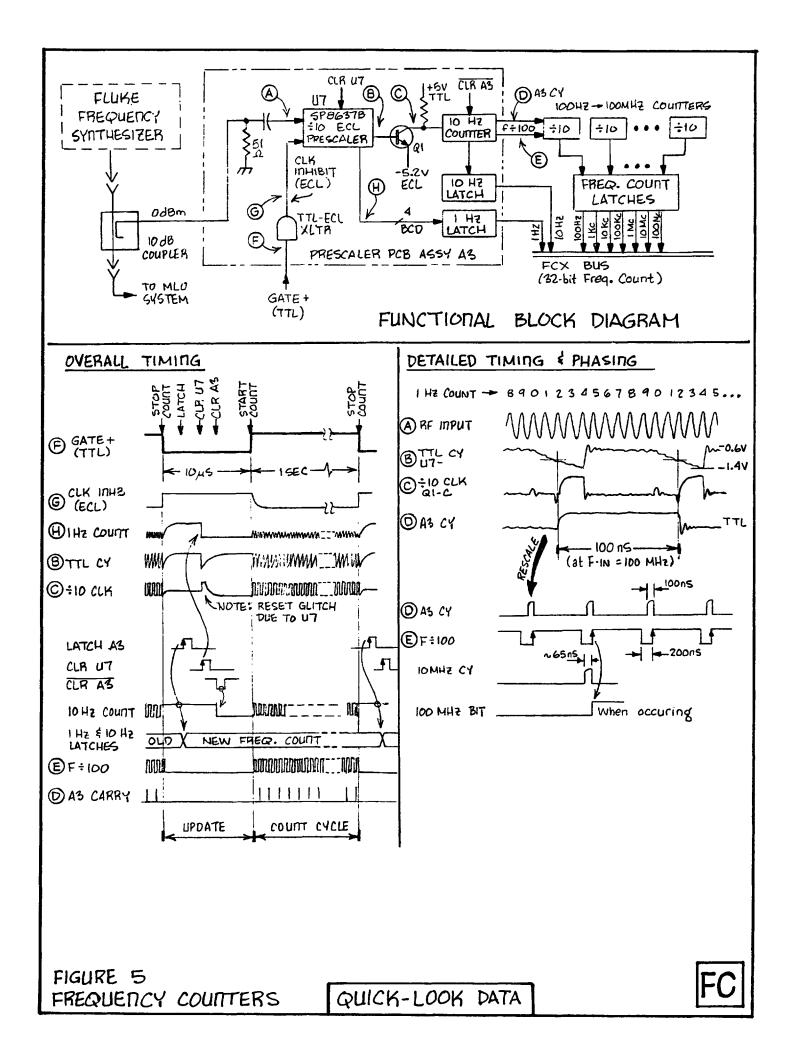

| Figure 5 -   | Frequency Counters & Waveforms                                                                                                                                                         |

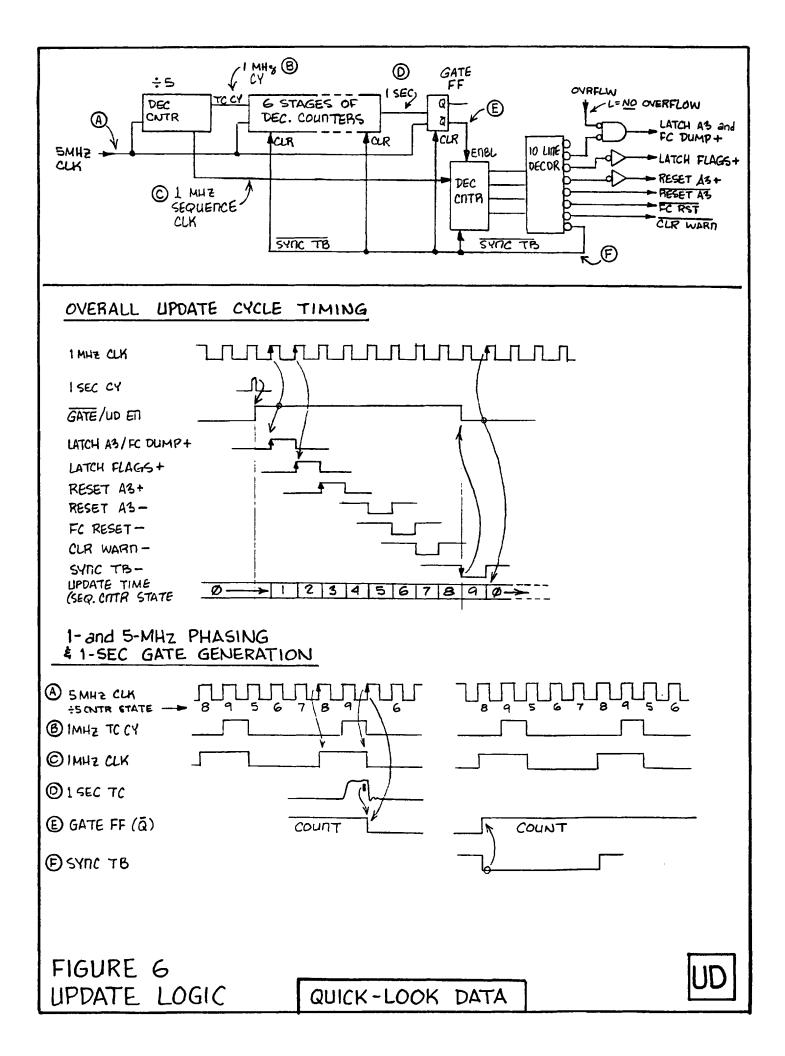

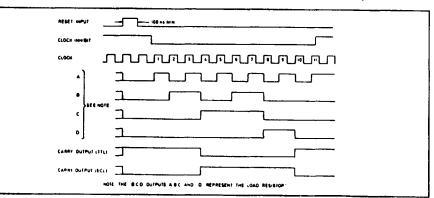

| Figure 6 -   | Update Logic & Waveforms                                                                                                                                                               |

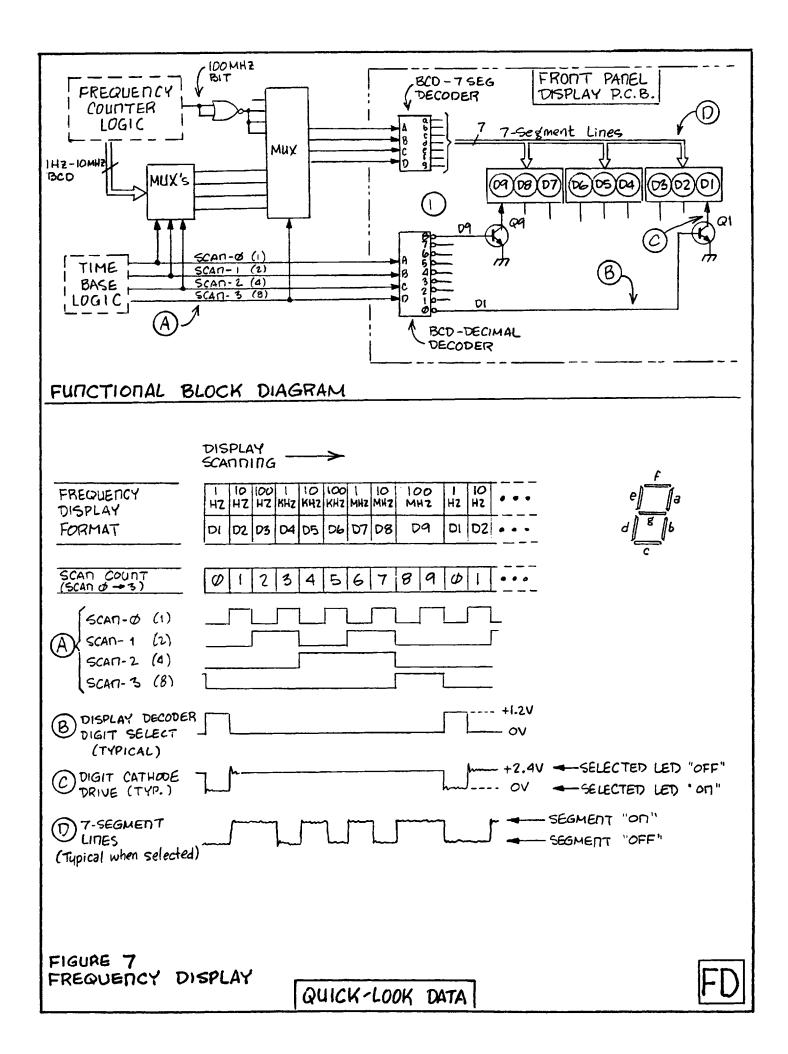

| Figure 7 -   | Frequency Display Logic & Waveforms                                                                                                                                                    |

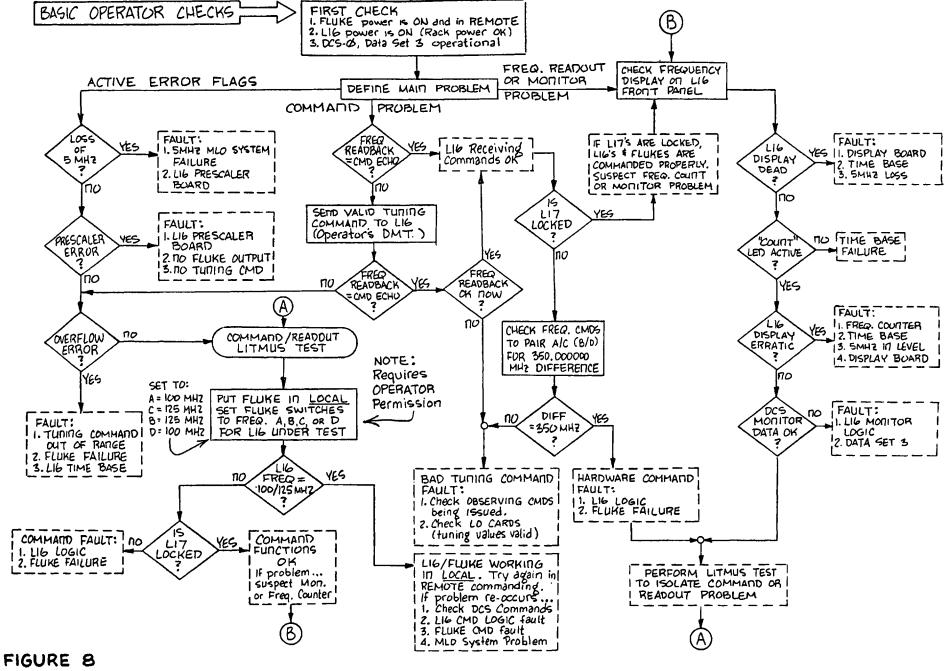

| Figure 8 -   | Troubleshooting Tree                                                                                                                                                                   |

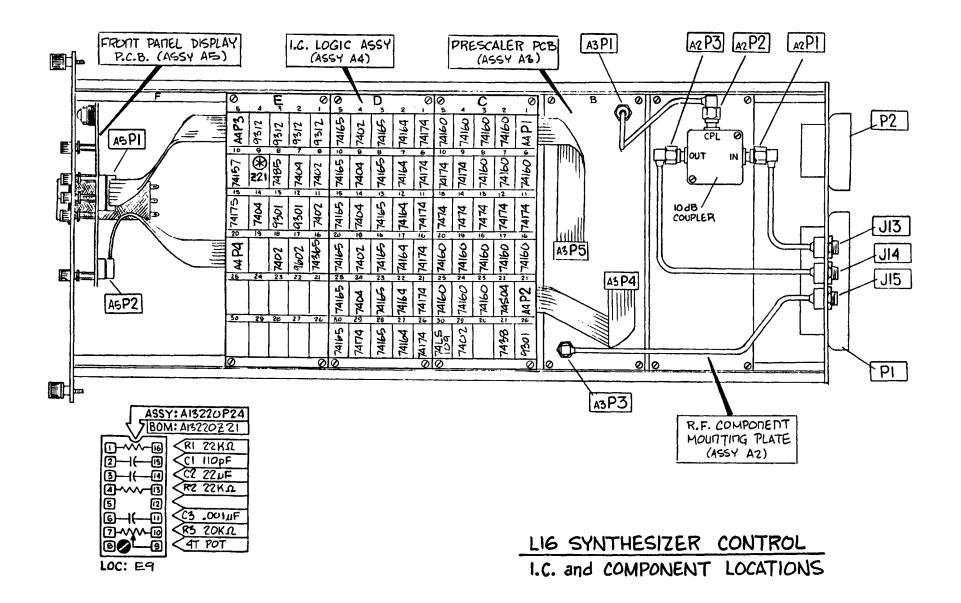

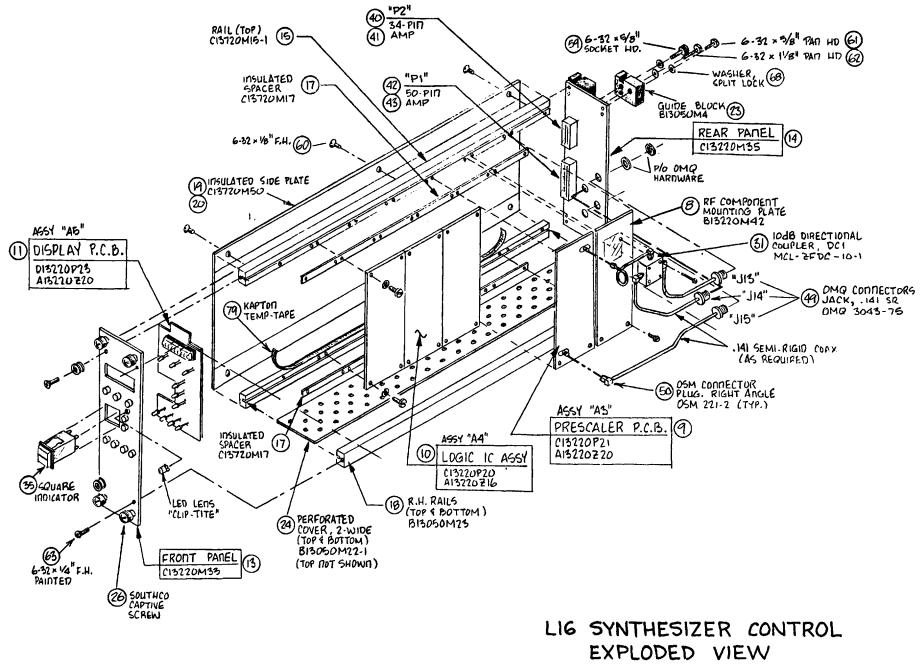

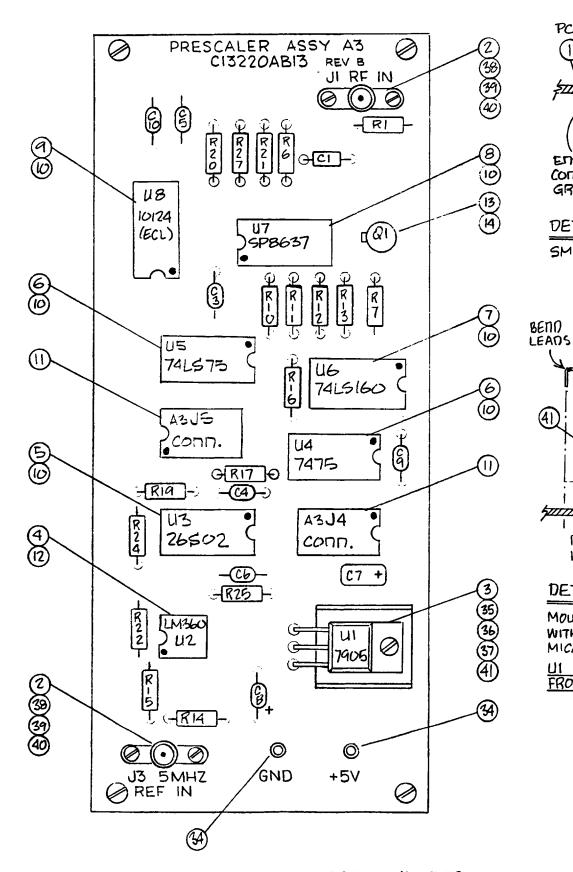

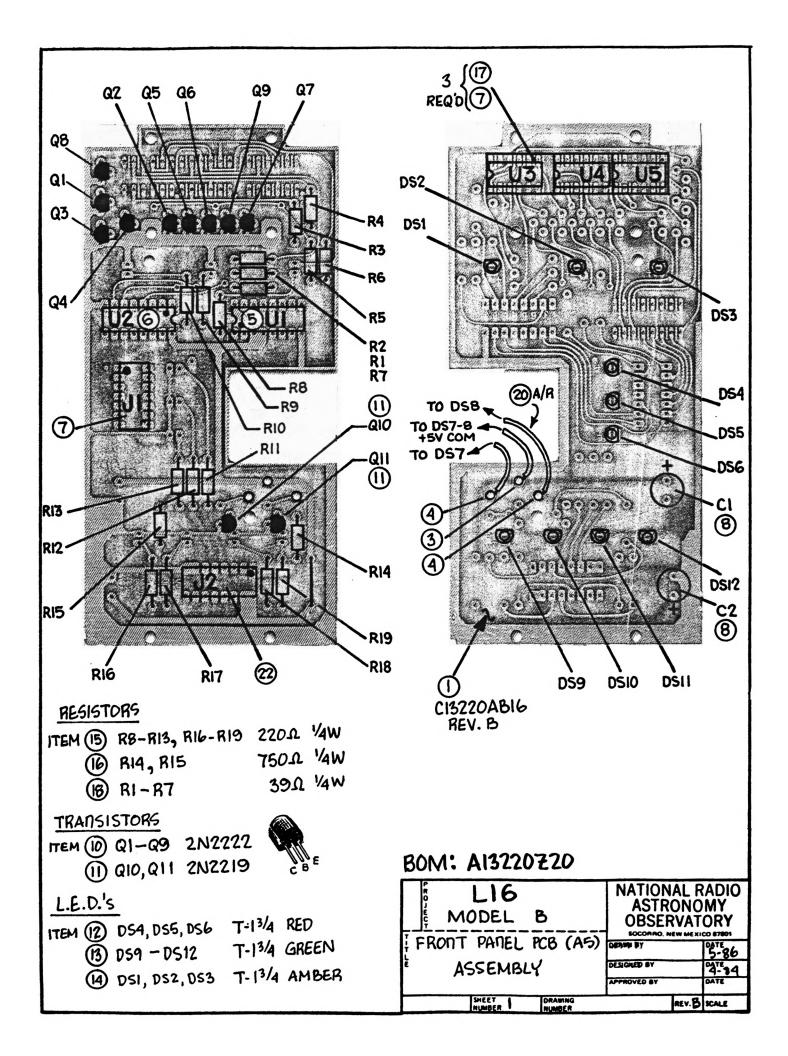

| Appendix 1 - | Ll6 Drawings<br>Logic Schematic Diagram<br>Exploded View<br>Top Assembly BOM<br>I.C. & Component Locations<br>Ass'y A3 Prescaler PCB Assembly/BOM<br>Ass'y A5 Display PCB Assembly/BOM |

| Appendix 2 - | Special Component Data Sheets<br>SP8637B Prescaler I.C.<br>DL330M 3-Digit LED I.C.<br>MCL 10 db Coupler                                                                                |

#### 1.0 INTRODUCTION

This manual describes the operation of the Model B Synthesizer Control module, type L16. Functional and detailed circuit analysis serve as а troubleshooting guide in performing Pertinent component data sheets, corrective maintenance actions. assembly drawings, **Bill** of Materials, etc provide further maintenance information and construction data should additional L16's (over the existing ten units) be someday required.

The System Overview (Sect 1.2) presents a brief description of the synthesizer portion of the Master Local Oscillator (MLO) system, the generation of LO'S A, B, C, D, and the differences existing between the two synthesizer systems in Racks MT-1 and MT-2. This is presented to place the system in proper context and thus offer the role. purpose and design considerations of the L16's in proper perspective.

#### 1.1 PURPOSE

The Synthesizer Control Module L16 provides the Monitor and Control interfacing required for remote frequency tuning and monitoring of the Model 6160B Fluke Synthesizers by the Central Computers via the DCS System. The four primary functions of the L16 are:

a) Formatting standard DCS serial command data into the 36 bit parallel "latched" tuning commands required by the Fluke Synthesizers for remote operation.

- b) Command "echo" readback for command word verification.

- c) Real-time 9-digit frequency counter of the Synthesizer RF output for both local display and DCS monitor data.

- d) Various status and error monitor reporting.

The Command Echo and Frequency Counter data is used by the MODCOMP Control Computers to confirm proper tuning of the Flukes as a result of the most recent commanded frequency to ensure proper operation of this segment of the MLO System. In Spectral Line and Polarization mode observations., proper setting of the four Flukes, within 2 Hz, is of paramount importance as this establishes the final IF-to-baseband conversion prior to correlation.

1

There are eight Fluke Synthesizers and associated L16 modules, one for each Fluke, physically located in Racks MT-1 and MT-2 as follows:

<u>Rack MT-1</u> contains four sets of Ll6's/Fluke Synthesizers, labeled Channel A, B, C and D. This is the primary local oscillator source for the VLA LO/IF System in the Central Electronics Room. The Fluke RF outputs are routed through their respective Ll6, sent to power dividers in Rack MS for equal distribution to the MLO electronics in Racks M-1 and M-2, with RF relays in Rack MS selecting either Rack M-1 or M-2 as the "Master" LO System. Rack MT-1 also contains Data Set 3 (DCS-0) serving the Ll6's in both MT-1 and MT-2 racks.

<u>Rack MT-2</u> contains four sets of L16's/Fluke Synthesizers, labeled Channels AA, BB, CC, and DD to distinguish these four channels from MT-1. This rack serves the dual-role of providing the local oscillator signals required by the VLBA observing equipment plus as a ready backup for the VLA in the event of a Rack MT-1 failure. Additionally, Rack MT-1 Flukes can be selected by various VLA antenna D-Racks as an alternate source of LO for split-IF operation. The L17 Synthesizer Phase Lock modules and associated electronics are identical to the Rack MT-1, M-1/M-2 arrangement, except these modules are physically located in Rack MT-2 to form a second, self-contained MLO system.

The Fluke Synthesizers in Racks MT-1 and MT-2 are thus both under computer control for remote frequency tuning and monitoring through their respective L16 control modules.

## 1.2 MLO/SYNTHESIZER SYSTEM OVERVIEW (Fig 1)

The VLA antennas provide four IF channels of astronomical data, called IF's A, B, C, and D, each being 50 Mhz in bandwidth. In Continuum Mode, the distributed power across the 50 Mhz band is In Spectral Line Mode, a specific frequency of much of interest. narrower bandwidth, located within the 50 Mhz IF, is the signal interest with all other signals to be rejected. of In Mode IF's A and B contain right-hand circularly Polarization polarized signals, while IF's C and D contain the left-hand polarized signals. The role of the Central Electronics LO/IF system is to convert these four IF's to 0 - 50 Mhz baseband (video) analog data for the Samplers and Correlator in the Screen This must be accomplished to accomodate the desired mode Room. Spectral Line, Polarization) while preserving (Continuum, the phase characteristics of the signals within nano-second accuracy.

These four IF's emerge from the T1 Modems in the 1.3-1.7 Ghz passband with the same spectral distribution as they left the antenna. Two levels of conversion follow, both being performed by the Baseband Converter module, type T3. Conversion to UHF occurs by mixing IF's AC with 1200 Mhz to produce 200-250 Mhz while IF's BD are mixed with 1800 to produce 200-250 Mhz. То accomplish the final 0-50 Mhz conversion, the LO signals must mix with these two ranges to produce IF's with a center frequency of 25 Mhz, being half the bandwidth. LO values would thus be 125 Mhz and 225 Mhz, and indeed these values are used for Continuum Mode baseband conversion when the full 50 Mhz bandwidth is desired. However, for Spectral Line Mode, it is desireable to be able to select any portion of each of these four IF passbands as center frequency and filter out narrower bandwidths for the increased selectivity and reject unwanted signals. The resultant narrow bandwidth signal coincides with the precise spectral-line For this reason, the local oscillator required for of interest. final IF-to-baseband the conversion must be variable in Slewing the center frequency along the frequency. four IF passbands to match the various bandwidth filters is the primary function of the four Fluke Synthesizers; a tunable LO in the ranges of 100-150 Mhz (for If's AC) and 200-250 Mhz (for IF's BD) in 2 Hz steps under computer control.

The UHF converters in T3 produce composite IF AC being upper side band (USB) and IF BD being inverted lower sideband (LSB) as a result of the 1200 and 1800 Mhz LO. Considering IF AB, the composite signal is applied to two USB-rejection mixers so that the desired sideband is selected and the unwanted image substantially rejected. Mixer outputs are the 0-50 Mhz baseband desired, with Fluke Synthesizers A and B being the LO source (indirectly). In a similar manner, IF's CD are applied to USBrejection mixers, producing two baseband outputs, Fluke C and D being the LO source.

four A, B, C, D basebands are amplified and sent to The Baseband Filter modules, type T4, one for each IF, where the final analog filter to establish the desired bandwidth, down to 0.098 Mhz is accomplished. Filter selection is under computer control using pin-diode switches to select one-of-eight octave step filters. Filter select commands are decoded and distributed to the proper filter modules for Baseband Control Module T6C, one for each antenna/D-Rack. The pin-diode arrays and filters are in the T4 Baseband Filter Modules, whose output are further amplified by Baseband Drivers, type T5C, and sent to the Samplers in the Correlator Room. The T5'C, one for each IF, also generates the ALC used by the Samplers for level control. Thus through the actions of the Fluke Synthesizers and Baseband Control and Filter modules, precise center frequency tuning and selectable bandwidth filtering is accomplished and coordinated under computer control via the DCS System. The Flukes/L16's are serviced by DCS-0, Data Set 3 and the filter selection through Data Set 5 of the associated DCS Channel.

The output of the Fluke Synthesizers are not sent to the four T3 Converter modules (per antenna) directly. The outputs are processed by Synthesizer Phase Lock modules, type L17, one for

synthesizer pair AC, another for pair BD, to ensure these LO pairs are phase-locked to the MLO to support polarization mode In polarization mode, IF A is the RH polarization observing. signal, with the corresponding LH polarization signal being IF C. Note the sum difference between A (100-150 Mhz) and C (200-250 Mhz) is always 350 Mhz. Polarization analysis requires the phase coherence between A (RH pol) and C (LH Pol) signals to be maintained within a fraction of a cycle with a 350 Mhz +/- 2 Hz To preserve this phase, the local oscillator sum difference. signals AC must likewise be properly phased. The same is true for IF B (RH pol) and D (LH pol) pairs.

The Synthesizer Phase Lock modules L17 perform two major functions:

1. Since the Fluke Synthesizers can not tune above 160 Mhz, and LO's B and C must be tunable over 200-250 Mhz, the L17 performs the frequency doubling required to LO B and C. The Flukes are tunable with a 1 Hz accuracy; however this accuracy is multiplied to +/-2 Hz through the frequency doublers. LO signals A and D are not modified by their respective L17's.

2. LO AC phase locking is performed by a portion of the A and 'Cx2 signal being applied to a mixer to produce the 350 Mhz sum signal. Phase referenced 50 Mhz is multiplied x7 by the L17 to form a 350 Mhz reference. This reference and the 350 Mhz AC sum is compared, the resultant difference an error signal driving a 5 Mhz VCXO phase-locked oscillator loop. This phase-locked 5 Mhz is sent to the "A" Synthesizer as the external 5 Mhz reference.

(The L17 for channels BD functions in an identical manner).

The B and C Fluke Synthesizers receive 5 Mhz external reference from the MLO system (un-locked), while the A and D Flukes receive their external 5 Mhz reference from the phase adjusted 5 Mhz their respective L17's. output from Any phase difference occurring in either the AC or BC Synthesizer pair output, or in the external 5 Mhz Synthesizer reference, will produce a 350 Mhz phase error signal in the L17. The action of the phase-lock 5 Mhz VCXO will immediately compensate for the phase to null the Thus, even though separate synthesizers are used to error. generate four tunable LO's, the AC and BD signals to the T3 Baseband Converters are always maintained at the 350 Mhz +/- 2 Hz sum difference with the phase relationship always known. This scheme also virtually eliminates all relative phase noise and spurious mixer products.

The outputs from the L17's, A, Bx2, Cx2, and D, are amplified by Variable Frequency Driver module L18. In VLBI Rack MT-2, the L18 outputs feed the various distribution loads directly. In Rack MT-1, the Fluke synthesizer output are split by power dividers and supplied to two sets of L17's simultaneously; one

set in M1, another set in Rack M2. The outputs of the L18 Drivers in both M1 and M2 Racks are inputs to RF relays. Both M1 and M2 racks are processing the Synthesizer signals, with all L17's "locked up". The RF relays determine which system, M1 or M2 is used for the "on-line" MLO. Relay outputs of LO's A, B, C, D, are sent to power dividers for distribution to each D Rack/T3 Baseband converters. The "off-line" rack LO signals are terminated into 50 ohm loads by the relays to simulate system loading.

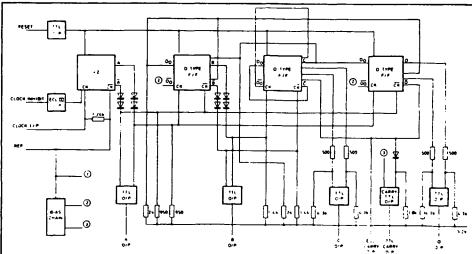

## 2.0 BRIEF FUNCTIONAL DESCRIPTION (Fig. 2)

This section presents a brief functional description of the logic and circuitry of the L16, with the sub-sections organized by the primary functions of the module. Detailed circuit analysis for troubleshooting is in Section 3. See Figure 2.

#### 2.1 MODULE DCS ADDRESSING

There are eight 116's serviced by DCS-0, Data Set 3. The Command and Monitor Sub-mux addresses (SMA's) are listed below:

|                       | MT-1 Rack L16's |       |      |        | MT-2 Rack Ll6's |        |        |     |  |

|-----------------------|-----------------|-------|------|--------|-----------------|--------|--------|-----|--|

| Channel>              | Α               | В     | С    | D      | AA              | BB     | CC     | DD  |  |

| Commands:             |                 |       |      |        |                 |        |        |     |  |

| Synth Cmd Wd A        | 320             | 322   | 324  | 326    | 340             | 342    | 344    | 346 |  |

| Synth Cmd Wd B        | 321             | 323   | 325  | 327    | 341             | 343    | 345    | 347 |  |

| Data Set Cmds:        | DIGO            | -0 CL | KO-0 | STRO-0 | DIGO-           | 1 CLKO | -1 STR | 0-1 |  |

| Outputs Mon:          | DIGI            | -0 CL | KI-0 | STRI-0 | DIGI-           | 1 CLKI | -1 STR | I-1 |  |

| Monitor Data:         |                 |       |      |        |                 |        |        |     |  |

| Cmd Wd A Echo         | 220             | 222   | 224  | 226    | 240             | 242    | 244    | 246 |  |

| Cmd Wd B Echo         | 221             | 223   | 225  | 227    | 241             | 243    | 245    | 247 |  |

| Synth Freq (1-100Mhz) | 230             | 232   | 234  | 236    | 250             | 252    | 254    | 256 |  |

| Synth Freq (1-100Khz) | 321             | 233   | 235  | 237    | 251             | 253    | 255    | 257 |  |

The command and monitor addresses shown above are selected by the states of the four SMA lines during the proper command or monitor time of the Data Set. The LSB (SMA-0) and MSB (SMA-3) specify the proper function within the L16 (i.e., whether the MSB or LSB of the command or monitor word), while address lines SMA-1 and SMA-2 identify the proper L16. Coding is provided by hard-wiring of the bin connector, which "programs" the L16 response address and illuminates the proper ID LED on the front panel. The SMA lines and the monitor and command data, clock and strobe lines are daisy chained to all eight L16's, with only one module responding as a result of this channel address coding.

#### 2.2 COMMAND PROCESSING

The Fluke Synthesizers require a steady-state 34-bit parallel TTL command word for remote tuning. This word is eight BCD (32 bits) defining the 1-Hz to 10 Mhz digits, a 100 Mhz bit, and a 1-12 Mhz or 10-160 Mhz range bit. This 34 bit tuning command is derived from two DCS 24-bit serial commands from the Data Set. The commands are serially loaded into shift registers by Data Set terms DIGO (data), CLKO (load clocks) and STRO (terminating load strobe). The load strobe stores the command into a latch for static storage. This latch, requiring two serial commands to specify the full Fluke Synthesizer command, is sent to the Fluke remote frequency command connector. The latch output is also loaded into a paralel in/serial out shift register for command echo readback to accomplish a bit-for-bit verification that the frequency command was correctly received. The storage latch is used to store the tuning command for long periods, as Fluke tuning commands are normally infrequently issued by the control computers only during source changes.

## 2.3 FREQUENCY COUNTER

To verify proper frequency setting of the Fluke Synthesizers over its useful range, a frequency counter is provided to match the 1 Hz resolution required. The Fluke +10 dbm output is routed through a 10 db coupler in the L16, providing 0 dbm of RF for the frequency counter stages. This coupled signal, in the nominal range of 100-150 Mhz, is applied to a divide-by-ten high speed ECL digital prescaler IC. The divide by ten ECL output is buffered to TTL and used to clock the following eight stages of TTL decade counters, enabled over a precise 1-second gating period. This forms a nine-digit frequency count to 160 Mhz (the maximum Fluke setting) in 1 Hz steps. The BCD count of the forms the least significant1-9 Hz digit. prescaler IC the subsequent stages forming the 10 Hz to 100 Mhz BCD digits. The frequency count is formatted for DCS monitor word readout and local LED display, as discussed in 2.5 and 2.6.

#### 2.4 1-SEC. GATING AND TIME BASE

The time base is driven by an external 5 Mhz sinusoidal signal from the MLO system, 0 dbm nominal, which is converted to a TTL clock by an LM 360 differential comparator. The time base establishes the 1-second gate period and provides clocks and discrete timing terms to the update (housekeeping) and LED multiplexed display logic. The 5 Mhz clock is applied to seven stages of TTL decade counters producing a 1-second terminal count used to clock the GATE flip flop OFF. When GATE is off, the frequency counter is halted, a binary counter is enabled to sequence through the various update terms to latch the frequency count, and upon completion, clocks the GATE on to begin another 1-second counting period. Display multiplexing is pulled off the

10 Khz stage to form the LED scanning terms.

The time base is basically free-running during both the 1-sec. count period and the 10 usec update period, synchronized to a count of zero at the end of the update cycle. Synchronization to "re-start" the time base to the 5 Mhz external input ensures a consistent gating period to compensate for propagation delays reducing frequency counter inaccuracies due to time base errors. Since a 5 Mhz one-half cycle error can easily cause a 10-Hz error in the frequency count, or a one-digit error. Synchronization keeps the count error within +/- 3 Hz and consistent to avoid last digit flickering.

#### 2.4 UPDATE SEQUENCING

the termination of the 1-sec GATE counting period, At the frequency count is latched into registers to drive the local LED display and to be ready as monitor data when polled by the Data Set. Data Set monitor data polling (and command transmissions) are asynchronous to the L16 functions. Once the frequency count and flags are latched, the next count period is immediately A new tuning command is processed by the L16 and commenced. Fluke to "settle out" at the new frequency in less than a second. Keeping the update sequencing cycle at less than 10 usec between count cycles ensures that while the Fluke output is slewing to a new frequency, no more than two count cycles will be contaminated by an erroneous count; the third cycle will be stable for the control computers to read for new tuning command verification.

The update actions are as follows in the order of their occurrance:

- 1. HALT the GATE enable flip flop.

- 2. HALT the Prescaler IC counter, then remaining frequency counter stages.

- 3. LATCH the Prescaler 1-9 Hz count. (if no overflow)

- 4. DUMP remaining count stages into latches. (if no overflow)

- 5. LATCH flags (command interrupt, 5 Mhz OK, Prescaler warning, Overflow and frequency slewing.

- 6. RESET Prescaler IC and frequency counter stages to zero.

- 7. CLEAR error flags. (unlatched flags)

- 8. SYNC Time Base and start next count.

#### 2.5 MONITOR DATA ACTIONS

Four monitor data words are polled from the L16 by the Data Set: 2 words containing the command echo and 2 words constituting the 9 digit frequency count and status flags.

Command echo monitor data is simply a parallel load shift register loaded by the Data Set load (STRI) term to read the contents of the tuning command register. Two DCS monitor words are required to read out the 34 command bits and two status flags (Fluke power ON and local/remote mode switch). The MSB bits in one register are polled by the Data Set during one VLA waveguide cycle, the LSB's polled during the next cycle.

Frequency counter monitor data is formatted in like fashion; two 24-bit parallel-load, serial-out shift registers; one containing the status and 1-100 Mhz count; the second containing the 1 Hz-100Khz count. At the end of each count period, the frequency count latches are updated. The FC latch outputs are the parallel inputs to the monitor word shift registers, being loaded by the Data Set load (STRI) term to the register corresponding to the SMA address. Data Set clocks (CLKI) follow, shifting the count bits to the Data Set. When the Data Set polls either of the monitor word shift registers, a Monitor Data Interrupt term is generated that halts the update sequencer, if active, for the duration of the data shifting operation. Halting the update actions ensures the frequency counter latches will not be updated while actively shifting out monitor data since the Data Set timing and L16 sequencing is asynchronous. Monitor data shifting does not interrupt the time base when in the frequency counting cycle.

The status flags Overflow, Prescaler warning, 5 Mhz warning and Command Update are loaded by the STRI load term to the shift register containing the most significant frequency count.

#### 2.6 FREQUENCY DISPLAY

The frequency counters are BCD counters, each stage being one The eight frequency counter stages are stored into FC digit. latches at the end of the counting cycle. The FC latch outputs, in addition to loading the monitor word shift registers, is also routed to a bank of 4 bit multiplexers to select one of eight digits plus the 100 Mhz bit. The selected digit and multiplexer address is sent to the front panel LED display logic to drive the 9 digit scanning LED numeric displays. The LED readout thus provides the full frequency count resolution of 150 Mhz +/- 1 Hz. The front panel display is primarily for local indication and control of Flukes, the same frequency of the display being the same count read by the Data Set as monitor data for remote monitoring and control.

#### 2.7 ERROR/STATUS FLAGS

Various status and error events are captured to monitor and report the operation of the L16 and associated Fluke, summarized below:

1. PWR FLAG indicates the Fluke Synthesizer is on and power supplies within operating range.

2. REMOTE FLAG indicates the Fluke Synthesizer mode switch is selected to remote commanding. If in Local mode, DCS commands through the L16 will be ignored. (note: power and remote flags are part of the Command Echo word).

3. 5 Mhz WARNing is activated upon loss of or insufficient level to drive the time base. It indicates the time base and hence the frequency counters are not running and the count values are not being updated. This error illuminates a front panel LED.

4. PRESCALER ERROR is generated by the Prescaler Board upon loss of prescaler output being in the 100-150 Mhz range. This indicates loss of or incorrect Fluke Synthesizer RF output due to a Fluke failure, a frequency outside the normal system 100-150 Mhz range, or failure of the prescaler IC. This error illuminates a front panel LED. When active indicates the frequency count is erroneous.

5. OVERFLOW is generated by the Frequency Counters when a count of 200 Mhz or greater is reached to indicate obvious malfunction in the frequency counter. This error illuminates a front panel LED. When active indicates the frequency count displayed is the last good count, as the frequency latches are not updated on Overflow. The frequency should thus be questioned.

6. CMD UPDATE is generated upon receipt of a new tuning command to verify the command was received and that the Fluke Synthesizer output is likely slewing. Indicates the frequency count may be erroneous when active, the duration nominally only a couple of 1-sec count cycles.

All flags are latched during the update cycle, while the capturing circuitry is cleared such that the condition can be re-checked during the next count cycle. Thus temporary and permanent error conditions can be determined.

#### 3. DETAILED CIRCUIT ANALYSIS

This section presents detailed circuit descriptions necessary for the troubleshooting and maintenance of the Ll6. The main function and purpose of this logic is described in Section 2. Refer to the Ll6 Logic Diagram, Cl3220L2 and Prescaler Schematic, Cl3220S12.

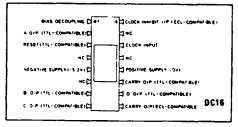

## 3.1 MODULE INTERCONNECTIONS AND SPECIFICATIONS

The L16 requires the following INPUTS:

5 Mhz REF IN - via OMQ P15, Odbm 5 Mhz from the MLO system.

SYNTH RF INPUT - via OMQ P13, +10 dbm 100-150 Mhz from the Fluke Synthesizer. 3. Data Set Interconnections - via P2, the SMA address lines, clocks, strobes and command data line to execute Data Set communications with the L16.

4. Synthesizer Status - via Pl, the Fluke Power and Remote mode flags (part of the Synthesizer Command cable).

The L16 provides the following OUTPUTS:

1. SYNTH RF OUT - via OMQ P14,  $\pm 10$  dbm 100-150 Mhz from the Fluke Synthesizer through the L16 10 db coupler.

2. SYNTH COMMAND CABLE - a multi-wire cable via Pl carrying the 34 bit parallel tuning command to the Fluke remote input connector.

3. MONITOR DATA - via P2, the serially shifted digital monitor data when polled by the Data Set.

NOTE: Fluke Synthesizer RF output is routed through the 10db coupler in the L16. Therefore, an L16 module (or suitable patch between P13 and P14) must be installed for proper system distribution.

The L16 satisfies the following specifications as per Memo, Feb. 21, 1980, L16 Specifications by Larry Beno:

1. Signal Input - 100-150 Mhz nominal into 50 ohm load via OMQ connector, +10 dbm nominal level, with frequency counte operation to 0 dbm sensitivity.

2. External Time Base - 5 Mhz, approximatly 250 mv RMS (0 dbm) sinusoidal input into 50 ohm load via OMQ connector.

Accuracy of Counter - +/- 1 count +/- time base error. Resolution - 1 Hz Display - nine digit numeric LED

4. The L16 shall produce no reflections on inputs and generate system noise within acceptable limits for proper MLO operation.

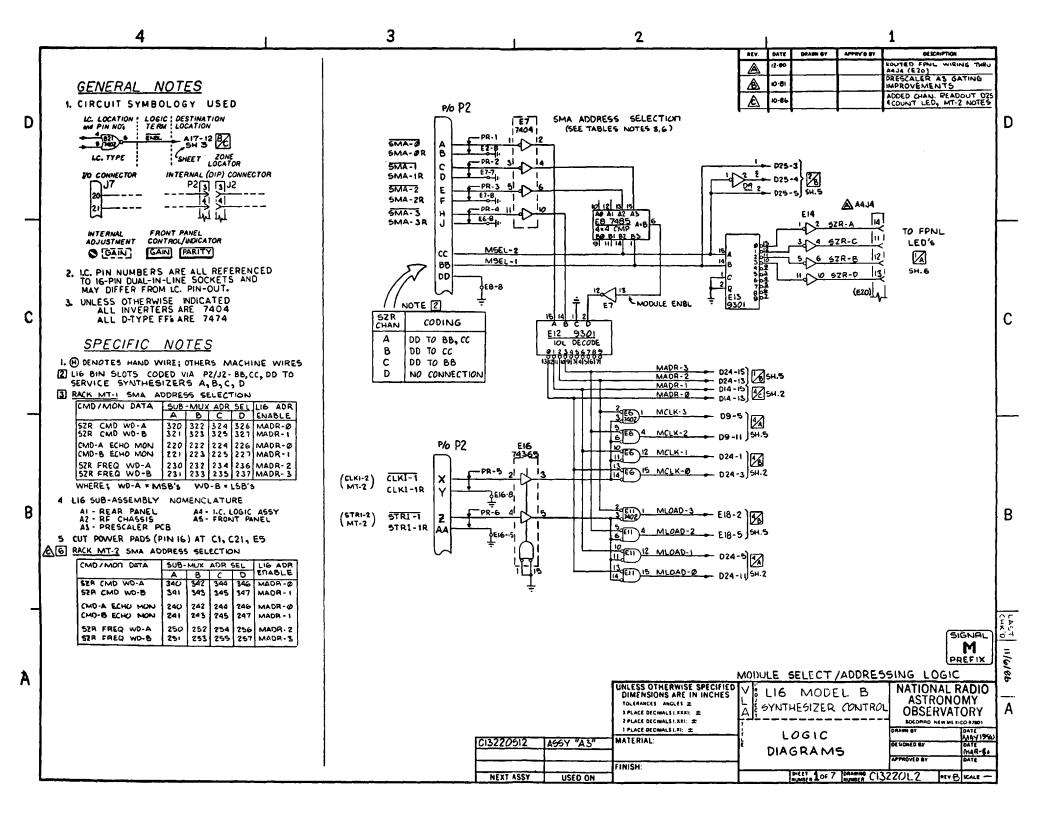

3.2 MODULE SELECTION/ADDRESSING (Logic Diagram Sheet 1)

To ensure only the proper L16 responds to Data Set commands and monitor polling, each L16 is hardwired through the bin connectors to be programmed to execute actions associated with the assigned MUX addresses. SMA address inputs are compared to the hardwired address by digital comparator 7485 E8, producing a MODULE EN term on the receipt of the proper SMA address. SMA lines SMA-0 and SMA-3, with MODULE EN, is decoded by 9301 E12 to produce discrete enabling terms associated with the SMA address. Gates 7402 E6 and E11 further produce enabling to route the Data Set clocks and strobes to the proper devices. SMA address functions are listed in Section 2.1. The hard-wired address drives 9301 decoder E13 to illuminate one-of-four front panel LED's indicating the Channel (A,B,C,D) the L16 is programmed to respond to.

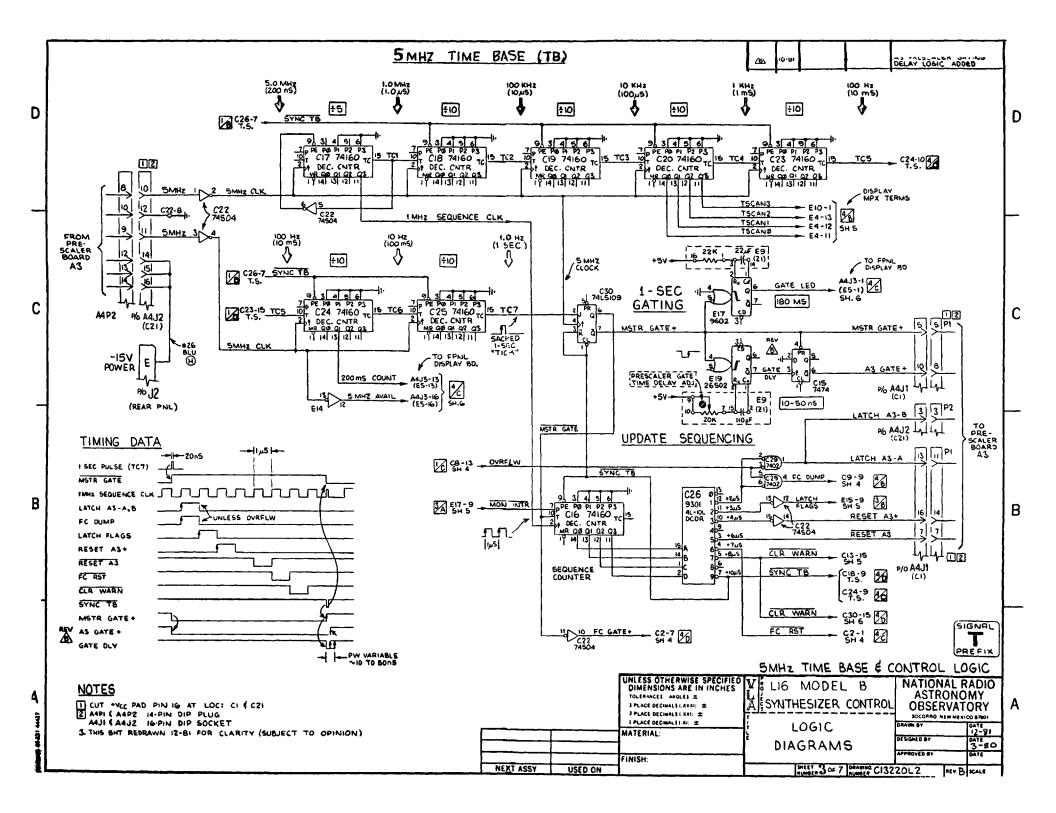

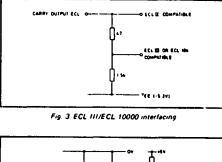

## 3.3 5 MHZ TIME BASE (Sheet 3; Fig 3)

External 5 Mhz input is carried from rear panel OMQ P15 to SMA P3 on the Prescaler Board using .161 Semi-rigid coax. On the Prescaler board, the 5 Mhz is terminated by a 51-ohm resistor, with approximatly 100 mv peak (-10 dbm) applied to the input to high speed comparator LM 360 U2. Loaded LM360 output goes HI at +50 mv input and LO at -50 mv with hysteresis. Rise and fall times are tr = 15 ns and tf = 9 ns. The LO to HI Lm360 output transition occurs at about 30 deg after the zero crossing point, provides consistent switching in relation to the 5 Mhz sinusoidal input. This stability in generating the TTL 5 Mhz clock is important as the 20:1 time base to frequency ratio (5 Mhz :100 Mhz input) produces a 1 Hz count error every 18 degrees of 5 Mhz. The LM 360 stability in comparator performance and temperature stability ( < 5 ns over 0 deg C to 25 deg C) maintains a count accuracy within 3 counts over the worst case signal and temperature operating range.

The (-) LM360 output is the 5 Mhz TTL referenced clock sent to the time base on the logic assembly. The (+) output drives retriggerable one-shot AM26S02 U3b such that loss of 5 Mhz or marginal signal level is detected and reported.

LM360 TTL output enters the logic assembly via ribbon connector A4P2 at IC location C21-10, 11 and inverted by 74S04 (low delay The two inverters C22-2 and C22-4 split the 5 Mhz TTL time) C22. distribution to equalize fan-out loading to keep propagation times as balanced as possible. (Driving all 5 Mhz loads off one 74S04 section approaches the fan-out limit with a very "mushy" rising edge for switching). 5 Mhz is divided by 5 to 1 Mhz by 74160 C17, producing a carry at 1 usec intervals so the following six stages of 74160 are operating at base ten units of one The 74160 stages C19, 20, 23, 24 and 25 are cascaded and second. clocked by 5 Mhz. The terminal count (TC) at 74160 C25-15 occurs on the rising 5 Mhz edge at 1.000000 sec. +/- 5 ns, being < 20 ns in duration, and captured by 74LS109, the master GATE FF. Though the 1 second period has been reached, the time base is allowed to continue providing a 1 Mhz clock to the input sequencer (see Sect 3.6) and display multiplexer terms (to avoid blanking of the display during the update cycle).

The Prescaler IC count is inhibited upon the 1-sec switching of the GATE FF, halting the frequency counters. At 9 usec following the 1-sec GATE trigger, update actions have been completed and term SYNC TB - is generated, initiating the start of the next 1sec GATE period. SYNC TB - is applied to the preset load enable (PE) on all time base stages (except 1 Mhz stage Cl7) and to the GATE FF clear C30-1. This switches the GATE FF "ON" and restarts the time base stages at a count of all zeros upon the next rising edge of the 5 Mhz clock. This scheme produces the same propagation delay in starting the counter as the delay produced when the 1-sec. terminal count was reached, ensuring both the start and end of the 1-sec gate is synchronized to 5 Mhz.

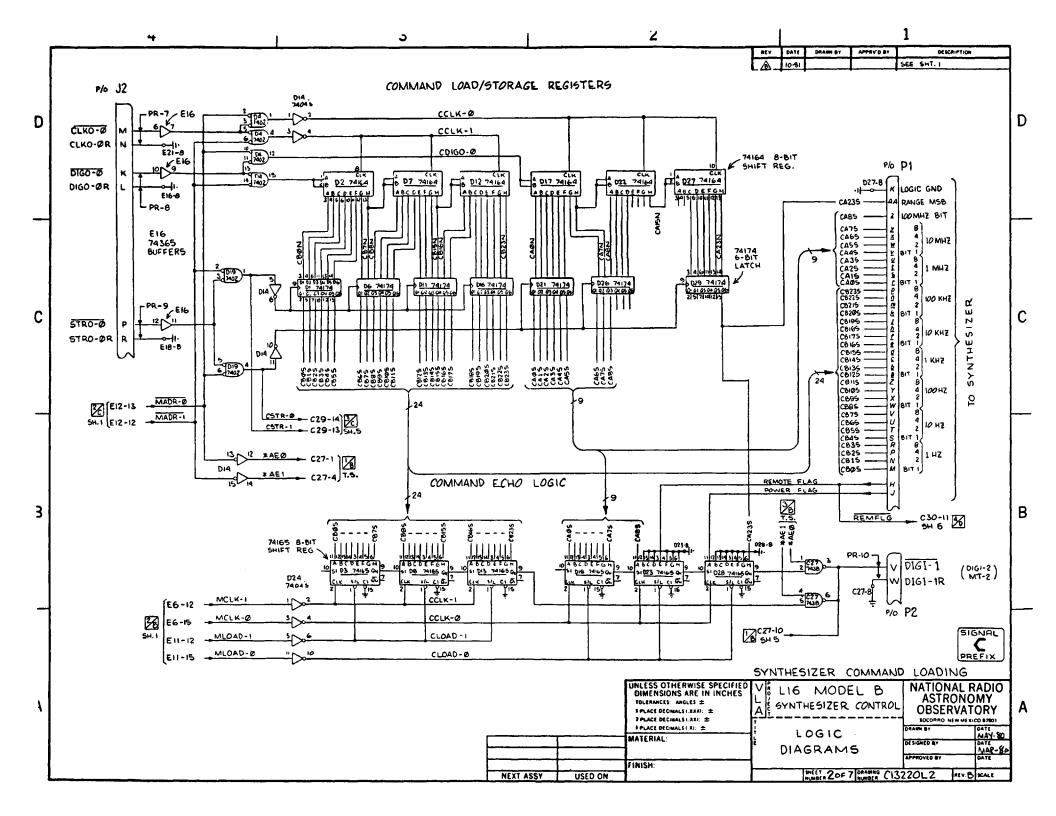

3.4 COMMAND LOADING (Sheet 2; Fig. 4)

Data Set commands, clocks and load strobes (DIGO, CLKO, STRO) enters the L16 through J2 (being daisy changed to all L16's). When a command destined for the L16 is detected by the SMA address and module select logic, command enable terms MADR - 0 or MADR - 1 are generated. DIGO and CLKO inputs are routed to the correct set of command loading shift registes by gates 7402 D4. The most significant command word is serially loaded into 74164 shift registers D17, D22, and D27, enabled by MADR - 0; the least significant command word is serially loaded into shift registers D2, d7, and D12, enabled by MADR - 1. The command strobe STRO is distributed by 7402 D19-4, the MSB word, and D19-1, the LSB word, to dump the parallel outputs of the shift registers into the corresponding latches; 74174 D21, D26, D29 MSB command, and D1, LSB command. D6 D11 Fluke tuning commands from the Data Set occur infrequently (usually only at source changes). The latches provide static storage of the command word for the Fluke Synthesizer remote input and continuous command echo monitoring.

The tuning command, requiring two successive DCS command words to load, are nine sets of BCD digits representing the 1 Hz to 100 Mhz digits bits CBO - CB23 and CAO - CA8. MSB CA23, when HI, selects the 10 - 160 Mhz tuning range of the Flukes, the intended range. Each command must contain MSB CA23.

## 3.6 FREQUENCY COUNTER (Sheet 4 and Schematic C13220S12; Fig.5)

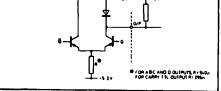

Fluke Synthesizer RF output is routed through a 10 db coupler in the Ll6, with th 0 db coupled port providing the RF power to drive the frequency counter circuit and logic. Connections to and from the coupler uses semi-rigid coax, with the coupled port terminated into 51-ohms on Prescaler PCB Assy A3 through SMA A3J1. The 0 dbm (~500 mv) RF signal is capacitively coupled to Prescaler IC U7, a Plessy SP8637 400 Mhz ECL decade divider. (See data sheets in the Appendix). The actions of the Prescaler Board elements vary depending whether the Ll6 is in the counting or update cycle.

The COUNT CYCLE is defined by the GATE + term being HI (1 second duration). GATE + (TTL) is translated to ECL by MC10124 U8

to ECL CLK INH term on the Prescaler. When CLK INHB goes ECL LO, providing a BCD A,B,C,D output and and a TTL divide by 10 carry (U7-11). While counting, the A,B,C,D outputs are < 1 v and unable to be used. The TTL carry (an anemic TTL) is "squared up" by saturating amplifier 2N2907 Ql, forming the clock to 74LS160 decade counter U6, the 10 Hz counter stage. The O3 output of U6 counter is used for the divide by 100 clock, the clock source for the following seven stages of counters on the logic assembly. 03 is used for the clock as its rising edge occurs at the zero of the input RF (CLK INPUT) to the Prescaler, crossing point keeping the phase of the various counting devices in phase. U6 output Q0, representing divide by 20, clocks retriggerable one-shot AM26SO2 U3 as an activity sensor for the Prescaler, transistor amplifier and 2nd stage counter U6 to detect a failure frequency counter "front end". Additionally, the in the one-shot will fail to retrigger at a frequency below about 4 Mhz, representing a frequency 80 Mhz (4 Mhz x 20) of the input RF, to indicate the Fluke Synthesizer is operating at a frequency below the normal system range. In these cases, the one-shot U3 will illuminate the PRESCALER ERROR front panel LED and associated error flags being set. (Momentary power glitches can clear the command latches. A zero command word to the Flukes will cause it to wander wildly in the 20-30 Mhz range. A PRESCALER error with a wandering frequency display indicates this state, corrected by re-issuing valid tuning commands). A PRESCALER error with a zero frequency display indicates loss of Fluke RF input, or failure of the Prescaler "front end" circuitry.

The divide by 100 clock from U6 enters the logic assembly by ribbon connector A4P1, IC location Cl-6. It is buffered by 7404 D9-12 and D9-14 which adds propagation delay to ensure the A3 CY term from the Prescaler is captured by 3rd stage (1Khz) counter 74160 C2 and following stages C3 thru C8. All frequency counter stages on both the Prescaler and logic assemblies will continue to count each cycle of the input RF for the 1-sec. duration of the Count/GATE cycle.

The UPDATE CYCLE is defined by the GATE + term being LO. a function of the time base/gate logic. TTL GATE + going LO is translated by prescaler IC U8 to ECL HI, the CLK INHB (inhibit) state of prescaler IC U7. This halt the counting action of U7. The TTL CY term U7-11 becomes static, halting the clock generation to the following counter stages, freezing the BCD counts of the frequency count in all nine counters. BCD outputs A,B,C,D on U7 prescaler settle within 2 usec to a TTL level, pulled up by 10 k resistors R10 - R13 and applied to the inputs of quad latch 74LS75 U5. At UPDATE +2 usec, sequence term LATCH A3 clocks the 1 Hz BCD count into latch U5, and the 10-Hz U6 BCD count into latch 7475 U4. (Note:term LATCH A3 is not generated if OVERFLOW error is detected). Term FC DUMP latches the remaining counters 74160 C2 thru 12. The 100 Mhz bit is latched into D-FF 7474 C13.

At UPDATE + 4 usec, sequence term RESET A3 + resets the BCD count in U7 prescaler to all zero. This inadverdently produces a TTL CY output and clocks counter U6, incrementing the frequency count by 10 Hz. For this reason, 74LS160 10 Hz counter U6 is cleared by term RESET - at time UPDATE + 6 usec, after the occurrance of the false U7 TTL CY to prevent an initial count of 10 Hz from occurring. At UPDATE + 7 usec the remaining frequency counter stages are cleared by term FC RST. All counter stages have now been read, latched and cleared awaiting the next count/gate cycle to begin. The outputs of the frequency count latches store the last count until the next update cycle, thus remaining static to drive the display and monitor word logic.

The last frequency counter stage, 74160 C8, develops the 100 Mhz count bit at Q0; output Q1, if HI, would represent 200 Mhz, an impossible count for the Fluke Synthesizer range. C8-13 Q1 is used as an OVERFLOW ERROR detector, indicating a malfunction in either the frequency counter stages or the time base operating beyond its 1-second interval. Frequency counts are not latched if an OVERFLOW occurs, so that the latched count represents the last "good" count. The term illuminates the OVRFLW front panel LED and is captured as an error flag.

3.6 UPDATE SEQUENCING & CONTROL LOGIC (Sheet 3; Fig. 6)

Of the main functions of the L16, the frequency counting components must be synchronous to the 1-second gating, while command and monitor functions between the L16 and Data Set are asynchronous (can occur at any time in relation to the gate timing). The updating logic must therefore be synchronous to preserve the precise 1-second count period.

All the update logic centers around the MASTER GATE flip flop, 74LS109 C30-6,7. When GATE + goes HI (C30-7), the 1-second count period begins; when GATE + goes LO, as a result of the time base reaching the 1-second +/- 5 ns point, the count cycle ends and the update cycle begins.

At time base = 1.000000 second, 74160 C25-15 terminal count (TC) is clocked into GATE FF by the 5 Mhz clock, toggling GATE + to LO (C30-7) and GATE - to HI (C30-6). The time base continues to run, however, to generate 1 Mhz CLK required by the update logic. When GATE + goes LO, the transition triggers 9602 one-shot E17-6 to produce a 180 ms period to illuminate the UPDATE front panel LED. GATE FF term GATE - going HI enables the update sequence counter 74160 C16, clocked by the time base 1 Mhz, such that counter C16 increments its BCD count every 1.0 usec. The BCD counter outputs Q0 - Q3 drive 9301 10-line decoder C26 to produce ten sequential discrete outputs Y0 through Y9, each being active lo for 1 usec.

At UPDATE + 1 usec (Y0, C26-13), no action occurs to allow the frequency counters, particularly the prescaler, to halt and settle. At UPDATE + 2 usec (Y1, C26-12), the LO output is and'd with the OVFLOW flag to produce terms LATCH A3FC DUMP if no OVERFLOW occurred. LATCH A3 latches the 1- and 10 Hz counts on the prescaler board, FC DUMP latching the seven 100 Hz to 100 Mhz count stages.

At UPDATE + 3 usec (Y2, C26-11), inverter C22-12 produces active HI term LATCH FLAGS, the L-H edge clocking the error states into the respective error latches.

At UPDATE + 4 usec (Y3, C26-10), inverter C22-14 produces active HI term RESET A3 +, clearing the prescaler IC BCD count, readying it for the next count cycle.

At UPDATE + 5 usec nothing happens because I couldn't think of anything for it to do!

At UPDATE + 6 usec (Y5, C26-5), term CLR WARN - clears the various error detecting capturing FF's.

This completes the update sequencing required to latch the frequency counts and restoring the logic for the next count cycle. The update cycle is now terminated and the count cycle initiated.

At UPDATE + 10 usec (Y9, C26-7), the SYNC TB - term going LO immediately clears the GATE FF, the transition of GATE + going HI defining the start of the count/gate cycle. GATE + going HI also triggers 26SO2 one-shot E19 producing variable delayed GATE of 10 - 50 ns, adjusted by potentiometer E9-7. A3 GATE FF 7474 C15 develops a special GATE period for the prescaler IC that is delayed slightly beyond the true gate start time, but is stopped in union with the MASTER GATE FF. This delay compensates for some chattering in the prescaler IC when first re-enabled for counting in which a few counts tend to accumulate before the first RF cycle. UPDATE + 10 usec/sync TB - is also used by the update sequence counter C16 for the PE - enable, loading a count of zero on the next 1 Mhz count, ensuring it is ready for the next count cycle. When SYNC TB - cleared the GATE FF to the count state, term MSTR GATE - going LO, the update counter enable inhibits the counter from sequencing during the term, next The next 1 Mhz time base clock does, however, count/gate cycle. clear the sequence counter through the PE preset, where it remains for the duration of the 1-sec. count cycle.

The update cycle actions are accomplished in 10 usec. The only interruption to the sequencing actions is caused by a monitor interrupt, caused when the Data Set, being asynchronous to the L16 timing, happens to poll for monitor data during the 10 usec update cycle. If either of the frequency count monitor words is polled, the Data Set shift clocks (CLKI) trigger one-shot 9602 E17 (Sheet 5) to produce a 270 usec pulse MON INTR -. The update sequence counter is inhibited while MON INTR - is active LO, preventing the sequence logic from updating the frequency and error latches until Data Set monitor polling is count This of course prevents monitor data from being completed. "read" while the register contents are changing. (Additionally, the MON INTR - feature keeps all L16's count cycles closely synchronous to each other, as the Data Set polls each L16 for monitor data in sequence, causing the MON INTR to occur in each L16 within two waveguide cycles of each other. This is evident by the UPDATE LED's on the four L16's in each MT-1 and MT-2 racks "blinking" at the same time). During the MON INTR 270 usec period, the sequence counter is halted and held at the state it was in when interrupted. When MON INTR is completed, update actions will continue where they left off.

#### 3.7 MONITOR DATA PROCESSING

Two monitor data values are polled by the Data Set: 2 words of Command Echo and 2 words of Frequency Count. The Ll6's are hardwired addressed to segment the Ll6's to respond only to the correct Data Set SMA address. (See Section 3.2)

#### 3.7.1 COMMAND ECHO LOGIC (Sheet 2)

The two DCS tuning commands are stored in 74174 latches D1, D6, D16, D21 and D29, outputs being static between updates and sent to the Flukes as the parallel command word. The latch outputs are also loaded into the parallel inputs of 74165 shift registers D18, D23, D28, the high order command bits, and D3, D8, D13, the 24 low order bits. Loading occurs upon receipt of the DS STRI. being routed to the proper shift registers (terms MCLK-0, MCLK-1), the shift register contents being serially marched out to the Data Set. There is a bit-to-bit image (or "echo") of the command The control computers use the Command Echo word to word format. verify the tuning commands were received by the L16 as sent. Note the difference between the Command Mux and Echo Mux is 100 (octal): thus Command Mux 320 can be seen "echoing" back on Mux 220. (See also Sect 3.4)

## 3.7.2 FREQUENCY COUNT MONITOR LOGIC (Sheet 4 and Sheet 5)

The frequency count is latched into registers on both the Prescaler board and main logic assembly. The 100 Hz to 100 Mhz digits from 74714 latches C9 - C12 are combined with the 1 Hz and 10 Hz digits from the Prescaler board on Sheet 4, forming the FCX BUS. The 9 digit frequency count is delivered to the display logic and the monitor data registers via the FCX BUS. Shift registers 74165 load the FCX BUS upon receipt of the Data Set stroge STRI, being sent to the proper shift register by steering gates on Sheet 1. Shift registers D5, D10, D15 contain the 1-Hz to 100 Khz BCD digits, and D30 the error flags. The format of the duo word used for tuning commands, command echo and frequency count are identical, allowing a direct BCD readout on a DCS Data Tap by viewing the appropriate MUX's.

3.8 FREQUENCY DISPLAY LOGIC (Sheet 5 and 6; Fig 7)

The frequency count, in addition to being provided as DCS monitor data, is also available on the L16 front panel as a local numeric display. The full 150 Mhz range with 1 Hz accuracy and resolution is displayed as a nine-digit word.

The full frequency count from the latches is sent via the FCX BUS to display multiplexers 9312 El throuh E4 to select one-ofeight frequency digits. The address scanning is derived from the time-base, the selected digit further multiplexedby 74157 El0 to merge in the 100 Mhz bit (FlJ+). If the 100 Mhz bit is HI, 7402 D19 forms BCD "1" (0001) on the 74157 inputs; if the 100 Mhz bit is LO, all 74157 BCD inputs become HI producing an LED blanking code (1111).

The four-bit scanning address and selected 4-bit BCD frequency digit is sent to the Display Board Assembly A5 through a ribbon cable. The selected digit is sent to the BCD-to-7 segment decoder CD4511 U1, (Sheet 6) the output sent to the segment select inputs on the numeric LED displays. Resistors R1 through R7 are current limiters for proper display intensity. The 4-bit scanning address is sent to CMOS BCD-Decimal decoder CD4028 U2 producing active HI digit select strobes, amplified by 2N918 transistors Q1 through Q8 to form the proper digit drive voltages of +2.4 volts (OFF) and 0 volts (ON). The multiplexer display scans from right to left at 5 Khz, each digit illuminated for 200 CMOS devices were selected for Ul and U2 to keep currents usec. at a minimum so the switching currents during LED scanning would not cause EMI interference to the sensitive MLO environment. The active HI feature of CMOS also eliminated using inverters for proper logic sense with the DL-330M common-anode display units.

Discrete LED's on the front panel/Display Board are driven by logic on the main logic assembly for status and error indications as follows:

5 MHZ REF AVAIL - illuminated to show 5 Mhz availability. COUNT - "blinks" to show 1-sec. time base operation. GATE - illuminated during the update cycle. OVRFLW - illuminated upon Overflow condition of frequency counters. PRESCALER - illuminated to show prescaler error or failure. LOSS OF 5 MHZ - illuminated upon loss of 5 Mhz.

#### 3.9 ERROR FLAG AND STATUS (Sheet 5)

Several status and error flags are generated to indicate normal and abnormal operation of the L16 and associated Fluke Synthesizer.

CMD INTR - OR gate C29-15 senses the arrival of either tuning command words, and when sensed is captured for presetting 7474 FF C13-11. During update, the event is clocked into error latch 74715 E15 and reported during the next monitor word polling. This flag indicates a new frequency command has been received, the Flukes likely "slewing", and thus the frequency count may not yet be settled. The capture FF C13-11 is cleared during each update cycle by CLR WARN -.

5MHZ OK - is generated by a retriggerable one-shot on the Prescaler Board. Should the external 5 Mhz fail, or be of insufficient level to clock the time base, 5 Mhz OK goes LO to indicate the error condition, captured by the 7474 FF Cl4-5 and sent directly to the monitor data register. 5 MHZ OK error is not latched since loss of 5 Mhz would render the update sequence inoperative, the event being otherwise unreported. A front panel LED is also illuminated.

PRESCALER error - is generated by a retriggerable one-shot on the Prescaler Board, an error indicated by PRESCALER ERROR being LO, captured by 7474 FF C14-10 and clocked into error latch E15 and reported during the next monitor word polling. The capture FF C14-10 is cleared during each update cycle.

OVERFLOW error is produced when a count of 200 Mhz or greater is accumulated in the frequency counter. The 200 Mhz bit, when set HI defines overflow and is clocked into error latch El5 and reported during the next monitor word polling. A front panel LED is also illuminated. The overflow condition is cleared when the frequency counters are cleard during the update cycle.

NOTE: The 74175 error latch E15 provides temporary storage of error conditions for reporting by DCS monitor data. If the error condition is momentary, the flag will be cleared upon the next latch update. (next 1-second gate end) and may not be active when monitor data is polled. Error flag reporting through monitor data is intended for a persistent error.

The Fluke Synthesizers provide two status monitor bits, the POWER on flag (H=ON) and REMOTE/local flag (H=remote) to indicate the mode of operation. These two status flags are loaded into the command echo monitor word shift registers 74165 D23-3 (REMOTE) and D28-11 (POWER) on Sheet 2.

18

TROUBLESHOOTING TREE

4.0 LIST OF L16 DRAWINGS

Top Assembly Drawings D13220P18 Top Assembly Drawing A13220Z18 Top Assembly Bill of Materials C13220L12 L16 Logic Diagram C13220S12 L16 Prescaler PCB Schematic Sub-Assembly Drawings Assembly A3 - Prescaler P.C.B. Assembly C13220P21 Prescaler Assembly Drawing Prescaler B.O.M. A13220Z17 C13220AB13 P.C.B. 2:1 Artwork C13220M34 P.C.B. Drill Drawing Assembly A4 - I.C. Module Logic Assembly C13220P20 I.C. Module Assembly Drawing A13220Z16 I.C. Module B.O.M. A13220P24 Dip Header Assembly A13220Z21 Dip Header B.O.M. A13220W10 Wire List, Master A13220W11 Wire List, Machine A13220W12 Wire List, Hand A13220W13 Wire List, Connector Assembly A5 - Front Panel Display Assembly C13220M33 Front Panel C13220M36 Front Panel Engraving C13220AA12 Front Panel Silk Screen D13220P23 Display P.C.B. Assembly Drawing A13220Z20 Display P.C.B. B.O.M. C13220AB24 Display P.C.B. 2:1 Artwork C13220M39 Display P.C.B Drill Drawing **Miscelleneous** C13220M35 Assembly A1 - Rear Panel B13220M42 Assembly A2 - RF Coupler Mounting Plate

For a list of drawings of major mechanical components (Side Panels, Module Rails, etc), see Top Assembly B.O.M. A13220Z18

# 5.0 LIST OF MASTER LOCAL OSCILLATOR (MLO) DRAWINGS

D16000B4MLO Block Diagram (older, Dumke version)D16000B10MLO System Rack LayoutD16000B11MLO System Block Diagram (as-built version)A13220W15MLO Rack MT1, Rack Wire ListA13220W16MLO Rack MT2, Rack Wire ListA13220W14MLO Rack MT1, Bin "E" Wire ListA13220W17MLO Rack MT2, Bin "E" Wire List

# LI6 DRAWINGS

2nd Doubler (-C, -) = 10 (-C,

THE OSCILLATOR AND FREQUENCY-DOUBLER CIRCUIT

A HIGH-POWER AMPLIFIER OF THE PUSH-PULL TYPE

(ILLUSTRATED PARTS BREAKDOWN)

| ELEC      | TRICAL       |              | IONAL RADIO ASTRONOMY OB | DATE <u>31 OCT 198</u> 0 page <u>1</u><br>REV: 10 JUL 1981 | of <u>5</u>  |

|-----------|--------------|--------------|--------------------------|------------------------------------------------------------|--------------|

| ITEN<br>I | REF<br>DESIG | MANUFACTURER | MFG PART Ø               | DESCRIPTION                                                | TOTAL<br>QUA |

| _1        | ļ            | NRAO         | A13220218                | LIG-SYNTHESIZER CONTROL                                    |              |

| 2         |              |              |                          |                                                            |              |

| 3         | l            |              | A13220W10                | WIRE LIST - MASTER                                         |              |

|           |              |              | A13220W11                | WIRE LIST - MACHINE                                        |              |

| 5         |              |              | A13220 W12               | WIRE LIST - HAND                                           |              |

| 6         |              |              | A13220W13                | WIRE LIST - CONNECTOR                                      |              |

| 7         |              |              |                          |                                                            |              |

| _ 8_      | A2           |              | B13220M42                | R.F. CHASSIS SUB-ASSY                                      | 1            |

| 9         | A3           |              |                          | PRESCALER SUB-ASSY                                         |              |

| 10        | _ A4         |              | A13220216/P20            | I.C. MODULE PANEL SUB-ASSY                                 | 1            |

|           | AS           |              | 1213440723               | L.E.D. DISPLAY SUB-ASSY                                    | 1            |

| 12        |              |              |                          |                                                            |              |

| 13        | P/0 A5       |              | C13220M33                | PANEL, FRONT                                               | 1            |

| 14        | AI           |              | C13220M35                | PANEL, REAR                                                |              |

| 15        |              |              | C13720M15-1              | RAIL, MODIFIED (TOP LEFT)                                  | 1            |

| 16        |              | <b>₩</b>     | C13720M15-2              | RAIL, MODIFIED (BOTTOM LEFT)                               | 1            |

| 17        |              | NRAO         | C13720M17                | RAIL, INSULATED SPACER                                     | 2            |

BILL OF N

INC

#### BILL OF IAL

NATIONAL RADIO ASTRONOMY OBSERVATORY

| ELECT     | RICAL        |                   | 13220218 REV 8 | DATE <u>31 OCT 198</u> 0 page 2 | OF           | 5 |

|-----------|--------------|-------------------|----------------|---------------------------------|--------------|---|

| ITEN<br>I | REF<br>DESIG | MANUFACTURER      | MFG PART \$    | DESCRIPTION                     | TOTAL<br>QUA |   |

| 18        |              | NRAO              | B13050M23      | RAIL, SIDE SUPPORT (R.H. SIDES) | 2            |   |

| 19        | . <u> </u>   |                   | C13720P68      | SIDE PLATE (LH. SIDE)           |              |   |

| 20        |              |                   | B13720M49      | INGULATION (FOR \$ 7 ABOVE)     | 1            |   |

| _21       |              |                   | B13050M18      | SIDE PLATE (R.H. SIDE)          | 1            |   |

| 22        |              |                   | B13720M47      | BALL, END SPACER                | 4            |   |

| _23       |              |                   | B13050M4       | GUIDE BLOCK                     | 4            |   |

| _24       |              | ¥                 | B13050M22-1    | COVER, PERFORATED (20A)         | 2            |   |

| 25        |              | NRAO              | (T.A.P. NOTE ) | DISPLAY FILTER (RED)            | 1            |   |

| 26        |              | SOUTHCO MFG.      | 47-10-204-10   | CAPTINE SCREW                   | 4            |   |

| 27        |              | NRAO              |                |                                 | 2            |   |

| _28       |              |                   |                |                                 |              |   |

| 29        |              |                   |                |                                 |              |   |

| 30        |              |                   |                |                                 |              |   |

| 31        | DC1          | MINI-CIRCUITS LAB | MCL-ZFDC10-1   | DIRECTIONAL COUPLER, 1048       | 1            |   |

| 32        | A4P1, P2     | A-P PRODUCTS      | 924108-6       | JUMPER CABLE, 14-PIN, 8 INCH    | 2            |   |

| 33        | A4P3         | A-P PRODUCTS      | 924110-6       | JUMPER CABLE, 14-PIN, 10 INCH   | 1            |   |

| 34        | A4P4         | CANNON            | CAIGP-II MW    | 1.C. DIP PLUG                   | 1            |   |

## BILL OF N INL

NATIONAL RADIO ASTRONOMY OBSERVATORY

| ELECT           | RICAL                    |                        | 3220218 REV B               | DATE <u>31 OCT 198</u> 0 page <u>3</u> | OF           | 5 |

|-----------------|--------------------------|------------------------|-----------------------------|----------------------------------------|--------------|---|

| ITEN<br>4       | REF<br>DESIG             | MANUFACTURER           | MFG PART #                  | DESCRIPTION                            | TOTAL<br>QUA | ] |

| _35             | D57,058                  | ELECTROMECH            | 674-32101815-<br>C-GY- V328 | INDICATOR, SQUARE, 2-COLOR             | 1            |   |

| 36              |                          |                        | i                           | L.E.D. LENS/MOUNT                      | 10           |   |

| 37              |                          |                        |                             |                                        |              |   |

| 38              |                          | <br>                   |                             |                                        |              |   |

| <u>39</u><br>40 | P2                       | AMP SPECIAL INDUSTRIE  | 5 601488-2                  | CONNECTOR, 34-PIN                      |              |   |

| 41              |                          |                        | 202434-4                    | SHIELD, 34-PIN CONN.                   |              |   |

| _42_            | P1                       |                        | 601488-3                    | CONNECTOR, 50-PIN                      | 1            |   |

|                 |                          |                        | 202394-2                    | SHIELD, 50-DIN CONN.                   | 1            |   |

| _44             |                          |                        | 200833-4                    | GUIDE PIN                              | 2            |   |

| 45              |                          |                        | 202514-1                    | GUIDE PIN (GROUND)                     | 2            |   |

|                 |                          |                        | 202964-6                    | GUIDE SOCKET                           | 4            |   |

| 47              |                          | ¥                      | 204219-1                    | CONNECTOR PIN, CRIMP                   | 2            |   |

| 48              |                          | AMP SPECIAL INDUSTRIES | 66460-6                     | CONNECTOR PIN, WIRE WRAP               | 80           |   |

|                 | J13-J15                  | OMNI-SPECTRA           | OMQ-3043-75                 | JACK, 141SR BULKHEAD                   | 3            |   |

| 50              | A2PI, A2P2<br>A3P1, A3P3 |                        | DSM 221-2                   | PLUG, RIGHT ANGLE, . 141 SR            | 4            |   |

| 51              | A2P4                     | 4                      | 05M 201-2A                  | PLUG, . 141 SEMI-RIGID                 | 1            |   |

## BILL OF JAL.

ELE

NATIONAL RADIO ASTRONOMY OBSERVATORY

| ECTRICAL | MECHANICAL |  |

|----------|------------|--|

|          |            |  |

| UEI | 8 | REV | <br><u>B</u> |  |

|-----|---|-----|--------------|--|

|     |   |     |              |  |

BON # A13220218 REV B DATE 31 OCT 1980 PAGE 4 OF 5

| iten<br>I | REF<br>DESIG | MANUFACTURER     | MFG PART # | DESCRIPTION                     | TOTAL<br>QUA |  |

|-----------|--------------|------------------|------------|---------------------------------|--------------|--|

| 52        | A2P3         | OMNI-SPECTRA     | OSM 219    | ADAPTER, RIGHT ANGLE, PLUG/JACK | 1            |  |

| 53        | ļ            |                  |            |                                 |              |  |

| 54        | "+5v"        | H.H. SMITH       | 20100      | TERMINAL, SPLIT-LUG             | 4            |  |

| 55        | "GND"        | H.H. SMITH       | 20250      | TERMINAL, MIN. THROUGH          | 4            |  |

| 56        |              | G.C. ELECTRONICS | 5706-C     | SOLDER LUG                      | 3            |  |

| 57        |              |                  |            |                                 |              |  |

| 58        | ļ            |                  |            |                                 |              |  |

| 59        | ļ            | BOSCO OR EQUIV.  | 6-32 × 5/8 | SCREW, HEX SOCKET               | 2            |  |

| 60        |              |                  | 6-32 × 1/8 | SCREW, PAN HE FLAT HD.          | 14           |  |

| 61        |              |                  | 6-32 × 5/8 | SCREW, PAN HD.                  | 4            |  |

| 62        |              |                  | 6-32 × 1'8 | SCREW, PAN HD.                  | 4            |  |

| 63        |              |                  | 6-32 × 1/4 | SCREW, FLAT HD (PAINTED)        | 2            |  |

| 64        |              |                  | 4-40 × 3/8 | SCREW, PAN HD                   | 16           |  |

| 65        |              |                  | 4-40 × 1/2 | SCREW, PAN HD                   | 4            |  |

| 66        |              |                  | 4-40       | NUT, ST. STEEL, HEX             | 4            |  |

| 67        |              |                  | *2         | WASHER, FLAT                    | 4            |  |

| 68        |              |                  | *4         | WASHER SPLIT-LOCK               | 16           |  |

## BILL OF IAL

| NATIONAL RAD | DIO ASTRONOMY | OBSERVATORY |  |

|--------------|---------------|-------------|--|

|              |               |             |  |

| ELECTRICAL | MECHANICAL | BOM 1 <u>A13220218</u> | REV <u>B</u> | _5 | or <u>5</u> |

|------------|------------|------------------------|--------------|----|-------------|

| ·          |            |                        |              |    |             |

| ITEN<br>4 | REF<br>Desig | MANUFACTURER          | MFG PART # | DESCRIPTION                    | TOTAL<br>QUA |

|-----------|--------------|-----------------------|------------|--------------------------------|--------------|

| 69        |              | BOSCO OR EQUIV.       | #6         | WASHER, EXT. TOOTH             | 12           |

| 70        |              |                       |            |                                | - <u>'</u>   |

| 71        |              |                       |            |                                |              |

| 72        |              | ALPHA WIRE CO.        | 286        | WIRE, BUS TINNED COPPER \$14   | A/R          |

| _73       |              | ALPHA WIRE CO.        | PVC-105/6  | PLASTIC TUBING, .066 DIA. PVC  |              |

| _74       |              |                       |            | WIRE \$16 STRANDED (BLK & ORG) |              |

| 75        |              |                       |            | WIRE #22 STRANDED              | A/R          |

| 76        |              |                       |            | WIRE # 26 SOLID KYNAR          | A/R          |

| 77        |              |                       |            | WIRE, \$30 SOLID KYNAR         | AIR          |

| _78       |              | Y                     |            |                                |              |

| _79_      |              | CONN. HARD RUBBER CO. | K350       | KAPTON TEMP-R-TAPE 32/64"      | A/R          |

|           |              |                       |            |                                |              |

|           |              |                       |            |                                |              |

|           |              |                       |            |                                |              |

|           |              |                       |            |                                |              |

|           |              |                       |            |                                |              |

BOM: A13220217

LIG SYNTHESIZER CONTROL ASSY A3 - PRESCALER P.C.B. ASSEMBLY DETAILS

57 (38)

**-**40

<u>с</u>т 39

1

S

SOLDER

SMA CONNECTORS (2)

NYLON!

TT.

α

Ð

(35)

37)

ENSURE GOOD CONTACT TO PCB GROUND PLANE

DETAIL "A"

(3

(1)

MICAZ

furning and the second

MOUNTING UI REGULATOR

WITH HEAT SINK AND

UI MUST BE GOLATED

FROM PCB GOD PLANE

MICA INSULATOR

NYLON!

DETAIL "B"

PCB

1

| ] ELECI   | TRICAL       | MECHANICAL BOM A     | 3220217 REV B | DATE 16MAR 80 PAGE 1<br>REV: 29 SEP 83 | of <u>3</u>  |

|-----------|--------------|----------------------|---------------|----------------------------------------|--------------|

| ITEN<br>4 | REF<br>DESIG | MANUFACTURER         | MFG PART #    | DESCRIPTION                            | TOTAL<br>QUA |

| 1         |              | NRAO                 | C13220AB13    | PRESCALER ASSY P.C.B.                  | 1            |

| 2         | J1, J2       | OMNI-SPECTRA         | OSM 244-2     | CONNECTOR, SMA P.C. MOUNT              | 2            |

| 3         | וט           | NATIONAL, OR EQUIV.  | LM320K-5.2    | I.C., REGULATOR TO-220 - 5.2V          | 1            |

| 4         | <u>U2</u>    |                      | LMIGON        | I.C., COMPARATOR (8-PIN DIP)           | 1            |

| 5         | U3           |                      | 26502         | I.C., ONE-SHOT                         | 1            |

| 6         | U4, U5       |                      | 74L\$75       | I.C., QUAD LATCH                       | 2            |

| 7         | U6           | 4                    | 74LS160       | I.C., DEC. COUNTER                     | 1            |

| 8         | U7           | PLESSY SEMICONDUCTOR | SP8637B       | I.C., 400MHZ ÷10 PRESCALER             | 1            |

| 9         | UB           | FAIRCHILD            | 10124         | I.C., TTL-ECL TRANSLATOR               | 1            |

| 10        | -            | T.I. OR EQUIV.       | C8516         | SOCKET, I.C., 16-PIN, S.T.             | 6            |

| //        | -            |                      | C8514         | SOCKET, I.C., 14-PIN, S.T.             | 2            |

| 2         |              |                      | C8508         | SOCKET, I.C., 8-PIN, S.T.              | 1            |

| 13        | Q1           | SYLVANIA OR EQUIN.   | 2N2907        | TRANSISTOR, TO-5                       | 1            |

| 4         | ~            |                      |               | SOCKET, TO-5 TRANISTOR                 | 1            |

| 5         | CI           | MALLORY              |               | CAP., 1000pf NPO                       | 1            |

| 6         | C2           |                      |               | CAP., 33 pF NPO CHIP                   | 1            |

| 7         | C3, C5, C9   |                      |               | CAP., O.INF                            | 3            |

BILL OF CAL

|           |              | 112 T        | BILL OF (1)<br>ONAL RADIO ASTRONOMY | -                                       |              |

|-----------|--------------|--------------|-------------------------------------|-----------------------------------------|--------------|

| _ ELEC    | TRICAL       |              |                                     | B DATE IGMAR 80 PAGE 2<br>REV: 295EP 83 | OF <u>3</u>  |

| iten<br>4 | REF<br>DESIG | MANUFACTURER | MFG PART #                          | DESCRIPTION                             | TOTAL<br>QUA |

| 18        | C4           |              |                                     | CAP., 100pF                             | 1            |

| 19        | <i>L</i> 6   |              |                                     | CAP, 30 pF                              | 1            |

| 20        | C7           |              |                                     | CAP., 2.2,4F                            | 1            |

| 21        | C8           |              |                                     | CAP., I.O, UF                           | 1            |

| 22        | C10          |              |                                     | CAP., D.DIMF                            |              |

| 23        | RI, R14      |              |                                     | RES., 51.2 1/8W                         | 2            |

| 24        | R6, R19-20   |              |                                     | RES., 2K                                | 3            |

| 25        | R7, R16      |              |                                     | RES., IK                                | 2            |

| 26        | R10-R13      |              |                                     | RES, IOK                                | 4            |

| 27        | R15          |              |                                     | RES., 7.5K                              | 1            |

| 28        | R17          |              |                                     | RES., 30K                               | 11           |

| 29        | R21          |              |                                     | RES., 68K                               | 1            |

| 30_       | R22          |              |                                     | RES., 200K                              | 1            |

| 31        | R24          |              |                                     | RES., 2.4K                              | 11           |

| 32        | R25          |              |                                     | RES., 39K                               | 1            |

| 33        | R27          |              |                                     | RES., 820.2 ¥                           | 1            |

| 34        | +5, GND"     | H.H. SMITH   | 20250                               | TERMINAL LUG, SOLDER                    | 2            |

BILL OF & IAL

|           |              |                      | L RADIO ASTRONOMY OB        |                                                            |              |

|-----------|--------------|----------------------|-----------------------------|------------------------------------------------------------|--------------|

| ] ELECTS  | RICAL        | MECHANICAL BOM 14/   | <u>8220217</u> rev <u>B</u> | DATE <u>IGMAR 80</u> PAGE <u>3</u><br><b>REV.29 EEP</b> 83 | _ OF3        |

| ITEN<br>4 | REF<br>Desig | MANUFACTURER         | MFG PART #                  | DESCRIPTION                                                | TOTAL<br>QUA |

| 35        |              |                      |                             | MICA INSULATOR, TO-220                                     | ,            |

| 36        |              | AMATOM OR H.H. SMITH | 4-40 × 1/4 LG               | SCREW, NYLON 4-40                                          | 1            |

| 37        |              | 11 11 11             | HHS 2554                    | NUT, HEX NYLON 4-40                                        | 1,           |

| 38        |              | ACME NUT & BOLT      | 2-56 × 1/4 PH               | SCREW 2-56 PAN HD.                                         | 6            |

| 39        |              |                      | 2-56                        | NUT, HEX 2-56                                              | 6            |

| 40        |              |                      | #4                          | WASHER, SPLIT LOCK                                         | 6            |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             | <u> </u>                                                   |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              |                      |                             |                                                            |              |

|           |              | <br>                 |                             |                                                            |              |

|           |              |                      |                             |                                                            | +            |

BILL OF MATERIAL

NATIONAL RADIO ASTRONOMY OBSERVATORY

|            | TRICAL            | MECHANICAL BOM # A   | 13220220 REV 12 | 1-04 DATE GNOV 1980 PAGE 1      | 0F           | 2 |

|------------|-------------------|----------------------|-----------------|---------------------------------|--------------|---|

| _L16       | DISPLAY           | (ASSY AS) PCB B.O.M. |                 |                                 |              |   |

| ITEN<br>T  | REF<br>DESIG      | MANUFACTURER         | MFG PART #      | DESCRIPTION                     | TOTAL<br>QUA |   |

| <u>1</u> A | A5-1              | NRAO                 | C13220A816 - 1  | PRINTED CIRCUIT A5-1            | 1            |   |

| 18         | A5-2              |                      | C13220AB16 - 2  | PRINTED CIRCUIT A5-2.           | 1            |   |

| 2          |                   | ·                    |                 |                                 |              |   |

| 3          | +5V, GND          | H.H. SMITH CO.       | HHS 2010        | TERMINAL, SPLIT LUG             | 2            |   |

| 4          | +5,G.Y            | H.H. SMITH CO.       | HHS 1502-4      | TERMINAL, MIN. THROUGH          | 3            |   |

| 5          | <u>U1</u>         | RCA (OR EQUIV)       | CD4511          | I.C., DISPLAY DECODER (CMOS)    | 1            |   |

| 6          | <u>u2</u>         | RCA (OR EQUIV)       | CD 4029         | I.C., DECIMAL DECODER (CMOS)    | 1            |   |

| 7          | A5J1              | T. I. (OR EQUIV.)    | C8114-ST        | SOCKET, 14-PIN I.C. IN-LINE     | 4            |   |

| 8          | <u>CI.CZ</u>      | PANASONIC            | 220-10R         | CAPACITOR, ELECTROLYTIC 2204F   | 2            |   |

| 9          | L1                | NYTRONICS            | WEE 100         | INDUCTOR, 1004H 5%              | 1            |   |

| 10         | Q1-Q9             | T.I. (OR EQUIV.)     | 2N2222          | TRANSISTOR, NPN-HSS, PLASTIC    | 9            |   |

| <u>_1</u>  | QIO,QII           | T.E. (OR EQUIN.)     | ZN2219          | TRANSISTOR, NPN-HSS, METAL TD-5 | 2            |   |

| 12         | D54-D56           | H.P. (OR EQUIV.)     | 5082-4655       | L.E.D., T1-3/4, RED             | 3            |   |

| 13         | D59-D512          | H.P. (OR EQUIV.)     | 5082-4955       | L.E. D., 71-3/4, GREEN          | 4            |   |

|            | DS1-DS3           | H.P. (OR EQUIV)      | 5082-4555       | L.E.D., T1-3/4, AMBER           | 3            |   |

|            | R8-R13<br>R16-R19 | A-B                  | RCR07G221J      | RESISTOR, 2200 5% 4W            | 10           |   |

| 16         | R14, R15          | A-B                  | RCR07G751J      | RESISTOR, 7502 5% 1/4W          | 2            |   |

| ITEN<br>4 | REF<br>DESIG      | MANUFACTURER     | DESCRIPTION | TOTAL                            |     |  |

|-----------|-------------------|------------------|-------------|----------------------------------|-----|--|