VLBA Technical Report No. 12

VLBA STANDARD INTERFACE BOARD MANUAL

WAYNE KOSKI AND DAVID WEBER JULY, 1991

# TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                           |    |

|-----|--------------------------------------------------------|----|

|     | Standard Interface Board Overview                      | 4  |

| 2.0 | THEORY OF OPERATION                                    | 5  |

|     | 2.1 MESSAGE FORMAT, PROTOCOLS AND TIMING               | 5  |

|     | Interface Address Block                                |    |

|     | Monitor and Control Bus                                | 5  |

|     | XMT Bus                                                | 5  |

|     | RCV Bus                                                | 6  |

|     | Bus Timing                                             | 7  |

|     | Function Codes                                         |    |

|     | Interface Internal Monitor and Control Functions       | -  |

|     | Bus Description                                        |    |

|     | 2.2 8032 MICROCONTROLLER AND SUPPORT CHIPS DESCRIPTION | 13 |

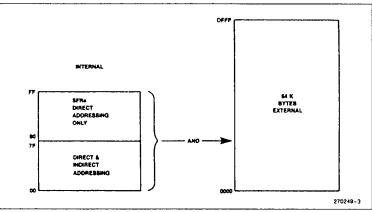

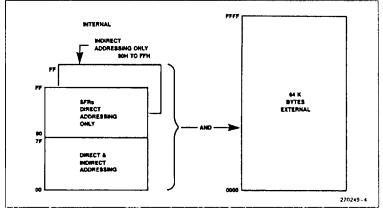

|     | Special Function Registers (SFR's)                     | 13 |

|     | • •                                                    |    |

|     | CPU Timing                                             | 14 |

|     | I/O Ports                                              | 15 |

|     | Accessing External Memory                              | 17 |

|     | PSEN (Program Store Enable)                            | 18 |

|     | ALE (Address Latch Enable)                             | 19 |

|     | Timer/Counters                                         | 19 |

|     | Timer/Counters 0 and 1                                 | 19 |

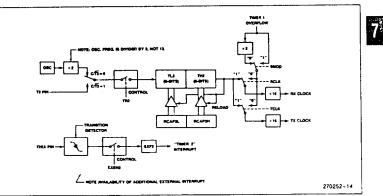

|     | Timer 2 (Watch-Dog Timer)                              | 21 |

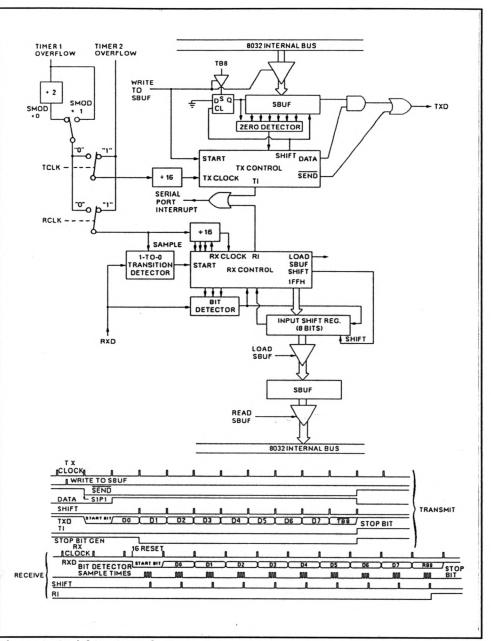

|     | Serial Port Interface                                  | 23 |

|     | Baud Rates                                             | 24 |

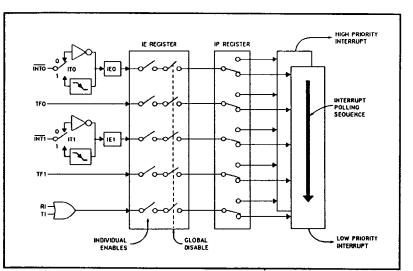

|     | Interrupts                                             | 26 |

|     | Priority Level Structure                               | 28 |

|     | How Interrupts Are Handled                             | 29 |

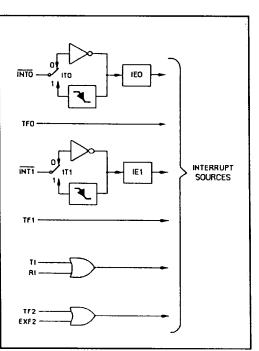

|     | External Interrupts                                    | 29 |

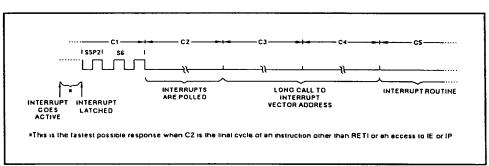

|     | Response Time                                          | 30 |

|     | Accumulator Register                                   | 30 |

|     | B Register                                             | 30 |

|     | Stack Pointer                                          | 31 |

|     | Data Pointer                                           | 31 |

|     | Serial Data Buffer                                     | 31 |

|     | Program Status Word                                    | 31 |

|     | Timer Registers                                        | 31 |

|     | Capture Registers                                      | 32 |

|     | SFR Memory Map                                         | 32 |

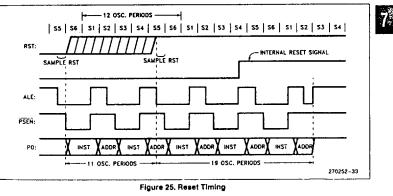

|     | Reset                                                  | 32 |

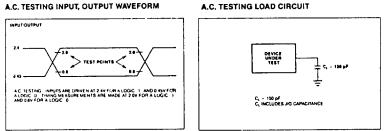

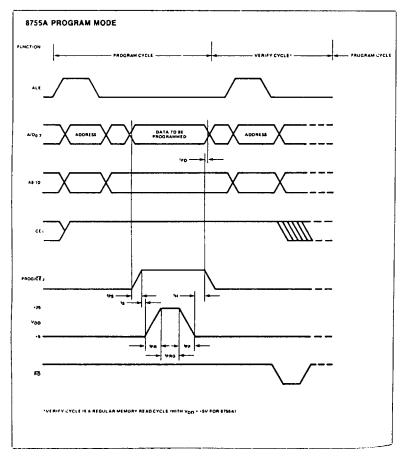

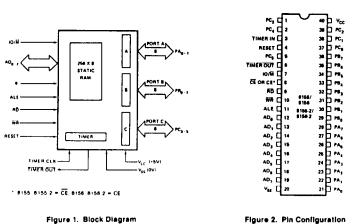

|     | 8755 EPROM-I/O Ports description                       | 33 |

|     | 8156 RAM-I/O Ports-Timer Description                   | 34 |

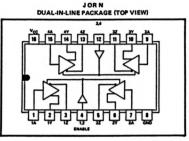

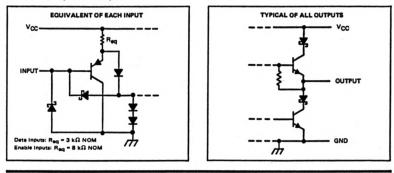

|     | 74LS245 Bidirectional Bus Driver                       | 38 |

|     |                                                        |    |

|     | 2.3 STANDARD INTERFACE BOARD LOGIC                     | 39 |

|     | Interface Signals                                      | 39 |

|     | Bus Drivers and Receivers                              | 42 |

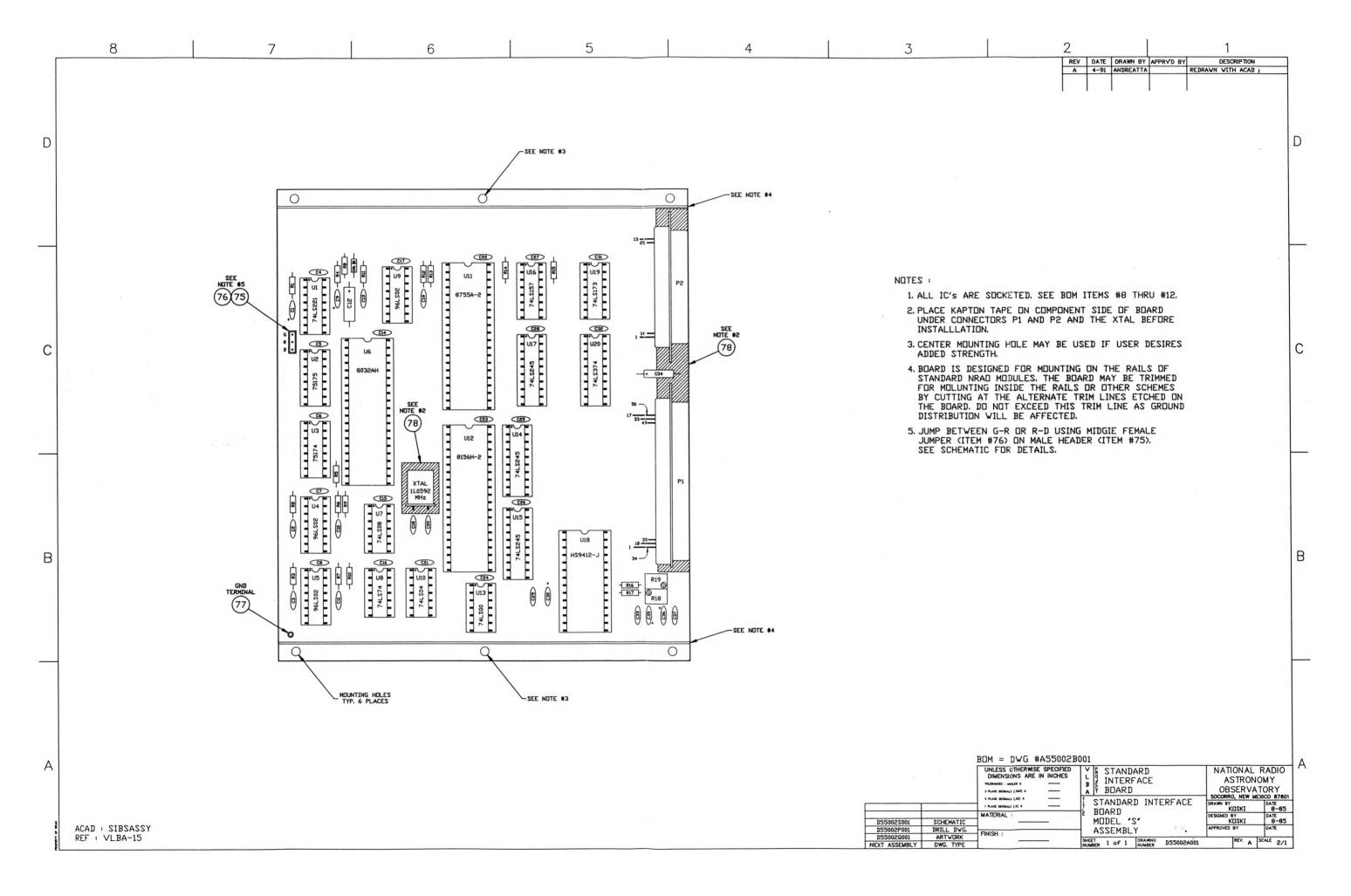

|           | Power On ResetDevice ID Byte ReadExecution of a Control MessageExecution of a Monitor Data Request for Digital Monitor DataExecution of a Monitor Data Request for Analog Data"D" Version Description"S" Version DescriptionHI/LO SEL UsageBus and Board Status Display Logic                                                                                                                                                                                                                                                                                                                                                 | 42<br>42<br>43<br>44<br>45<br>46<br>48<br>49<br>50                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

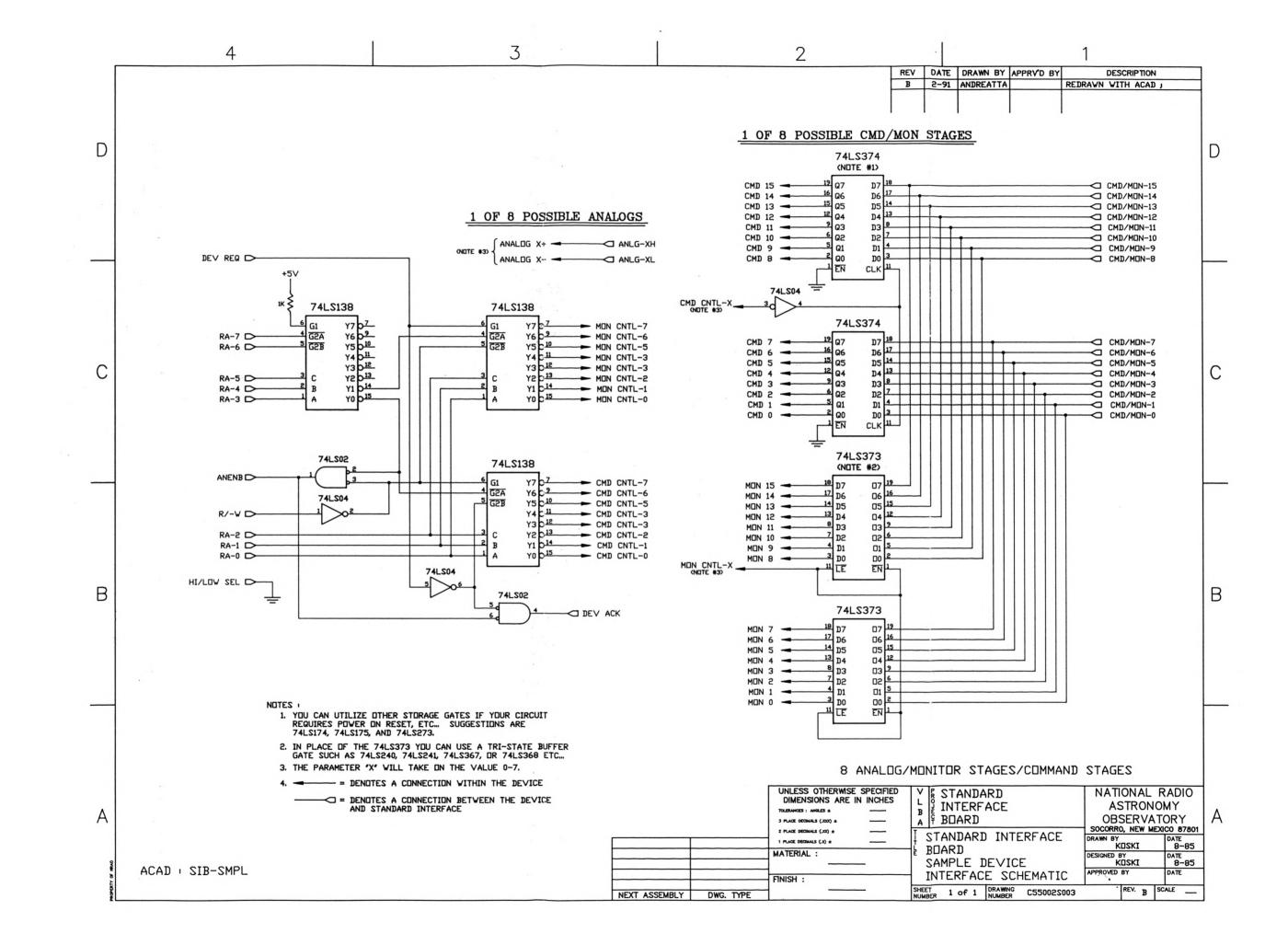

| 2.4       | TYPICAL DEVICE LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                                                                |

| 2.5       | INTERFACE BOARD ADDRESS CONVENTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                                                                |

| 2.6       | INTERFACE - DEVICE TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57                                                                                                                                |

| 2.7       | BAUD RATE GENERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59                                                                                                                                |

| 2.8       | BOARD ALIGNMENT AND TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                                                                                                |

| 2.9       | POWER REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65                                                                                                                                |

| 3.0 FIRMV | ARE DESCRIPTION, ALGORITHMS AND PROGRAM LISTINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                                                                                                                |

| 3.1       | INTRODUCTION AND FIRMWARE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67                                                                                                                                |

| 3.2       | PROGRAM MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69                                                                                                                                |

| 3.3       | FIRMWARE AND ALGORITHMS DESCRIPTION         MACRO Instruction Description         Data Definition Area Description         Reference Values         Internal RAM Assignments         Register Assignments         SFR Register-Label, Bit-Label and Flag Mnemonic Assignments         INTTIAL and Program Start         Interrupt Code         NUMBER         NACK, DC2, ACKN, DC1, SPEOUT, and SPEXIT         SPOOUT and SPEXIT         XMT Bus Character Handling         SERP         READ         SPIN         SYNC         TIMER         ADDCK         XORB Macro         INCRE         OUTIT         LOOP         PARCI | 71<br>71<br>71<br>72<br>72<br>72<br>73<br>76<br>77<br>81<br>82<br>84<br>85<br>87<br>90<br>91<br>93<br>95<br>96<br>97<br>98<br>100 |

|       | NOTUS                                         | 101<br>106  |

|-------|-----------------------------------------------|-------------|

|       | MONLOST                                       | 111         |

|       | 3.4 FIRMWARE PROGRAM LISTING                  | 117         |

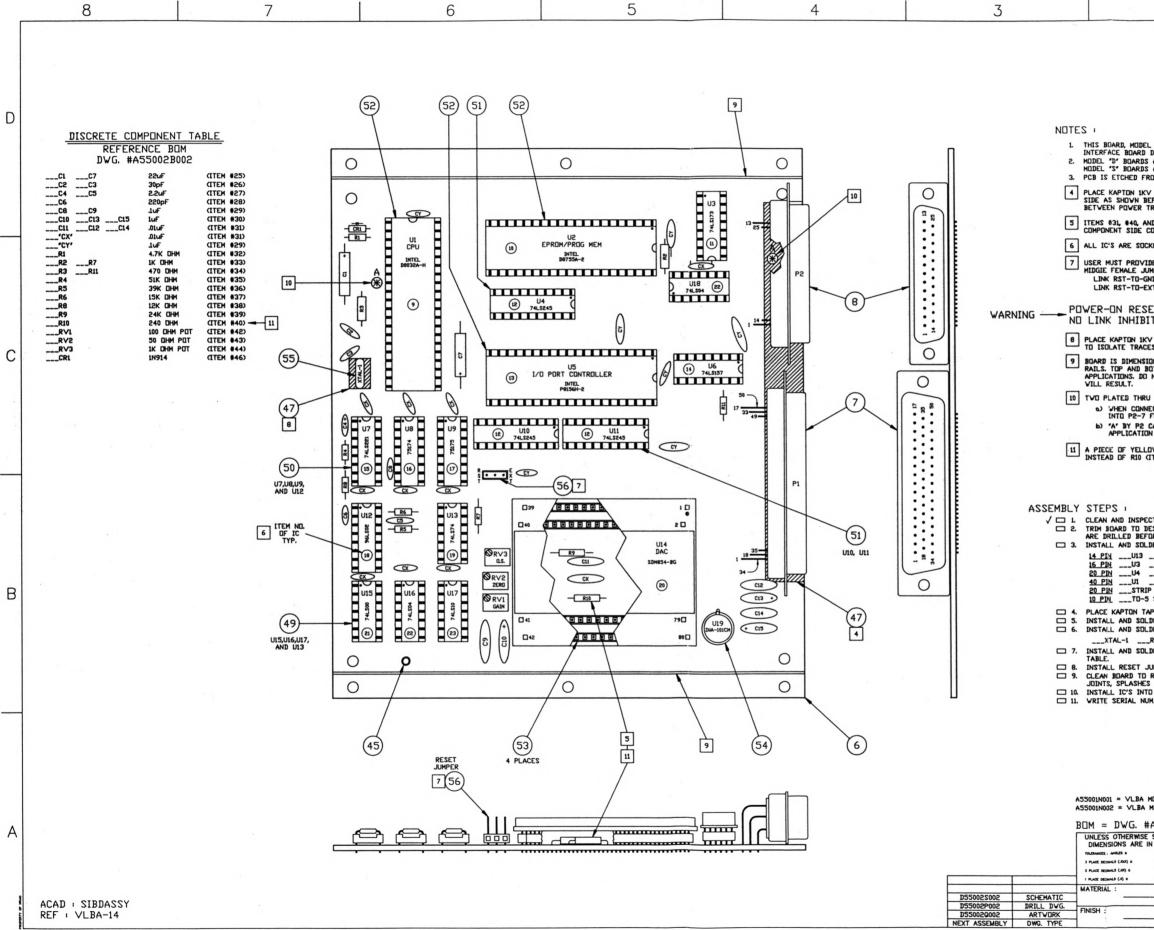

| • • • | STANDARD INTERFACE BOARD PHYSICAL DESCRIPTION |             |

|       | LIST OF DRAWINGS AND DRAWINGS                 |             |

| 6.0   | APPENDIX                                      | 1 <b>49</b> |

# LIST OF ILLUSTRATIONS

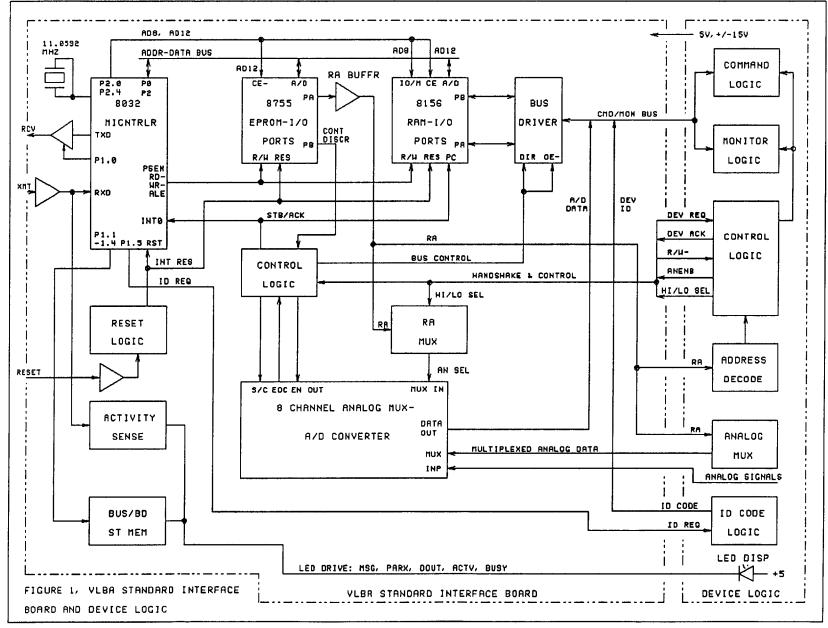

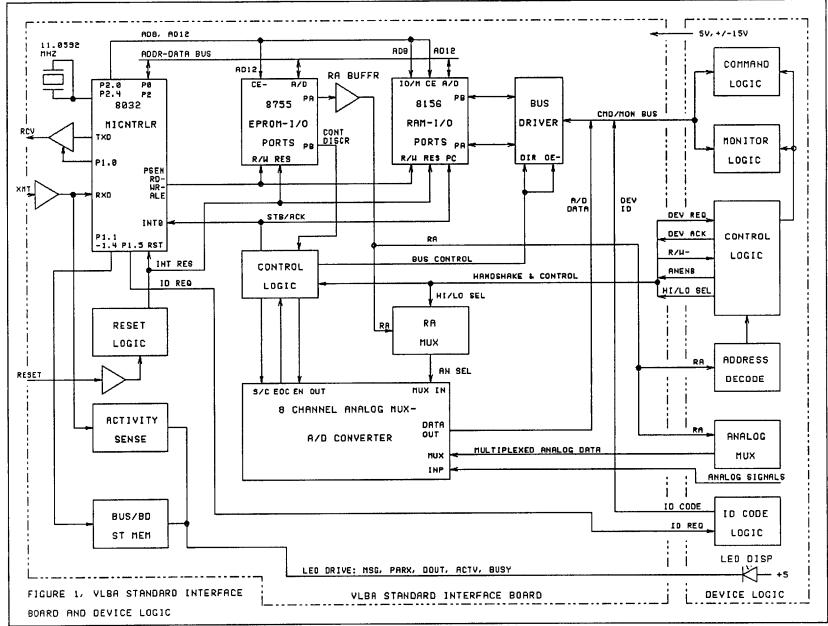

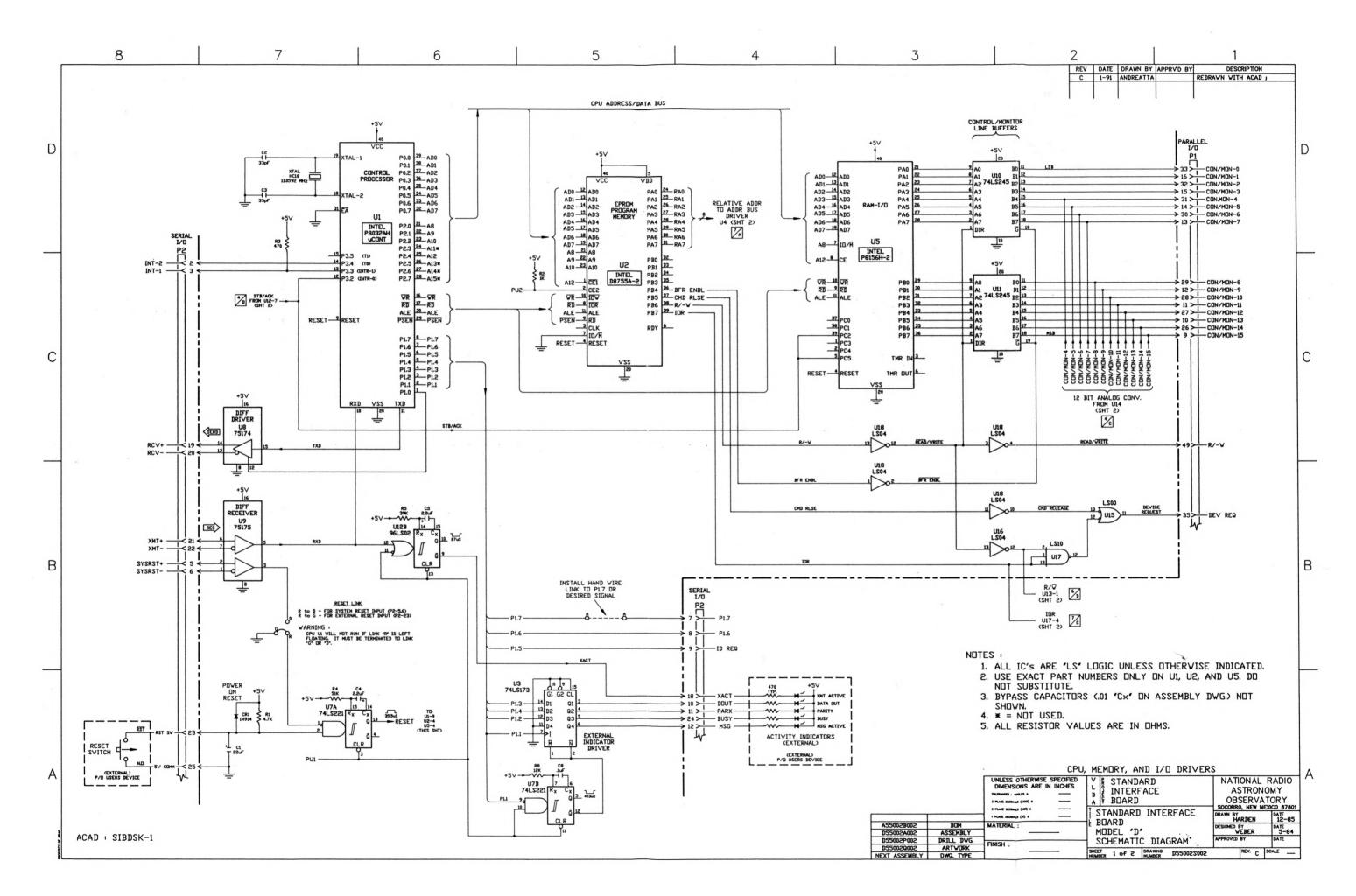

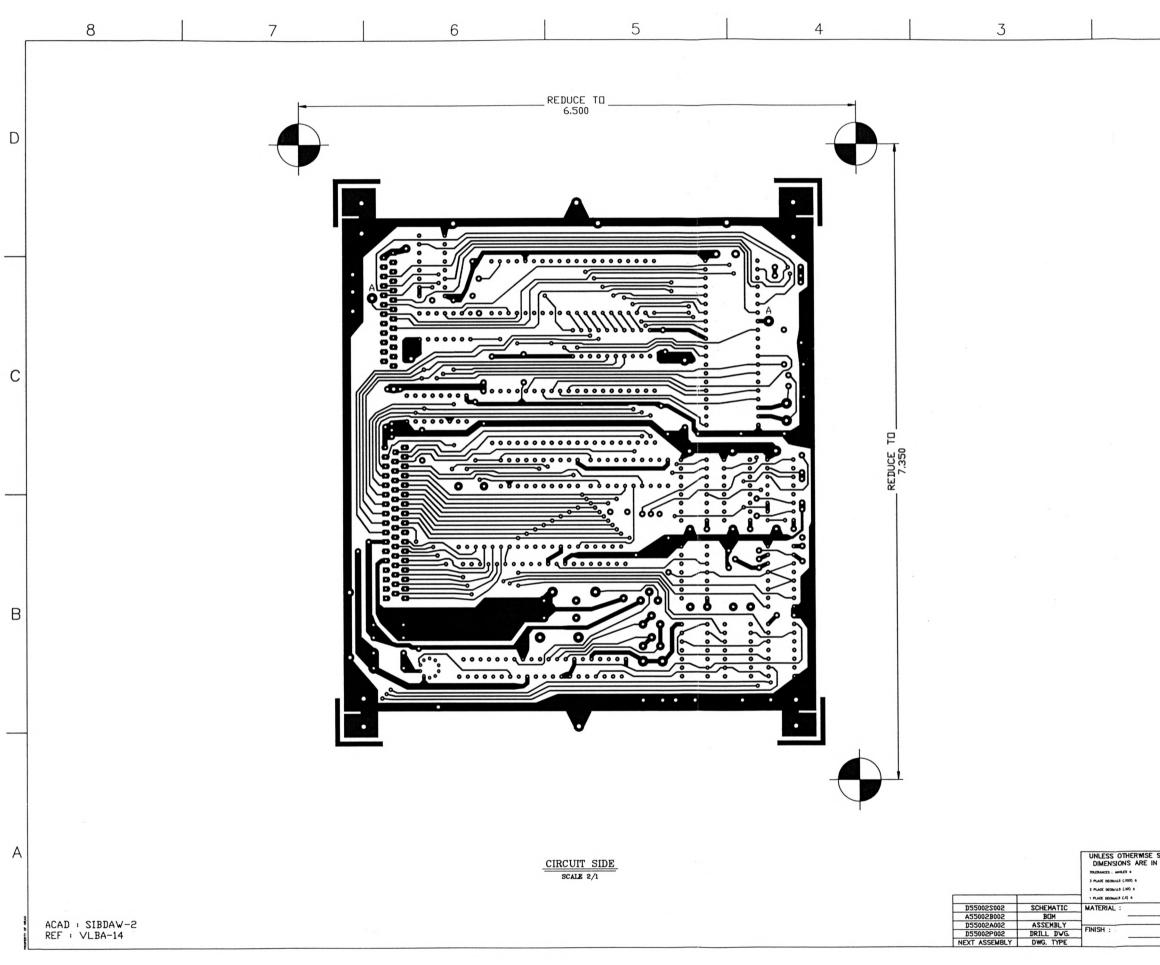

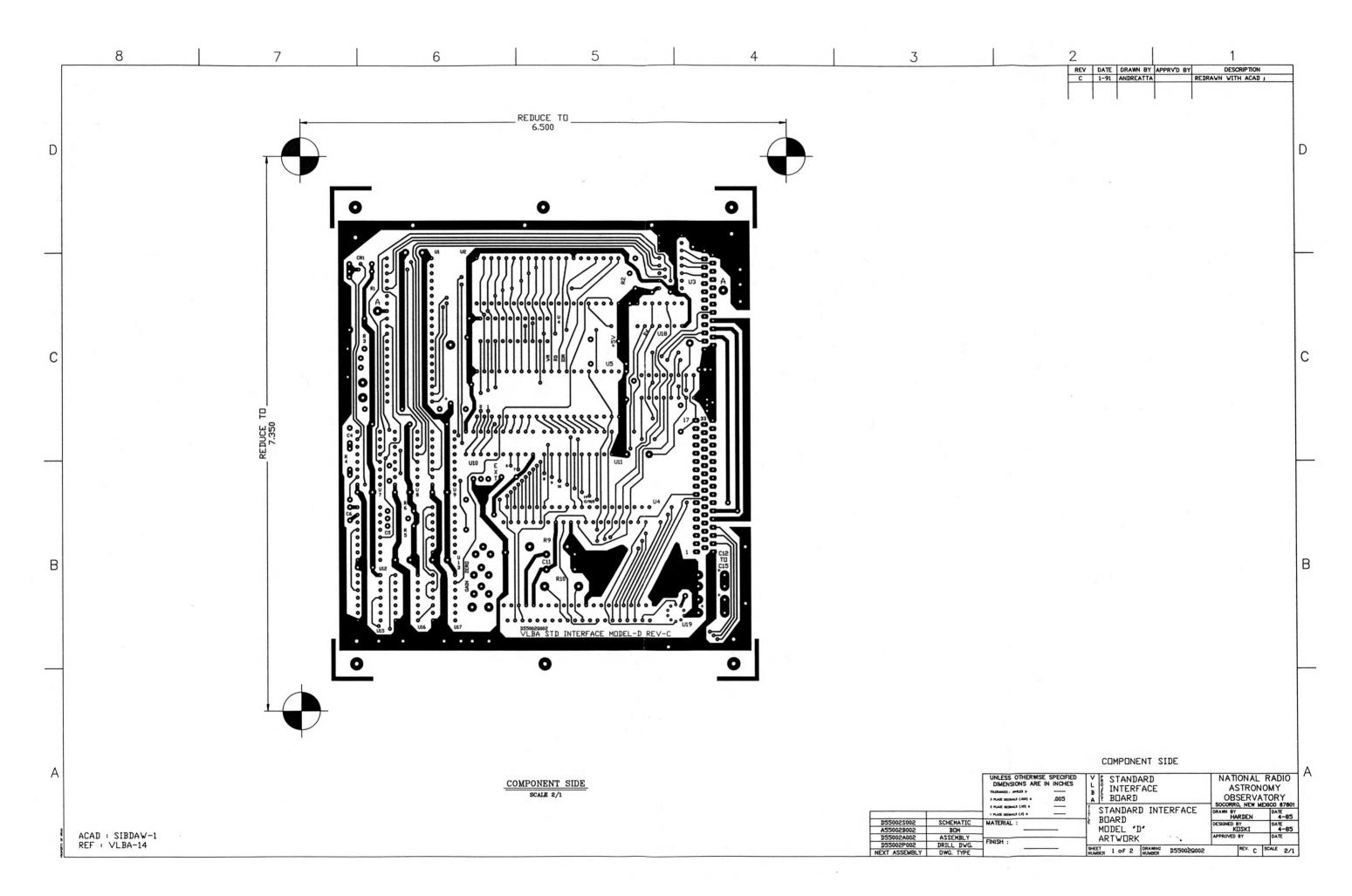

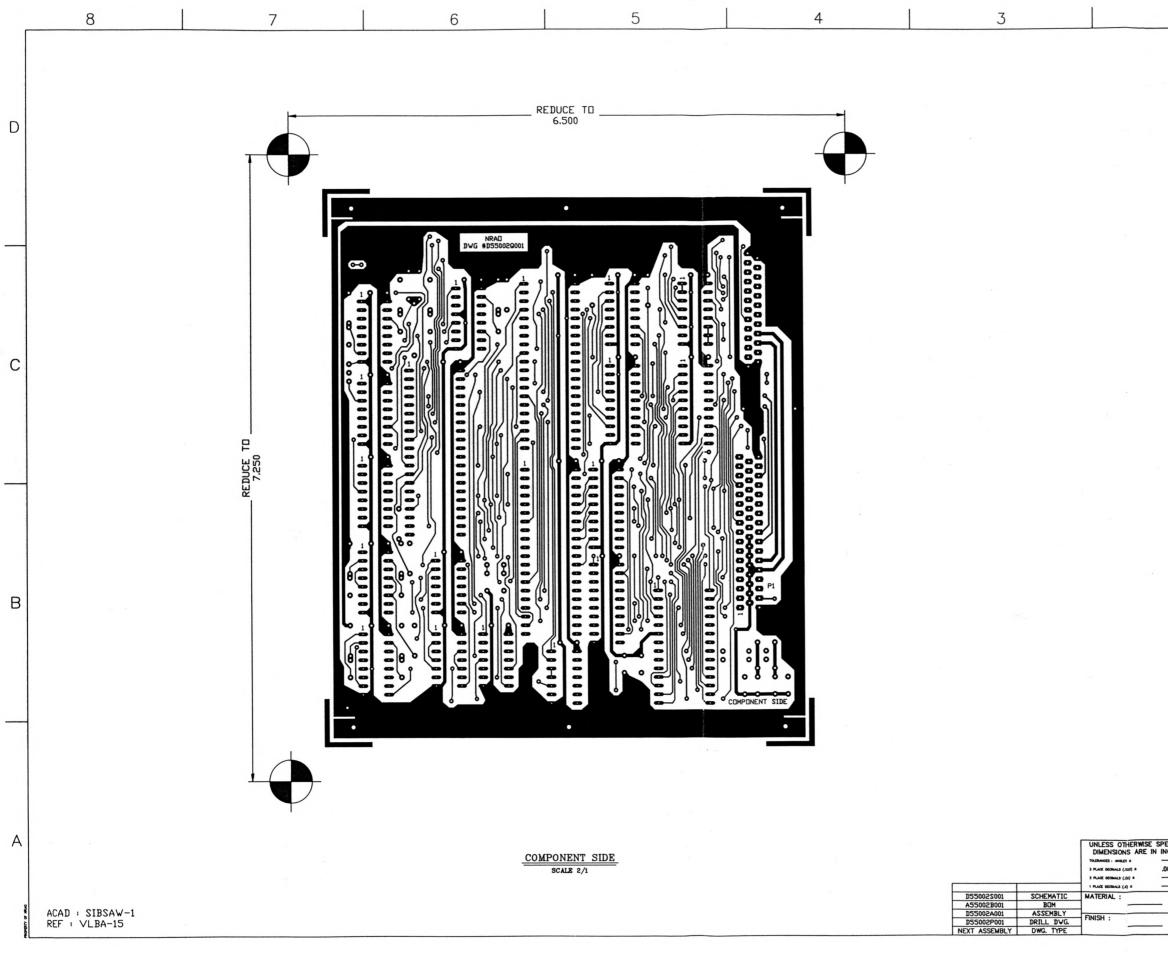

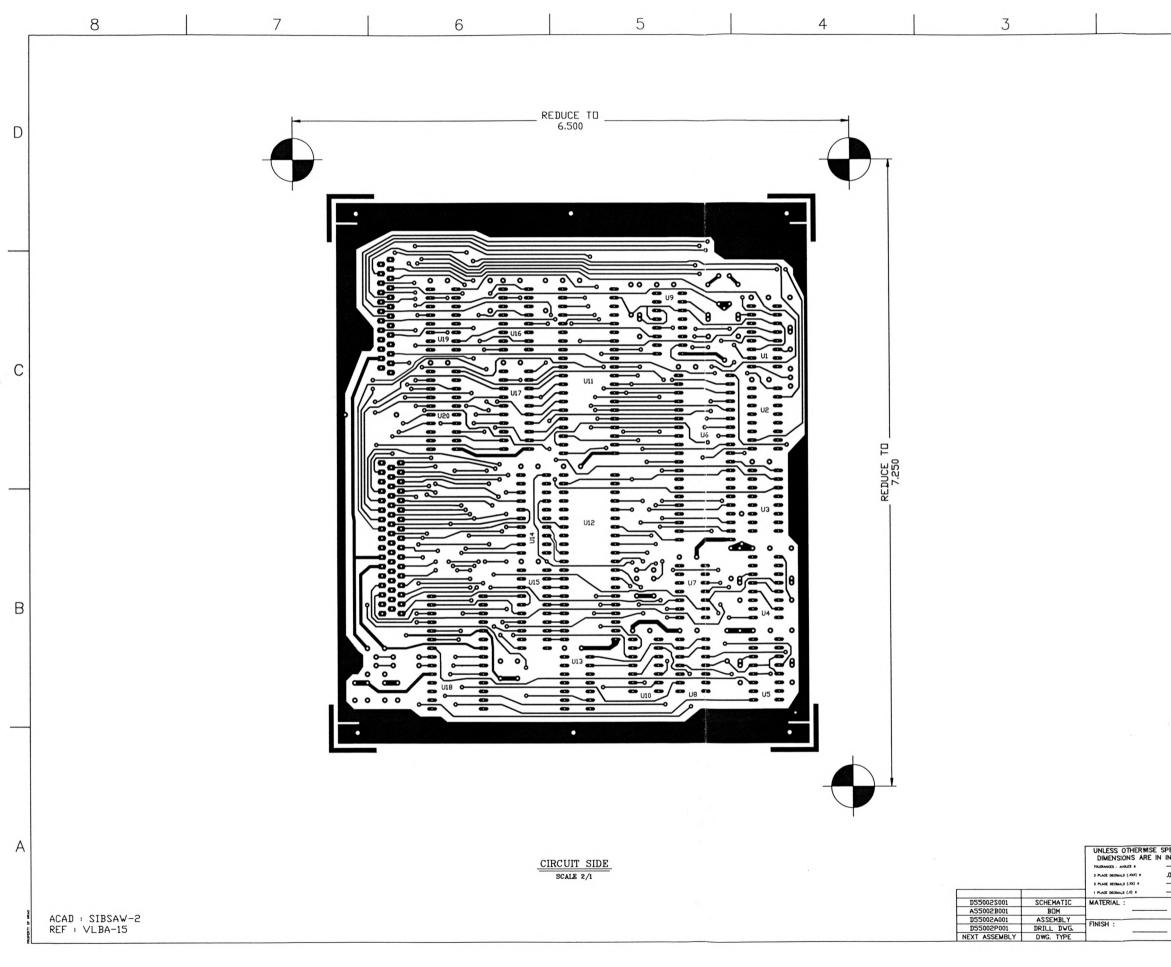

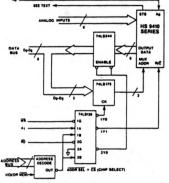

| Figure 1, VLBA Standard Interface Board and Device Logic          | 2   |

|-------------------------------------------------------------------|-----|

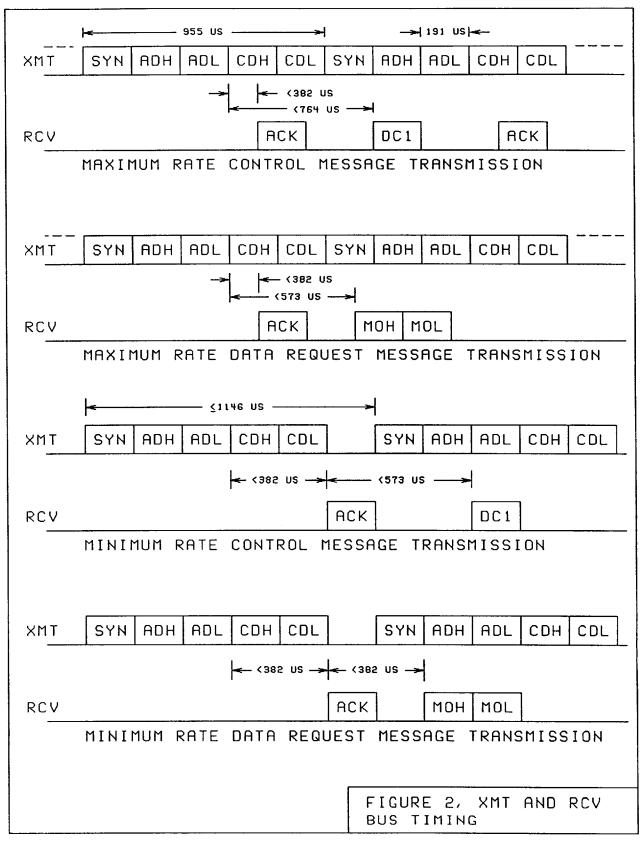

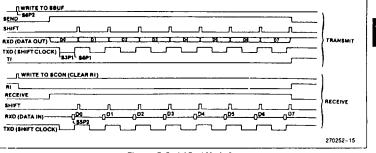

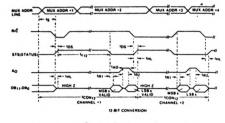

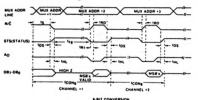

| Figure 2, XMT and RCV Bus Timing                                  | 8   |

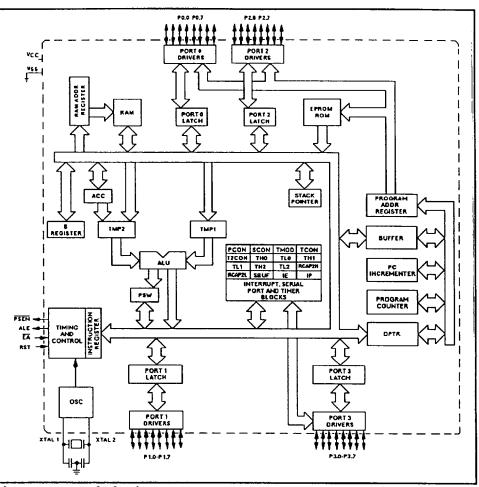

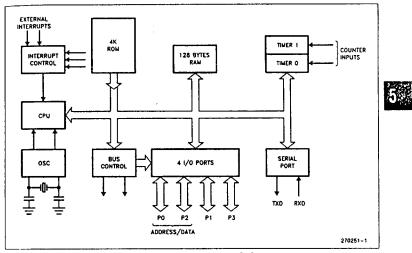

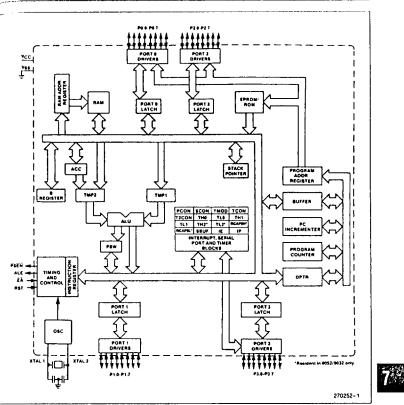

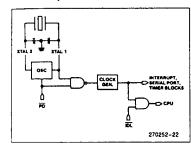

| Figure 3, 8032 Block Diagram                                      | 14  |

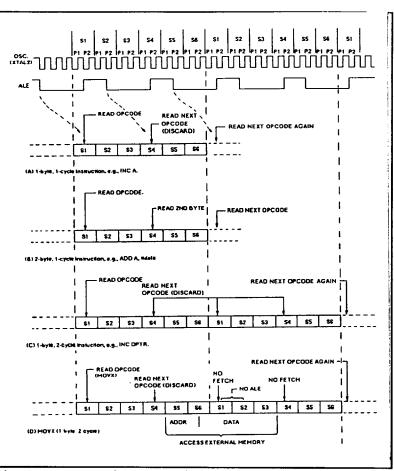

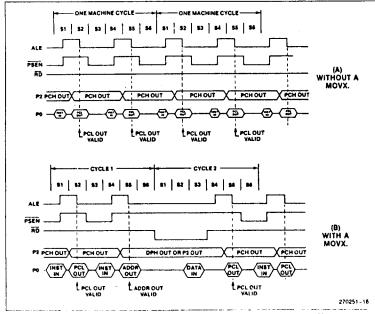

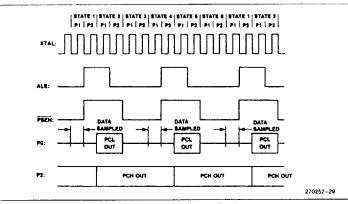

| Figure 4, 8032 Fetch-Execute Timing                               | 15  |

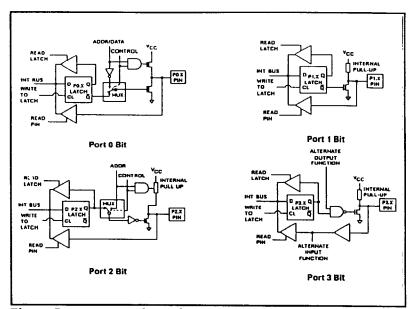

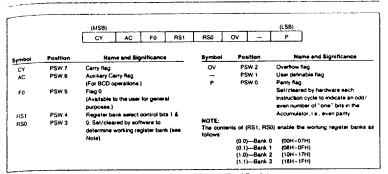

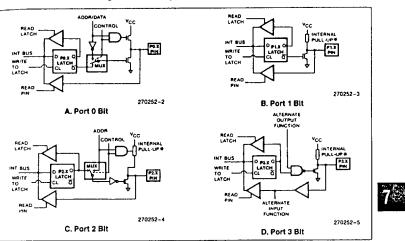

| Figure 5, 8032 Port Bit Latches and I/O Buffers                   | 16  |

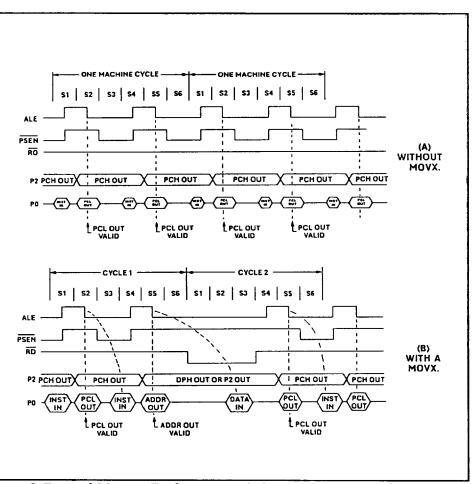

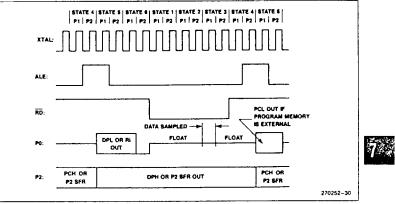

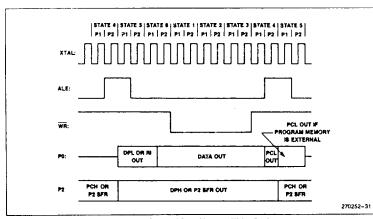

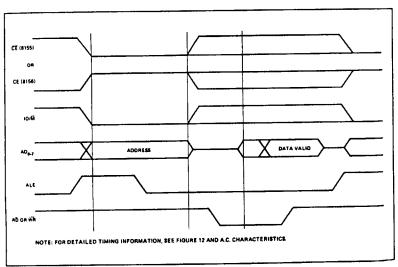

| Figure 6, External Memory Fetch/Execute Timing                    | 17  |

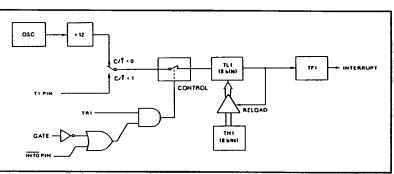

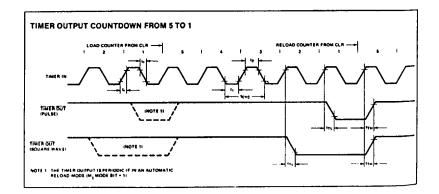

| Figure 7, Timer 1, Mode 2                                         | 19  |

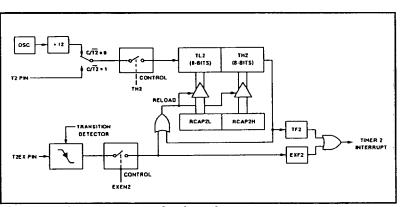

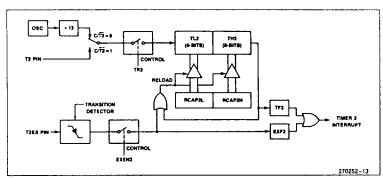

| Figure 8, Timer 2, Auto-Reload Mode                               | 21  |

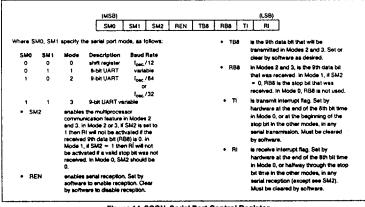

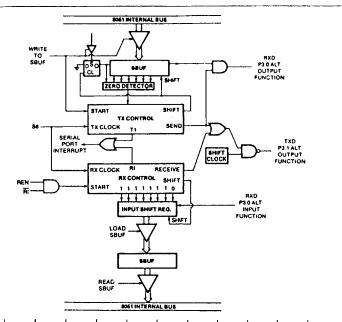

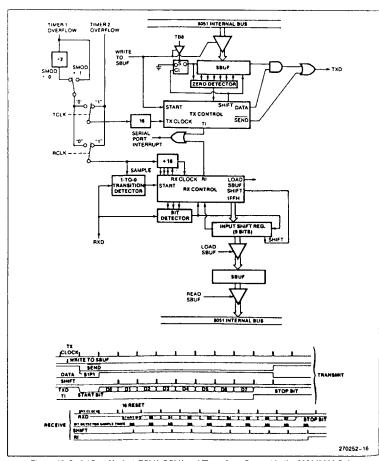

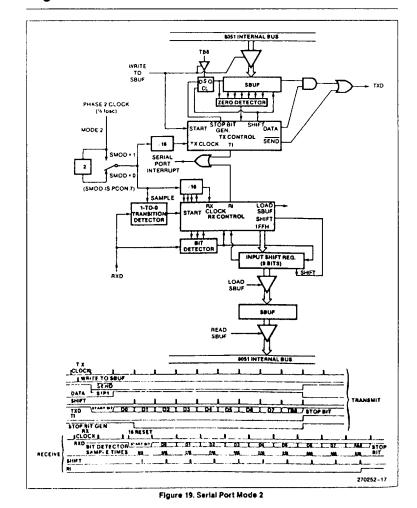

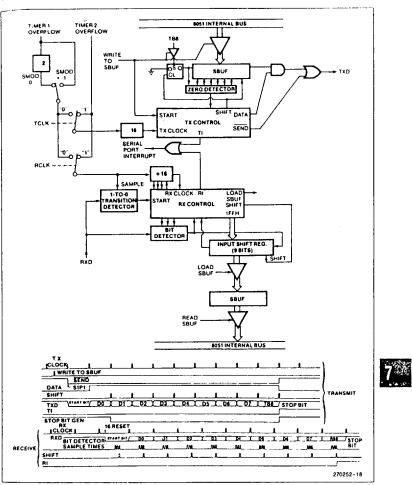

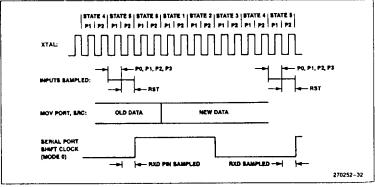

| Figure 9, Serial Port, Mode 3                                     | 25  |

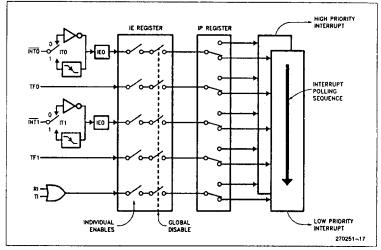

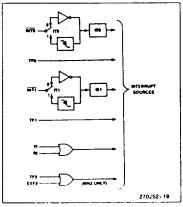

| Figure 10, MCS-51 Interrupt Control System                        | 27  |

| Figure 11, Interrupt Sources                                      | 28  |

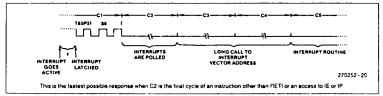

| Figure 12, Interrupt Response Timing                              | 30  |

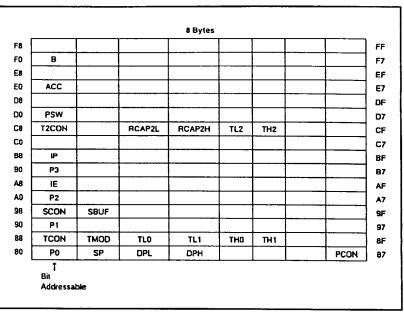

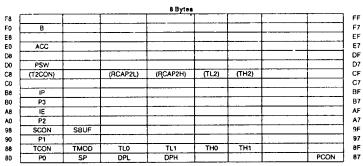

| Figure 13, SFR Memory Map                                         | 32  |

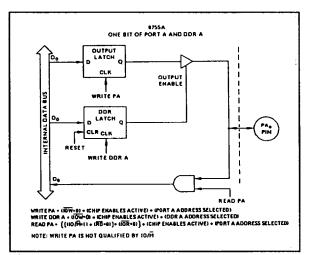

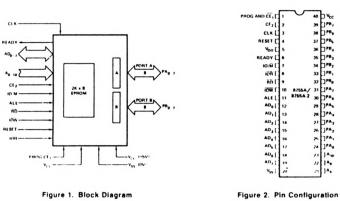

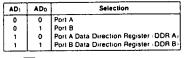

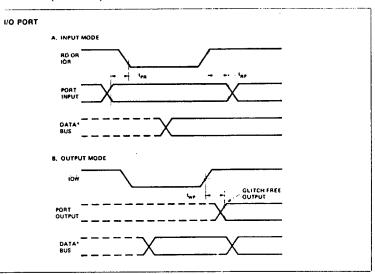

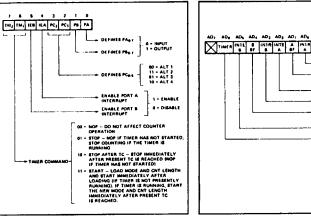

| Figure 14, 8755 I/O Port Structure                                | 33  |

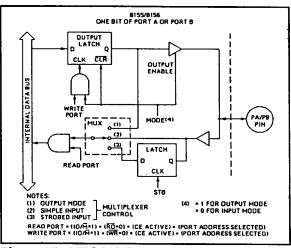

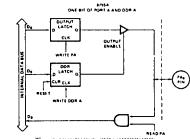

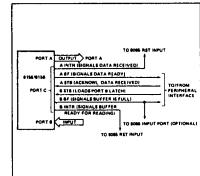

| Figure 15, 8156 I/O Ports Structure                               | 36  |

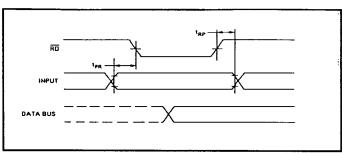

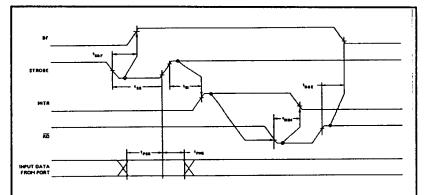

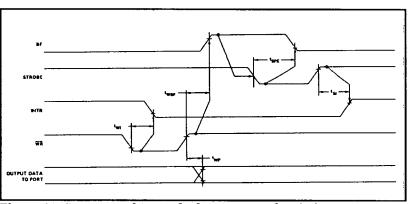

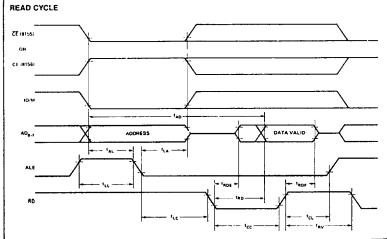

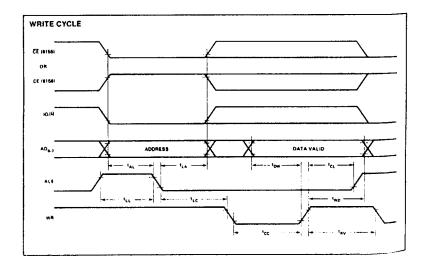

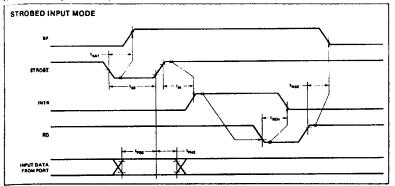

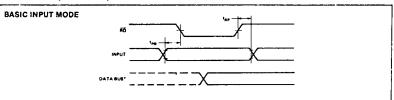

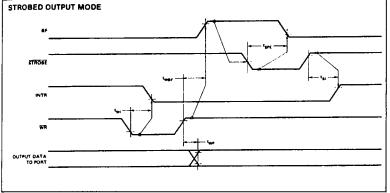

| Figure 16, Ports A and B Simple Input Timing                      | 37  |

| Figure 17, Ports A and B Strobed Mode Input Timing                | 37  |

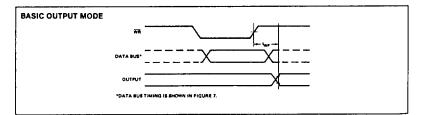

| Figure 18, Ports A and B Strobed Mode Output Timing               | 37  |

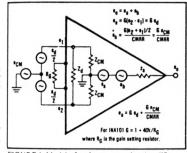

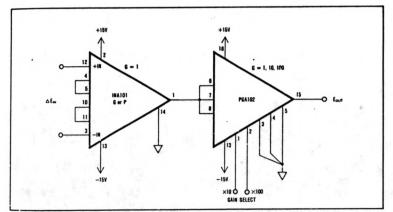

| Figure 1, VLBA Standard Interface Board and Device Logic          | 41  |

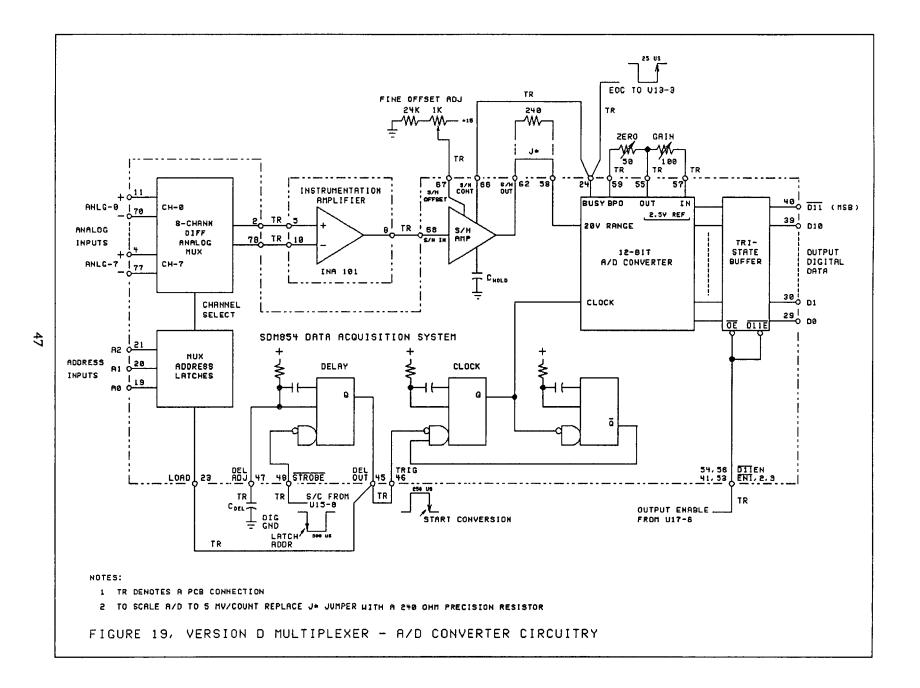

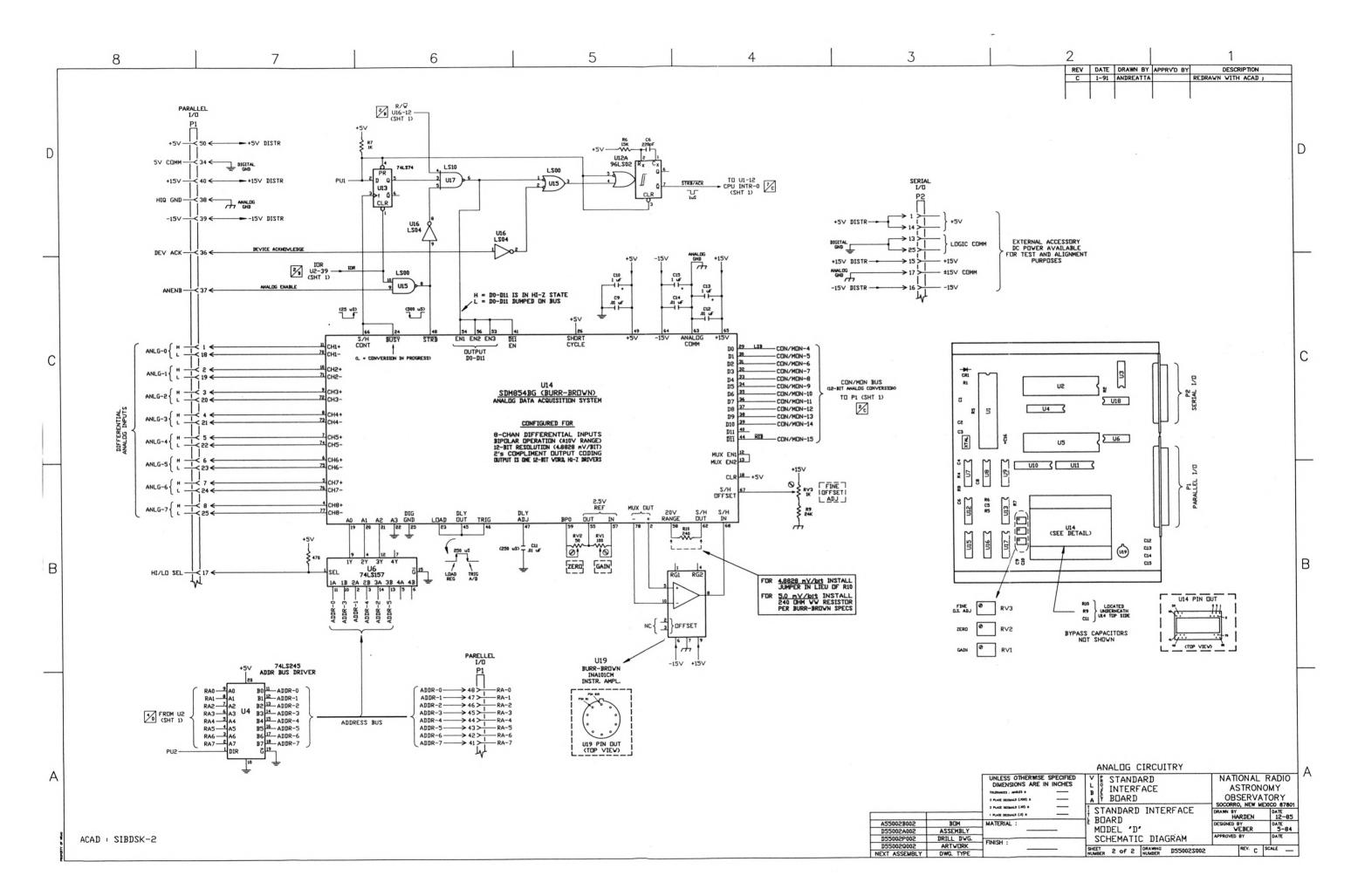

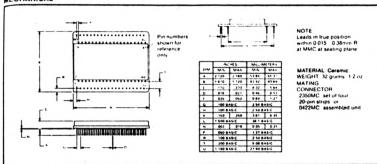

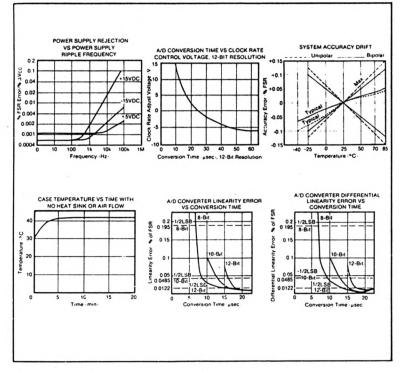

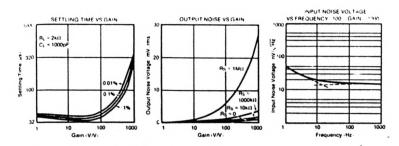

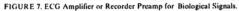

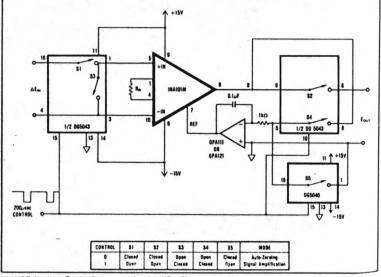

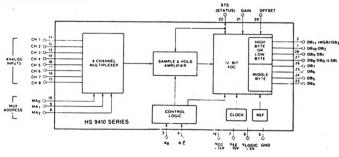

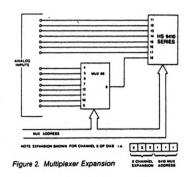

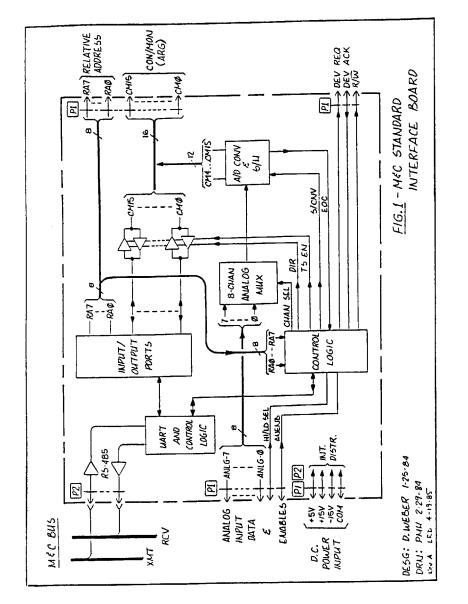

| Figure 19, Version D Multiplexer - A/D Converter Circuitry        | 47  |

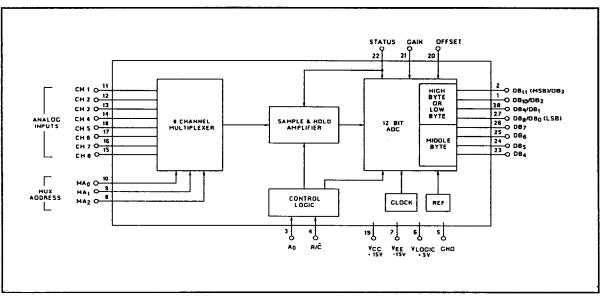

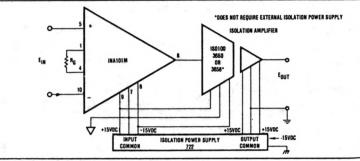

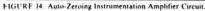

| Figure 20, HS 9412 12-Bit Multiplexer-A/D Converter Block Diagram | 49  |

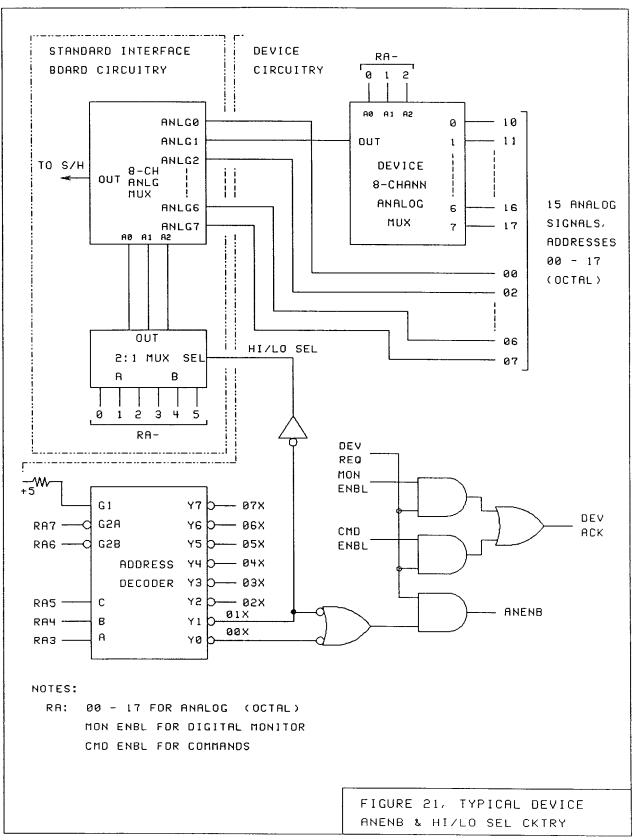

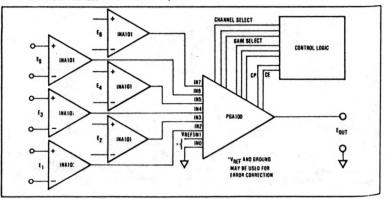

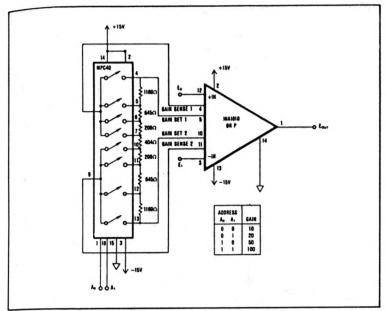

| Figure 21, Typical Device ANENB & HI/LO SEL Cktry                 | 52  |

| Figure 22, Interface Board Address Space (Hex)                    | 56  |

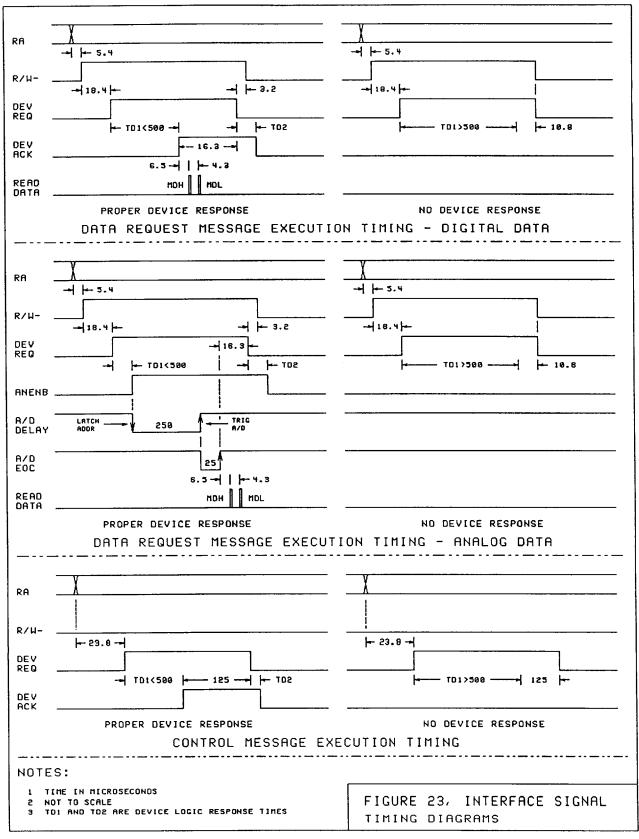

| Figure 23, Interface Signal Timing Diagrams                       | 58  |

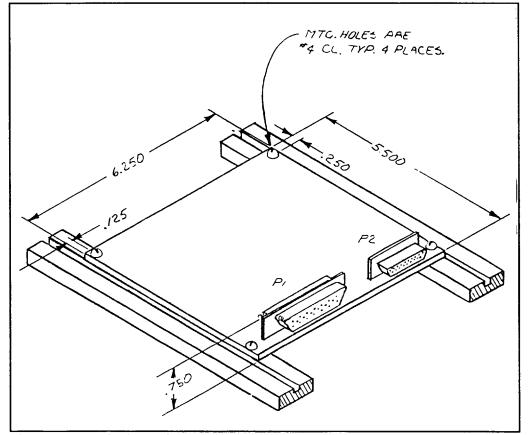

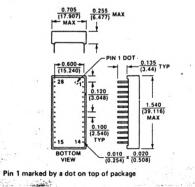

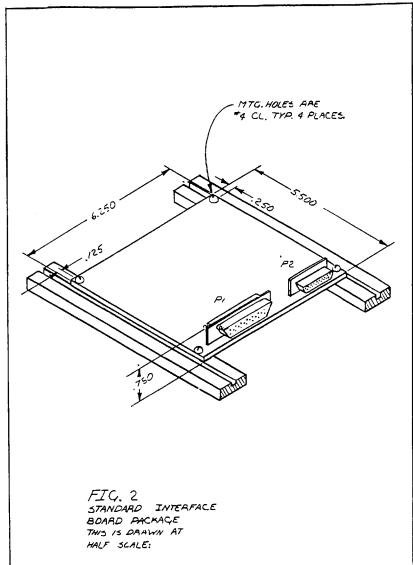

| Figure 24, Standard Interface Package                             | 135 |

# **1.0 INTRODUCTION**

This manual describes the VLBA Standard Interface Board used as a general purpose monitor and control interface in the VLBA Telescope Monitor and Control System. The Antenna Control Computer is the system Controller in this system. The Controller communicates with Standard Interface Boards installed in the system components (these components are called devices in this manual). The communication path is a two-pair, party-line, time-serial Monitor and Control Bus. The Controller (the computer) outputs time-serial, simplex mode, messages to the system devices via the Command (XMT) bus. XMT bus messages are either control messages to a device or monitor request messages to cause the device to return monitor data messages to the computer on the simplex mode, Monitor Data (RCV) bus.

The Standard Interface Board is typically a modular component of a device and functions as a serial-parallel converter to interface the Monitor and Control Bus to the devices that are to be controlled or monitored. Some devices are modules, such as a receiver control unit or an IF processor; other devices are subsystems, such as the subreflector position control system or the weather station. In either case, the use of the Standard Interface in monitor and control interfacing is very simple; the chief differences between applications are the character and volume of control or monitor operations to be performed.

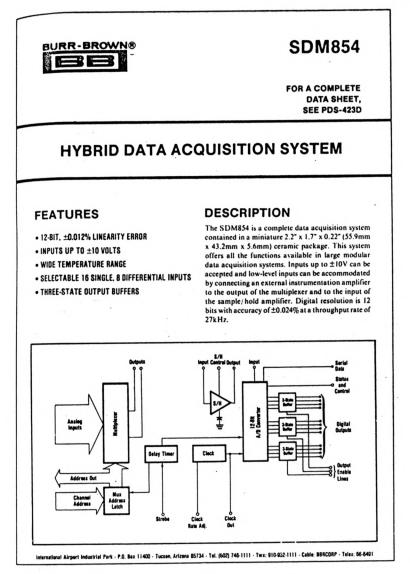

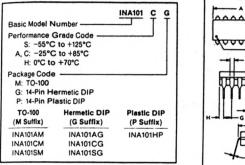

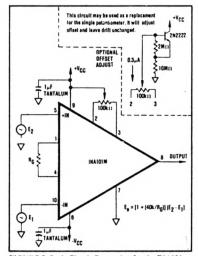

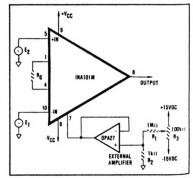

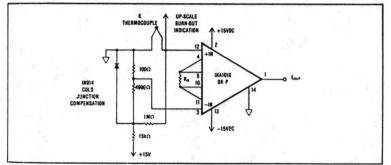

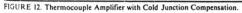

Because analog signal multiplexing and A/D conversion are frequently required, the Standard Interface Board contains an optional analog multiplexer-A/D converter. The converter is integrated into the logic of the interface so that it may be easily applied to analog signal monitoring applications. The analog multiplexing capacity of the interface may be extended by additional analog multiplexers installed in the device circuitry. The two versions of the Standard Interface Board differ in the type of analog multiplexing. Version "S" uses a single-ended multiplexer and version "D" uses a differential input multiplexer-instrumentation amplifier for applications where common-mode noise is a concern.

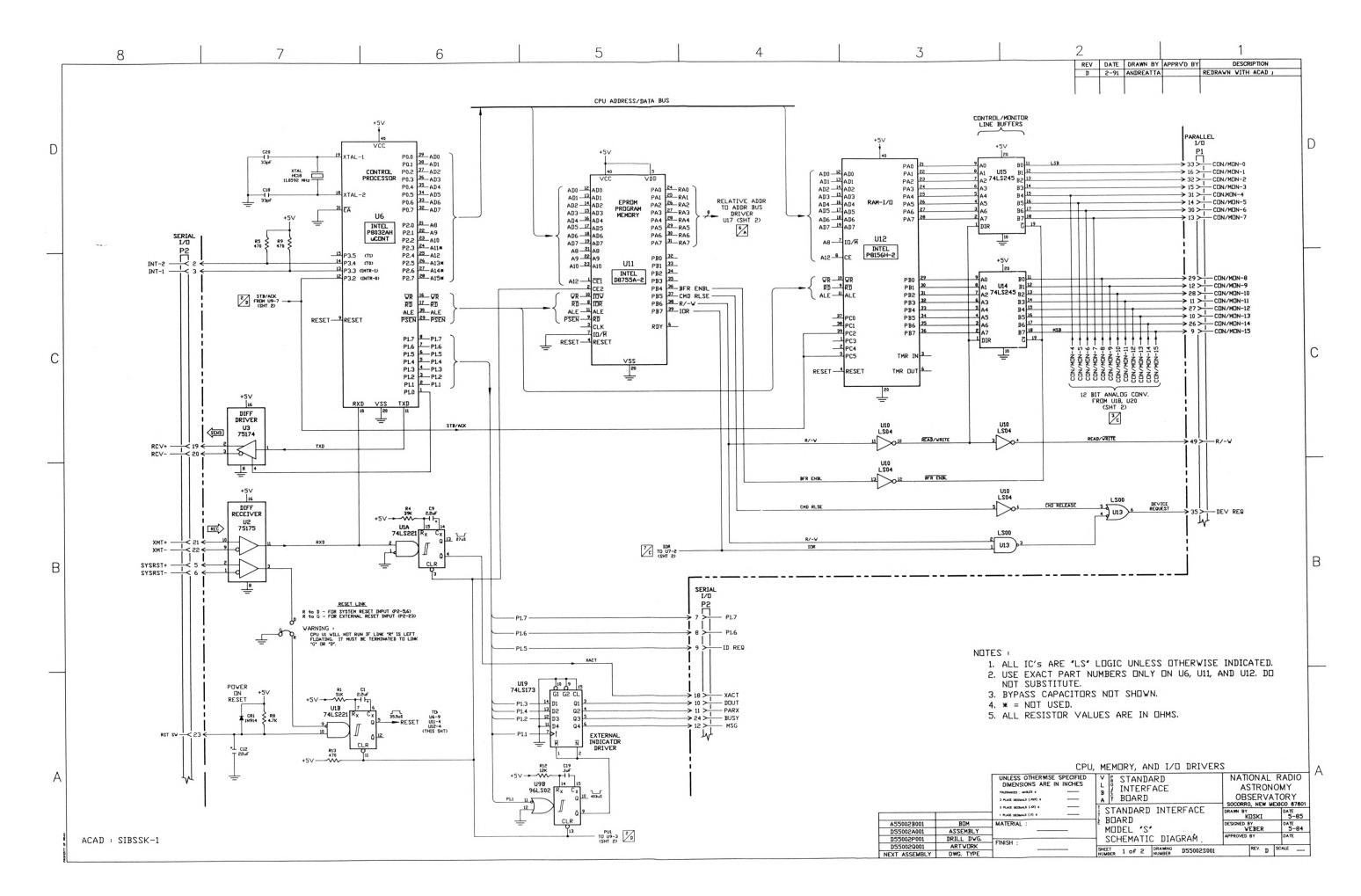

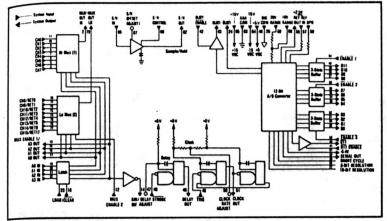

The VLBA Standard Interface Board is always used in conjunction with digital circuitry in the device that implements the device address, command and monitor data functions. Figure 1 (following this page) shows the block diagram of the Standard Interface Board and associated device logic.

This board has been used in several PC-controlled monitor and control systems. In these applications, the PC RS-232 serial port drives the Monitor and Control Bus via RS-232/RS-485 translator chips in the device logic. A Turbo Pascal driver program is available for these applications.

This interface board has also been used in NRAO applications which are not part of the VLBA project. The application information in this manual may be useful in these cases.

This single, general purpose interface board is used for most of the VLBA Monitor and Control system interface applications. Since it is a complete interface to the Monitor and Control bus, it reduces design time by obviating the need for any other bus interfacing design. Being a single design, it insures uniformity in the design of device control and monitoring circuitry because the logic designs conform to a single set of simple rules. The few cases in which this board is not used in the VLBA station are applications in which, for packaging convenience, the chips and firmware of the interface board are directly incorporated into device circuitry. In these cases, the operation of the interface circuitry is identical to that on the Standard Interface Board.

The VLBA Monitor and Control Bus (XMT and RCV) conform to the EIA RS-485 signal specification (Section 6 of this manual). The XMT and RCV bus message formats and protocol are described by specification A55001N001 (Section 6).

The Standard Interface Board is an address-restricted implementation of Specification A55001N002-A (Section 6). The board device address capability is 256 command and 256 data channels. In addition there are 16 interface internal command and 16 interface internal data addresses. The message format specifications (cited above) do not define the maximum size of an interface address block; it could be any size within the specified address range. The interface board specification is both a functional and physical specification in that it defines the functional properties, physical size, and I/O connector types and pin assignments.

Readers unfamiliar with these two specifications are urged to carefully review them before proceeding further in this manual; these specifications determined the hardware and firmware design of the interface.

# Manual Overview

This manual provides a detailed description of the digital and analog circuitry of the interface board and the control firmware which determines the operating characteristics of the interface. Subjects such as message formats, bus protocol, bus signal characteristics, the microcontroller and associated support chips, the analog multiplexer-A/D converters, device interface signals and timing are all described in detail. In addition, this manual describes typical device interface logic and address block assignments. The control firmware algorithms and firmware are fully described in Section 3. These subjects are listed on the Table of Contents and List of Illustrations.

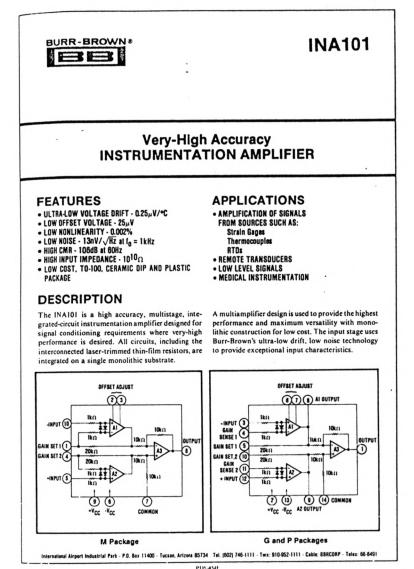

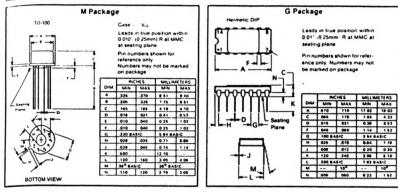

The characteristics of the Intel 8032 microcontroller which are important to the operation of the Standard Interface are described and 8032 data sheets included in Section 6. The characteristics of the Intel 8755 EPROM-I/O port chip and the 8156 RAM-TIMER-I/O port chip are also described and data sheets for these chips are included in Section 6.

The two types of analog multiplexer-A/D converters are described. Data sheets for these components are included in Section 6.

The EIA RS-485 specifications are included in Section 6.

#### Standard Interface Board Overview

The Standard Interface Board is a 6"x6"x.75" PC board suitable for installation in an NRAO module.

The address capacity of the Standard Interface Board is 256 device command channels and 256 device data channels. This is more than adequate for all reasonable applications. In addition there are interface internal command and data addresses associated with bus conditions and interface internal functions. These addresses consist of 16 command and 16 data channels. The analog multiplexing capacity of the board is 8 channels which may be easily expanded to a maximum capacity of 64 channels by the addition of one or more eight-channel analog multiplexers in the device circuitry.

The address range for all interfaces in a system is 32 K. A flag bit in the XMT message address field distinguishes control messeges from data request messages; thus the VLBA Monitor and Control system can accomodate up to 32K of control and 32 K of data request messages. The message formats and structure are described in Section 2.1.

The Controller assigns unique blocks of contiguous addresses to interfaces. The Interface Board uses a Device ID code (read from the device logic) as an index to the address block assignment stored in the interface's RAM memory.

The Standard Interface Board hardware and firmware design has diagnostic features to identify, record and report bus fault conditions (parity errors) and non-response of the device circuitry. The recorded fault and data conditions are parity error counts and address and arguments of the most recent control and data request messages. These values are read out of the interface as internal interface data. The Controller can set new values (typically resets to zero counts) by control messages. (The values in three addresses cannot be altered by the Controller). The interface can drive front panel display LED's to provide a visual indication of bus and board activity.

It is easy to interface the device logic with the Standard Interface Board; interface logic is simple address decode and hand-shaking. Logic timing is simple and non-critical. Timing diagrams in Section 2.6 graphically illustrate these relationships.

The use of even parity for message control function codes provides unique, unambigous message interface synchronization and response feed-back to the controller.

The VLBA Monitor and Control Bus operates at a 57.6 k-baud rate. The interface board may be adapted to operate at any of the (lower) standard baud rates by reprogramming the 8755 EPROM. Details of the baud rate selection are described in Section 2.7.

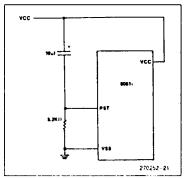

The Standard Interface Board has provisions for an external reset input to re-initialize the board logic and microprocessor via an RS-485 Reset (RST) bus. This feature may be selected by a jumper plug on the board. The VLBA Monitor and Control system does not use this reset feature.

### 2.0 THEORY OF OPERATION

### 2.1 MESSAGE FORMAT, PROTOCOLS AND TIMING

This section is an abstract of the bus specification A55001N001 and describes the characteristics of the serial VLBA Monitor and Control Bus. The bus Controller is the station computer and its interface to the bus. The Standard Interface in a device connects to the bus.

### Interface Address Block

Each Interface is assigned a block of contiguous addresses to which it alone responds. The block may be any length, but it must be disjoint with the address blocks of all other Interfaces. The last 16 addresses of each block are dedicated to monitor and control functions internal to the Interface. These functions are described below.

### Monitor and Control Bus

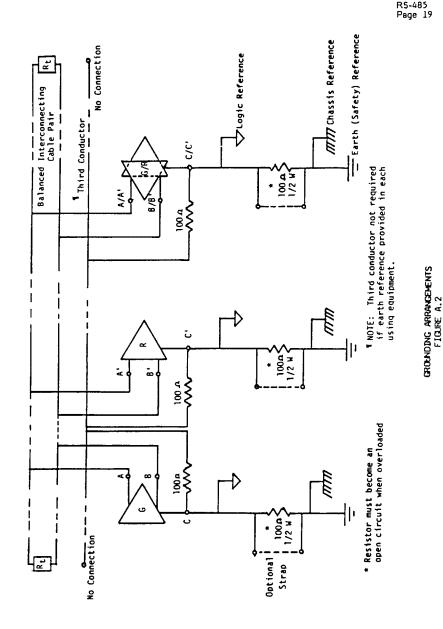

The bus consists of two differential-mode logic signals, each on a shielded twisted pair cable wired as a multi-drop party line. The bus signals are called Transmit Data (XMT) and Receive Data (RCV). There is one Controller (the antenna control computer) and numerous Standard Interfaces (in devices) are connected to the bus. The Controller is the only source of Transmit Data, and the Interfaces (one at a time) are the sources of Receive Data. Data is bit-serial at a rate of 57.6 kbaud and the transmissions are byte asynchronous. Each byte consists of, in order, a start bit (binary 0), eight data bits (least significant bit first), one parity bit, and one stop bit (binary 1).

XMT and RCV bus messages are combinations of data value bytes and control function codes. The data value bytes are address and argument values: Address High (ADH), Address Low (ADL), Control Data High (CDH), Control Data Low (CDL), Monitor Out High (MOH) and Monitor Out Low (MOL). Data value bytes are transmitted with odd parity.

Control function codes (bytes) signal the start of a message or report interface-device status during the execution of control and data request messages. The Control Function codes are: Synchronization (SYN), Acknowledge (ACK), Second Acknowledge (DC1), Non-Response Acknowledge (DC2) and Negative Acknowledge, (NAK). Control Function codes are transmitted with even parity.

# XMT Bus

Every message on the XMT bus is exactly five bytes long and the bytes occur in the following sequence: SYN, Address High (ADH), Address Low (ADL), Control Data High (CDH), and Control Data Low (CDL). The SYN byte indicates the beginning of a message, and is the only even bit parity byte on the XMT line (thus distinguishing it from all data bytes). The SYN byte is followed by ADH. If the most significant bit of ADH is 1, then the message is a control message; otherwise it is a monitor request message. The remaining 15 bits of ADH/ADL form a binary address in the range of 0 through 32767.

Each Standard Interface receives ADH and ADL of every message on the XMT line (there is no dead time during which an interface is not listening). Each Interface is assigned a block of contiguous addresses to which it alone responds. The block may be any length, but it must be disjoint with the address blocks of all other Interfaces. The last sixteen addresses of each block are dedicated to functions occuring within the Interface, as described below under Interface Board Parameters. The Interface must check parity on all bytes received. If SYN has a parity error, an internal counter (BE-4, invalid SYN character counter) is incremented. The value of this counter is assigned to a monitor address.

If ADH or ADL has a parity error, the Interface does not respond (just as if the address were outside its block), but increments an internal address parity error counter (BE-7, address parity error counter) and looks for the next valid SYN. The value of this counter is assigned to a monitor address.

If the address transmitted is within the assigned interface address block, then within 382 microseconds of the last bit (Stop) of ADL, that interface must begin to transmit a one byte acknowledge code (ACK) on the RCV line. If the message was a control message (indicated by a 1 in the msb of the address), then the Interface must also receive and store CDH and CDL, and within 382 microseconds of the end of CDL or 573 microseconds after the initial ACK was put on the line (whichever occurs later) it must begin to transmit a second acknowledge byte (DC1) on RCV.

If SYN, ADH, ADL, CDH and CDL have valid parity, the address is within the assigned block, a control message is specified and the device responds to the interface handshaking properly, a DC1 acknowledge code is transmitted on the RCV line.

If SYN, ADH and ADL have valid parity, the address is within the assigned block and a control message is specified, but CDH or CDL has a parity error, then the second acknowledge byte (DC1) is replaced by a negative-acknowledge code, NAK. In this case CDH/CDL is not passed to the device and a control data parity error counter is incremented. The value of this counter is assigned to a monitor address. A second form of negative acknowledge byte (DC2) is returned if the interface is unable to complete its handshaking with the device to which it interfaces. [This may occur (but does not necessarily occur) if the device is powered down or unplugged, and signals other conditions in which the state of the controlled device is not altered (for commands) or for which it is not meaningful to return monitor data.] The non-response condition is counted by two internal counters: BE-12 for control messages and BE-11 for monitor data request messages.

If the message is a monitor request message within the address space assigned to monitor data, the CDH and CDL byte values are ignored, they have no meaning. The parity of CDH/CDL is, however, tested and the control data parity error counter is incremented if tainted by an error. In this case, the monitor data specified by ADH/ADL is returned in the normal manner because the CDH/CDL parity error has no effect upon the validity of the monitor data.

# **RCV Bus**

Messages on the RCV line are either a two byte command acknowledgement or a two or three byte monitor data acknowledgement, as follows:

Command acknowledgement messages are: 1) ACK, DC1 (normal, no fault command execution acknowledgement), 2) ACK, NAK (CDH/CDL parity error acknowledgement), and 3) ACK, DC2 (device non-response acknowledgement).

Monitor request acknowledgement messages are: 1) ACK, MOH, MOL (normal, no fault acknowledgement followed by two bytes of monitor data obtained from the address specified by ADH/ADL); 2) ACK, DC2 (fault acknowledgement, monitor data is unavailable from the device).

The Controller also checks parity on all bytes received on the RCV line. In the event that monitor data or function codes have parity errors, the Controller application software notes the errors and disqualifies the data.

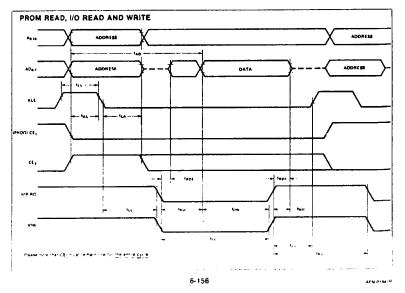

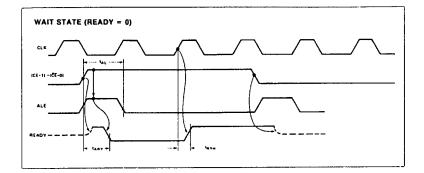

### **Bus Timing**

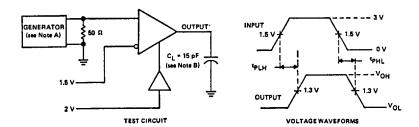

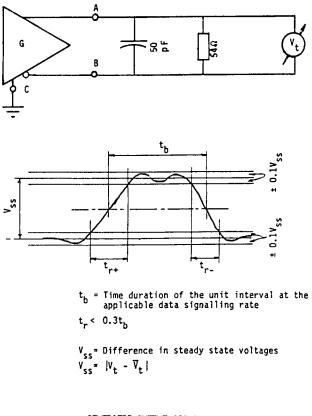

The first acknowledge byte (ACK) will also function as a clear to send to the controller, granting the controller the right to begin its next message, and promising to yield the RCV line before it is needed for another interface's response. (The time available to it is at least 764 microseconds, but may be longer if the controller has not begun to transmit CDL on the XMT line at the time the interface begins to send ACK on the RCV line; the interface will have at least 573 microseconds after the end of transmission of CDL to disconnect from RCV). Figure 2 (on the next page) shows the timing relationships.

The Controller may begin transmitting another message following a control message after the receipt of the acknowledge (ACK) byte. The maximum-speed timing (in the sense that all transactions are limited by line speed) for a sequence of control messages and for a sequence of monitor requests is illustrated in Figure 2. The minimum speed timing (in the sense that the controller is responding as rapidly as permitted by this protocol, while the interfaces are responding as slowly as permitted by this protocol) is illustrated in Figure 2.

Note from the figures that in the maximum rate mode of control message reception, the interface is transmitting the second acknowledgement (DC1) concurrent with the reception of a new control message; DC1 is being transmitted at the same time that ADH for the new message is being received on the XMT bus. This concurrency requires that the microprocessor manage both message transmission and reception operations concurrently.

Note also from the figures that in the maximum rate mode of monitor request message reception, MOH/MOL are being transmitted on RCV at the same time that a new message is being received on the XMT bus. Like the case above, the microprocessor must manage both types of message operations concurrently.

### **Function Codes**

The hexadecimal byte values for the control function codes are as shown below. These bytes are transmitted in even parity which makes them unique since data bytes are odd parity.

SYN - 16, Synchronization byte which prefixes all messages from the controller.

ACK - 06, First acknowledgement byte to the controller which signifies that SYN was detected and that SYN, ADH and ADL did not have parity errors. ACK is not transmitted if there was a parity error on any of these three bytes.

DC1 - 11, Second acknowledgement byte to the controller which signifies that in the case of control messages, there were no parity errors in CDH/CDL and the device responded properly to the interface-device handshaking requirements.

NAK - 15, Negative acknowledgement byte to the controller which signifies that, for control messages, CDH/CDL was tainted by a parity error.

DC2 - 12, Second negative acknowledgement byte to the controller which signifies that the device logic did not respond to the interface handshaking within the allocated time period. This non-response acknowledgement is used for both control and monitor request messages.

#### Interface Internal Monitor and Control Functions

The last 16 addresses in the address block are allocated to Monitor and Control parameters internal to the Standard Interface board. The occurance of bus fault conditions (such as parity errors, invalid SYNC, etc.) are accumulated in counters and are available for monitor data readout by the Controller. Device non-response events are also accumulated. These parameters were described above. The counters are capable of being reset or set to other values by a control message from the Controller.

Other parameters in this block are the Interface Type and Revision level, Block ID Code (N) and Address Block start address. This Block ID Code is the index for assignment of the address block by the Controller. None of these locations can be overwritten by the Controller. The last three addresses in the block are reserved for future assignment.

These Interface addresses are identified by the notation: BE-1, BE-2, etc. where BE designates the Block End (last) address. The assignments are as follows:

| Address | Value                                                                    |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------|--|--|--|--|--|--|

|         |                                                                          |  |  |  |  |  |  |

| BE-15   | Reserved for future use                                                  |  |  |  |  |  |  |

| BE-14   | н н н П                                                                  |  |  |  |  |  |  |

| BE-13   | 81 18 18 18                                                              |  |  |  |  |  |  |

| BE-12   | No Control Response counter (i.e, no DEV ACK from device)                |  |  |  |  |  |  |

| BE-11   | No Monitor Response counter (i.e., no DEV ACK or ANENB from device)      |  |  |  |  |  |  |

| BE-10   | Interface Type and revision code (cannot be altered by the Controller)   |  |  |  |  |  |  |

| BE-9    | Address of last control message received. (i.e., ADH and ADL)            |  |  |  |  |  |  |

| BE-8    | Control data for last control message received. (i.e., CDH and CDL)      |  |  |  |  |  |  |

| BE-7    | Address parity error counter, all messages                               |  |  |  |  |  |  |

| BE-6    | Control data parity error counter, all messages                          |  |  |  |  |  |  |

| BE-5    | Invalid SYN character                                                    |  |  |  |  |  |  |

| BE-4    | Control data parity error counter, messages in block                     |  |  |  |  |  |  |

| BE-3    | N, ID byte value from device logic (cannot be altered by the Controller) |  |  |  |  |  |  |

| BE-2    | Count of correctly received control messages                             |  |  |  |  |  |  |

| BE-1    | Count of correctly received monitor data request messages                |  |  |  |  |  |  |

| BE-0    | Address of beginning of block (cannot be altered by the Controller)      |  |  |  |  |  |  |

The addresses designated by bold print cannot be altered by the Controller. The reasons for this restriction are described in Sections 2.5 and 3.3.

### **Bus Description**

Important properties of the VLBA Monitor and Control bus are as follows:

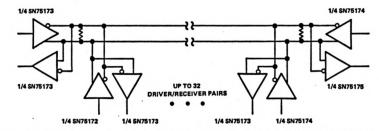

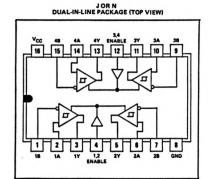

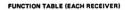

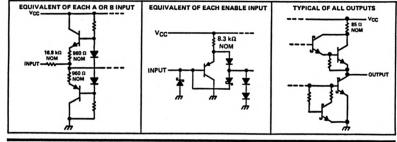

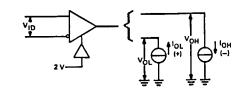

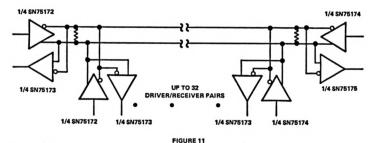

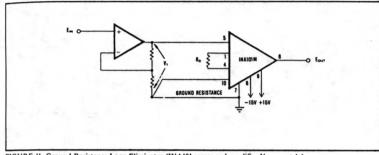

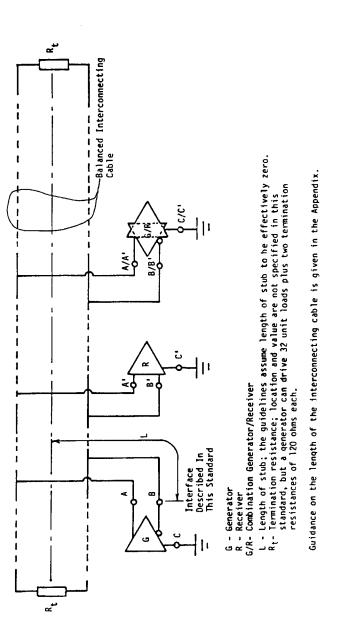

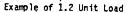

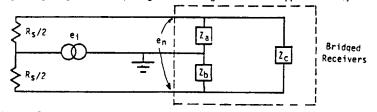

RS-485 specifications permit up to 32 drivers and receivers on a bus. Thus an RCV line could have up to 32 drivers and one receiver (the Controller), and a XMT line could have one driver (the Controller) and up to 32 receivers in Standard Interfaces. Bus drivers and receivers are 75174 line drivers and 75175 line receiver chips which conform to the EIA standard RS-485 specifications.

In the VLBA station, there is a possibility that the Monitor and Control Bus may have to service more than 32 devices. This exceeds the capacity of a single XMT driver chip in the controller and the capacity of the interface RCV driver chips. To provide adequate drive capacity and to simplify cabling, three bus cable runs are used between the controller and devices in the station. These three buses use separate driver chips that are driven by a single XMT signal from a UART; there is no XMT selection of cable runs by the controller. The UARTs that service the three RCV receiver chips are read by the controller in sequence. The first cable run is used to service devices in the station building (this includes the weather station). Approximately 29 devices are serviced by this bus run. The second cable run services devices in the antenna Pedestal room; approximately 4 devices are serviced by this cable run. The third cable run services devices in the antenna Vertex room; approximately 16 devices are serviced by this cable run.

The bus transmission rate is 57.6 kbaud, including all framing and parity bits. The transmission rate may be lowered by reprogramming the 8032's baud rate generator counters in the EPROM firmware.

The bus transmission lines are #24 twisted pair, shielded, (roughly 100 ohms characteristic impedance), max length 500 feet, terminated with a 100 ohm resistor. Belden # 9842 cable is used for the bus cable runs between electronics racks. Bus wiring within a rack is two pairs of unshielded wire. At the end of the bus run, 100 ohm terminating resistors terminate the bus.

All rack bus connectors are Cinch or Amphenol DE-9S or equivalents. All bus cable connectors are DE-9P connectors or equivalents.

Controller and interface bus drivers and receivers are bridged across the XMT and RCV bus lines with stubs less than 20 feet.

RCV bus drivers are tri-state, connected to the bus only when required to respond to a monitor request. RCV drivers maintain their high impedance state when the interface is unpowered.

To provide bus line high-voltage safety, clipping surge arrestors are used on the bus lines between the control building and the antenna. Surge arrestors are located at each end of the bus cable run and shunt the surge currents to antenna frame and building counterpoise ground.

Interfaces which service equipment subject to lightning-induced currents are protected by optical isolators with high voltage (typically 2500 volts) hold-off capability. Examples of such devices are the subreflector drive, the weather station, and feed heater controller. In the case of the weather station, a fiber optics interface drives the bus lines to the Standard Interface Board in the weather station enclosure. In the subreflector position controler, the bus is protected by optical isolators which are interposed in the discrete signal lines between the controller and the apex. Resolver signals are protected by surge arrestors and isolation circuitry in the R/D converters. In the case of the feed heater controller that powers heaters in the dish, optical isolators in the controller isolate the controller from the Utility Interface.

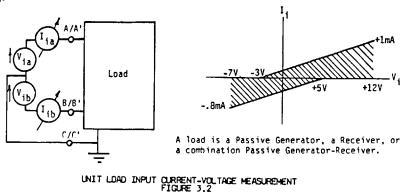

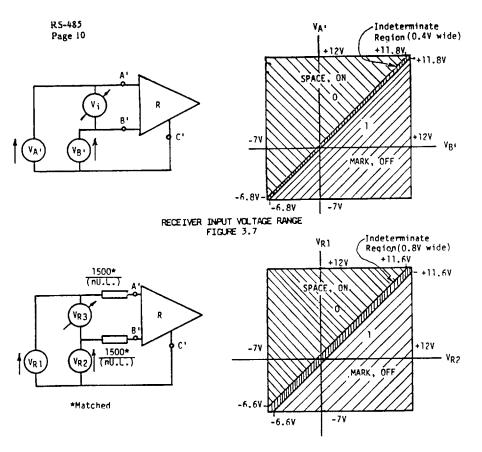

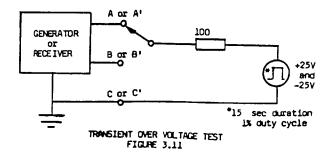

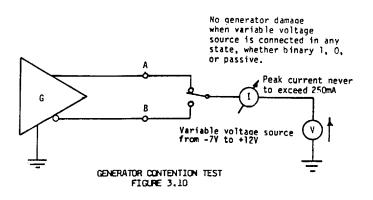

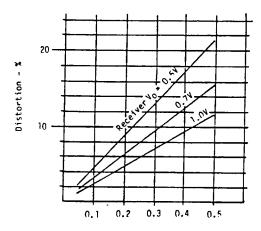

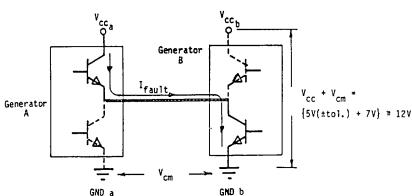

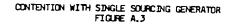

Bus signals shall conform to EIA RS-485. Important properties of the RS-485 specification are:

Transmission and reception modes are differential, +-2 to +-6 volt signal range.

Drivers and receivers are capable of operation in the presence of common mode voltages between -7 to +12 volts.

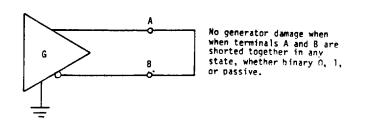

When two or more drivers contend for a bus, there is no device damage but the bus signal may be distorted or garbled.

The maximum driver output current in the tri-state condition is - +- 100 ua.

The maximum driver output current with power off is: - +- 100ua.

Receiver input sensitivity is +- 200 mv, minimum, differential mode.

The receiver input resistance is 12 kohms, minimum.

The driver output signal is +- 1.5 V minimum, differential mode, into a 54 ohm load.

Loss of power on one or more drivers or receivers does not cause device damage.

The RCV bus has many interface tri-state drivers connected to it. To eliminate occasional signal transitions resulting from tri-state current interactions of the driver chips, the RCV bus lines are biased at the input to the Controller. On the RCV+ line, a 1 kohm resistor is connected to the Controller +5 Volts line. The RCV- line is connected to the Controller logic common through a 1 kohm resistor and a 100 ohm line terminating resistor is connected across the two lines.

The Controller interface is a modified Motorola MVME705A, six-channel serial driver/receiver board. Motorola document MVME705A/GD1 describes this interface. Drawing C55001A015 describes the modifications to adapt the board to the RS-485 signal domain. This entails replacement of the RS-232 drivers and receivers with 75174 and 75175 chips. The termination resistors mentioned above are also installed on this board.

# 2.2 8032 MICROCONTROLLER AND SUPPORT CHIPS DESCRIPTION

This section describes the characteristics of the 8032 microcontroller, 8755 and 8156 support chips in the context of the Standard Interface Board application. Details which are not relevant to this function are briefly discussed or passed over. The application of these chips signals to the Standard Interface Board logic is described in the Board Logic description below.

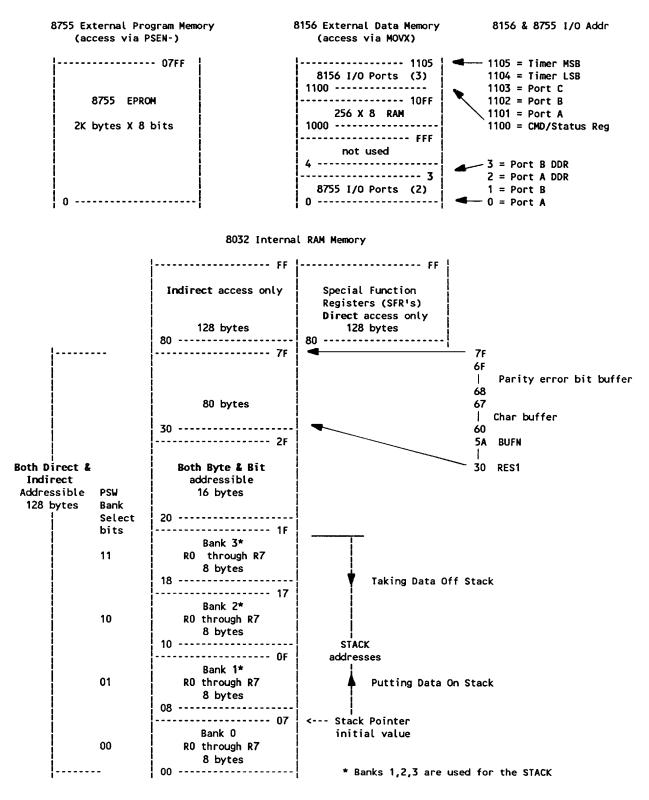

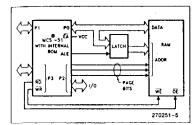

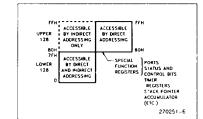

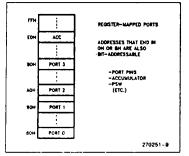

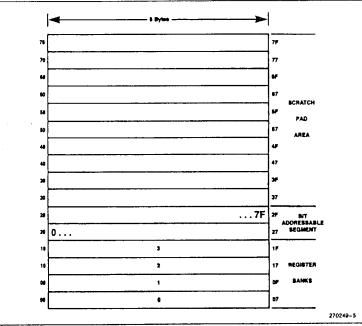

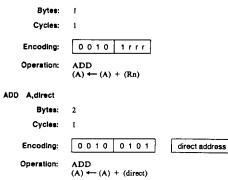

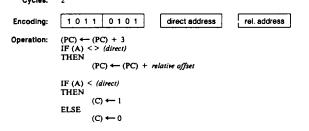

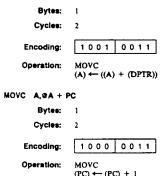

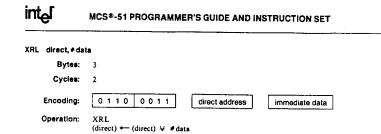

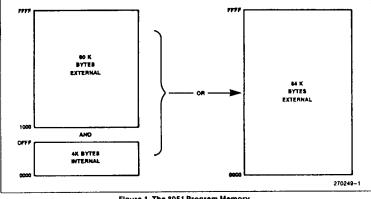

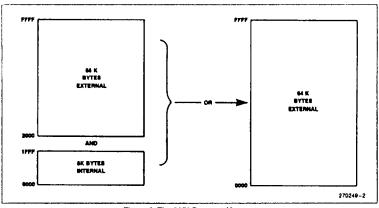

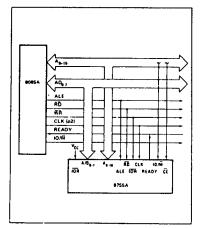

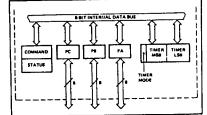

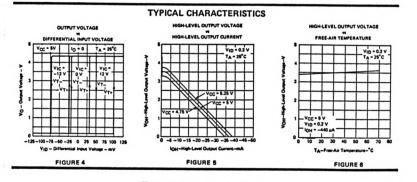

The Standard Interface Board microcontroller is an Intel 8032, which is a member of the eightbit Intel MCS-51 family. The architecture is shown in Figure 1. For a detailed description of the chip architecture refer to the MCS-51 data sheets in Section 6. The 8032 has three timer/counters (Timer 0, 1 and 2), a 256 byte on-chip RAM memory, and uses an external program memory. The 8032 support chips are: an Intel 8755 2-Kilobyte EPROM-I/O Port chip for firmware program storage and I/O, an Intel 8156 256 byte RAM-I/O-Timer, and three 74LS245 bidirectional bus drivers. The 8755 chip has two eightbit I/O ports with bits that can be individually assigned to input or outputs and has internal address latches for the multiplexed address-data bus. The 8156 provides 256 bytes of RAM, a timer, three I/O ports (two 8-bit and one 6-bit) with handshaking capabilities, and internal address latches for the multiplexed address-data bus. The 74LS245 bus drivers provides robust tri-state buffering of the sixteenbit RAM I/O ports to the (potentially heavily loaded) CMD/MON lines in the device logic. A third 74LS245 buffers the eight RA lines to the board and device logic.

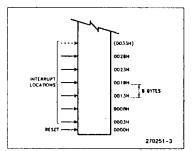

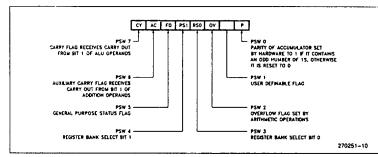

The MCS-51 series of microcontrollers is designed for control applications and has programmable internal timer/counters and a programmable, buffered full-duplex serial port. In a typical application, one of the timers may be used for a baud rate generator for the serial port and the others as event counters or watch-dog timers. Because the timers and serial port are programmable, they can be used in many different modes. Other valuable features are the use of separate program and data memories, a six-source interrupt structure with two priority levels, 32 I/O lines, a Boolean processor and an Accumulator parity bit in the Program Status Word (convenient for serial transmissions). On-chip data memory contains both byte and bit storage capabilities. Data memory and I/O ports are bit addressable which makes it easy to manipulate discretes without having to do byte read/write and masking operations. I/O Port pins may be assigned to alternate functions such as interrupt inputs rather than standard I/O bit functions. Program and data memory are in separate address spaces and may be as large as 64 Kilobytes.

The 8032 description in this manual has the following restrictions. First, this is not an 8032, 8755 or 8156 data book and it does not contain a full description of all these chip's features and modes. The description is restricted to those features which are relevant to the Standard Interface Board application. A complete set of 8032, 8755 and 8156 data sheets is included in Section 6. Second, the 8032 instruction set and assembly language programming techniques are not discussed but the program is fully described. The details of programming the 8755 EPROM are not discussed.

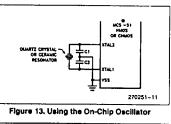

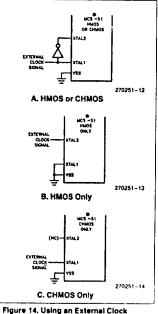

The 8032 clock is an on-chip oscillator which uses an external 11.0592 Mhz crystal. A programmed subdivision of this clock rate by Timer 1 is used as the serial port transmit and receive clocks.

Figure 3, 8032 Block Diagram, is shown on the next page.

### Special Function Registers (SFR's)

On-chip Special Function Registers (SFR's) control the operating modes of the timer/counters, serial port, and interrupts. Arguments and values for these functions are stored as data in the SFR's. Some SFR's are both bit and byte addressable (e.g. IP, IE, T2CON and SCON).

Timer/counters 0 and 1 have separate mode and control registers while Timer/counter 2 has a combined mode/controlregister. Thus TMOD establishes the modes of timers 0 and 1 and TCON turns the timers on and off. T2CON controls the modes and operation of T2. SCON controls both the mode and operation of the serial port. The SMOD bit in PCON causes the serial port baud rate to be doubled. Control bits in T2CON select Timer/counter 1 or 2 as the clock for the serial port. The IE register enables the interrupts (some of which are the result of timer overflow). The IP register establishes the priority of the six interrupt sources.

Figure 3, 8032 Block Diagram

The functions performed by these SFR mode and control registers will be described in more detail below. They are mentioned here to introduce their function.

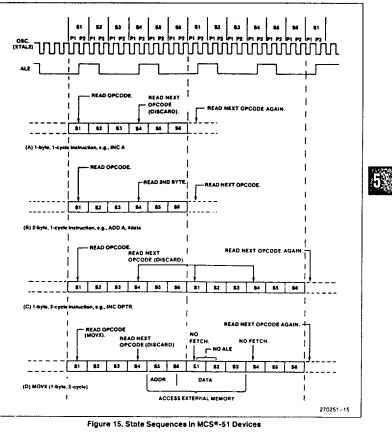

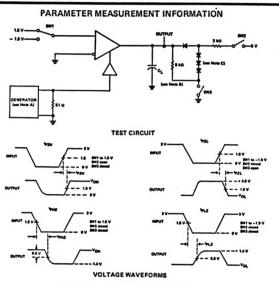

# **CPU** Timing

An 8032 machine cycle consists of 6 states (12 oscillator periods). Each state is divided into a Phase 1 half during which the Phase 1 clock is active and a Phase 2 half, during which the Phase 2 clock is active. Thus a machine cycle consists of 12 oscillator periods, numbered S1P1 (State 1, Phase 1) through S6P2 (State 6, Phase 2). Each phase lasts for two oscillator periods. Typically, arithmetic and logical operations take place during Phase 1 and internal register-to-register transfers take place during Phase 2.

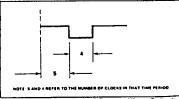

The timing diagrams of Figure 4 (next page) show the instruction fetch/execute timing referenced to the internal states and phases. Since these internal clock signals are not user accessible, the XTAL2 oscillator signal and the ALE (Address Latch Enable) are shown for external reference. ALE is normally activated twice during each machine cycle: once during S1P2 and S2P1 and again during S4P2 and S5P1. The trailing (falling edge) of ALE is used to latch the address for data read during the next cycle.

At the board clock frequency of 11.0592 Mhz, the ALE period is 542 nanoseconds; this is half of a machine cycle.

Execution of a one-cycle instruction begins at S1P2, when the opcode latched is into the Instruction Register. If it is a twobyte instruction, the second byte is read during S4 of the same machine cycle. If it is a one-byte instruction, there is still a fetch at S4, but the byte read (which would be the next opcode) is ignored and the Program Counter is not incremented. In any case, execution is complete at the end of S6P2. Figures 4-A and 4-B (this page) show the timing for a 1byte, 1-cycle instruction and for a 2byte, 1-cycle instruction.

An important aspect of the Figure 4 timing diagram which is not emphasized in the Intel data books is that ALE is used for the fetch for the next cycle. The ALE that occurs at S1P2-S2P1 latches the address for data which is read at S4P2 and the ALE at S4P2-S5P1 latches the address for data read at S1P2 of the next cycle. This

Figure 4, 8032 Fetch-Execute Timing

timing relationship is shown by the dashed lines on Figure 4.

Most 8032 instructions execute in one machine cycle. MUL (multiply) and DIV (divide) are the only instructions that take more than two machine cycles to complete; they take four cycles.

Normally, two code bytes are fetched from Program Memory during every machine cycle. The only exception to this is when a MOVX instruction is executed. MOVX is a 1-byte 2 cycle instruction that accesses external Data Memory. During a MOVX, two fetches are skipped while the external Data Memory is being addressed and strobed. Figures 4-C and 4-D show the timing for normal 1-byte, 2 cycle instruction and for a MOVX instruction.

# I/O Ports

All four 8032 I/O ports (shown on the next page) are bidirectional. Each consists of a latch (SFR's P0 through P3), an output driver, and an input buffer. These ports are shown in Figure 5. In the Standard Interface Board application (with the exception of P3.3 and P3.4), only a few (P1.6, P1.7, P3.3 and P3.4) of the 8032 I/O pins are accessible. Since these inputs are not used in the Standard Interface Board application, the properties of these ports are not described in detail. For specifics on the port structures, refer to Sections 6.4.1, 6.4.2, 6.4.3 and 6.4.4 in the 8032 data sheets in Section 6. P3.3 and P3.4 are accessible on connector P2 but are not used in the VLBA Standard Interface Board application.

desiring to use these inputs are referred to the 8032 data sheet sections mentioned above.

Note that the Ports 1 and Port 3 alternate functions are set when the associated port latch bit is set.

The output drivers of Ports 0 and 2 and the input buffers of Port 0 are used in accesses to external memory. In this application, Port 0 outputs the low byte of the external memory address. time-multiplexed with the byte being written or read. Port 2 outputs the high byte of the external memory address when the address is 16 bits wide. Otherwise the Port 2 pins continue to emit the P2 SFR content.

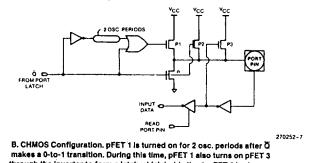

Figure 5, 8032 Port Bit Latches and I/O Buffers

The last three instructions in this list read the port byte, all 8 bits, modify the addressed bit, then write the new byte back to the latch.

All of the Port 3 pins and two Port 1 pins (P1.0 and P1.1) are multifunctional. They are not only port pins, but also serve the functions of various special features listed below. The alternate functions are selected when the associated port latch bits are set. Power reset sets all the alternate function latch bits.

- P1.0 T2 (Timer/Counter 2 external imput. This function is not used in the Standard Interface Board.)

- P1.1 T2EX (Timer/Counter 2 capture/reload trigger. This function is not used in the Standard Interface board).

- P3.0 RXD (Serial Input port)

- P3.1 TXD (Serial Output port)

- P3.2 INTO- (External Interrupt, low-true. This pin is wired to P2 and is available for external interrupt use with firmware changes.)

- P3.3 INT1- (External Interrupt, low-true. This pin is wired to P2 and is available for external interrupt use with firmware changes.)

- P3.4 TO (Timer/Counter 0 external input. This input is available on the Standard Interface Board P2 connector but TO is not used in the standard firmware. With appropriate care taken for firmware timing, TO could be used in special applications.)

- P3.5 T1 (Timer/Counter 1 external input. T1 is dedicated for baud rate generation so this input is not used in the standard application. Other applications could use this input if the baud rate generation function is shifted to another timer/counter.)

- P3.6 WR- (external Data Memory write strobe, low-true. Used to strobe the 8755 and 8156 WRinputs when writing to the 8755 I/O ports and data direction registers, and the 8156 RAM and I/O ports and port command registers.)

- P3.7 RD- (external Data Memory read strobe, low-true. Used to strobe the 8755 and 8156 RDinputs when reading from the 8755 I/O ports and the 8156 RAM, I/O ports and port status register.)

In the Standard Interface Board application most of the Port 1 bits are used for control discretes for board functions such as enabling the RCV bus tri-state line driver. Port bits P1.6 and P1.7 are available for interfacing external equipment. This use requires alteration of the control firmware in the EPROM. Some instructions that read a port read the latch and others read the pin. Which ones do which? The instructions that read the latch rather than the pin are the ones that read a value, possibly change it, and then rewrite it to the latch. These are called "read-modify-write" instructions. The instructions listed below are read-modify-write instructions. When the destination operand is a port, or a port bit, these instructions read the latch rather than the pin:

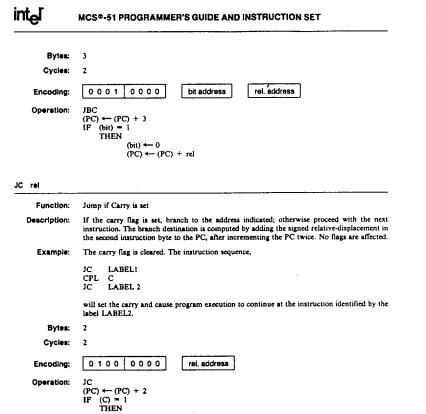

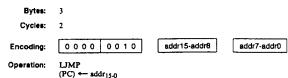

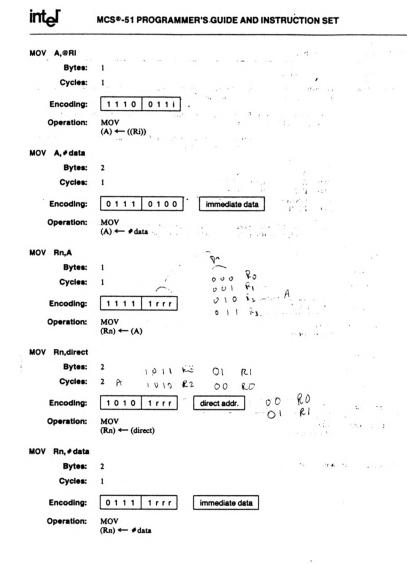

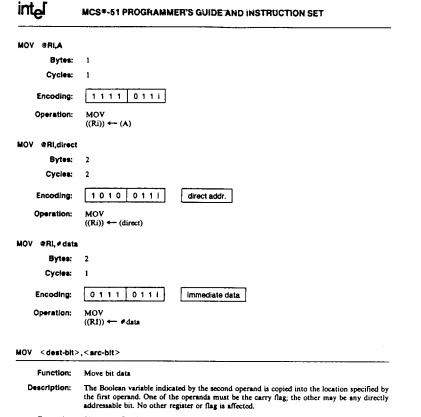

| ANL        | (Logical AND, e.g., ANL P1,A)                          |

|------------|--------------------------------------------------------|

| ORL        | (Logical OR, e.g., ORL P2,A)                           |

| XRL        | (Logical EX-OR, e.g., XRL P3,A)                        |

| JBC        | (Jump if bit=1 and clear bit, e.g., JBC P1.1, LABEL)   |

| CPL        | (Complement bit, e.g., CPL P3.0)                       |

| INC        | (Increment, e.g., INC P2)                              |

| DEC        | (Decrement, e.g., DEC P2)                              |

| DJNZ       | (Decrement and jump if not zero, e.g., DJNZ P3, LABEL) |

| MOV PX.Y,C | (Move carry bit to bit Y of Port X)                    |

| CLR PX.Y   | (Clear bit Y of Port X)                                |

| Set PX.Y   | (Set bit Y of Port X)                                  |

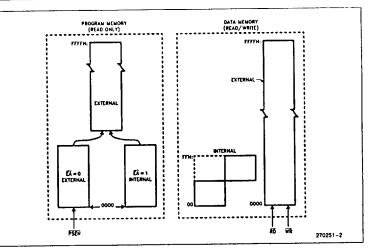

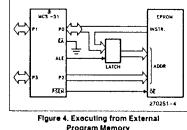

# Accessing External Memory

Accesses to external memory (i.e., memory external to the 8032) are of two types: accesses to external Program Memory and accesses to external Data Memory. Accesses to external Program Memory use signal PSEN- (Program Store Enable) as the read strobe. Figures 6A and 6B (below) shows External

Program and Data Memory read Timing. Note that program data from the EPROM is read on the rise (leading edge) of **PSEN-.** This signal is connected to the 8755 RD- pin to read the firmware program stored in the EPROM memory. Accesses to external Data Memory use RD- or WR- to strobe the memory. These signals are connected to the 8156 RD- and WRpins to read and write to the RAM memory, I/O ports, and I/0 ports command and status registers.

Like many other Intel microprocessors and microprocontrollers, the 8032 uses a multiplexed address

Figure 6, External Memory Fetch-Execute Timing

and data bus to the EPROM and RAM. Ports 0 and 2 are dedicated to this function.

Fetches from external Program Memory always use a 16-bit address. Accesses to external Data Memory can use either a 16-bit address (MOVX @DPTR) or an 8-bit address (MOVX @Ri).

Whenever a 16-bit address is used, the high byte of the address comes out on Port 2, where it is held for the duration of the read or write cycle. During this time the Port 2 latch (the Special Function Register) does not have to contain 1's and the contents of Port 2 SFR are not modified. If the external memory cycle is not immediately followed by another external memory cycle, the undisturbed contents of the Port 2 SFR will reappear in the next cycle.

If an 8-bit address is being used (MOVX @Ri), the contents of the Port 2 SFR remain at the Port 2 pins throughout the external memory cycle.

In any case, the low byte of the address is time-multiplexed with the data byte on Port 0. The ADDR/DATA signal drives both FET's in the Port 0 output buffers. (See Figure 6 above and Section 6.4 in the 8032 data sheets for additional details.) Signal ALE should be used to capture the address byte into an external latch. The address byte is valid at the negative transition of ALE. Then in a write cycle, the data byte to be written appears on Port 0 just before WRbar is activated and remains there until after WRbar is deactivated. Note that on the Standard Interface Board schematic diagram (drawing D55002S004), ALE is connected to the ALE inputs of the 8755 and 8156 to store the lower address byte in the chip latches.

### PSEN (Program Store Enable)

The fetch/execute sequences are the same whether the Program Memory is internal or external to the chip. Execution times do not depend upon whether the Program Memory is internal or external.

The read strobe for external Program Memory fetches is PSEN-. The 8032 reads program data on the rise (leading edge) of PSEN-. When the CPU is accessing external program memory, PSEN- is activated twice every machine cycle (except during a MOVX instruction) whether or not the byte fetched is actually needed for the current instruction. A complete PSEN- cycle, including activation and deactivation of ALE and PSEN-, takes 6 oscillator periods. This timing is illustrated in Figure 6A in which there is not an access to external data memory. When PSEN- is activated, its timing is not the same as RD-.

If an access to external Data Memory occurs, as shown in Figure 6B, two PSEN-'s are skipped, because the address-data bus is being used for Data Memory access.

Note that an external Data Memory bus cycle takes twice as much time as a Program Memory bus cycle. This is probably done to provide a greater read time for external data memory since the 8032 does not have a wait pin. Figure 6B shows the relative timing of the addresses being emitted at Ports 0 and 2, and of ALE and PSEN. ALE is used to latch the low address byte from P0 into the address latch.

The execution sequence for these two types of read cycles are shown in Figure 4 for comparison. The dashed lines in Figure 6B shows the ALE for External Program and External Data memory. In the Standard Interface application, interface board I/O lines are driven by the 8156 and 8755 I/O ports which are in the External Data memory address space. The timing for these I/O ports is thus identical to External Data memory timing. See the memory map in Section 3.2 for details on the address assignments.

# ALE (Address Latch Enable)

The main function of ALE is to provide a properly timed signal to latch the low byte of an address from P0 to an external address latch during fetches from external Program Memory. For that purpose ALE is activated twice every machine cycle. The falling (i.e. trailing) edge of ALE is used as the latch strobe. This activation takes place even when the cycle involves no external fetch. Contrary to statements in earlier MCS-51 data books, ALE is used with external Data Memory cycles; any external memory read or write operation must have an address and ALE is the signal to latch the lower byte of the memory address. Figure 6B shows the timing for a MOVX instruction. ALE for reading the external Data Memory is shown by the dashed line. Cycle 2 of this instruction has only one ALE which is for the instruction fetch for the cycle following cycle 2. The first ALE of the second cycle of a MOVX instruction is missing (see Figure 6). Consequently, in any system that does not use external Data Memory, ALE is activated at a constant rate of 1/6 the oscillator frequency and can be used for external clocking or timing purposes.

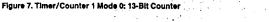

# Timer/Counters

The 8032 has three 16-bit timer/counter registers. All three can be configured to operate as timers or event counters.

In the "timer" function, the register is incremented every machine cycle. Thus one can think of it as counting machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the "counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0, T1 or T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register in the S3P1 of the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (24 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal but to insure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

In addition to the "timer" or "counter" selection, Timer 0 and Timer 1 have four operating modes from which to select. Timer 2 is has three modes of operation: "capture," "auto reload" and baud rate generator.

# Timer/Counters 0 and 1

In the Standard Interface application, T0 is not used and T1 is used in mode 2 to generate the serial port baud rates. The description of modes 0, 1 and 3 is very brief to high-light the main features

of these modes. Interface board users who intend to use the timers in these other modes are referred to the 8032 data sheets in Section 6 for a more complete description of the timer/counter modes.

Register TMOD specifies Timer/Counters 0 and 1 modes. Register TCON controls the operation (i.e. turns them on and off) of these two timer/counters.

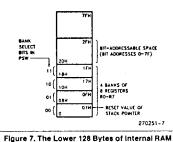

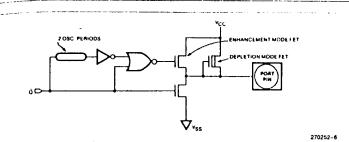

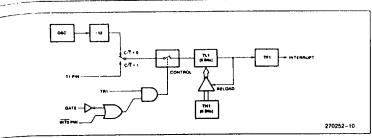

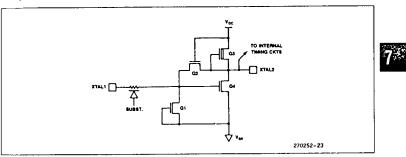

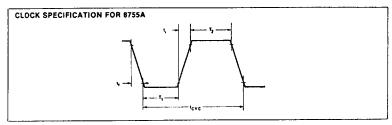

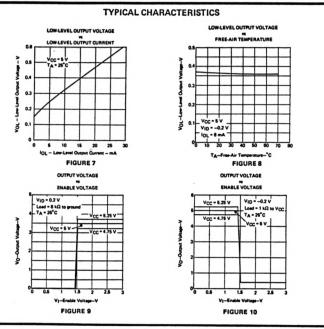

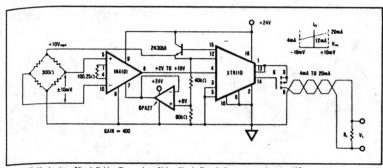

Figure 7, Timer 1, Mode 2

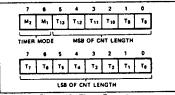

The TMOD register bit assignments are depicted below:

TMOD: Timer/Counters 0 and 1 Mode Register

| Timer/Counter 0 |      |    |    | Timer/Counter 1 |      |    |       |                                |

|-----------------|------|----|----|-----------------|------|----|-------|--------------------------------|

| (MSB)           | o (7 |    |    | 04 <b>7</b> 5   | 6/7  |    | (LSB) |                                |

| GATE            | C/T- | M1 | MO | GATE            | L/1- | M1 | HO    |                                |

| 0               | 0    | 1  | 0  | 0               | 0    | 0  | 0     | < Value set by INITIAL routine |

GATE Gating control. When set, Timer/Counter "X" is enabled only while INTX pin (Port pins 3.2 or 3.3) is high and TRX bit is set in TCON.

C/T- Timer or Counter selector, cleared for Timer operation (timer input from internal system clock). Set for Counter operation (counter input from TX input pin).

Figure 7 (previous page) shows the Timer 1 configuration.

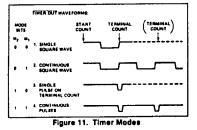

T0 and T1 have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both counter/timers. Note that Mode 3 is different in that Timer/Counter 0 operates as two independent 8-bit counters. The four operating modes are shown below:

| м1 | MO | Operati | ng Mode                                                                                                                                                                                                                    |

|----|----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0       | Timer TLX serves as a five-bit prescaler                                                                                                                                                                                   |

| 0  | 1  | 1       | 16 bit Timer/Counter. THX and TLX are cascaded; there is no prescaler.                                                                                                                                                     |

| 1  | 0  | 2       | 8-bit auto-reload timer-counter. THX holds a value which is to be reloaded into TLX<br>each time it overflows. Timer 1 operating in mode 2 generates the serial port<br>transmit and receive clocks. (VLBA operating mode) |

| 1  | 1  | 3       | (Timer 0) TLO is an eight-bit timer/counter controlled by the standard Timer O control bits. THO is an eight-bit timer (only) controlled by Timer 1 control bits.                                                          |

| 1  | 1  | 3       | (Timer 1) Timer/counter 1 is stopped.                                                                                                                                                                                      |

Mode 0 In mode 0, T0 and T1 are an 8-bit counter with a divide-by-32 prescaler. In this mode the timer register is configured as a 13-bit register. As the count rolls over from all 1's to all 0's, it sets the Timer Interrupt Flag, TF1 in TCON. For additional details on this mode see the Timer/Counters section of the 8032 data sheets.

Mode 1 Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

Mode 2 Mode 2 for Timer 1 is used to generate the 57.6 kilo-baud serial port shift clocks in the Standard Interface application. Mode 2 configures the timer register as an 8-bit counter (TL1) with automaticreload as shown in Figure 7. Overflow from TL1 not only sets TF1 but also reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged. Mode 2 is the same for Timer/Counter 0. Figure 7 shows the configuration of Timer/Counter 1 in Mode 2. The application of Timer 1 for baud rate generation is found below in the description of the serial port. Figure 7 (previous page) shows the Timer 1, Mode 2 configuration.

Mode 3 Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0 in TCON. Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. For additional details on this mode see the Timer/Counter section of the 8032 data sheets.

Timer/Counters 0 and 1 are controlled by the TCON register. The TMOD register determines the timer/counter modes. The TCON register bit assignments are shown on the next page.

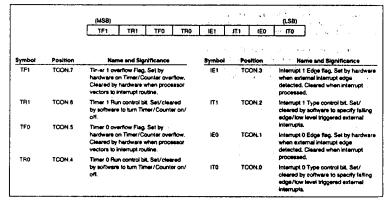

TCON: Timer/Counter 0 and 1 Control Register

|            | (MSB)<br>TF1 | TR1     | TFO | TRO                                                                   | IE1                                                                                                                                | IT1                                                                                                           | IEO                                                 | (LSB)<br>Ito                                  |  |  |  |  |

|------------|--------------|---------|-----|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|--|--|--|--|

| Symbol     |              | Positio | 'n  | Name an                                                               | d Signif                                                                                                                           | icance                                                                                                        |                                                     |                                               |  |  |  |  |

|            |              |         |     |                                                                       | Timer 1 overflow Flag. Set by hardware on timer/counter overflow. Cleared by hardware when processor vectors to interrupt routine. |                                                                                                               |                                                     |                                               |  |  |  |  |

| TR1        |              | TCON.6  |     | Timer 1                                                               | Run cont                                                                                                                           | rol bit.                                                                                                      | Set/clea                                            | red by software to turn timer/counter on/off. |  |  |  |  |

| TFO TCON.5 |              |         |     | Timer O overflow Flag. Set/cleared in the same manner as TF1 above.   |                                                                                                                                    |                                                                                                               |                                                     |                                               |  |  |  |  |

| TRO TCON.4 |              |         |     | Timer O Run control bit. Set/cleared in the same manner as TR1 above. |                                                                                                                                    |                                                                                                               |                                                     |                                               |  |  |  |  |

| IE1        |              | TCON.3  |     |                                                                       | apt 1 Edge<br>i when in                                                                                                            | -                                                                                                             | rdware when external interrupt edge detected.<br>I. |                                               |  |  |  |  |

| 111        |              |         |     |                                                                       |                                                                                                                                    | upt 1 Type control bit. Set/cleared by software to specify falling<br>ow level triggered external interrupts. |                                                     |                                               |  |  |  |  |

| IEO        |              | TCON.1  |     | Interru                                                               | upt 0 Edg                                                                                                                          | e flag.                                                                                                       | Set and c                                           | leared in the same manner as IE1 above.       |  |  |  |  |

| 110        |              | TCON.0  |     | Interru<br>above.                                                     | apt 0 Тур                                                                                                                          | pe contro                                                                                                     | ol bit.                                             | Set and cleared in the same manner as IT1     |  |  |  |  |

Bold lettering in the TCOM table indicates active bits in the Standard Interface Board application.

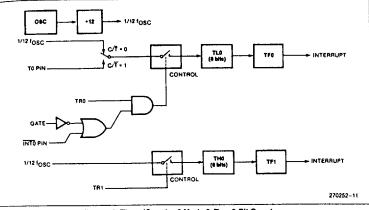

# Timer 2 (Watch-Dog Timer)

Timer/Counter 2 is implemented in only the 8032 and 8052 versions of the MCS-51 family. Timer/counter 2 is controlled by SFR register T2CON. In the Standard Interface Board application, Timer 2 is used as a watch-dog timer and operates in the "auto-reload" mode.

Timer 2 is a 16-bit timer/counter. Like Timers 0 and 1 it can operate either as timer or as an event counter. The function is selected by bit C/T- in the Special Function Register T2CON. Timer 2 has three operating modes: "capture", "auto-reload" and "baud rate generator," which are selected by bits in TCON as shown below.

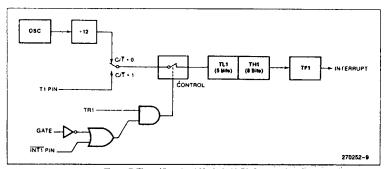

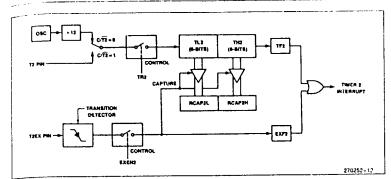

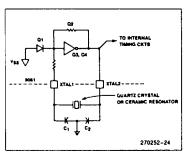

The configuration of Timer/Counter 2 in the Auto-Reload Mode is shown in Figure 8, below:

In the capture mode there are two options selected by bit EXEN2 in TCON. If EXEN2 = 0, then

timer 2 is a 16 bit timer or counter which upon overflowing sets bit TF2 (the Timer 2 overflow bit) which can be used to generate an If EXEN2 = 1, then interrupt. Timer 2 generates an interrupt and in addition, a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2 to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes bit T2EX in TCON to be set, and EXF2, like TF2, can generate an interrupt.

Figure 8, Timer 2, Auto-Reload Mode

The capture mode configuration of Timer 2 is shown in Section 6 of the 8032 data sheets in Section 6.

In the auto-reload mode there are also two options, which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, when Timer 2 rolls over it not only sets TF2, but also causes the Timer 2 registers to be reloaded with the 16-bit values in RCAP2L and RCAP2H, which are preset by software. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX will also trigger the 16-bit reload and set EXF2. The auto-reload configuration of Timer 2 is described in more detail in Section 6.6 of the 8032 data sheets.

Referring to the TCON; Timer/Counter 2 Control Register figure below, the baud rate generator mode for Timer 2 is selected by RCLK = 1 and TCLK = 1 in T2CON. Note that the baud rates for transmit and receive can be simultaneously different. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode.

The Timer 2 baud rate generator mode is similar to the auto-reload mode in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit values in RCAP2H and RCAP2L, which are preset by software. For a full description of the operation of Timer 2 see Section 6.7.3 in the 8032 data sheets in Section 6.

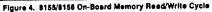

T2CON: Timer/Counter 2 Control Register

| (MSB)<br>TF2 | EXF2                                                                                                                                                                                                                                                    | RCL                                                                                                                               | K TCLK       | EXEN2               | TR2                          | C/T2bar    | (LSB)<br>CP/RL2bar         |                                 |                                 |             |                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------------------|------------|----------------------------|---------------------------------|---------------------------------|-------------|------------------------------------------------|

| 0            | 0                                                                                                                                                                                                                                                       | 0                                                                                                                                 | 0            | 0                   | 1                            | 0          | 0                          | ۰۰۰-                            | Value set                       | by INITIAL  | . routine                                      |

| Symbol       | Posit                                                                                                                                                                                                                                                   | tion                                                                                                                              | Name and Sig | nifican             | e                            |            |                            |                                 |                                 |             |                                                |

| TF2          | τ2α                                                                                                                                                                                                                                                     | 2CON.7 Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by sof<br>not be set when either RCLK = 1 or TCLK = 1. |              |                     |                              |            |                            |                                 |                                 |             | are. TF2 will                                  |