# VLBA Technical Report No. 45 THE VLBA CORRELATOR MAC and LTA SUB-SYSTEMS VOLUME 1 of 2

**Chuck Broadwell**

**Ray Escoffier**

January 1, 1999

macltaman.vol1.doc

Microsoft Word

not under SCCS control

master file stored in /corrdwgs/manuals/macltaman/SCCS

(where the SCCS file would have been stored)

This page intentionally left blank.

# TABLE OF CONTENTS

# VOLUME 1

| TABL           | E OF CONTENTS                              | 3  |

|----------------|--------------------------------------------|----|

| TABL           | E OF FIGURES                               | 6  |

| 1 Tł           | HE VLBA CORRELATOR MAC AND LTA SUB-SYSTEMS | 7  |

| 1.1            | Introduction                               | 7  |

| 1.2            | VLBA Correlator Drawings                   | 8  |

| 1.3            | Test Fixtures                              |    |

| 2 Tł           | HE MASTER CONTROL CARD (MCC)               | 11 |

| 2.1            | Introduction                               | 11 |

| 2.2            | Circuit Description                        | 11 |

| 2.2.1          | The FFT Cycle Sequencer                    | 12 |

| 2.2.2          |                                            |    |

| 2.2.3          |                                            |    |

| 2.2.4          |                                            |    |

| 2.2.5          | · ····································     |    |

| 2.2.6          |                                            |    |

| 2.2.7          |                                            |    |

| 2.2.8<br>2.2.9 |                                            |    |

| 2.3            | MCC software                               |    |

| 2.3.1          | Descriptions of the MCC Software           |    |

| 2.3.2          | Microprocessor Interrupt Structure         | 20 |

| 2.4            | MCC Utility Displays                       | 21 |

| 2.5            | The MCC PLOT Program                       | 25 |

| 3 TH           | HE MULTIPLY AND ACCUMULATE CARD (MAC)      | 27 |

| 3.1            | Introduction                               |    |

| 3.1.1          | The MAC VLBA1 Control Word Daisy Chain     |    |

| 3.2            | MAC Card Description                       |    |

| 3.2.1          | MAC Card I/O Pin Definitions               |    |

| 3.2.2          | FFT to MAC Interface                       |    |

| 3.3            | Ram Addressing                                                          | 32    |

|----------------|-------------------------------------------------------------------------|-------|

| 3.4            | Card Edge Timing and MACWE Accesses                                     | 33    |

| 3.5            | Short Term Accumulator Readout Cycle                                    | 22    |

| 3.5.1          | Readout Sequence                                                        |       |

|                | - 1                                                                     |       |

| 3.6            | Tri-State Buses on the MAC Card                                         | 36    |

| 4 TH           | E LONG TERM ACCUMULATOR CARD (LTA)                                      | . 39  |

| 4.1            | Introduction                                                            | 39    |

| 4.2            | LTA General Description                                                 | 30    |

| 4.2.1          | DRAM Addressing                                                         |       |

| 4.2.2          | Backend Access                                                          |       |

| 4.2.3          | Validities                                                              |       |

| 4.2.4          | Details of sequence of results from MAC quadrants to LTA:               |       |

| 4.2.5          | Details of 15,15,6 to IEEE conversion:                                  |       |

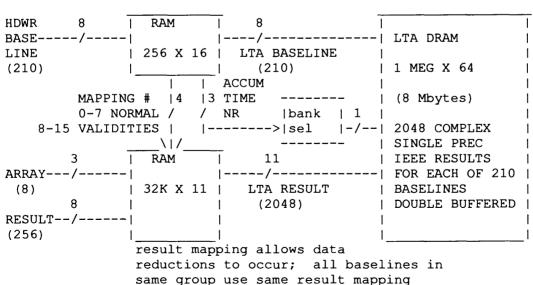

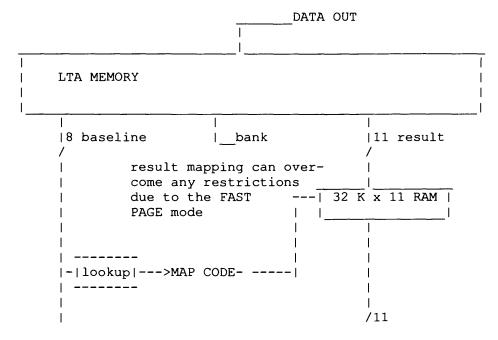

| 4.2.6          | LTA input address mapping and Fast Page Mode:                           |       |

| 4.2.7          | LTA output address mapping and rast ruge brode.                         |       |

| 4.2.8          | Detailed Description of Pulsar Validities:                              |       |

|                |                                                                         |       |

| 4.3            | LTA Circuit Description                                                 | 66    |

| 4.3.1          | Input Circuit                                                           | 66    |

| 4.3.2          | 15,15,6 To IEEE Conversion                                              | 66    |

| 4.3.3          | Sequencers                                                              | 67    |

| 4.3.4          | Front End Address Mapping                                               |       |

| 4.3.5          | Bank Selection                                                          | 68    |

| 4.3.6          | Clear Accumulator                                                       | 68    |

| 4.3.7          | Row and Column Multiplexing                                             | 69    |

| 4.3.8          | 87C51 Access                                                            | 69    |

| 4.3.9          | HCB Interface                                                           |       |

| 4.3.10         | Backend Interface                                                       | 69    |

|                |                                                                         |       |

| 4.4            | LTA Utility Displays and Tests                                          |       |

| 4.4.1          | Looking at LTA Results While Observing or Testing                       |       |

| 4.4.2          | Real Time System Tests                                                  |       |

| 4.4.3          | Terminal Tests                                                          | 72    |

| 4.5            | LTA Assembly Language Source Files                                      | 72    |

|                |                                                                         |       |

| 5 AP           | PENDIX I LIST OF FILES                                                  | . / 5 |

| 5.1            | Master Control Cord (MCC)                                               | 75    |

| 5.1.1          | Master Control Card (MCC)<br>Files maintained in corrdwgs/mcc/sch/SCCS  | 75    |

| 5.1.1<br>5.1.2 | 87C51 source files maintained in vlbsoft/mccasm/SCCS                    |       |

| 5.1.2<br>5.1.3 | PAL files maintained in vibsoft/pal_prom/pals/mcc/SCCS                  |       |

| 5.1.3<br>5.1.4 | Sequencer source files maintained in vibsoft/pal_prom/proms/mccseq/SCCS |       |

| J.1.4          | sequencer source mes manualited in viosoropai_promyproms/meeseq/SCCS    | //    |

| 5.2            | Multiply Accumulate Card (MAC)                                          | 77    |

| 5.2.1          | Files maintained in corrdwgs/mac/sch/SCCS                               |       |

| J 1            |                                                                         |       |

| 5.3            | Long Term Accumulator (LTA)                                             | 78    |

| 5.3.1 | Files maintained in corrdwgs/lta/sch/SCCS                   |    |  |  |  |  |  |

|-------|-------------------------------------------------------------|----|--|--|--|--|--|

| 5.3.2 | 87C51 source files maintained in vlbsoft/ltaasm/SCCS        |    |  |  |  |  |  |

| 5.3.3 | C source maintained in vlbsoft/ltaasm/SCCS                  |    |  |  |  |  |  |

| 5.3.4 | PAL files maintained in vlbsoft/pal_prom/pals/lta/SCCS      |    |  |  |  |  |  |

| 5.3.5 | Sequencer files maintained in vlbsoft/pal prom/proms/ltaseq |    |  |  |  |  |  |

| 5.3.6 | Xilinx files maintained in vlbsoft/xilinx/lta               |    |  |  |  |  |  |

| 6 APP | PENDIX II HCB PROTOCOL FOR MCC                              | 81 |  |  |  |  |  |

•

| 7 | APPENDIX III | HCB PROTOCOL FOR LTA8 | <b>;7</b> |

|---|--------------|-----------------------|-----------|

|---|--------------|-----------------------|-----------|

# TABLE OF FIGURES

# VOLUME 1

| FIGURE 1  | VLBA CORRELATOR RACK LAYOUT            | .7  |

|-----------|----------------------------------------|-----|

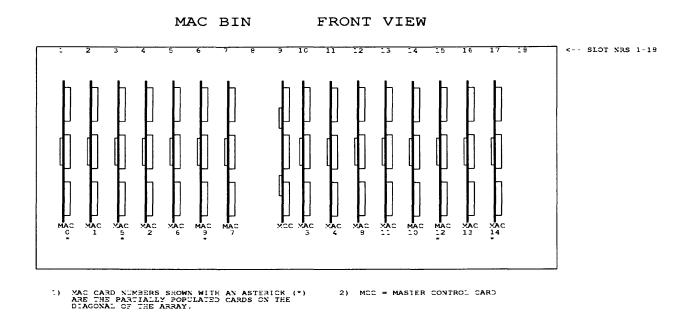

| FIGURE 2  | MAC BIN CARD LAYOUT                    | . 8 |

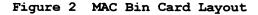

| FIGURE 3  | MASTER CONTROL CARD BLOCK DIAGRAM      | 26  |

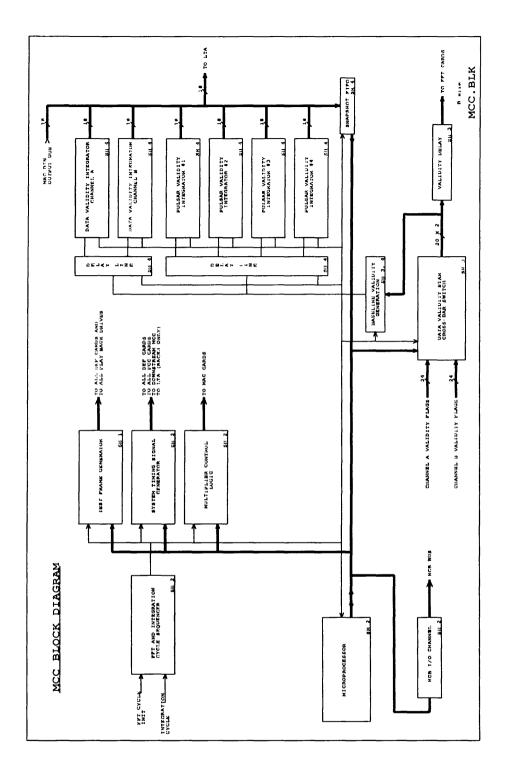

| FIGURE 4  | HARDWARE BASELINES                     | 34  |

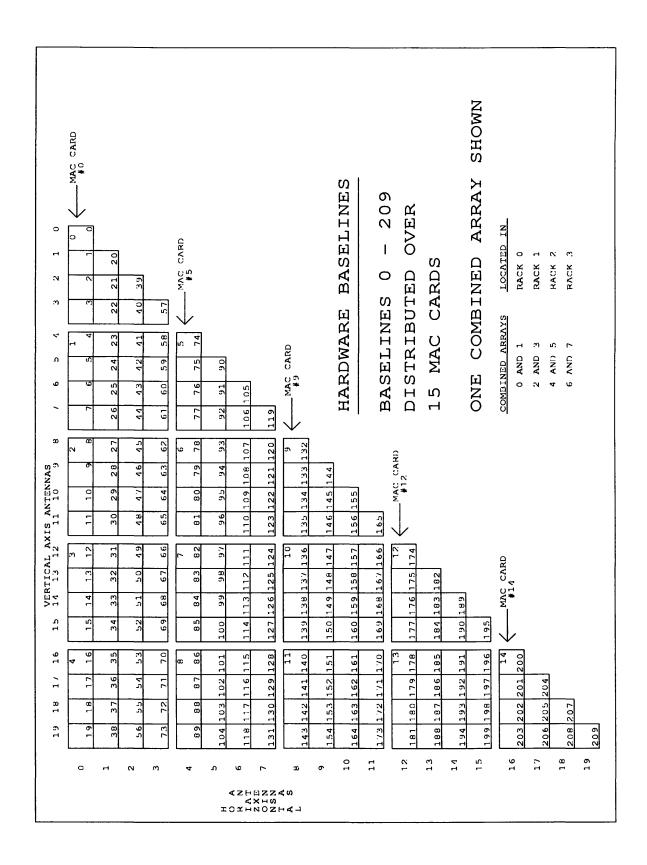

| FIGURE 5  | MAP OF CARDS VERSUS BASELINES          | 35  |

| FIGURE 6  | MAP OF COLUMN NUMBERS VERSUS BASELINES | 35  |

| FIGURE 7  | MAP OF ROW NUMBERS VERSUS BASELINES    | 36  |

|           | LTA DRAM ADDRESS FIELDS                |     |

| FIGURE 9  | LTA INPUT MAPPING                      | 42  |

| FIGURE 10 | ) LTA BACKEND ACCESS                   | 44  |

| FIGURE 1  | I LTA BACKEND ADDRESSING               | 45  |

|           |                                        |     |

# 1 The VLBA Correlator MAC and LTA Sub-Systems

## 1.1 Introduction

The MAC and LTA sub-systems consist of the following card types:

- 1) Master Control Card (MCC)

- 2) Multiply and Accumulate Card (MAC)

- 3) Long Term Accumulator Card (LTA)

The MCC provides master control signals to the complete correlator system, as well as controlling the MAC cards.

The MAC cards come after the FFT cards in the data flow path of the VLBA Correlator System (see VLBA Technical Report Number 44). The spectral results produced by the FFT process, for each antenna, are cross multiplied with results from all other antennas and the results are accumulated on a short term basis in the MAC cards. The short term accumulation cycle is 131 msec.

Results from the MAC cards are transferred to the Long Term Accumulator (LTA) every 131 msec and usually accumulated for longer intervals. The LTA accumulates for integer multiples of the 131 msec interval. Results from the LTA are transferred to the Digital Filter (FIR), covered in VLBA Technical Report Number 46.

The MCC and MAC cards are located in the top card bin in each of the correlator racks. There is one MCC card per rack, and 15 MAC cards per rack. The LTA card is located in the FFT bin of rack 3 only. See Figure 1 for the location of these bins. There is only one LTA card in the system.

| [ | CO                                    | C1                                    | C2                       | C3                                     |     |

|---|---------------------------------------|---------------------------------------|--------------------------|----------------------------------------|-----|

| E | • • • • • • • • • • • • • • • • • • • |                                       | • •                      | SYSTEM MONITOR                         |     |

| D | MAC                                   | MAC                                   | MAC                      | MAC                                    |     |

|   | ARRAYS 3-1                            | ARRAYS 2-3                            | ARRAYS 4-5               | ARRAYS 6-7                             |     |

| с | FFT                                   | FFT                                   | FFT<br>DELAY CENTERS 2-3 | FFT<br>LTA<br>FIR<br>DELAY CENTERS 2-3 | VME |

|   | STN 2-9 CH 2-3                        | STN 10-19 CH 0-3                      | STN C-9 CH 4-7           | STN 10-19 CH 4-7                       |     |

| в | PBI                                   | PBI                                   | PBI                      | PBI                                    | нсв |

|   | PBD 1-6                               | PBD 7-12                              | PBD 13-19                | 28£ 19-24                              |     |

| A |                                       | • • • • • • • • • • • • • • • • • • • |                          | • •<br>• •<br>• •                      |     |

Figure 1 VLBA Correlator Rack Layout

Figure 2 shows the card layout in a MAC bin.

## **1.2 VLBA Correlator Drawings**

All hardware and firmware related files for the VLBA correlator are maintained under SCCS version control, in one of two areas. These two areas are identified as the vlbsoft and corrdwgs areas. The path to vlbsoft is /home/magnolia2/vlbsoft and the path to corrdwgs is /home/azalea/corrdwgs (as of May 1998). All drawing filenames are lower case, but may appear in documentation as either upper or lower case.

The vlbsoft area is where all source code for the correlator is maintained. It is also used to store all source files that are processed in any manner to produce objects that are downloaded into the correlator, or programmed into devices that are installed in the correlator.

The corrdwgs area is where Orcad schematic files, netlists, partlists, etc. are maintained.

Section 5 of this Technical Report contains a complete list of all drawings for the MCC, MAC and LTA cards.

Volume 2 of this Technical Report contains many of the schematics referred to in Volume 1. Drawings for test fixtures are not included in this report.

٠.

Copies of many Postscript files for drawings are presently stored in the /home/w5uxh/plots directory.

## 1.3 Test Fixtures

To support testing of the MCC, MAC and LTA cards, there are several test fixtures available. The PBI test fixture, described in Technical Report No. 43, supports the MCC card. The FFT test fixture, described in Technical Report No. 44, supports the MAC cards. A separate test fixture, the LTA-FIR test fixture, supports the LTA and FIR (Digital Filter) cards. This test fixture has no built in test features. It consists of slots for the LTA and FIR cards and a HCB interface to the VME system.

The VLBA Correlator Testbed Rack provides additional test capability for all system cards.

This page intentionally left blank.

# 2 The Master Control Card (MCC)

### 2.1 Introduction

The main function of the master control card (MCC) is to provide timing and control signals throughout the VLBA correlator. A summary of the specific functions provided by the MCC card is given below:

- Provide FFT cycle, fringe cycle, and integration cycle sequencers that can produce timing signals required by other sections of the correlator.

- Provide control signals for the MAC cards in the crossmultiplier bin.

- Duplicate, for validity signals, the 4-into-1 data muxes that exist on the FFT cards.

- Provide tape validity integrators for 2-channels (all 20stations) and pulsar validity integrators for the pulsar gate generators of one FCC.

- 5) Provide differential drivers for the 18-bit short term integrator bin output bus into the LTA.

- 6) Provide a data tap for the short term integrator output for testing purposes.

- 7) Provide correctly timed validity gate signals to the FFT cards.

- 8) Provide an HCB (Hardware Control Bus) communication link with the real time computer system (RTS).

- 9) Load the MAC ASIC control words.

- 10) Provide a test PBD frame for system testing.

There are 4 MCC cards in the system, one in each MAC bin. The MCC card in rack 3 is a master MCC and its sequencers free-run on the 32-MHz system clock. The MCC cards in racks 0, 1, and 2 are slaved to the rack 3 card. See Figure 3 for a block diagram of the MCC.

# 2.2 Circuit Description

Refer to the MCC schematic sheets, L027D01.SCH - L027D04.SCH in Volume 2, for the following circuit descriptions.

#### 2.2.1 The FFT Cycle Sequencer

The FFT cycle sequencer of the MCC is seen on sheet 2 of the MCC schematic in the upper left hand corner. This logic provides a 516-state sequencer which is synchronized, in the slave MCC cards, to the master MCC by the MASTER FFT INIT signal from an upstream MCC. The PAL counters, 16G and 15G, count through the 516 states of the sequencer to address 516 memory locations of the four 7C245A 2K X 8 ROMs. The ROMs are programmed to provide timing control for many of the functions of the MCC.

Some of the control signals out of the sequencer ROMs are dedicated lines such as S12 (STA READ) out of pin 14 of ROM 18G. Other functions are encoded across several bits and decoded into individual timing signals by stages such as PALs 19F, 16E, or 20F. Some control terms are timing signals required on the MCC itself, like the ENA and RST signals coming out of PAL 14G, while other signals go off the card and provide the system with timing signals.

#### 2.2.2 The Fringe/Integration Sequencer

The second sequencer on sheet 2 of the MCC schematic is the fringeintegrator cycle sequencer. PALs 16F and 15F count through the 8192 FFT cycles of an integration cycle while ROMs 17F and 18F provide timing signals during the course of this 131 msec cycle. The master MCC sequencer free runs and the slave cards use the INTEG CYC ENA signal for integration cycle synchronization (see the block diagram on the left hand border of sheet 2).

#### 2.2.3 The MCC Microprocessor

The MCC microprocessor can be seen on sheet 2 of the MCC schematic. The 87C51 has a number of functions on the MCC card:

- 1) communicate via an HCB port with the RTS.

- 2) program the delay lines (14E, 17E, 18E, and 19E) that are set to insure good timing of 32-MHz signals to other bins.

- 3) provide the master/slave flag as instructed by the RTS (26J-12).

- 4) load the MAC card ASIC control words.

- 5) control the test frame generator.

The HCB support is seen in the lower right hand corner of the MCC schematic. The HCB communication is interrupt driven via the 87C51 INT1 interrupt.

#### 2.2.4 Data Valid Muxes

Each FFT card in the VLBA correlator has a 4-into-1 data mux at the input of the card to select one of four possible PBD/DEF (Playback Drive / Deformatter) data sources. This mux function is duplicated on the MCC for the corresponding PBD/DEF validity signals.

A DEF card provides validity flags with each output channel that reflects the status of the data coming out of the DEF for that channel. These validity signals are updated on an FFT cycle basis. When improper operation (for example, a PBD frame with many parity errors) is detected in the transport output signal, the DEF uses the validity output to flag the FFT engine it feeds to discard all Fourier transform results polluted by data bits from the bad frame. In addition to discarding such invalid spectra, a count must be kept of how many such bad FFT cycles were discarded (actually, valid FFT cycles are counted).

The MCC card provides 4-into-1 muxes for the DEF validity outputs so a count can be made of the valid FFT cycles performed in a given FFT engine. Program words that address the 74ALS153s, seen on sheet 3 of the MCC schematic, are assembled by the RTS to duplicate the mux program bits on the FFT cards and stored in the registers 22E, 23E, 22C, 23C, and 22B.

DEF validity signals from two channels (all 24 DEF cards) go to a given MCC card. The capture signal CAPVA clocks the input registers for the validity signals once per FFT cycle and the output of the muxes go to registers (28E, 29E, 28C, 28B, and 28A), clocked once per FFT cycle by signal CAPVB (the capture signals are decoded in PAL 23B from the FFT sequencer signals).

The PALs 30E, 29C, 29B, 29A, 30A, 30C, and 30B form two independently programmable dual 20-into-1 muxes (4 outputs, total). Program bits S16, S17, S18, S19, and S20, from the FFT cycle sequencer, select one of the 20 validity signals to drive the DATAVALID AX line (and simultaneously selects the corresponding B-channel validity signal to drive the DATAVALID BX output). Program bits S21, S22, S23, S24, and S25 select A and B y-axis validities (DATAVALID BX and DATAVALID BY). The goal of this operation is to form baseline validities by logically ANDing the validities of stations X and Y for all 210 combinations of X and Y for the 20 stations (since if either station of a baseline is invalid, the baseline cross product is invalid). The S16 thru S20 control signals and the S21 thru S25 control signals will cycle through the 210 combinations of X and Y during the course of an FFT cycle as determined by the sequencer ROMS 19G and 20G. The logical AND occurs in ICS 2C and 3C on sheet 4 of the schematic.

### 2.2.5 Validity Delay Lines

The output of the 74ALS153 4-into-1 muxes on sheet 3 of the MCC schematic also drive the ten 27LS07 RAMs at the right edge of the page. The validity signals out of the muxes of the MCC must be connected to their respective FFT engines. It is in the FFT engine that the validity signals are acted upon (when the data being transformed is invalid,

i.e. when the validity signal is at logic zero, the transform output is forced equal to zero).

The validity signal is connected to the ASIC of butterfly stage 4 in an FFT pipeline. A delay is provided on the MCC to duplicate the pipeline delay that data incurs in the FFT engine getting to stage 4 so that the data and validity signals that meet are from the same epoch. This delay is obtained in the 27LS07 RAMS (31E, 32E, 31D, and others). PAL 23B generates RAM addresses in a loop whose size reflects the delay required for the validity lines. A RAM address is selected, the validity signals previously stored in the RAM are read and new validity signals are written into the RAMs. The length of time until these RAM addresses are read again during the next address loop is the delay given to the validity signals. Each address of the address loop delays the validity signals an integral FFT cycle. Fractional FFT cycles are obtained by the phasing of the read and write signals within an FFT cycle.

The delayed validity output, from ICs 33E, 34E, 33C, 33B, and 33A, are wired into the FFT bins.

#### 2.2.6 Multiplier Control Logic

The logic seen in the lower right hand corner of the MCC schematic, sheet 3, is the multiplier control logic. This logic generates control signals for the MAC cards in the bin the MCC occupies.

ICs 13B and 12B form a baseline counter that counts through 210 baselines (plus 3 special validity "baselines") in the course of reading out MAC results. The BLA[0..7] bus is the radix 210 (or, 213 as per above to be exact) counter output and ICs 12A, 11A, 8A, and 9A decode the BLA[0..7]baseline address into a MAC card select (CRDSEL\x) and row and column selects for the target ASIC chip on the MAC card. For each baseline, the MAC card has four results, 18-bit real and imaginary results from each of 2 channels. The two LSbits from IC 13B count through these four results.

The MAC control logic also provides the 8-bit EXT ADDR bus for the MAC cards. This bus is the source of the external address for the ASIC RAMs used for short term integration. This bus has three sources. IC 15B is the source of integration RAM addresses and counts through the 210 baselines in the course of an FFT cycle, IC 14B provides the external RAM address during short term integration readout, and IC 18B provides the external RAM address during self test readout. ROMs 17B and 16B are provided in case the RAM address sequence needs to be scrambled from a straight binary count. These ROMs were not used, however, and, as programmed, are straight through look-up tables. The only real function the ROMs serve is the 3-state output function.

IC 20B is the source of the bank bit of the MAC external RAM address. This signal toggles every 131 msec integration cycle to swap the integrating bank of the MAC ASIC RAM and the secondary storage (readout) bank of the RAM.

The control signals that drive more than one MAC card have more than one version for fanout purposes. Some signals have 2 fanout versions (such as AUXOUT SEL), some have 3 (such as the external address) and some have 4 (such as MACWE).

### 2.2.7 Data Validity and Pulsar Validity Counters

Sheet 4 of the MCC schematic is mostly the logic required for the tape data valid and the pulsar data valid counters. Each MCC handles the data validities for 2 channels (2 counters required) and the pulsar validities for one FCC card (4 counters required).

The function required of the validity counters is to duplicate the action of the MAC short term integrators, but whereas the MAC short term accumulators integrate astronomical cross products, the validity counters count the number of FFT cycles in an integration cycle for which a given baseline has valid data. For each baseline, the two stations of the baseline have their station data valids, as developed at the output of IC 30C or 30B (sheet 3 of the MCC schematic), logically ANDed together to produce a baseline valid signal (VA or VB from IC 2C or 3C). The pulsar validity counters count the number of FFT cycles, in an integration cycle, for which the pulsar gate (see the FCC card description) is permissive. Each spectral point has an individual counter.

A data valid counter consists of 210 binary counters (across 210 RAM addresses) each of which counts from 0 to 8192 and reflect, at the end of an integration cycle, the number of FFT cycles of the integration cycle for which a given baseline had valid data. A pulsar validity counter consists of 256 binary counters (one for each spectral point) each of which counts from 0 to 8192 and reflect, at the end of an integration cycle, the number of FFT cycles of the integration cycle for which a given spectral point was integrated. (Recall that the pulsar gate generator develops a signal used to retain or discard station spectral data, on a spectral point basis, as a function of the phase in the pulsar period. When the pulsar pulse is on, the pulsar gate will be expressed as permissive, allowing cross products to be integrated, when the pulse is off the gate will inhibit integration by forcing the station spectral point value to zero. Frequency dispersion causes the pulse to appear to be on in different spectral points at different times, hence the pulsar gate for different spectral points will be different.)

The 6 validity counters seen on sheet 4 of the MCC schematic, 2 for data and 4 for pulsar, are identical. RAMs 1D and 2D, latches 1E and 2E, and PAL adders 1F, 2F, and 2G constitute one validity counter. The RAMs can be thought of as being in parallel with the MAC ASIC short term accumulator RAMs. The RAM address counters 2C, 3C, and 4C are analog to the 3 sources of the EXT ADDR bus seen on sheet 3 of the MCC schematic (15B, 14B, and 18B). In short:

- 1) the RAM address counter addresses a running sum in the RAMs.

- 2) the partial sum from that RAM location is latched into the latch.

- 3) the PAL adder (for example, ICs 1F, 2F, and 2G) adds the logical state of a validity signal (for example DVA on latch pin 2E-18, applied to the adder on pins 1F-8, 2F-8, and 2G-8) to the old count (the old count is incremented if the validity signal is a logic one).

- 4) the new sum is written back into the same RAM address.

The control signals (from PALs 5B, 6B, 4B, 6C, and 11C) and the RAM address counters control the validity counters so that they operate step by step in parallel with the MAC short term accumulators. Output registers, for example ICs 1G and 1H, are analogous to the output registers in the MAC ASICs that store 18-bit output results. During the 4-bit gap between FFT cycles, results can be read out of the RAMs (using the output address counter 3C or 9C) and stored in these registers. The registers are subsequently read on the same 3-state bus as the MAC results (they are stored in the LTA as baselines 210, 211, and 212). PALs 6B and 11C provide two bits (always zero) during validity readout to bring the bus drive to 18-bits.

Both the data valids and pulsar valids must be delayed before being applied to the validity counters to compensate for the pipeline delays encountered in the data path (the MAC short term integrators and the validity counters should work in exact synchronism). The delay lines seen at the bottom of sheet 4 of the MCC schematic provide this delay. Two delay lines are seen, one for the 2 baseline data valid signals (ICS 3B, 2B, and IC) and one for the 4 pulsar validity signals (ICS 7B, 8B, and 7C). Control logic for the delay lines is provided by IC 9B. Each delay line is a RAM clocked around a closed loop of addresses. The size of the loop defines the total time between a bit going in the RAM and the time it comes out and hence the delay obtained in the delay line.

#### 2.2.8 MAC Output Bus

The MAC output bus, MAC BUS[0..17], passes through the MCC. This bus cycles through the 210 baseline results (baselines 0 through 209) from the short term integrators every 131 msec integration cycle. The validity counters described above are 3-stated onto this bus and enter the long term accumulator (LTA) as 3 additional "baselines" (210, 211, and 212). The bus drivers 2H, 4H, 6H, 8H, and 10H provide differential drive into the LTA.

#### 2.2.9 Snapshot FIFO

As the short term results pass through the MCC on the way to the LTA, the FIFO stages (ICs 14I and 15I) can capture one set of 131 msec results for any given baseline. The desired baseline number is written into IC 18I by the microprocessor and the control logic of PAL 16I clocks 18-bit results into the FIFO every time the target baseline drives the MAC bus. The local micro then reads the FIFO contents. The 2 FIFO chips are tri-stated together with 8 of the 9-bits from each FIFO going directly to the microprocessor data bus and the 9th bit of the FIFOs being multiplexed together in IC 8C.

#### 2.3 MCC software

The 87C51 microprocessor on the MCC card has a 32K X 8 main memory RAM. The main program for the MCC microprocessor is downloaded by the RTS into this memory.

#### 2.3.1 Descriptions of the MCC Software

Below is a brief description of each of the modules listed in the chart below. (Memory allocations seen below are as of 9/17/92.)

| ** * * * * * * * * * * * * * * * * * * * | ****                                    | *****                                 | *****  |

|------------------------------------------|-----------------------------------------|---------------------------------------|--------|

| Module Name                              | Starting Address                        | Ending Address                        | Memory |

| *****                                    | *****                                   | *****                                 | *****  |

| MASTER.ASM                               | 0000                                    | 0149                                  | ROM    |

| ROMHCB.ASM                               | 014A                                    | 02FE                                  | ROM    |

| ASIC.ASM                                 | 02FF                                    | 03AD                                  | ROM    |

| TEST.ASM                                 | 03AE                                    | 053C                                  | ROM    |

| TIME.ASM                                 | 053D                                    | 0659                                  | ROM    |

| MONITOR.ASM                              | 0800                                    | OFOF                                  | ROM    |

| RAM.ASM                                  | 1000                                    | 1023                                  | RAM    |

| RAMTEST.ASM                              | 1024                                    | 1045                                  | RAM    |

| HELP.ASM                                 | 1046                                    | 1D9D                                  | RAM    |

| AUTOPLOT.ASM                             | 1D9E                                    | 1E3B                                  | RAM    |

| RAMHCB.ASM                               | 2000                                    | 22EB                                  | RAM    |

| OBS.ASM                                  | 22EC                                    | 2431                                  | RAM    |

| DISPLAY.ASM                              | 3000                                    | 37EF                                  | RAM    |

| PLOT.ASM                                 | 4000                                    | 47E3                                  | RAM    |

| AUTOTEST.ASM                             | 4800                                    | 4DEB                                  | RAM    |

| *****                                    | * * * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * | *****  |

# 2.3.1.1 MASTER.ASM

MASTER.ASM has the software executed after a hardware reset to the microprocessor. This software will initialize the card and microprocessor functions like the interrupts, the serial port, etc. This module also has the interrupt vector locations. After a reset, the micro will execute from an idle loop in MASTER.ASM awaiting instructions from the terminal or RTS conveyed by interrupts. The fringe cycle interrupt is enabled in the idle loop so that the time code in the PBD frame will appear to run normally.

# 2.3.1.2 ROMHCB.ASM and RAMHCB.ASM

ROMHCB.ASM and RAMHCB.ASM handle the microprocessor communications with the RTS. Some of the basic functions, such as memory load, are handled in the ROM based software but most protocol support is executed out of the RAM based RAMHCB.ASM program.

# 2.3.1.3 ASIC.ASM

ASIC.ASM has the software to load the MAC ASIC control words. The table ATABLE contains the default ASIC control words loaded when a reset occurs.

# 2.3.1.4 TEST.ASM and RAMTEST.ASM

The TEST.ASM module has a number of hardware test routines that allow an operator to test the MCC card either in the FFT test fixture or in the system. Hooks are in place so that software tests can be written in RAM in the RAMTEST.ASM module. This capability allows the generation of new tests without changing the MCC ROMs.

### 2.3.1.5 MONITOR.ASM

The monitor software package has various terminal options supported by the MCC microprocessor.

## 2.3.1.6 RAM.ASM

RAM.ASM is mainly used for linking the ROM and RAM based programs of the MCC together. It is not desirable to have to change ROMs on the MCC cards because on a change in a RAM based program. Thus direct linking of the ROM and RAM based modules is not possible. The strategy used in the MCC software is to always link from the ROM software into the RAM software via jumps to locations that are on page boundaries in RAM modules. These jump locations will not change in memory as software changes are made to the main bodies of the RAM modules and hence link addresses in the ROM modules will not change because of a change to a RAM subroutine.

# 2.3.1.7 HELP.ASM

This module contains ASCII terminal help screens. MONITOR.ASM has an option to display the help screen. Four help screens are provided.

# 2.3.1.8 AUTOPLOT.ASM

This module contains software to support the PLOT routine for plotting spectra captured by the FIFO. PLOT runs on a PC and can be used to view MAC short term accumulator results. The program on the PC is plot.exe and uses a serial port to connect to the MCC. The plot program is menu driven.

## 2.3.1.9 OBS.ASM

OBS.ASM is the main observing software for the MCC microprocessor. This module is entered upon receipt of an OBSERVE command from the RTS. The first action of the software is to configure the MCC card for the observation.

Once the card is configured, the MCC microprocessor starts the observation by enabling interrupts. All of the actions required to support the observation are executed out of interrupt handlers. The interrupt system is described in more detail below. When not supporting an observation in an interrupt routine, the microprocessor waits in an idle loop in OBS.ASM.

Actually, except for supporting self test, the MCC OBS.ASM program has very little to do. Support of the test frame time code and the FIFO readout occurs whether or not the MCC is observing.

#### 2.3.1.10 DISPLAY.ASM

This module contains software to support the display of actual MAC results from the FIFO. It works through the monitor with the monitor command Vyxx. When evoked, this command will cause the FIFO to take a snapshot of the MAC result for baseline xx, channel y, and print the 15, 15, 6 results on the terminal. Each terminal screen will display a 4-by-16 array of numbers and the terminal keys 1, 2, 3, or 4 will choose from 4 possible screens. The screen display can be either single shot or will continuously update as new FIFO snapshots are taken depending on the monitor S function.

## 2.3.1.11 PLOT.ASM

This module contains software to support the plotting of actual MAC results from the FIFO (on the local terminal as opposed to PLOT, above, which interfaces through a PC). It works through the monitor with the monitor command Byxx. When evoked, this command will cause the FIFO to take a snapshot of the MAC result for baseline xx, channel y, and do a very crude plot of the spectrum. The screen will continuously update as new FIFO snapshots are taken (unless the monitor S function prohibits).

# 2.3.1.12 AUTOTEST.ASM

AUTOTEST.ASM is another test routine that uses the FIFO on the MCC card. It is run through the monitor and has the monitor command Qyxx. When evoked, it will first take a snapshot of baseline xx, channel y, and store the results for use as predicted data for the rest of the test. The program will then cycle through all 210 baselines, one at a time, taking snapshots and checking the resulting spectrum against the predicted snapshot. A terminal screen is produced that gives the count of times a given baseline snapshot differed from the predicted. The count saturates at hex F.

If the Qyxx command is used with xx = D2 (the validity baseline number), a different function results. Now each of the 210 results comes down to a single value instead of 256 spectral points and each point is checked against a few specific values. The test result should be self-explanatory. (When xx = d3 or d4, the pulsar validity baseline numbers, the result is different again.)

#### 2.3.2 Microprocessor Interrupt Structure

Almost all of the functions provided by the MCC software are done in interrupt routines. There are several interrupts and a summary is given below:

| interrupt | function          | priority |  |

|-----------|-------------------|----------|--|

| SERIAL    | terminal          | low      |  |

| INTO      | fringe cycle      | high     |  |

| INT1      | HCB communication | medium   |  |

| TIMERO    | not used          | -        |  |

| TIMER1    | not used          | -        |  |

The serial port interrupt is not normally used during an observation but supports a terminal and provides the functionality of the MONITOR.ASM software.

The INTO hardware interrupt is the 4.128 msec fringe cycle interrupt. This interrupt is generated by the sequencers and actually occur 4 times per 4.128 msec fringe cycle. The MCC microprocessor senses the T1 micro input to get integration cycle synchronization and also to initialize a software counter so it can distinguish which of the 4 interrupts per fringe cycle is the actual fringe cycle indicator.

The reason for having 4 interrupts per fringe cycle is so the microprocessor can update the PBD test frame time. The PBD frame period is 2.5 msec and the microprocessor has no interrupt to allow it to know when to update the frame time. The micro instead polls the HEADER discrete in the fringe cycle interrupt routine to know when a header has occurred hence when the time can be updated. The 4.128/4 msec interrupt is frequent enough so it will never miss the time update requirement.

The INT1 hardware interrupt is used for RTS HCB communications with software support provided by the ROMHCB.ASM and RAM.ASM software.

# 2.4 MCC Utility Displays

The MCC terminal provides various utility functions for use when investigating problems in the system. At the MCC prompt a HELP screen is available:

MCC HELP screen (invoke at MCC prompt with letter H):

| DXXXX  | DISPLAY STARTING AT MEM LOC XXXX                          |

|--------|-----------------------------------------------------------|

| PXXXX  | DISPLAY PAGE STARTING AT MEM LOC XXXX                     |

| C/R    | DISPLAY MORE (D, T, P, OR H)                              |

| D      | DISPLAY STARTING AT LAST MEM LOC XXXX                     |

| P      | DISPLAY PAGE STARTING AT LAST MEM LOC XXXX                |

| R      | DISPLAY INTERNAL RAM                                      |

| RXX YY | MODIFY INTERNAL RAM                                       |

| MXXXX  | MODIFY STARTING AT MEM LOC XXXX                           |

| GXXXX  | GOTO MEM LOC XXXX                                         |

| LZZ    | STORES FIFO FULL OF BASELINE ZZ DATA STARTING AT LOC 7000 |

| VYZZ   | DISPLAY RESULTS, BASELINE ZZ, CHANNEL Y                   |

| BYZZ   | PLOT SPECTRA FOR BASELINE ZZ, CHANNEL Y                   |

| QYZZ   | AUTOTEST, USE BASELINE ZZ, CHANNEL Y, FOR PREDICTED       |

|        | ZZ = 00 TO D1, GETS BASELINE 00 TO 209                    |

|        | ZZ = D2, GETS DATA VALIDS (PREDICTED IN RAM LOC 50-51)    |

|        | ZZ = D3, GETS PULSAR DATA VALIDS                          |

|        | ZZ = D4, GETS PULSAR DATA VALIDS                          |

|        | ZZ = FF, NO NEW PREDICTEDS TAKEN                          |

,C/R FOR NEXT HELP SCREEN

Second part (invoke with C/R):

| FX     | SET PLL FREQ FOR STANDARD FREQ (X=0 9.001674 MHZ)    |

|--------|------------------------------------------------------|

| FXXX   | SET PLL FREQ XXX                                     |

| HX     | SET HEADER RAM CONTENTS                              |

| HXX YY | MODIFY HEADER RAM STARTING AT LOC XX                 |

| IXX YY | SET HEADER TIME INCREMENT                            |

| ТΧ     | EXECUTE TEST X                                       |

| ΤΧ ΥΥ  | ANOTHER FORM OF TEST                                 |

| ТМ     | TEST RAM MEMORY                                      |

| WXX    | FILL TAPE FRAME RAM WITH XX BYTE                     |

| H OR ? | (OR HELP) HELP SCREEN                                |

| A*     | PERFORM LAST INSTRUCTION AGAIN                       |

| C*     | DISPLAY VALIDITY CROSS-BAR SWITCH                    |

| S*     | SWITCH BETWEEN INTERNAL AND EXT MEM (DISPLAY & PAGE) |

| X*     | TOGGLE RANDOM DATA/RAM DATA IN TAPE FRAME            |

| Y*     | TOGGLE VLBA/MKIII TAPE FRAME FORMAT                  |

| Ζ*     | TOGGLE TIME IN HEADER RUNNING/NOT RUNNING CONDITION  |

| .*     | CLEAR CRT SCREEN                                     |

,C/R FOR NEXT HELP SCREEN

Third part:

т0 SENDS A BINARY COUNT TO CHIP 28J Τ1 SENDS A BINARY COUNT TO CHIP 281 т2 SENDS A BINARY COUNT TO CHIP 251 ТЗ SENDS A BINARY COUNT TO CHIP 26J AND 26I т4 Х SENDS A BINARY COUNT TO CHIP 22E, 23E, 22C, 23C, 22B, OR 21C SENDS A BINARY COUNT TO CHIP 181 т5 T6 XX TESTS THE CHIP PROG WORD LOGIC (CARD GIVEN BY XX) т7 WRITES AND CHECKS THE FRAME BUFFER RAM (29F) т8 WRITES AND CHECKS THE HEADER BUFFER RAM (27F) т9 WILL TEST THE PLL ТΑ LOOP ON TEST 9 ТΒ TC ТD ΤЕ ΤF TEST IN RAM TF 00 LOOP SENDING ASIC CONTROL WORDS ,C/R FOR NEXT HELP SCREEN Fourth part: PLOT SPECTRA FROM BASELINE XX, CHANNEL Y BYXX SELECT HORIZONTAL SCALE 1\* TO 7\* E\*, C\* EXPAND, COMPACT VERTICAL SCALE U\*, D\* MOVE PLOT UP, DOWN WILL GIVE REAL, IMAGINARY, OR MAGNITUDE PLOT R\*, I\*, OR M\* VYXX DISPLAY RESULTS, BASELINE XX, CHANNEL Y SELECT PAGE 1 TO PAGE 4 1\* TO 4\* QYXX AUTOTEST OF CHANNEL Y (TAKES PREDICTED SNAPSHOT FROM BASELINE XX) 7.\* ZERO ERRORS B,V,OR Q COMMON OPTIONS N\* NEXT BASELINE Х\* SWITCH CHANNEL s\* SWITCHES FROM CONTINUOUS TO SINGLE SHOT CR TAKES ANOTHER SHOT IN SINGLE SHOT MODE SP OR ESC EXITS PLOT ROUTINE

LXX STORES FIFO FULL OF BASELINE XX DATA STARTING AT LOC 7000 S\* SWITCHES FROM CONTINUOUS TO SINGLE SHOT

| The C command<br>ANTENNA |     | the cros<br>SELECTIO | s bar assignment displays as follows:<br>N |

|--------------------------|-----|----------------------|--------------------------------------------|

| 00                       | 0   |                      | At each four into one mux,                 |

| 01                       | 0   |                      | the MUX SELECTION column                   |

| 02                       | 0   |                      | shows which of the four inputs             |

| 03                       | 0   |                      | is selected; these tape validity           |

| 04                       | 0   |                      | muxes on the MCC must be programmed        |

| 05                       | 0   |                      | the same as the tape data muxes on         |

| 06                       | 0   |                      | the FFT cards.                             |

| 07                       | 0   |                      |                                            |

| 08                       | 0   |                      |                                            |

| 09                       | 0   |                      |                                            |

| 10                       | 0   |                      |                                            |

| 11                       | 0   |                      |                                            |

| 12                       | 0   |                      |                                            |

| 13                       | 0   |                      |                                            |

| 14                       | 0   |                      |                                            |

| 15                       | 0   |                      |                                            |

| 16                       | 0   |                      |                                            |

| 17                       | 3   |                      |                                            |

| 18                       | 0   |                      |                                            |

| 19                       | 0   |                      |                                            |

| TEST = 00                | COU | JNT = 05             |                                            |

Examples of two useful commands are shown below:

The VOD2 command shows validity values for baseline 0xD2 (210 decimal): (SPACE bar ends the updating of the display) This example could apply to a job with stations 0-12 in use. The E indicates a validity count equal to the 0x2000 stored for reference at ram locations 50-51. The B indicates a validity count in the range of 0x1F00 to 0x2000.

|     |    |    |    | DATA VALIDITY |    | Ι  | 02 | CHANNEL 4 |    |    |   |     |    |     |     |      |     |    |   |   |

|-----|----|----|----|---------------|----|----|----|-----------|----|----|---|-----|----|-----|-----|------|-----|----|---|---|

| ANT | 19 | 18 | 17 | 16            | 15 | 14 | 13 | 12        | 11 | 10 | 9 | 8   | 7  | 6   | 5   | 4    | 3   | 2  | 1 | 0 |

| 0   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | E         | Ε  | Ε  | E | Е   | Ε  | Ε   | В   | Е    | Е   | Е  | Ε | Ε |

| 1   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | E         | E  | Ε  | E | Е   | Е  | Ε   | В   | Е    | Е   | Е  | Ε |   |

| 2   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Ε  | E  | E | Е   | Е  | Е   | В   | Е    | Е   | Е  |   |   |

| 3   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | E         | Е  | Ε  | Е | Е   | Ε  | Е   | в   | Е    | Е   |    |   |   |

| 4   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Е         | Е  | Е  | Е | Е   | Е  | Е   | В   | Е    |     |    |   |   |

| 5   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | В         | В  | в  | В | В   | в  | в   | в   |      |     |    |   |   |

| 6   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Е  | E  | Е | Е   | Е  | Е   |     |      |     |    |   |   |

| 7   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Ε  | E  | Е | Е   | Е  |     |     |      |     |    |   |   |

| 8   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | E         | Е  | E  | E | E   |    |     |     |      |     |    |   |   |

| 9   | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Ε  | E  | E |     |    |     |     |      |     |    |   |   |

| 10  | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Е  | E  |   |     |    |     |     |      |     |    |   |   |

| 11  | 0  | 0  | 0  | 0             | 0  | 0  | 0  | Ε         | Е  |    |   |     |    |     |     |      |     |    |   |   |

| 12  | 0  | 0  | 0  | 0             | 0  | 0  | 0  | E         |    |    |   | E = | F  | MA  | 50- | 51   | VAL | UE |   |   |

| 13  | 0  | 0  | 0  | 0             | 0  | 0  | 0  |           |    |    |   | * = | >2 | 000 | (1  | LLE  | GAL | ı) |   |   |

| 14  | 0  | 0  | 0  | 0             | 0  | 0  |    |           |    |    |   | 1 = |    | 000 |     |      |     |    |   |   |

| 15  | 0  | 0  | 0  | 0             | 0  |    |    |           |    |    |   | B = | (2 | 000 | ,1F | .00] |     |    |   |   |

| 16  | 0  | 0  | 0  | 0             |    |    |    |           |    |    |   | M = | (1 | F00 | ,10 | 00]  |     |    |   |   |

| 17  | 0  | 0  | 0  |               |    |    |    |           |    |    |   | m = | (1 | 000 | ,01 | 00]  |     |    |   |   |

| 18  | 0  | 0  |    |               |    |    |    |           |    |    |   | S = | (0 | 100 | ,00 | 01]  |     |    |   |   |

| 19  | 0  |    |    |               |    |    |    |           |    |    |   | 0 = | 0  | 000 |     |      |     |    |   |   |

The following table tabulates the number of invalid FFT cycles per 4 msec tick due to buffer activity in the DEF (assuming low bandwidth mode is not in use). This table is excerpted from stnTask.c. It can be used to calculate the expected number of valid FFT cycles in 131 msec (the VOD2 display above is based on the number of valid FFT cycles in 131 msec). For example, there are 256 FFT cycles per 4 msec, and 32 4 msec cycles per 131 msec, so the maximum possible validity count in 131 msec is  $32 \times 256 = 8192 = 0x2000$ .

| 1    | 2          | 4     | 8           | 16<br>       | $\leftarrow$ Oversample factors |

|------|------------|-------|-------------|--------------|---------------------------------|

| /*   | FFT s      | ize 6 | 4 */        |              |                                 |

| Ó.   | 0.         | 2.    | · ,<br>6.   | 14           | /* 1-4 */                       |

| 1.   | 0,<br>2,   | 6     | 14          | 30,          |                                 |

| 3    | 6          | 14    | 30          | 64,          | /* 1-1 */                       |

| 7    | 14         | 30    | 50 <b>,</b> | 256          | /* 2-1 */                       |

| 15,  | 30,        | 64,   | 256,        | 256,<br>256, | /* 4-1 */                       |

| /*   | FFT s      | ize 1 | 28 */       |              |                                 |

| Ο,   | Ο,         | 2,    | 6,          | 14,          | /* 1-4 */                       |

| 1,   | 2,         | 6,    | 14,         | 30,          | /* 1-2 */                       |

|      |            |       |             |              | /* 1-1 */                       |

| 7,   | 6,<br>14,  | 30,   | 64,         | 128,         | /* 2-1 */                       |

| 15,  | 30,        | 64,   | 128,        | 256,         | /* 4-1 */                       |

| /* : | FFT s      | ize 2 | 56 */       |              |                                 |

| Ο,   | Ο,         | 2,    | 6,          | 14,          | /* 1-4 */                       |

| 1,   | 2,         | 6,    | 14,         | 30,          | /* 1-2 */                       |

| 3,   | 2,<br>6,   | 14,   | 30,         | 64,          | /* 1-1 */                       |

| 7,   | 14,        | 30,   | 64,         | 128,         | /* 2-1 */                       |

| 15,  | 30,        | 64,   | 128,        | 256,         | /* 4-1 */                       |

|      | FFT s      |       |             |              |                                 |

| Ο,   | 0,<br>2,   | 2,    | 6,          | 14,          | /* 1-4 */                       |

| 1,   | 2,         | 6,    | 14,         | 30,          | /* 1-2 */                       |

| 3,   | 6,         | 14,   | 30,         | 64,          | /* 1-1 */                       |

| 7,   | 14,<br>30, | 30,   | 64,         | 128,         | /* 2-1 */                       |

| 14,  | 30,        | 64,   | 128,        | 256,         | /* 4-1 */                       |

|      | FFT s      |       |             |              |                                 |

|      | 2,         |       |             |              | /* 1-4 */                       |

| з,   | 6,         | 14,   | 30,         | 64,          | /* 1-2 */                       |

| 7,   | 14,<br>30, | 30,   | 64,         | 128,         | /* 1-1 */                       |

| 15,  | 30,        | 64,   | 128,        | 256,         | /* 2-1 */                       |

| 32,  | 64,        | 128,  | 256,        | 256,         | /* 4-1 */                       |

|      | FFT s      |       |             |              |                                 |

| З,   | 6,         | 14,   | 30,         | 64,          | /* 1-4 */                       |

| 7,   | 14,<br>30, | 30,   | 64,         | 128,         | /* 1-2 */                       |

| 15,  | 30,        | 64,   | 128,        | 256,         | /* 1-1 */                       |

|      | 64,        |       |             |              | /* 2-1 */                       |

| 64,  | 128,       | 256,  | 256,        | 256          | /* 4-1 */                       |

24

#### 2.5 The MCC PLOT Program

The MCC terminal can also be used to display amplitude and phase plots of the spectra for any baseline. The executable program used for this is named plot.exe and is usually run by first connecting to the MCC using the VTERM terminal emulator to verify that a valid MCC prompt is operating, then escape from VTERM using the double shift key operation. At the DOS prompt, invoke the PLOT program. The program prompts for the baseline (in hex), the channel (0 or 1) and the desired display (amplitude or phase etc.).

The plot.exe and plot.c files are presently stored in the CORRDWGS area in the directory /misc/re/c. Copies of plot.exe are available on the four PCs in the correlator area and on the PC used with the testbed rack.

Figure 3 Master Control Card Block Diagram

# **3** The Multiply and Accumulate Card (MAC)

# 3.1 Introduction

The MAC Cards (also referred to as Multiplier Cards) perform the multiplication and accumulation functions in the VLBA Correlator. Both self and cross multiplication products are done for 20 stations times 20 stations, producing 210 baselines for each of 8 baseband converter channels, in arrays of MAC cards.

The MAC has two modes of operation. These modes are nonpolarization (MACNP) and polarization (MACP). In non-polarization mode, the multipliers can be logically viewed as 8 distinct triangular arrays of 210 baselines each.

In order to handle polarization mode, pairs of arrays are physically combined, forming four combined arrays as seen in the FFT to MULTIPLIER INTERFACE block diagram, K029D01.BLK, found in Volume 2 of this report. Polarization pairs are handled in adjacent FFT pipelines, and the output data streams are multiplexed together. The multiplexed data streams drive VLBA1 ASICs in both the even and odd sections of the combined arrays.

In non-polar mode, the even sections of the arrays produce the Right x Right (RxR) products and the odd sections produce the Left x Left (LxL) products, by processing the appropriate FFT results in the multiplexed data streams. In polar mode, the even sections produce RxR and RxL while the odd sections produce LxR and LxL, as shown in K029D01.BLK.

A single combined array consists of 15 MAC cards, numbered 0 through 14 as seen in K029D01.BLK. See Figure 2 for the layout of the 14 cards in a MAC bin. The cards located on the array diagonal are cards number 0, 5, 9, 12 and 14. The cards on the diagonal are partially populated in order to not have unused VLBA1 chips running under power in un-used locations (below the diagonal). In Figure 2, these card locations are indicated with an asterisk.

The block diagram of a single Multiplier Card is shown in K030D01.BLK, found in Volume 2 of this report. The physical layout of the VLBA1 chips on the card is in two square arrays of 16 chips each, but K030D01.BLK shows a logical arrangement rather than the physical layout. The physical layout can be seen on sheet one of the MAC schematic, L003D01.SCH (see Volume 2). In both K030D01.BLK and L003D01.SCH, the VLBA1 chips below the dashed lines are the chips that are not installed in the partially populated cards located on the array diagonal.

### 3.1.1 The MAC VLBA1 Control Word Daisy Chain

Arrayl Array0 Arrayl Array0

Col 3 Col 2 Col 2

The 32 VLBA1 chips on a MAC card are daisy chained together in such a way that partially populated cards along the diagonal of the multiplier array may be loaded with VLBA1 control words using the same software as a fully populated card. This requires that the control word daisy chain connects to all of the VLBA1 chips "on and above the diagonal" before connecting to the chips below the diagonal.

Col 1

Array1 Array0 Array1 Array0

Col 1 Col 0

Col 0

| ·····                     |                      |                              | - |

|---------------------------|----------------------|------------------------------|---|

| -  24  <-  25  <-  26  <- | -  27  <  28  <-  29 | <-  30  <-  31  <            | R |

|                           |                      | CTRL WRD IN                  |   |

| -  18  <-  19  <-  20  <- | -  21  <  22  <-  23 | 10  <-  11   </td <td>R</td> | R |

|                           | <br>                 |                              |   |

| -  14  <-  15  <-  16  <- | -  17    6  <-  7    | <-  8  <-  9  <-             | R |

| I                         | I                    |                              |   |

| -  12  <-  13   -  0  <-  | -  1  <  2  <-  3    | <br> <-  4  <-  5  <-        | R |

I----->CTRL WRD OUT The offset (OFS) within the daisy chain is indicated for each VLBA1 location, where offset 0 is the first 32 bit control word shifted into the card and offset 31 is the last control word shifted in.

| OFS | ROW | COL | ARRAY |                                                                         | OFS      | ROW   | COL    | ARRAY |

|-----|-----|-----|-------|-------------------------------------------------------------------------|----------|-------|--------|-------|

|     |     |     |       |                                                                         |          |       |        |       |

| 0   | 3   | 2   | 1     | <first td="" word<=""><td>16</td><td>2</td><td>2</td><td>1</td></first> | 16       | 2     | 2      | 1     |

| 1   | 3   | 2   | 0     | SHIFTED INTO                                                            | 17       | 2     | 2      | 0     |

| 2   | 3   | 1   | 1     | CARD                                                                    | 18       | 1     | 3      | 1     |

| 3   | 3   | 1   | 0     |                                                                         | 19       | 1     | 3      | 0     |

| 4   | 3   | 0   | 1     |                                                                         | 20       | 1     | 2      | 1     |

| 5   | 3   | 0   | 0     |                                                                         | 21       | 1     | 2      | 0     |

| 6   | 2   | 1   | 1     |                                                                         | 22       | 1     | 1      | 1     |

| 7   | 2   | 1   | 0     |                                                                         | 23       | 1     | 1      | 0     |

| 8   | 2   | 0   | 1     |                                                                         | 24       | 0     | 3      | 1     |

| 9   | 2   | 0   | 0     |                                                                         | 25       | 0     | 3      | 0     |

| 10  | 1   | 0   | 1     |                                                                         | 26       | 0     | 2      | 1     |

| 11  | 1   | 0   | 0     |                                                                         | 27       | 0     | 2      | 0     |

|     |     |     |       |                                                                         | 28       | 0     | 1      | 1     |

| 12  | 3   | 3   | 1     |                                                                         | 29       | 0     | 1      | 0     |

| 13  | 3   | 3   | 0     |                                                                         | 30       | 0     | 0      | 1     |

| 14  | 2   | 3   | 1     |                                                                         | 31       | 0     | 0      | 0     |

| 15  | 2   | 3   | 0     | (last v                                                                 | word shi | ifted | into c | ard)  |

Col 3

# 3.2 MAC Card Description

The MAC card logic is composed primarily of the VLBA1 ASIC chips, with a minimum of glue logic required. The data streams from the FFT cards are in 4,4,4 format (four bits of real mantissa, four bits of imaginary mantissa, and four bits of common exponent). These input data signals are all differential ECL. These inputs are converted to TTL using 10125 ECL to TTL translators, and then captured by the 32 MHz system clock in 74F821 or 74F574 registers.

Refer to the schematic sheets L003D01.SCH through L003D04.SCH, found in Volume 2, for the following descriptions.

# 3.2.1 MAC Card I/O Pin Definitions

| _      |             |     |        |                 |       |      |      |        |       | _   |       |     |

|--------|-------------|-----|--------|-----------------|-------|------|------|--------|-------|-----|-------|-----|

| 1      |             |     | 3V     | 2V              |       | 1 V  |      | 0      | <br>7 |     |       |     |

| İ      | OH[011]     |     |        | [0]             |       |      |      | [0.    | .11]  |     |       |     |

|        | 1H[011]     |     |        | '444'<br>per in |       |      | TS   |        |       | 192 | FROM  | FFT |

| Ì      |             |     |        | per in          |       |      |      |        | l     | 2   | CK32  |     |

|        | 2H[011]     |     |        |                 |       |      |      |        |       | 4   | CTRL  |     |

| I.     |             |     |        | TOTAL           |       |      |      |        |       |     | CTRL  |     |

| I      | 3H[011]     | (V= | vert a | axis H          | I = h | oriz | axis | ;)     |       | -   | EXTAI |     |

|        |             |     |        |                 |       |      |      |        |       | -   | CRWRI | 2   |

| I      | CK32ECL\    | -   |        |                 |       |      |      |        | l     |     | CRSO  |     |

| 1      | CK32ECL     | 2   | PINS   |                 |       |      |      |        |       | 18  | DOUT  |     |

|        | INIT\       |     |        |                 |       |      |      |        | i     | 236 | -     |     |

|        |             | 4   | DINC   |                 |       |      |      |        | 1     |     | VCC   |     |

| -      | MACWE       | 4   | ETNO   |                 |       |      |      |        | 1     |     | GND   |     |

|        | STAREAD     |     |        |                 |       |      |      |        |       |     | VEE   |     |

| 1      | D IIII(DIID |     |        |                 |       |      |      |        |       |     | SPARE | 5   |

| i      | CRDSEL      |     |        |                 |       |      |      |        |       |     | -     | _   |

| i      | ROW0        |     |        |                 |       |      |      |        | I     | 288 | TOTAI |     |

| Ì      | ROW1        | 7   | PINS   |                 |       |      |      |        | I     |     |       |     |

| 1      | COL0        |     |        |                 |       |      |      |        |       |     |       |     |

|        | COL1        |     |        |                 |       |      |      |        |       |     |       |     |

| 1      | ARRAY       |     |        |                 |       |      |      |        | I     |     |       |     |

| I.     | AUXOUT      |     |        |                 |       |      |      |        | I     |     |       |     |

| Ι      |             |     |        |                 |       |      |      |        | I     |     |       |     |

|        | EXTADR[08]  | 9   | PINS   |                 |       |      |      |        | l     |     |       |     |

| I<br>I | CRCLK       |     |        |                 |       |      |      |        |       |     |       |     |

| i      | CRSI        | 3   | PINS   |                 |       |      | 1 PI | N      | CRSO  |     |       |     |

| Ì      | CRSTB       |     |        |                 |       |      |      |        | ļ     |     |       |     |

| Ι      |             |     |        |                 |       |      |      |        | l     |     |       |     |

| Ι      |             |     |        |                 |       |      |      |        | I     |     |       |     |

|        |             |     |        |                 | 18    | PINS | DC   | O] TUC | 17]   | l   |       |     |

| Ι      |             |     |        |                 |       |      |      |        | [     |     |       |     |

|        |             |     |        |                 |       |      |      |        |       | -   |       |     |

Signal Descriptions:

FFT INPUTS: '444' signals from FFT engines; 32 MHz rate, ECL differential; 6 bridging loads per run, 100 ohm termination at end of run on backplane; each '444' signal consists of bits 0-11 (12 bits total); 8 sets total \* 12 bits per set \* 2 pins per bit = 192 pins; CK32 inputs: SYSTEM CLOCK differential ECL master clock to card, 2 pins; 100 ohm termination on card; INIT\: FFT CYCLE INIT PULSE TTL single ended, 32 MHz resolution, drives one 74F574 input on each card; one clock pulse wide, asserted once per fft cycle CLAC: CLEAR ACCUMULATOR TTL single ended, 32 MHz resolution, drives one 74F574 input on each card; asserted during first cycle of accumulation into a bank of ram; MACWE\: MAC WRITE ENABLE TTL single ended, 32 MHz resolution, drives one 74F574 input on each card; Asserted during bit period #514 (periods= 0-515); causes off line ram bank contents to be strobed into 36 bit storage register on the ASIC (the external address bus applies the ram address during bit period #513); if CLAC happens to be asserted during the MACWE\ pulse, the data will be blanked; STAREAD: SHORT TERM ACCUMULATOR READ TTL single ended, 32 MHz resolution, drives one 74F574 input on each card; defines the read out cycle for reading the 36 bit results in the storage register on the ASIC; STAREAD is high for one 32 MHz clock period, low for 7 clock periods; the rising edge of STAREAD captures the "address" (CRDSEL\, ROW, COL, ARRAY and AUXOUT) of the result to be read; if a result is selected during one STAREAD cycle, that result is valid at the card output during the low portion of the next STAREAD cycle; CRDSEL CARD SELECT ROW[0..1] ROW SELECT COL[0..1] COLUMN SELECT ARRAY ARRAY SELECT AUXOUT: **18 BIT CHUNK SELECT** TTL single ended, 4 MHz resolution, drive one 74F574 input on each card;

When a hardware baseline result from an array is to be selected, the MCC translates the baseline number, 0-209, into a card select, row select and column select in order to access a single ASIC in an array on a MAC card.

When AUXOUT is logic zero, the 18 bits selected from the ASIC RAM B are: d17 d16 d15 d14 d13 d12 d11 d10 d9 d8 d7 d6 d5 d4 d3 d2 d1 d0 \_\_\_ ex5 ex4 ex3 i14 i13 i12 i11 i10 i9 i8 i7 i6 i5 i4 i3 i2 i1 i0 When AUXOUT is logic one, the 18 bits selected from the ASIC RAM A are: d17 d16 d15 d14 d13 d12 d11 d10 d9 d8 d7 d6 d5 d4 d3 d2 d1 d0 --- --- --- --- --- --- --- --ex2 ex1 ex0 r14 r13 r12 r11 r10 r9 r8 r7 r6 r5 r4 r3 r2 r1 r0 where the data is 15,15,6 format: 15 bits of real mantissa, one's complement format 15 bits of imag mantissa, one's complement format 6 bits of common exponent, two's complement format EXTADR[0..8]: EXTERNAL ADDRESS TTL single ended, 16 MHz resolution, drive one 74F824 input on each card; Provides the READ address for ASIC accesses; the internal address generator provides the WRITE address; CRCLK CONTROL REGISTER CLOCK CRSI CONTROL REGISTER SERIAL DATA INPUT CRSTB CONTROL REGISTER STROBE CRSO: CONTROL REGISTER SERIAL DATA OUTPUT TTL single ended, lower resolution (87C51 driver) inputs drive one 74F541 input on each card; CRCLK rising edge clocks 32 serial data bits (bit 0 first) into each ASIC; ASICs are daisy chained on a card; CRSTB pulses high to latch the serial register contents into a secondary storage latch; DOUT[0..17]: DATA OUTPUT TTL tri-state card output bus; outputs of 15 cards tri-stated together within a chassis; In both MACNP and MACP modes, the INIT, EXTADR, CLAC and MACWE

In both MACNP and MACP modes, the INIT, EXTADR, CLAC and MACWE signals require a single 32 MHz clock cycle delay for the versions that go to array 1, with respect to the array 0 inputs.

# 3.2.2 FFT to MAC Interface

Adjacent channel 4,4,4 results from the FFT are multiplexed together. For purposes of discussion, even channels are assumed to be right polarization, odd channels left polarization, as seen in the FFT to MULTIPLIER INTERFACE block diagram, K029D01.BLK, found in Volume 2. At the beginning of an FFT cycle, the first 4,4,4 data point coming out of CHO is sent across the interface in one clock cycle, followed by the first point out of CH1. The data rate out of the FFT pipelines is 16 MHz, the data rate over the interface is 32 MHz.

At the FFT end, the multiplexing is done in a 2:1 mux with storage. The resulting signals are translated to ECL (10124) and sent differentially to the MAC cards. Each signal has 6 bridging loads, with a termination at the end of the run.

At the MAC end, each bridging load is a 10125 ECL/TTL translator, the output of which is captured in a 74F821 or similar register. Each register for vertical axis signals drives 8 ASIC inputs. Each register for horizontal axis signals drives 8 ASIC inputs. (In MAC modes, the NORM input is internally connected to the AUX input for use in MACPA1.)

#### 3.3 Ram Addressing

The original scheme for addressing the rams in MAC mode called for a single system wide external address that would control both reading and writing during accumulation, and readout access for dumping the accumulated results.

The advent of sub-arrays, which allows MACP and MACNP to co-exist, made this impossible. The following list shows the address sequences required for both modes (see V009D01.TIM in Volume 2):

| Μ    | IACNP | MZ     | ACP   |                              |

|------|-------|--------|-------|------------------------------|

| READ | WRITE | E READ | WRITE |                              |

|      | ·     |        |       |                              |

| 0    |       | 0      |       | These sequences are all      |

| RD0  |       | RD0    |       | 16 MHz clock rate counter    |

| 1    |       | RD1    |       | outputs.                     |

| RD1  |       | 1      |       |                              |

| 2    |       | 2      |       | The "RD" and "WR" are used   |

| RD2  |       | RD2    |       | to indicate when the address |

| 3    | WR0   | RD3    | 0     | must be present. The other   |

| RD3  | 0     | 3      | WR0   | times were then filled in to |

| 4    | WR1   | 4      | WR1   | show that the same sequence  |

| RD4  | 1     | RD4    | 1     | may be used for reading the  |

| 5    | WR2   | RD5    | 2     | ram in both modes.           |

| RD5  | 2     | 5      | WR2   |                              |

| 6    | WR3   | 6      | WR3   |                              |

| RD6  | 3     | RD6    | 3     |                              |

| 7    | WR4   | RD7    | 4     |                              |

Since one read sequence can handle both modes, the system wide external address bus may be used for reading the rams during accumulation, as well as accessing the accumulated results when reading out the "off line" memory bank.

The external address can not also be used for the write address sequence, so the internal address generator is used for this purpose.

#### 3.4 Card Edge Timing and MACWE Accesses

The timing relations between the 4,4,4 input data streams and the control signals (INIT, EXTADR and MACWE) at the MAC card edge are shown in drawing V009D01.TIM, found in Volume 2. This drawing starts with the required timings at the ASIC input pins in both array 0 and array 1, and then derives the card edge timing.

The four cycle gap (clock cycles #512 - #515) allows time to access results from the off line bank in the ASIC. Every 131 msec the ram bank in the ASIC switches. While one bank is accumulating, the other bank is available for readout. The ACCESS references in V009D01.TIM show the clock cycles at which the MACWE pulse and the EXTADR address must be present in order to read out a single result from the off line bank. These MACWE accesses occur every 27 FFT cycles, requiring 6912 FFT cycles to read out all 256 spectral results.

#### 3.5 Short Term Accumulator Readout Cycle

After every MACWE access, the single 36 bit results are read from every MAC ASIC in the system, 18 bits at a time. The STAREAD (Short Term Accumulator Read) signal controls the readout. The rising edge of STAREAD clocks the "address" into U35. If CRDSEL\ is asserted (low), then the selected ASIC is output enabled onto one of the two 18 bit buses. See K030D01.BLK, Multiplier Card Block Diagram, in Volume 2, for the steps involved in selecting a MAC card, selecting an ASIC on the card and enabling the card output onto the backplane tri-state bus.

#### 3.5.1 Readout Sequence

The PROM at location 12A on the MCC controls the readout sequence for reading the 36 bit results from each of the 210 baselines in the combined array controlled by a MCC. The PROM is addressed to sequence from baseline 0 through baseline 209. The outputs of the PROM are decoded to select a row, column and card. The following figure defines the baselines (0-209) on each card (0-14):

Figure 4 Hardware Baselines

The following three figures summarize the card numbers, column numbers and row numbers as a function of baseline. This information is required in the MCC PROM at location 12A.

#### Figure 5 Map of Cards versus Baselines

|    |              | 19  | 18 | 17 | 16 | 15   | 14   | 13   | 12   | 11  | 10   | 9  | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0  |

|----|--------------|-----|----|----|----|------|------|------|------|-----|------|----|---|---|---|---|---|-----|-----|-----|----|

|    |              |     |    |    |    |      |      |      |      | VE  | RTIC | AL |   |   |   |   |   |     |     |     |    |

| 0  |              | 4   | 4  | 4  | 4  | 3    | 3    | 3    | 3    | 2   | 2    | 2  | 2 | 1 | 1 | 1 | 1 | 0   | 0   | 0   | 0  |

| 1  |              | 4   | 4  | 4  | 4  | 3    | 3    | 3    | 3    | 2   | 2    | 2  | 2 | 1 | 1 | 1 | 1 | 0   | 0   | 0   | 1  |

| 2  |              | 4   | 4  | 4  | 4  | 3    | 3    | 3    | 3    | 2   | 2    | 2  | 2 | 1 | 1 | 1 | 1 | 0   | 0   | 1   | 1  |

| 3  |              | 4   | 4  | 4  | 4  | 3    | 3    | 3    | 3    | 2   | 2    | 2  | 2 | 1 | 1 | 1 | 1 | 0   |     | 1   | 1  |

| 4  | Н            | 8   | 8  | 8  | 8  | 7    | 7    | 7    | 7    | 6   | 6    | 6  | 6 | 5 | 5 | 5 | 5 |     |     | 1   | 1  |

| 5  | 0            | 8   | 8  | 8  | 8  | 7    | 7    | 7    | 7    | 6   | 6    | 6  | 6 | 5 | 5 | 5 | b | ase | lin | e   | 1  |

| 6  | R            | 8   | 8  | 8  | 8  | 7    | 7    | 7    | 7    | 6   | 6    | 6  | 6 | 5 | 5 |   | n | r 2 | 0   |     | 1  |

| 7  | Ι            | 8   | 8  | 8  | 8  | 7    | 7    | 7    | 7    | 6   | 6    | 6  | 6 | 5 |   |   |   |     |     |     | 1  |

| 8  | Z            | 11  | 11 | 11 | 11 | 10   | 10   | 10   | 10   | 9   | 9    | 9  | 9 |   |   |   |   |     |     |     | 1  |

| 9  | 0            | 11  | 11 | 11 | 11 | 10   | 10   | 10   | 10   | 9   | 9    | 9  |   |   |   |   |   | b   | ase | lin | el |

| 10 | N            | 11  | 11 | 11 | 11 | 10   | 10   | 10   | 10   | 9   | 9    |    |   |   |   |   |   | n   | r 0 |     |    |

| 11 | Т            | 11  | 11 | 11 | 11 | 10   | 10   | 10   | 10   | 9   |      |    |   |   |   |   |   |     |     |     |    |

| 12 | А            | 13  | 13 | 13 | 13 | 12   | 12   | 12   | 12   |     |      |    |   |   |   |   |   |     |     |     |    |