# VLBA Technical Report No. 46 THE VLBA CORRELATOR **DIGITAL FILTER** VOLUME 1 of 2

Joseph Greenberg

February 1, 1999

firmanv1.doc Microsoft Word not under SCCS control

Master file stored in /corrdwgs/manuals/firman/SCCS (where the SCCS file would have been stored)

This page intentionally left blank

# TABLE OF CONTENTS

| <b>T</b> | 4 <i>BL</i> 1 | E OF CONTENTS                            | . 3 |

|----------|---------------|------------------------------------------|-----|

| T        | 4 <i>BL</i> I | E OF FIGURES                             | . 6 |

| 1        | Int           | roduction                                | . 7 |

|          | 1.1           | Functions of the FIR Filter Card         | 7   |

| 2        | Th            | e FIR Card                               | . 7 |

|          | 2.1           | Top Level FIR Block Diagram Description  | 7   |

|          | 2.1.          | 1 Reading Data from the LTA              | 7   |

|          | 2.1.          | 2 Processing the LTA Data                | 8   |

| 3        | Ove           | erview of the FIR Card                   | 12  |

|          | 3.1           | Data Rates                               |     |

|          | 3.1.          |                                          |     |

|          | 3.1.          | 2 FIR Output Data Rate                   | 12  |

|          | 3.2           | Basic FIR Program Loop                   | 13  |

|          | 3.3           | Straight Thru Mode                       | 14  |

|          | 3.4           | Backend Buffer                           | 14  |

|          | 3.5           | Subarrays                                | 14  |

|          | 3.6           | Validity Counts                          | 15  |

|          | 3.6.          | •                                        |     |

|          | 3.6.          |                                          |     |

|          | 3.7           | Tap Weights                              | 16  |

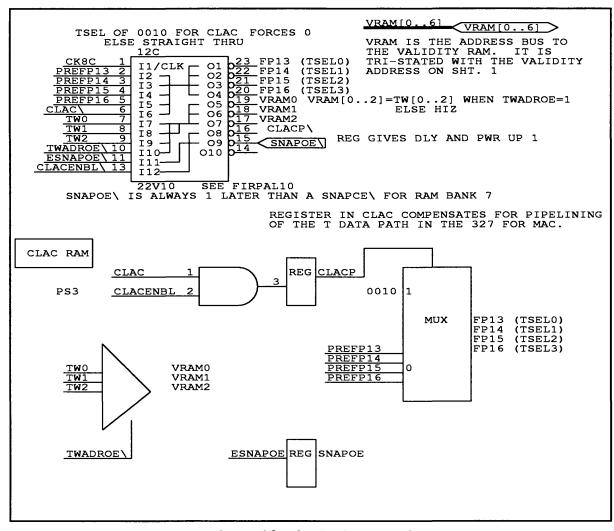

|          | 3.8           | Clear Accumulator (CLAC)                 | 17  |

|          | 3.9           | Microprocessor Interface                 | 17  |

|          | 3.9.          |                                          |     |

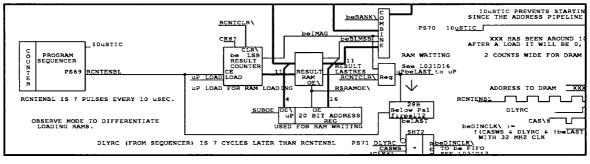

|          | 3.9.          | 2 Microprocessor DRAM Address Generation | 18  |

|          | 3.10          | Dram Address Generation                  | 18  |

|          | 3.11          | DRAM Printed Circuit Boards              | 19  |

|          | 3.12          | Backend Address Generation               | 19  |

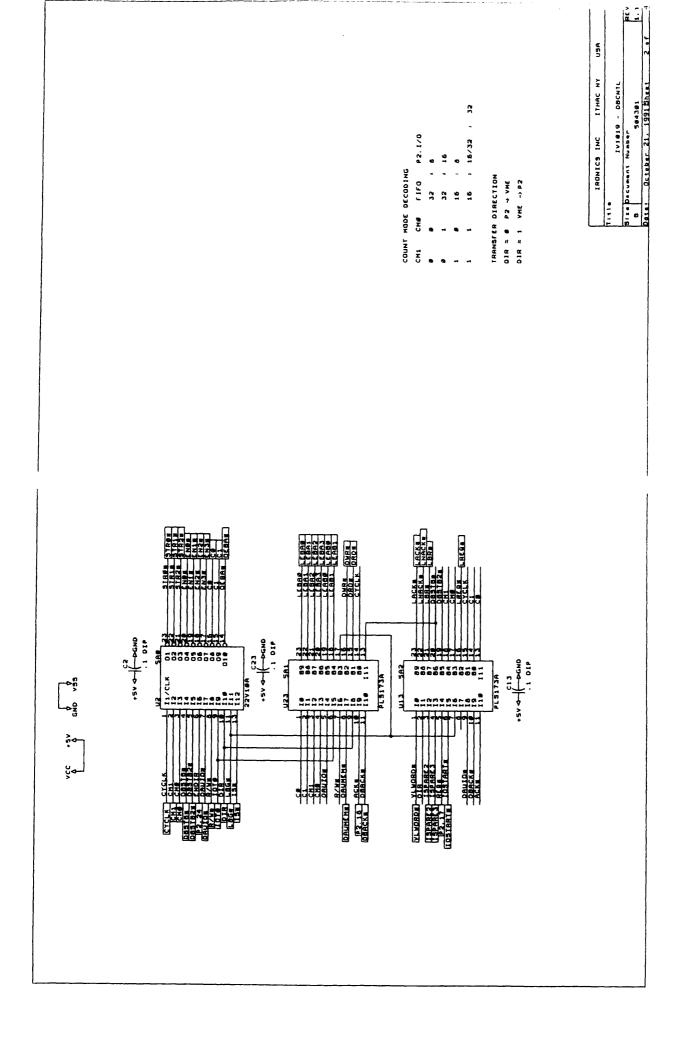

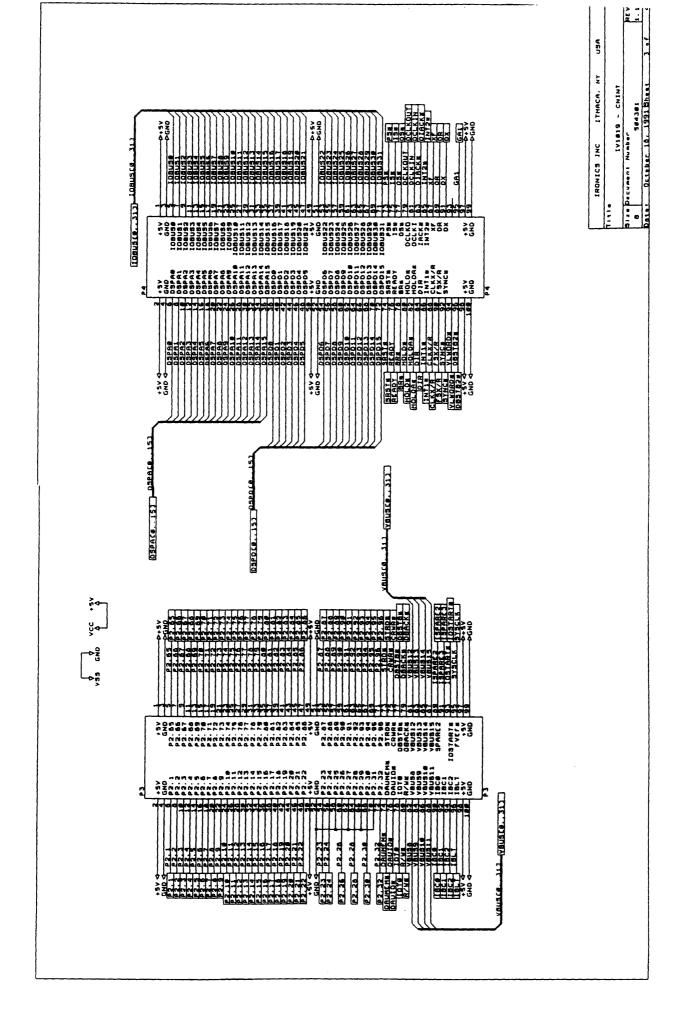

|          | 3.13          | Backend Interface via the Ironics Board  | 20  |

|          | 3.13          |                                          |     |

|          | 3.13          | B.2 Backend Data Transfer Example        | 22  |

| 4        | Inp           | outting and Filtering Validities         | 22  |

|          | 4.1           | Validities Introduction                  | 22  |

|          | 4.2           | Filtering Validities                     | 23  |

| 5        | FI            | R Sequencer                              | 24  |

| : | 5.1  | Sequencer Overview                                     | . 24 |

|---|------|--------------------------------------------------------|------|

|   | 5.2  | LTA Interface to the Sequencer                         | .24  |

| : | 5.3  | FIR Program Counter                                    | .24  |

| : | 5.4  | Main Loop Structure                                    | .25  |

|   | 5.5  | Tasks for the Sequencer to Do Broken up into HCB Tasks | .25  |

| : | 5.6  | How the Sequencer Tasks are Implemented                | .25  |

| - | 5.7  | Detailed Sequencer Main Filter Loop Structure          |      |

|   | 5.7. |                                                        |      |

|   | 5.7. | 2 The Idle Loop                                        | . 27 |

|   | 5.7. | 3 The Main Loop                                        | . 27 |

|   | 5.7. |                                                        |      |

|   | 5.7. |                                                        |      |

|   | 5.7. | 6 For More Detail Than Shown on 1031d14                | . 30 |

| 6 | FI   | R Microprocessor Software                              | .30  |

| ( | 6.1  | Brief Descriptions of the Software Modules             | .30  |

|   | 6.1. | 1 MASTER.ASM                                           | . 31 |

|   | 6.1. |                                                        |      |

|   | 6.1. |                                                        |      |

|   | 6.1. |                                                        |      |

|   | 6.1. |                                                        |      |

|   | 6.1. |                                                        |      |

| ( | 6.2  | Microprocessor Interrupt Structure                     | . 32 |

| 7 | FI   | R PAL Descriptions                                     | .32  |

|   | 7.1  | PAL File Locations                                     | . 32 |

|   | 7.2  | FIRPAL1 7 Bit Modulus Counter PAL                      | . 32 |

|   | 7.3  | FIRPAL2A & 2B Baseline and Result Count Switch         | .34  |

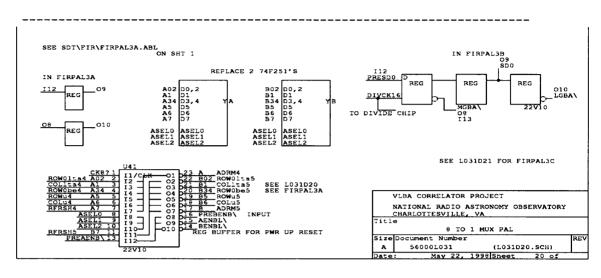

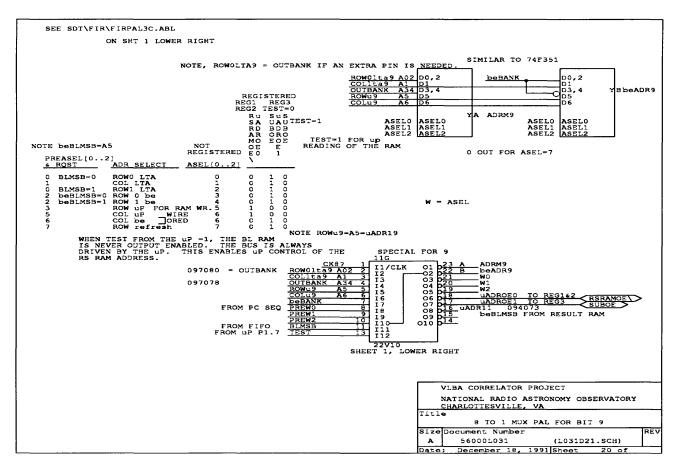

|   | 7.4  | FIRPAL3A & B & C 8 to 1 Mux PALs                       | .35  |

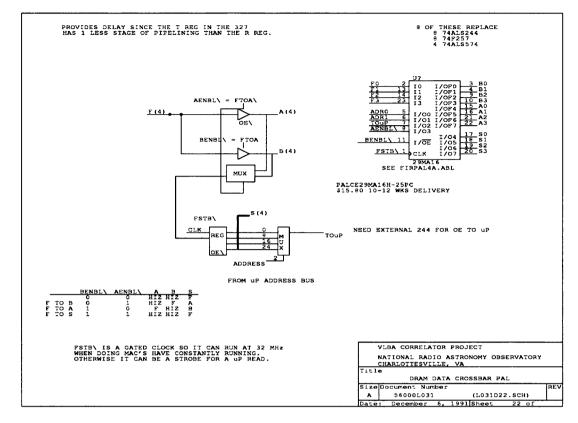

|   | 7.5  | FIRPAL4A Data Crossbar                                 | .37  |

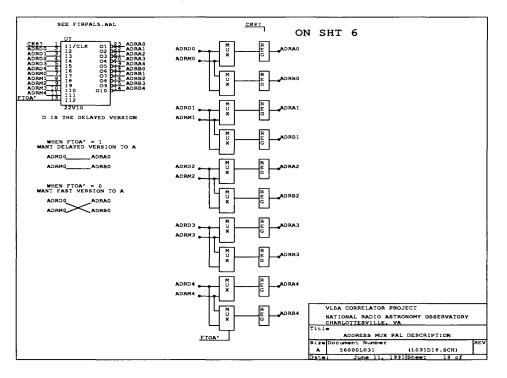

|   | FIRP | AL5 Address Multiplexer                                | . 38 |

|   | 7.7  | FIRPAL6B Ironics                                       |      |

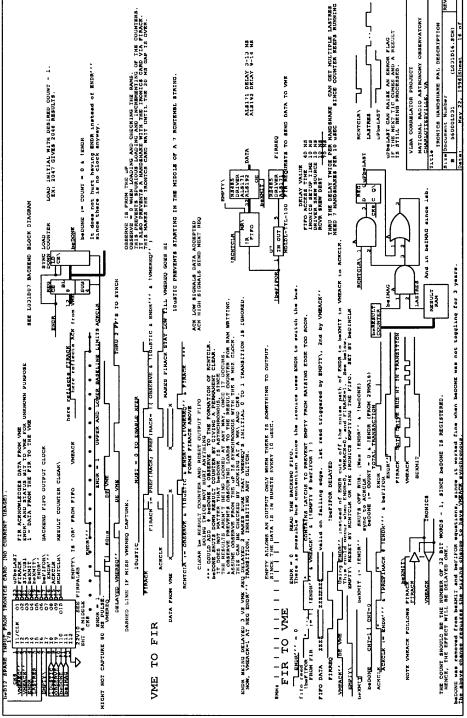

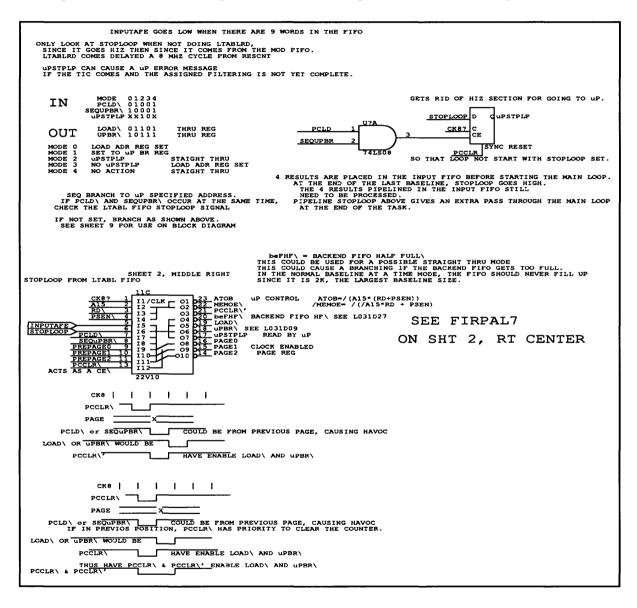

|   | 7.8  | FIRPAL7 Sequencer                                      |      |

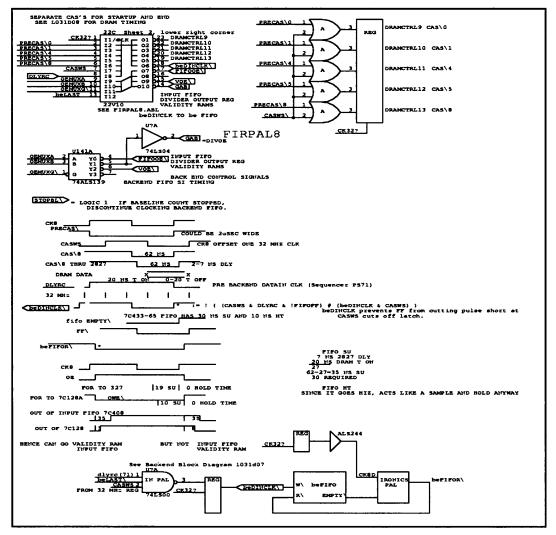

|   | 7.9  | FIRPAL8 CAS                                            | . 41 |

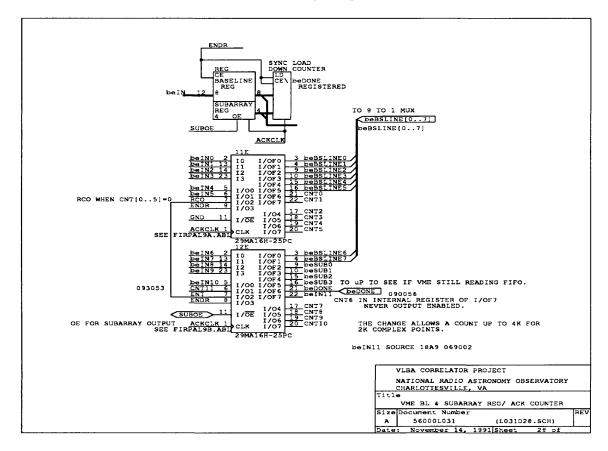

|   | FIRP | AL9A & B VME BL & Subarray Register / ACK Counter      | . 42 |

|   |      | AL10 Clear Accumulator (CLAC)                          |      |

|   | 7.12 | FIRPAL11 HCB Control                                   |      |

|   | 7.12 | FIRPAL12 Delay beLAST                                  |      |

|   |      | -                                                      |      |

| 8 |      | e Locations                                            |      |

| 9 | -    | ftware for Exercising the FIR                          |      |

|   | 9.1  | firSST                                                 | .45  |

| 9.2 firValSST                                                                                                         | 45   |

|-----------------------------------------------------------------------------------------------------------------------|------|

| 9.3 bldbsln                                                                                                           | 45   |

| 9.4 firRun                                                                                                            | 46   |

| 9.5 Backend Access                                                                                                    |      |

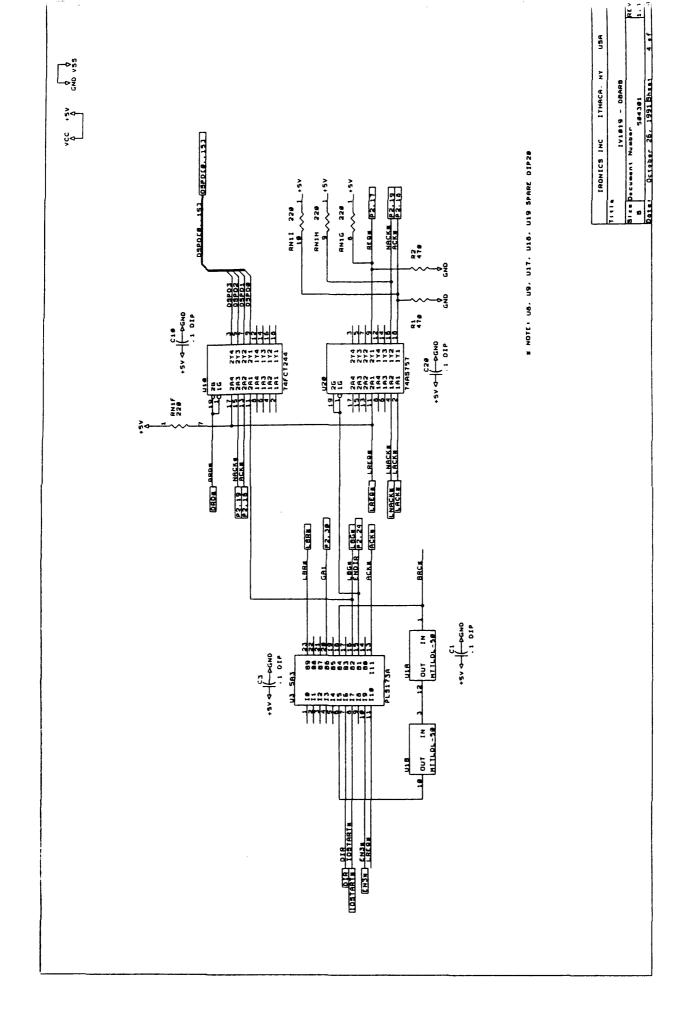

| 10 Transition Module for the Ironics Card                                                                             | . 48 |

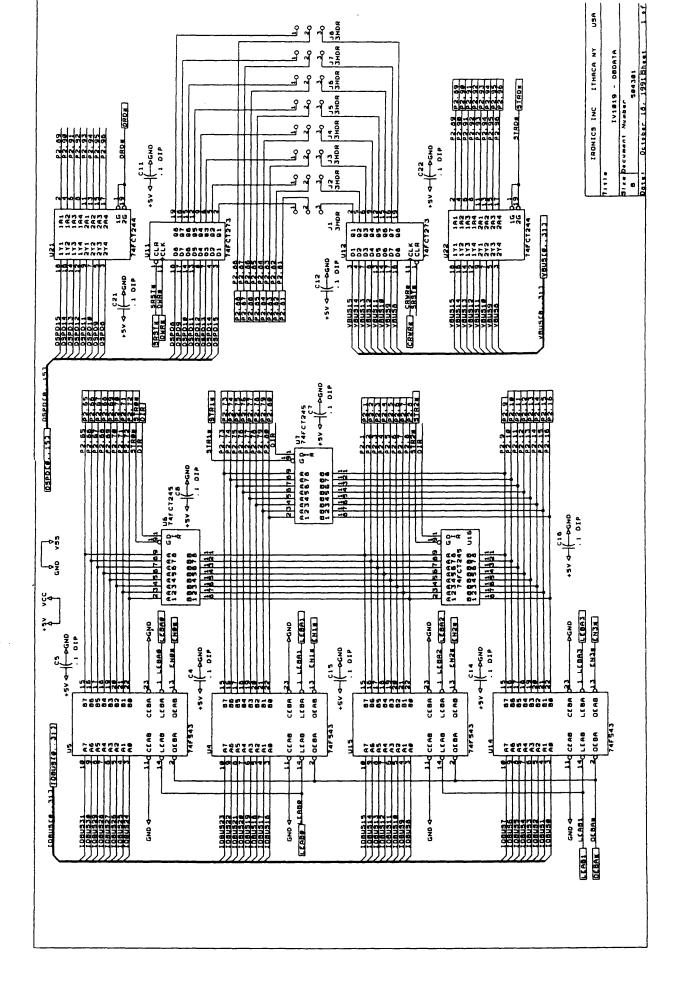

| 11 The Ironics Card                                                                                                   |      |

| 11.1 Ironics Hardware Description                                                                                     |      |

|                                                                                                                       |      |

| 11.2         Ironics Software Description           11.2.1         *irFirRead(firstbsln,nrbslines,nrresults,subarray) |      |

| 11.2.2 irReset()                                                                                                      | 48   |

| 11.2.3 irStartDma()                                                                                                   | 49   |

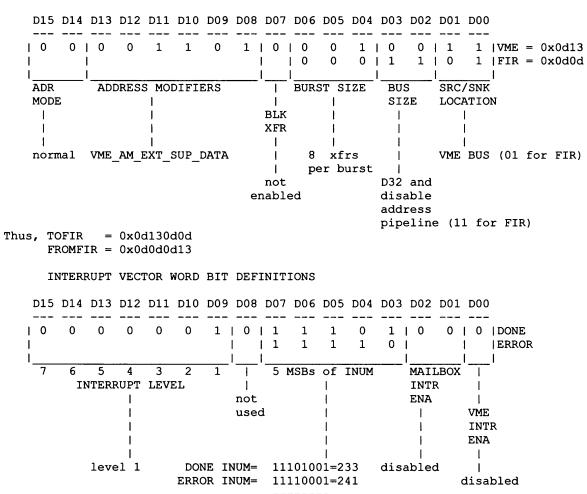

| 11.2.4 Other Ironics Control Words                                                                                    | 49   |

| 12 The FIR Test Fixture                                                                                               | . 50 |

| 12.1 Introduction                                                                                                     | 50   |

| 12.2 FIR Test Fixture Control Logic                                                                                   | 51   |

| 12.3 FIR Test Fixture Wiring                                                                                          | 51   |

| 12.4 Using the FIR Test Fixture                                                                                       |      |

| 13 Troubleshooting the FIR                                                                                            |      |

| 13.1 Microprocessor Based Tests                                                                                       | 51   |

| 13.1.1 Rom Based Tests                                                                                                | 51   |

| 13.1.2 Microprocessor RAM based tests                                                                                 | 51   |

| 13.2 Tests via the Real Time System                                                                                   | 52   |

| 13.2.1 firTestTaps                                                                                                    | 52   |

| 13.2.2 fir TestRRLd                                                                                                   | 52   |

| 13.2.3 firSST                                                                                                         |      |

| 13.2.4 firValSST                                                                                                      |      |

| 13.2.5 firRun<br>13.2.6 hcbTestLtaFir                                                                                 |      |

|                                                                                                                       |      |

| 13.3 How to Read an LTA Baseline Via the FIR                                                                          | 53   |

| 13.3.1 How to Read an Fir Baseline                                                                                    | 53   |

| 13.3.2 How to Read LTA Baselines via the FIR                                                                          |      |

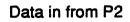

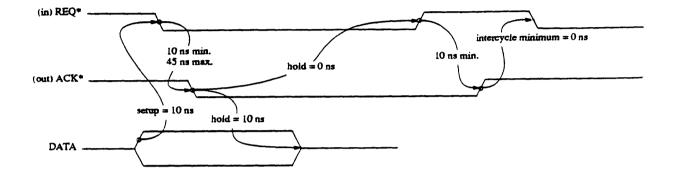

| APPENDIX I FIR HCB Protocol                                                                                           |      |

| APPENDIX II FIR Memory Allocations                                                                                    |      |

| APPENDIX III TRW TMC3210 CMOS Floating Point Divider                                                                  | 71   |

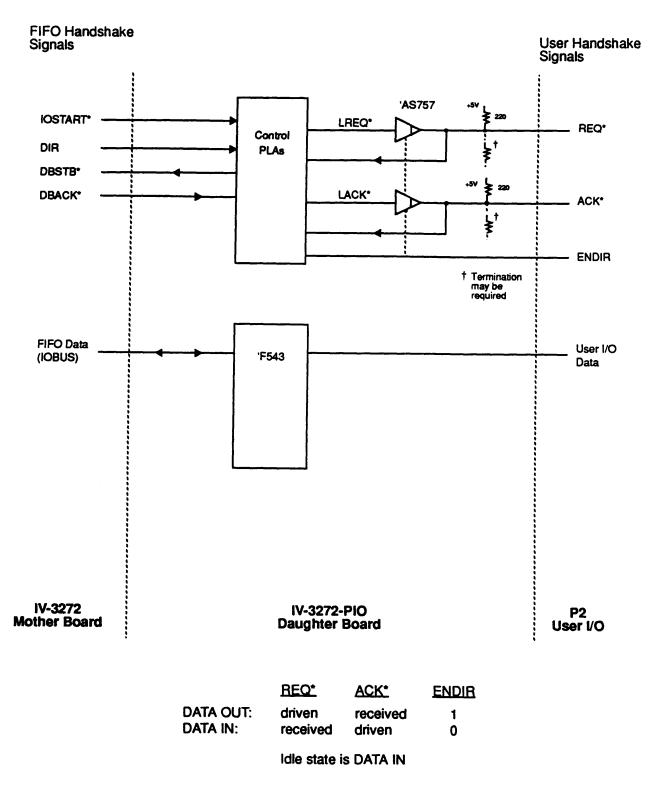

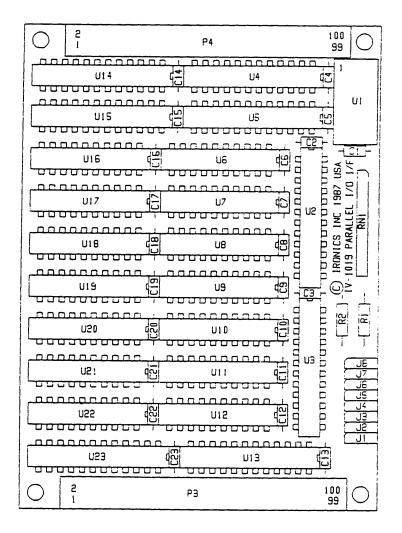

| APPENDIX IV Ironics IV-3272-PIO Parallel Interface Daughter Board                                                     | 73   |

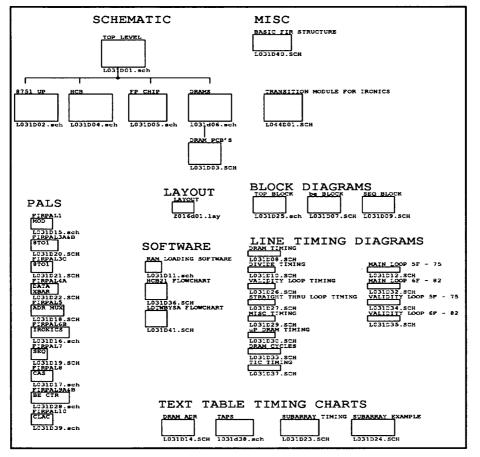

# **TABLE OF FIGURES**

| Figure | 1  | Basic FIR Structure                                    |

|--------|----|--------------------------------------------------------|

| Figure | 2  | 1031d38 Tap Weights9                                   |

| Figure | 3  | FIR Subarray Example                                   |

| Figure | 4  | Backend Result Ram Loading25                           |

| Figure | 5  | The Seven Bit Modulus Counter Pal                      |

| Figure | 6  | Baseline and Result Count Switch from Block Diagram    |

| Figure | 7  | The 8 to 1 MUX PAL                                     |

| Figure | 8  | 8 to 1 MUX PAL for Bit 9                               |

| Figure | 9  | The DRAM Data Crossbar PAL                             |

| Figure | 10 | ) Address Mux PAL Description                          |

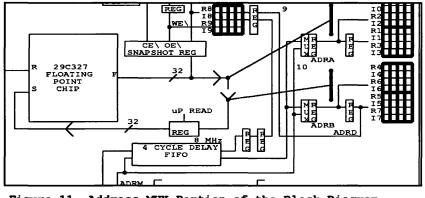

| Figure | 11 | Address MUX Portion of the Block Diagram               |

| Figure | 12 | •                                                      |

| Figure | 13 | 3 The Sequencer Control PAL Description40              |

| Figure | 14 | I The CAS Handling Pal                                 |

| Figure | 15 | 5 VME Baseline and Subarray Register / ACK Counter PAL |

| Figure | 16 |                                                        |

| Figure | 17 | I Lower Center of Backend Block Diagram, 1031d07       |

| Figure | 18 | 3 FIR Orcad Drawing Menu                               |

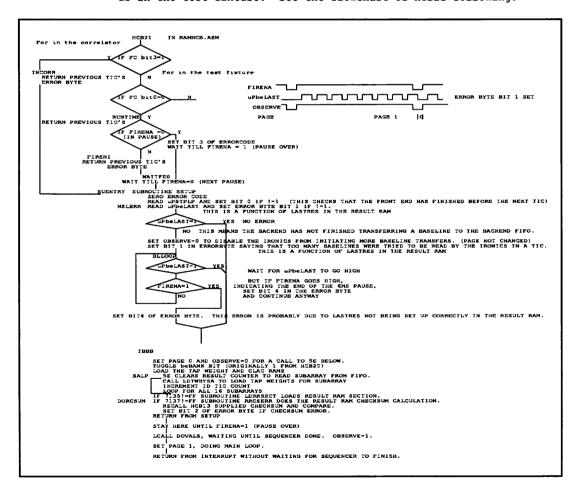

| Figure | 19 | 9 HCB21 Flowchart                                      |

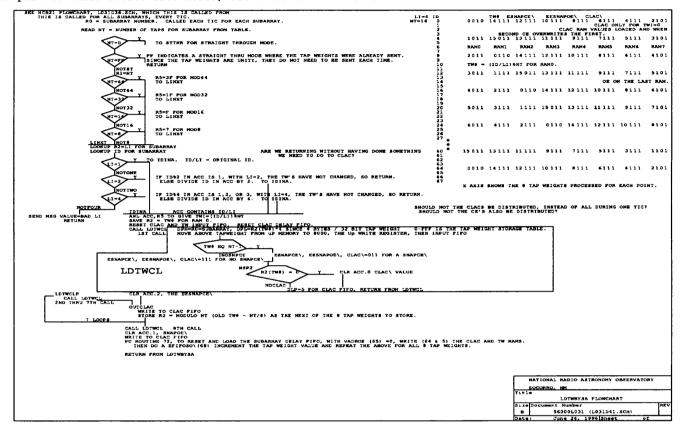

| Figure | 20 | ) LDTWBYSA Flowchart64                                 |

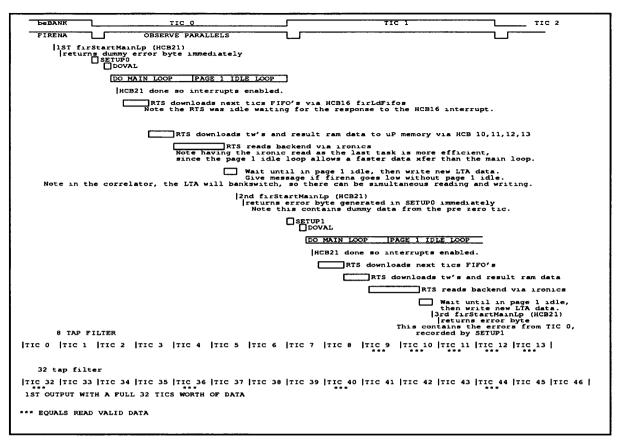

| Figure | 21 | L Tic Timing                                           |

# 1 Introduction

## 1.1 Functions of the FIR Filter Card

The FIR Filter Card (FIR) has two main functions. In normal operation, the FIR is an interface between the LTA (Long Term Accumulator) and the VME system. In this case, the FIR reads results from the LTA and transfers them unaltered to the VME system. Alternatively, the FIR can be operated as a Finite Impulse Response Filter that filters the data from the LTA before passing it on to the VME system. The primary purpose of this filtering is to reduce the output data rate while retaining fringe frequency response.

The interface from the FIR to the VME system is by way of a commercial DMA controller card installed in the VME chassis. This is the Ironics IV-3272 card with the IV-3272-PIO Parallel I/O Daughter Board installed. Signals between the FIR and the Ironics are buffered on the Transition Module for Ironics IV-3272, NRAO schematic drawing number 56000L044 (Orcad file name L044D01.SCH). This transition module is located in the rear section of the VME chassis, with the other system transition modules.

Each spectral point, of each baseline requested, is filtered. The data streams are filtered in time, where one unit of time is one integration period. The minimum LTA integration period is 131 ms.

# 2 The FIR Card

### 2.1 Top Level FIR Block Diagram Description

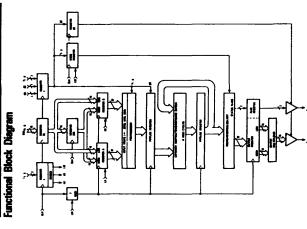

For the following discussion, refer to 1031d25.sch in Volume II, the Top Level FIR Block Diagram. This diagram shows the overall data and address flow in the FIR.

### 2.1.1 Reading Data from the LTA

The LTA is read out, one complex result at a time. A complex result consists of two, 32 bit IEEE floating point numbers, real and imaginary. A 19 bit address is supplied to the LTA. The address consists of an eight bit baseline (0-255), and an eleven bit result (0-2047).

The FIR operates in a batch mode, in that it is given a list of instructions to process every 131 msec. Once the instructions are processed, the FIR is idle, until given more work. The instructions are queued up in Fifos on the FIR.

An instruction consists of the following;

The LTA baseline to be read. The 'modulus' which tells how many results are in the baseline. The 'tap weight index' telling which tap weights to use. The 'stoploop bit' signaling the end of the list of baselines. The 'DRAM baseline' specifying the FIR memory baseline to place the results in.

The modulus controls a programmable counter, to count out the number of results assigned to that baseline. This eleven bit result field becomes part of the address to the LTA. A sequencer controls the sending of the addresses from the FIFO to the LTA, along with a RQSTSTB\ signal to request reading the LTA. The IEEE complex results from the LTA are strobed into an FIR input fifo, by the signal

FIRSI\. See HCB Function 16, LDFIFOS, in Appendix I, the HCB Protocol, for more details.

# 2.1.2 Processing the LTA Data

### 2.1.2.1 Straight thru Mode

The simplest mode is Straight thru Mode. The data is passed straight thru the 29C327 Floating Point Chip (FPC). This is accomplished by setting the tap weights equal to one. The output of the FPC is captured in the Snapshot Register. The Snapshot Register output is transferred to the Output Buffer. The Output Buffer is a double buffer in DRAM, labeled R8,I8,R9,I9 on the diagram. Each half of the Output Buffer has storage for 128 baselines of 2048 results each. Depending on the state of BLMSB, each baseline can be broken in half to form two baselines of 1024 results, providing storage for 256 baselines of 1024 results each.

The address for writing into the Output Buffer is generated as follows. The DRAM Baseline FIFO supplies the baseline number, and the control bit, BLMSB. BLMSB=1 for 256 baselines and 1024 results. BLMSB=0 for 128 baselines and 2048 results. The result portion of the address comes from the same counter that generated the result address to the LTA. A FIFO delays the result field for timing. The Output Buffer address comes from a multiplexer, which chooses the correct address source. The opposite half of the double buffered Output Buffer is read by the Real Time System (RTS). This is done via the Ironics Card. The Output buffer is read into a FIFO for timing purposes. The Ironics Card drains the FIFO. This will be described in more detail in Section 11.

## 2.1.2.2 Filter Mode

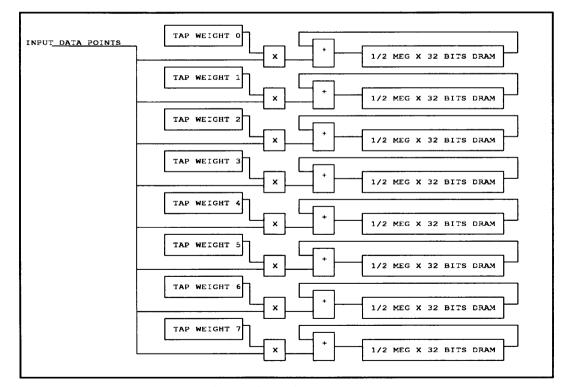

Figure 1 presents an overview of how the FIR digital filter works.

Figure 1 Basic FIR Structure

Each input data point is multiplied by eight distinct tap weights. A running sum of these products is stored in a distinct ram. This is done for all the results of all the baselines being processed in the 131 ms time tic. The eight ram sections correspond to R0/I0 through R7/I7 on the right edge of the block diagram, 1031d25.sch.

Actually, the tap weights 0 through 7 are reloaded from the microprocessor for each time tic. This reloading allows different values of tap weights to be used each tic. For an N tap filter, the N tap weight would be rotated through in N tics. After N products have been summed in ram, the value can be read out as the filtered result. After that, the CLAC signal clears the accumulator and the process repeats. Notice the data rate can be reduced, since data is only output every N tics. By having the process going on concurrently in 8 ram banks, with the tap weights used staggered among the ram banks, we multiply the output data rate by 8. Thus, the decimation factor is equal to N/8. The decimation factor is the amount the data rate has been reduced, and is shown below for each value of N.

| ecimation Factor | C                                    |

|------------------|--------------------------------------|

| 1                |                                      |

| 2                |                                      |

| 4                |                                      |

| 8                |                                      |

|                  | ecimation Factor<br>1<br>2<br>4<br>8 |

| NÎ - 32 TAP FILTER<br>Id/Li ramo ranî ranz rans rans rans rans rans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NT — 64 TAP FILTER<br>IC/LI RANG RANI RAN2 RAN3 RAN4 RAN5 RAMé RAM7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NOTE FOR EACH SUBARRAY, THERE ARE ONLY & TAP WEIGHTS OF<br>Interest in a given dump time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUTO TO<br>INPUTI TI ID EQUALS TIC COUNT<br>INPUT2 T2 LI - TICS PER DUNGP 1, 2, OR 4<br>INPUT3 T3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INPUTD TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EACH 131 XS:<br>Store the 9 tap weights of interest for the 9 subarrays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INPUT4 T4 T0<br>INPUT5 T5 T1<br>INPUT4 T6 T2 • - REACY FOR OUTPUT<br>INPUT7 T7 T3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1APUT4 T4<br>IAPUT5 T5<br>IAPUT6 T6<br>IAPUT7 T7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - READY FOR OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INPUTS TS T4 T0<br>INPUTS T9 T5 T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | INPUTO TO TO<br>INPUTO TO TI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S TAP FILTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| INVERT TF         T6           INVERT TF         T6 <td>LEVELS TS TS TELEVISION CONTRACTOR CONTRACTS TS TELEVISION CONTRACTS TS TELEVI</td> <td>17/11         KAMG         <t< td=""></t<></td> | LEVELS TS TS TELEVISION CONTRACTOR CONTRACTS TS TELEVISION CONTRACTS TS TELEVI | 17/11         KAMG         KAMG <t< td=""></t<> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INVERSE         TO           INVERSE         TO </td                                                                                                                                                                                                                                                                                           |

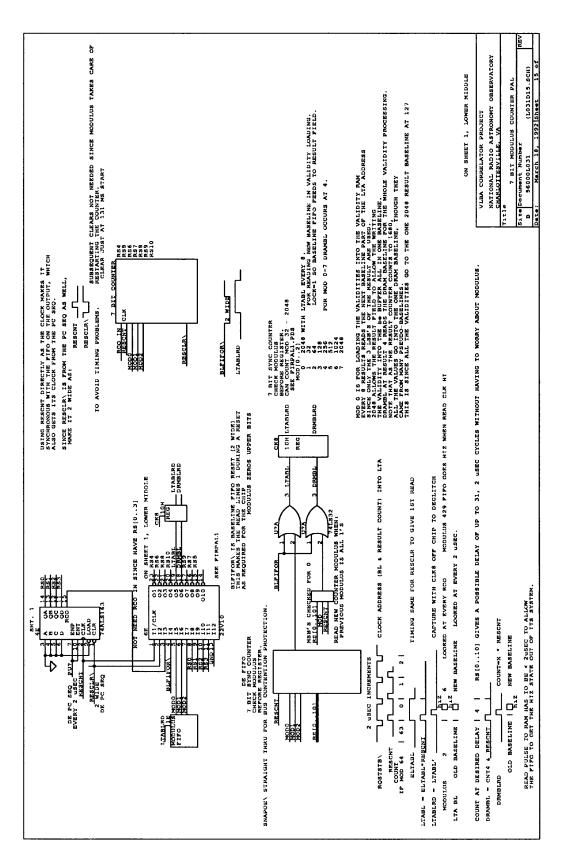

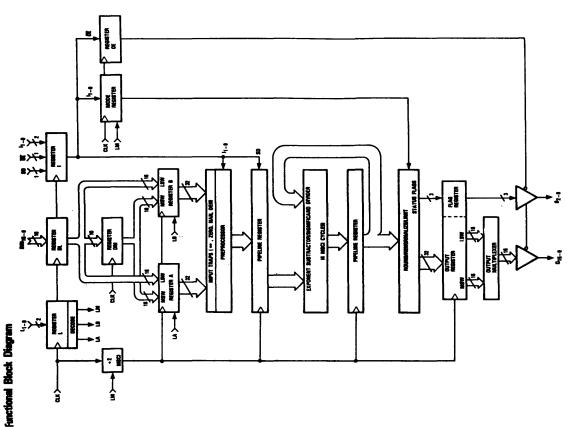

#### Figure 2 1031d38 Tap Weights

L031d38.sch here shows the tap weights used for N=8, 32, and N=64.

For the 8 tap filter on the right, each ram uses tap weights T0 through T7 over eight tics. Notice the staggering of tap weights between rams. When each ram has had the data points multiplied by T7 added in, then that ram's data is ready for output, as indicated by the \*. After the initial eight tics, there is data output every tic.

For the 32 tap filter on the left, ram0 shows the rotation of T0 through T31. The  $\star$  at T31 indicates the summation is ready for output. In Ram 1, we see the tap weights occurring 4 tics later. The next point output would be from Ram 1 when it gets to T31. This yields a decimation by four.

The factor LI is the tics per dump. For simplicity in the above explanation, 1 tic per dump was assumed. However, LI=2 or LI=4 are allowed. For LI=2, baselines are processed every other 131 ms tic. The basic batch cycle of the FIR is always 131 ms. However, we can do different baseline lists each 131 ms, to give an effective LI of 2 or 4. Alternatively, the FIR could be idle for some of the tics. The batch nature of the FIR allows the RTS full control of the work load distribution to the FIR. The RTS must be careful not to give the FIR more work than can be done in 131 ms.

The following table shows an example of distributing the FIR workload when there are multiple subarrays.

SUBARRAY EXAMPLE:

| SUBARRAY 0 FILTERED THRU AN 8 TAP FILTER                                                                     |

|--------------------------------------------------------------------------------------------------------------|

| 16 BASELINES, DUMPED EVERY 131 MS.                                                                           |

| 16*2048 RESULTS*8 BYTES /.131 SEC = 2 MBYTES/SEC                                                             |

|                                                                                                              |

|                                                                                                              |

| SUBARRAY 1 IN STRAIGHT THRU MODE                                                                             |

| 136 BASELINES, DUMPED EVERY 20 * 131 MS.                                                                     |

| 136 BASELINES, DOMPED EVERY 20 $^{\circ}$ 131 MS.<br>136*2048 RESULTS*8 BYTES /20*.131 SEC = 0.85 MBYTES/SEC |

|                                                                                                              |

| DUMP 6 OR 7 BASELINES PER CYCLE                                                                              |

| 4 MBYTES/SEC AVAILABLE FROM LTA. VS (2 + 0.85) MBYTES/SEC NEEDED                                             |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 0-5                                                                                     |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 6-10                                                                                    |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 11-16                                                                                   |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 17-23                                                                                   |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 24-30                                                                                   |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 31-35                                                                                   |

| DUMP SUB 0 BASELINES 0-15                                                                                    |

| DUMP SUB 1 BASELINES 36-42                                                                                   |

| DUMP SUB 0 BASELINES 0-15 OUTPUT INITIAL FILTERED SUB0 DUMP                                                  |

| DUMP SUB 1 BASELINES 43-49                                                                                   |

|                                                                                                              |

#### 2.1.2.2.1 Tap Weight Ram Loading

Return to 1031d25.sch in Volume II, the Top Level Block Diagram. The Tap Weight Ram is the 2Kx32 Ram in the center of the drawing. The tap weights are loaded into the ram via HCB Function 10, DWNLDTAPS (Refer to Appendix I, the HCB Protocol). The tap weights are stored as 32 bit IEEE floating point numbers. They are written via the Microprocessor Write register, which parallels the data path from the LTA. The data goes, via the FIFO, to the tap weight ram. The 11 bit address to the tap weight ram has the 4 msb's pulled high. In the remaining 7 bits, there is a 4 bit Tap Weight Index(TWI). This allows 16 different versions of the tap weights to be stored in the ram at once. The RTS could load a version of the tap weights, in a non-active TWI ahead of time. A 3 bit address from the sequencer chooses among the eight active tap weights. This same address bus is used for reading the tap weights when the filter is active.

### 2.1.2.2.2 The CLAC Ram

The Clear Accumulator (CLAC) Ram shares its address bus with the 7 active bits of the Tap Weight Ram. It is also loaded from the microprocessor. The ram provides these three control bits:

CLAC - Controls an instruction to the floating point chip, to zero the ram accumulator contents, coincident with the T0 tap weight.

SNAPCE\ - Snapshot Register Clock enable causes the Snapshot Register to capture the data which is ready for transfer to the output buffer. That is the data which has the complete summation of tap weights times data points.

SNAPOE\ - Snapshot Register Output Enable puts the Snapshot Register stored data on the bus for transfer to the Output Buffer.

### 2.1.2.2.3 The DRAM Address Select Multiplexer

The address multiplexer provides the addresses to the DRAMs. One function of the multiplexer is to break the 20 bit DRAM address into the two, 10 bit sections (ROW and COL) the DRAM requires.

The Multiplexer supplies DRAM addresses for the following purposes:

- 1) The DRAMs can be written to or read by the microprocessor.

- 2) The DRAMs can be written with results from the LTA.

- 3) The DRAMs can be read by the backend logic.

- 4) The DRAMs are systematically refreshed.

# **3** Overview of the FIR Card

# 3.1 Data Rates

# 3.1.1 LTA to FIR Data Rates

Each dump from all the MAC cards, every 131 ms produces 210 baselines times 256 spectral points per baseline times 8 channels. This results in 430,080 complex floating point numbers per dump, or 860,160 single precision IEEE values per dump, or 3,440,640 bytes per dump. These values are integrated in the LTA.

The LTA has a maximum output rate of 1 complex floating point number / 2.0156 usec or 3.969 Mbytes/sec. At least one 2 usec period per 16 usec fft cycle is needed for refresh. This degrades the LTA maximum rate to  $7/8 \times 3.969 = 3.473$  Mbytes/sec.

The LTA transfers one complex point to the FIR every 2 usec, if requested. The FIR software uses 5, 2 usec cycles to process 4 data points. This degrades the maximum input rate to  $4/5 \times 3.969 = 3.175$  Mbytes/sec. This rate allows the LTA a refresh cycle every 5, 2 usec cycles. This satisfies the requirement that a refresh cycle be allowed every 8, 2 usec cycles. The LTA imposes an up to 20 ms. pause each tic for house keeping. This can degrade the input rate by 111ms/131ms to 2.7 Mbytes/sec. A 32 tap filter would decimate this to 0.67 Mbytes/sec.

### 3.1.2 FIR Output Data Rate

The maximum output data rate of the fir loop is determined by how much work the fir is given each tic. A 2 usec period, which provides backend access, gives 7, 4 byte reads in the 2 usec. This is based on one backend ram read every 250 ns, for 1.750 usec. The extra 250 ns cycle, in the 2 usec pause, is used to refresh all DRAM's. When the fir is filtering, it uses the above 10 usec cycle, which contains one 2 usec output cycle. This gives 2.8 Mbytes/sec maximum output rate while running the 10 usec loop. During the portion of the tic, in which the fir is not filtering, a 4 usec idle loop is run. This has one, 2 usec output cycle every 4 usec, for an output rate of 6.9 Mbytes/sec. See 1031d14 in Volume II for the sequence.

Each complex number gets multiplied by 8 real tap weights, and accumulated in 8 separate ram banks. Each output is the weighted sum of 32 inputs. For the output data rate to be 4 the input, 32/4=8. i.e. in order to store 32 points worth, when we output every 4<sup>th</sup> dump, we need 8 ram banks. Each ram bank size is half the maximum dump size or 1,720,320 bytes.

# 3.2 Basic FIR Program Loop

The following shows the basic 29C327 program loop for filtering data.

The 16 clock cycles represent 2 usec at a 125 ns clock period. T1,T2... represent the tap weights for successive filter banks. ACCr1,ACCr2... represents the accumulated value from memory.

This first section has 16 clock cycles to load R0-R7. The validities are input, then the 4 complex values are input, normalized and stored. R IN and S IN straight thru give a window for a microprocessor read of S & R.

| CLOCK  | R-INPUT   | S-INPUT     | INSTRUCTION INPUT    | SOURCE OUTPUT   |

|--------|-----------|-------------|----------------------|-----------------|

| 0      | DUMMY     | INSTRUCTION | FOLLOWING LAST MAC   | 76 T4*R7+ACCi28 |

| 1      | VAL0      |             | STRAIGHT THRU        | 77 T5*R7+ACCi29 |

| 2      | VAL1      |             | STRAIGHT THRU        | 78 T6*R7+ACCi30 |

| 3      | VAL2      |             | STRAIGHT THRU        | 79 T7*R7+ACCi31 |

| 4      | VAL3      |             | STRAIGHT THRU        | 1 R4=VAL0       |

| 5      | RE0       |             | REO*R4               | 2 R5=VAL1       |

| 6      | IM0       |             | IMO*R4               | 3 R6=VAL2       |

| 7      | RE1       |             | RE1*R5               | 4 R7=VAL3       |

| 8      | IM1       |             | IM1*R5               | 5 RO=REO*VALO   |

| 9      | RE2       |             | RE2*R6               | 6 R1=IMO*VALO   |

| 10     | IM2       |             | IM2*R6               | 7 R2=RE1*VAL1   |

| 11     | RE3       |             | RE3*R7               | 8 R3=IM1*VAL1   |

| 12     | IM3       |             | IM3*R7               | 9 R4=RE2*VAL2   |

| 13     | R IN      |             | STRAIGHT THRU        | 10 R5=IM2*VAL2  |

| 14     |           | S IN        | STRAIGHT THRU        | 11 R6=RE3*VAL3  |

| 15     |           |             |                      | 12 R7=IM3*VAL3  |

| NOW FI | ILTER 32  | RESULTS     |                      | OUTPUT =        |

| 16     | тО        | ACCr0       | T0*R0+0              | 13 R IN         |

| 17     | Т1        | ACCr1       | T1*R0+ACCr1          | 14 S IN         |

| 18     | т2        | ACCr2       | T2*R0+ACCr2          |                 |

| 19     | тЗ        | ACCr3       | T3*R0+ACCr3          |                 |

| 20     | Т4        | ACCr4       | T4*R0+ACCr4          | 16 TO*RO+O      |

| 21     | т5        | ACCr5       | T5*R0+ACCr5          | 17 T1*R0+ACCr1  |

|        | т6        | ACCr6       | T6*R0+ACCr6          | 18 T2*R0+ACCr2  |

| 23     | т7        | ACCr7       | T7*R0+ACCr7          | 19 T3*R0+ACCr3  |

|        | тО        | ACCi0       | T0*R1+0              | 20 T4*R0+ACCr4  |

| -      | Т1        | ACCi1       | T1*R1+ACCi1          | 21 T5*R0+ACCr5  |

| 26     | -         | ACCi2       | T2*R1+ACCi2          | 22 T6*R0+ACCr6  |

|        | тЗ        | ACCi3       | T3*R1+ACCi3          | 23 T7*R0+ACCr7  |

| 28     |           | ACCi4       | T4*R1+ACCi4          | 24 T0*R1+0      |

|        | т5        | ACCi5       | T5*R1+ACCi5          | 25 T1*R1+ACCi1  |

|        | т6        | ACCi6       | T6*R1+ACCi6          | 26 T2*R1+ACCi2  |

| 31     | т7        | ACCi7       | T7*R1+ACCi7          | 27 T3*R1+ACCi3  |

|        |           |             |                      | 28 T4*R1+ACCi4  |

|        |           |             |                      | 29 T5*R1+ACCi5  |

|        |           |             |                      | 30 T6*R1+ACCi6  |

|        |           |             |                      | 31 T7*R1+ACCi7  |

| CLC    | оскз 32 т | O 47 REPEAT | ABOVE USING R2 & R3. |                 |

CLOCKS 32 TO 47 REPEAT ABOVE USING R2 & R3. CLOCKS 48 TO 63 REPEAT ABOVE USING R4 & R5. CLOCKS 64 TO 79 REPEAT ABOVE USING R6 & R7.

NOTE: A 0 IS ADDED ONLY WHEN CLAC IS USED TO CLEAR ACCUMULATOR.

This has a cycle of inputting 4 complex points and their validities in 2 usec. Then 8 usec is spent MACing these to the 8 rams. The program timing and addressing to the 8 rams is fixed and set by the sequencer. See L031D32 in Volume II for more detailed timing.

The actual sequencer code is in vlbsoft/pal\_prom/proms/firfpc/pg0.wk3, a Lotus worksheet. The worksheet is divided into 3 pages. Page 0 is test and discrete functions. Page 1 is the main loop processing, defined above. Page 2 is the validity loop processing.

The program fircode.c translates the printout of the above worksheet, fir.prn, to the binary files to be downloaded into the discrete rams. The command line is: fircode fir.prn. At the filter maximum input rate of 3.175 Mbytes/sec, it takes 542 ms, or 4.14 131 ms cycles, to fill a FIR ram bank of 1,720,320 bytes. Thus, if the dump time is 4 cycles, the maximum input rate can be sustained for 4 cycles without filling up the ram. Dump times of 4, 2, or 1 cycles will be allowed through the filter. Longer dump times can be used in straight thru mode.

# 3.3 Straight Thru Mode

In straight thru mode, there are unity tap weights downloaded into the tap weight ram, as specified by the microprocessor routine LDTWBYSA. Whatever goes into ram bank 0, also is written to the output buffer. We do not need to worry if the total dump is bigger than the output buffer size, since only a portion of it can be read out each tic anyway. The specified LTA and DRAM baseline numbers, being different, allows translating from the LTA memory bank, to the FIR memory bank. An FIR memory bank is half the size of an LTA memory bank. The information stored in the other eight, FIR DRAM banks, is of no interest in straight thru mode.

### 3.4 Backend Buffer

The output buffer to the backend consists of a 32 bit x 1 Meg DRAM. This is divided into 2 banks. One is output to, while the other is read by the backend. The bank switching occurs every 131 ms cycle, by P1.6 beBANK from the microprocessor. For a 32 tap filter, the filter outputs every  $4^{th}$  131 ms cycle, for a 131 ms dump time from the LTA. The bank will switch, and the backend will have the subsequent 131 ms cycles to read out these results. The bank will again switch, and nothing new will be written. The bank will switch back, and results could be read if they had not all been read out two tics ago.

### 3.5 Subarrays